|              |                                                                             |

|--------------|-----------------------------------------------------------------------------|

| Title        | A High-speed NDN Forwarding Engine on a Commercial Off-the-shelf Computer   |

| Author(s)    | 武政, 淳二                                                                      |

| Citation     | 大阪大学, 2019, 博士論文                                                            |

| Version Type | VoR                                                                         |

| URL          | <a href="https://doi.org/10.18910/72593">https://doi.org/10.18910/72593</a> |

| rights       |                                                                             |

| Note         |                                                                             |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# A High-speed NDN Forwarding Engine on a Commercial Off-the-shelf Computer

Submitted to

Graduate School of Information Science and Technology

Osaka University

January 2019

JUNJI TAKEMASA

# List of Publications

## Journal Papers

1. Kaito Ohsugi, Junji Takemasa, Yuki Koizumi, Toru Hasegawa and Ioannis Psaras, “Power Consumption Model of NDN-Based Multicore Software Router Based on Detailed Protocol Analysis,” *IEEE Journal on Selected Area in Communications*, vol. 34, no. 5, pp. 1631–1644, May. 2016.

2. Junji Takemasa, Yuki Koizumi and Toru Hasegawa, “Is Caching a Key to Energy Reduction of NDN Networks?,” *IEICE Transactions on Communications*, vol. 99, no. 12, pp. 2489–2497, Dec. 2016.

3. Junji Takemasa, Yuki Koizumi and Toru Hasegawa, “Lightweight Cache Admission Algorithm for Fast NDN Software Routers,” *to appear in IPSJ Journal of Information Processing*.

## Refereed Conference Papers

1. Junji Takemasa, Yuki Koizumi, Toru Hasegawa, and Ioannis Psaras, “On Energy Reduction and Green Networking Enhancement due to In-Network Caching,” in *Proceedings of IEEE MASS Workshop on Content-Centric Networking*, pp. 513–518, Oct. 2015.

2. Kosuke Taniguchi, Junji Takemasa, Yuki Koizumi and Toru Hasegawa, “Poster: A Method for Designing High-Speed Software NDN Routers,” in *Proceedings of ACM Conference on Information-Centric Networking, Poster Session*, pp. 203–204, Sep. 2016.

3. Junji Takemasa, Kosuke Taniguchi, Yuki Koizumi and Toru Hasegawa, “Identifying Highly Popular Content Improves Forwarding Speed of NDN Software Router,” in *Proceedings of IEEE GLOBECOM Workshop on Information Centric Networking Solutions for Real World Applications*, pp. 1–6, Dec. 2016.

4. Junji Takemasa, Yuki Koizumi and Toru Hasegawa, “Toward an Ideal NDN Router on a

Commercial Off-the-shelf Computer,” in *Proceedings of ACM Conference on Information-Centric Networking, Full-Paper Session*, pp. 43–53, Sep. 2017.

5. Junji Takemasa, Yuki Koizumi and Toru Hasegawa, “Analysis of Mutual Exclusion Overhead of NDN Packet Forwarding on Multi-core Software Router,” in *Proceedings of ACM Conference on Information-Centric Networking, Poster Session*, Sep. 2018.

## Non-Refereed Technical Papers

1. Junji Takemasa, Yuki Koizumi, Toru Hasegawa, “A Study on a Power Trade-off between Cache Processing Overheads and Traffic Reduction in CCN Networks,” in *IEICE Communication Society Conference*, B-7-45, Sep. 2014 (in Japanese).

2. Junji Takemasa, Yuki Koizumi, Toru Hasegawa and Ioannis Psaras, “A Study on Energy Reduction Effects due to In-Network Caching in ICN Networks,” in *IPSJ Kansai Society*, E-17, Sep. 2015 (in Japanese).

3. Junji Takemasa, Kosuke Taniguchi, Yuki Koizumi, and Toru Hasegawa, “Cache Admission for Improving Forwarding Speed of NDN Software Router,” in *IEICE Technical Report*, vol. 116, no. 361, IN2016-83, pp. 97–102, Dec. 2016 (in Japanese).

4. Junji Takemasa, Yuki Koizumi, Toru Hasegawa, “A Study on Power Consumption Trade-Off Due to Caching in NDN Networks,” in *IEICE General Conference*, B-7-5, Mar. 2016 (in Japanese).

5. Junji Takemasa, Yuki Koizumi, Toru Hasegawa, “A Study on Power Reduction due to Caching in an NDN Access Network,” in *IEICE Communication Society Conference*, B-7-25, Sep. 2016 (in Japanese).

6. Junji Takemasa, Yuki Koizumi, and Toru Hasegawa, “Bottleneck Analysis on Packet Forwarding of an NDN Software Router,” in *IEICE Technical Report*, vol. 116, no. 485, IN2016-83, pp. 97–102, Mar. 2017 (in Japanese).

7. Junji Takemasa, Kosuke Taniguchi, Yuki Koizumi, Toru Hasegawa, “On a Bottleneck Analysis on Packet Forwarding of an NDN Software Router,” in *IEICE General Conference*, B-7-74, Mar. 2017 (in Japanese).

8. Junji Takemasa, Yuki Koizumi, and Toru Hasegawa, “An Analysis on Data Structures and Algorithms for FIB of a Fast PC-based NDN Router,” in *IEICE Technical Report*, vol. 116, no. 205, IN2017-25, pp. 13–18, Sep. 2017 (in Japanese).

9. Junji Takemasa, Kosuke Taniguchi, Yuki Koizumi, Toru Hasegawa, “On an Analysis on

Increase in Packet Processing Latency Due to Parallelizing a PC-based NDN Router,” in *IEICE Communication Society Conference*, B-7-27, Sep. 2017 (in Japanese).

10. Junji Takemasa, Yuki Koizumi, and Toru Hasegawa, “An Analysis on Cache Algorithm for CS of Fast PC-based NDN Router,” in *IEICE Technical Report*, vol. 117, no. 460, IN2017-130, pp. 243–248, Mar. 2018 (in Japanese).

11. Junji Takemasa, Yuki Koizumi, Toru Hasegawa, “A Study on Fast Cache Algorithm on PC-based NDN Router,” in *IEICE General Conference*, B-7-36, Mar. 2018 (in Japanese).

12. Junji Takemasa, Yuki Koizumi, Toru Hasegawa, “A Study on Maintaining Consistency of PIT States in NDN Parallel Packet Processing,” in *IEICE Communication Society Conference*, B-7-11, Sep. 2018 (in Japanese).

# Preface

A software router, which is built on a hardware platform based on a commercial off-the-shelf (COTS) computer, becomes feasible because of recent advances in multi-core CPUs and fast networking technologies for COTS computers. Fast IP packet forwarding has been a research issue for a long time and hardware architecture designed based on a CPU device with fast memory devices like static random access memory (SRAM) devices shows that storing data structures for IP forwarding on SRAM devices enables fast IP forwarding for about  $5 \times 10^4$  IP prefixes. Successively, compact data structures have become a research issue to keep up with the increasing number of IP prefixes in the Internet. Most of the studies have addressed compact trie-based data structures like multi-bit trie data structures by replacing consecutive elements in a trie to a single element. Such efforts enable it to store increasing IP prefixes on latest SRAM devices.

Recently, studies on high-speed algorithms and compact data structures are being revisited due to the emergence of the new Internet architecture called Named Data Networking (NDN), wherein rich data, including large video data and small sensor data, is delivered by a single architecture. High-speed NDN packet forwarding is not trivial compared to IP packet forwarding in terms of memory space and time complexity because name-based forwarding and packet caching, which are key components of NDN, need much larger data structures than IP forwarding. The number of names in the NDN-based Internet is believed to be at least the same that of unique domain names, and the number as of December 2017 is about  $2.1 \times 10^8$ . Such a large number of name prefixes needs large memory space and heavy computation. In addition to packet forwarding, caching needs extra data structures for managing packets in a router's cache and computation for it. Handling variable-length and human-readable names and stateful forwarding also incur heavy computation. Heavy name-based forwarding and caching make high-speed NDN packet forwarding challenging.

The goal of this thesis is to present what a high-speed NDN forwarding engine on a COTS computer is supposed to be. In this thesis, the author designs a reference forwarding engine by selecting well-established high-speed techniques and then analyzes a state-of-the-art prototype

implementation to identify its performance bottlenecks. The microarchitectural analysis at the level of CPU pipelines and instructions provides us with two observations. The first observation is that the DRAM access latency due to accesses to forwarding tables, which include tables of name-based forwarding and caching, is one of bottlenecks for high-speed forwarding engines and the other one is that wasteful cache computation for unpopular Data packets is the rest of the bottlenecks. According to the first observation, the author designs prefetch algorithms for name-based forwarding and caching in order to hide DRAM access latency. According to the second observation, the author designs a lightweight cache admission algorithm so that wasteful cache computations for unpopular Data packets are avoided with fast computation. The prototype of an NDN software router with the two techniques achieves a forwarding rate exceeding 40 million packets per second on a COTS computer.

The main contributions of this thesis are summarized as follows: First, as far as the author knows, this is the first study that summarizes observations found in existing studies to build high-speed NDN routers on computers and compiles the observations into a design guideline. According to the guideline, the author reveals that a hash table-based algorithm and a frequency-based cache admission algorithm are suitable for name-based forwarding and caching, respectively. Second, the author designs a prefetch algorithm for hiding most of the DRAM access latency for both name-based forwarding and caching. The prefetch algorithm reorders instruction executions for a pair of packets so that the DRAM access latency due to data fetches is successfully hidden by execution time of instructions independent of the data fetches. Third, the author carefully designs a lightweight frequency-based cache admission algorithm, Filter, on the basis of the results of the empirical measurement of an NDN software platform. As the results of the careful design, Filter consumes a few tens of CPU cycles in average with providing as high cache hit rate as ARC, which is one of the sophisticated cache eviction algorithms. Fourth, the author implements a proof-of-concept prototype of an NDN software router with the proposed two techniques and empirically proves that forwarding speed with the two techniques increases linearly as the number of CPU cores increases, whereas that without the two techniques does not increase so. A detailed analysis at the level of CPU pipelines and instructions reveal that most DRAM access latency are successfully hidden by the prefetch algorithm and that the number of CPU cycles of NDN packet processing is reduced by the Filter admission algorithm. Fifth, the author sheds light on power efficiency of NDN software routers as a positive effect of CPU cycle reduction at the different view point from forwarding speed improvement. By modeling how NDN packet processing consumes power of hardware devices on an NDN software router, the author reveals that reducing the number of CPU cycles spent for NDN packet processing contributes to power consumption reduction of an NDN software router.

# Acknowledgments

My research activities would not have been achieved without many individuals.

First of all, I would like to express my greatest appreciation to my supervisor, Professor Toru Hasegawa, Graduate School of Information Science and Technology, Osaka University, for his invaluable support and guidance during my study at Osaka University. He has always been encouraging and provided insights to help me develop research ideas. I have always been impressed by how he simplifies complex issues based on practical considerations.

I would like to express my gratitude to the members of my thesis committee, Professor Masayuki Murata, Professor Takashi Watanabe, and Professor Teruo Higashino, Graduate School of Information Science and Technology, Osaka University, and Professor Morito Matsuoka, Cyber Media Center, Osaka University, for carefully reviewing this thesis and providing valuable comments.

I am deeply grateful to Associate Professor Yuki Koizumi, Graduate School of Information Science and Technology, Osaka University, for irreplaceable guidance and support. His apt comments have stimulated my daily research activities and helped me to make a breakthrough in research.

I am cordially thankful to Dr. Ioannis Psaras, Department of Electronic & Electrical Engineering, University College London, for valuable comments to raise the quality of my research.

I would like to thank Dr. Keiichiro Tsukamoto of Dwango Corporation, Yuto Nakai of NTT Communications Corporation, Kaito Ohsugi of KDDI Corporation, and Yuji Manaka of NTT Communications Corporation, for their direction during my bachelor and master coursework. Their direction also has promoted my daily research activities.

Special thanks are due to Kosuke Taniguchi, Yoji Yamamoto and Yasunaga Murai for their ideas and valuable discussions. They have strengthened the base of my researches and reinforced the value of this thesis.

I would like to extend my appreciation to the members of the Information Sharing Platform Laboratory. Especially, I am thankful to Ms. Tomoko Ueshima for her kind help. I thank Yasutaka Tara and Keita Hasegawa of past members of the Laboratory. I think that daily conversation with them

has given me many inspirations. I also express my appreciation to all members of the Information Sharing Platform Laboratory, Graduate School of Information Science and Technology, Osaka University.

Finally, I would like to express my heartfelt appreciation to my father, mother, old brother, and little sister, for their warm-hearted help and support. With the help of them, I could concentrate on this work and complete it with an easy mind.

# Contents

|                                                                           |            |

|---------------------------------------------------------------------------|------------|

| <b>List of Publications</b>                                               | <b>i</b>   |

| <b>Preface</b>                                                            | <b>v</b>   |

| <b>Acknowledgments</b>                                                    | <b>vii</b> |

| <b>1 Introduction</b>                                                     | <b>1</b>   |

| 1.1 Background . . . . .                                                  | 1          |

| 1.2 Approaches . . . . .                                                  | 2          |

| 1.2.1 Elimination of DRAM Access Latency . . . . .                        | 3          |

| 1.2.2 Fast Cache Algorithm with High Cache Hit Rate . . . . .             | 4          |

| 1.2.3 Power Efficiency Due to CPU Cycle Reduction . . . . .               | 5          |

| 1.3 Contributions . . . . .                                               | 6          |

| 1.4 Outline . . . . .                                                     | 6          |

| <b>2 Related Work</b>                                                     | <b>9</b>   |

| 2.1 Name-based Forwarding . . . . .                                       | 9          |

| 2.2 Caching . . . . .                                                     | 10         |

| 2.3 Software Packet Processing . . . . .                                  | 11         |

| 2.4 Hardware Packet Processing . . . . .                                  | 12         |

| 2.5 Power Efficiency of Routers . . . . .                                 | 13         |

| <b>3 Microarchitectural Bottleneck Analysis of an NDN Software Router</b> | <b>15</b>  |

| 3.1 Hardware and Software Platforms . . . . .                             | 16         |

| 3.1.1 Hardware Platform . . . . .                                         | 16         |

| 3.1.2 NDN Packet Forwarding . . . . .                                     | 17         |

|          |                                                                                           |           |

|----------|-------------------------------------------------------------------------------------------|-----------|

| 3.1.3    | Practices to Exploit Parallel Computation . . . . .                                       | 18        |

| 3.2      | Microarchitectural Hardware Bottleneck Analysis . . . . .                                 | 20        |

| 3.2.1    | Bottleneck Analysis Method . . . . .                                                      | 20        |

| 3.2.2    | Experiment Settings . . . . .                                                             | 22        |

| 3.2.3    | Analysis Results . . . . .                                                                | 24        |

| 3.3      | Microarchitectural Software Bottleneck Analysis . . . . .                                 | 28        |

| 3.3.1    | NDN Packet Processing of Reference NDN Software . . . . .                                 | 28        |

| 3.3.2    | Analysis Results . . . . .                                                                | 28        |

| 3.4      | Design Rationale . . . . .                                                                | 29        |

| <b>4</b> | <b>Data Prefetches to Eliminate Pipeline Stalls on Hash Table-based Forwarding Tables</b> | <b>31</b> |

| 4.1      | Data Structure and Algorithm for FIB . . . . .                                            | 32        |

| 4.1.1    | Overview . . . . .                                                                        | 32        |

| 4.1.2    | Hash Table-based FIB . . . . .                                                            | 32        |

| 4.1.3    | Trie-based FIB . . . . .                                                                  | 34        |

| 4.1.4    | Summary . . . . .                                                                         | 35        |

| 4.2      | Cache Algorithm for CS . . . . .                                                          | 36        |

| 4.2.1    | Overview . . . . .                                                                        | 36        |

| 4.2.2    | Cache Eviction Algorithm . . . . .                                                        | 36        |

| 4.2.3    | Cache Admission Algorithm . . . . .                                                       | 37        |

| 4.2.4    | Summary . . . . .                                                                         | 38        |

| 4.3      | Prefetch-Friendly Packet Processing . . . . .                                             | 39        |

| 4.3.1    | Unhidden Data Fetches in Conventional Packet Processing . . . . .                         | 39        |

| 4.3.2    | Prefetch Strategies . . . . .                                                             | 40        |

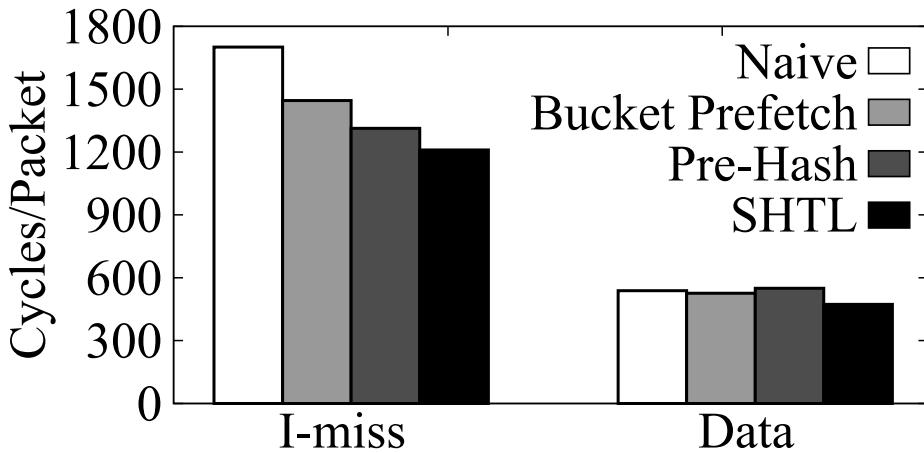

| 4.4      | Performance Evaluation . . . . .                                                          | 43        |

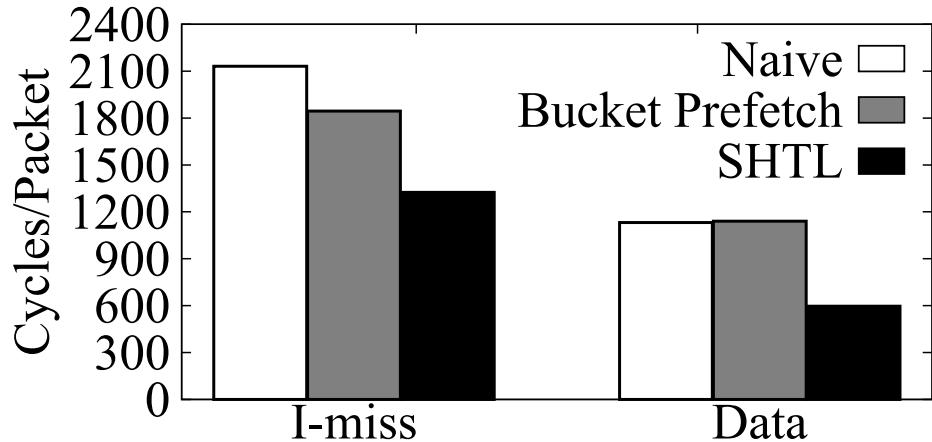

| 4.4.1    | CPU Cycles in Single-Threaded Case . . . . .                                              | 43        |

| 4.4.2    | CPU Cycles in Multi-Threaded Case . . . . .                                               | 44        |

| 4.4.3    | Forwarding Speed . . . . .                                                                | 45        |

| 4.4.4    | Discussion . . . . .                                                                      | 46        |

| 4.5      | Conclusion . . . . .                                                                      | 47        |

| <b>5</b> | <b>A Lightweight Cache Admission Algorithm for Optimizing Time Complexity</b>             | <b>49</b> |

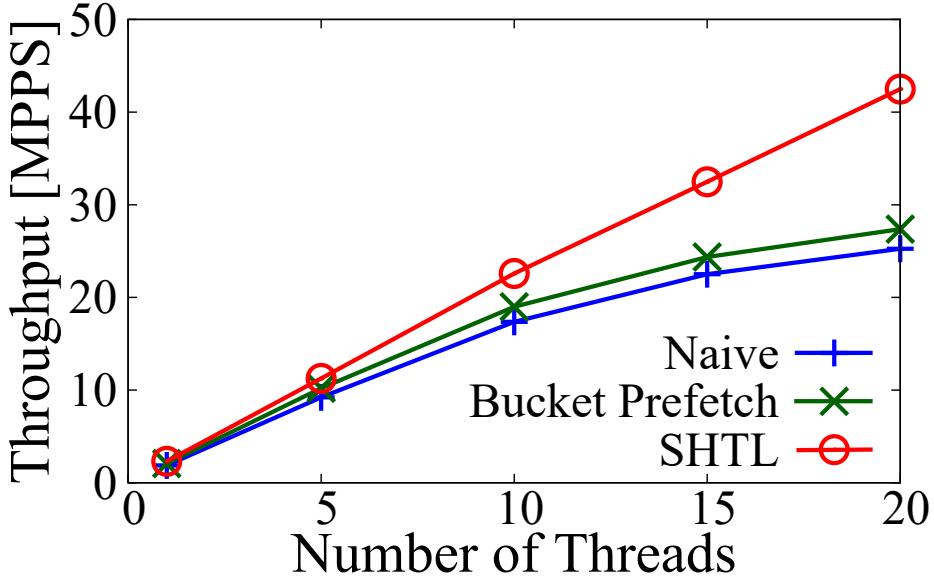

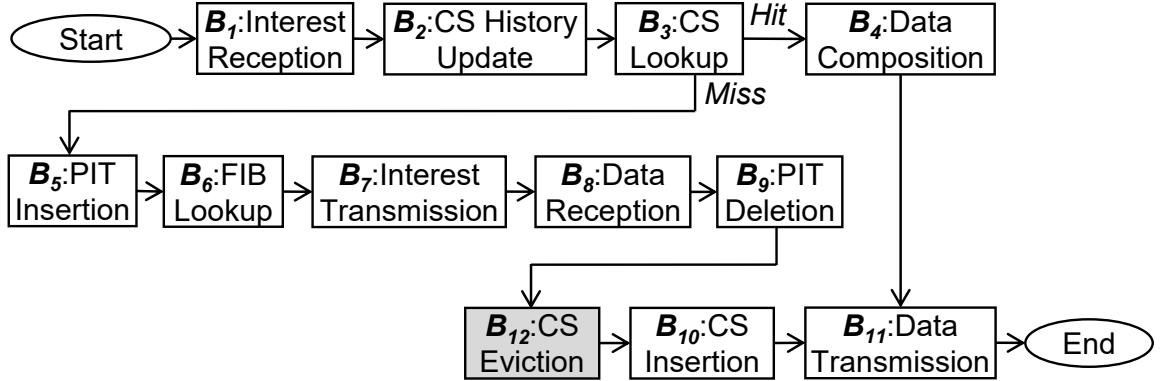

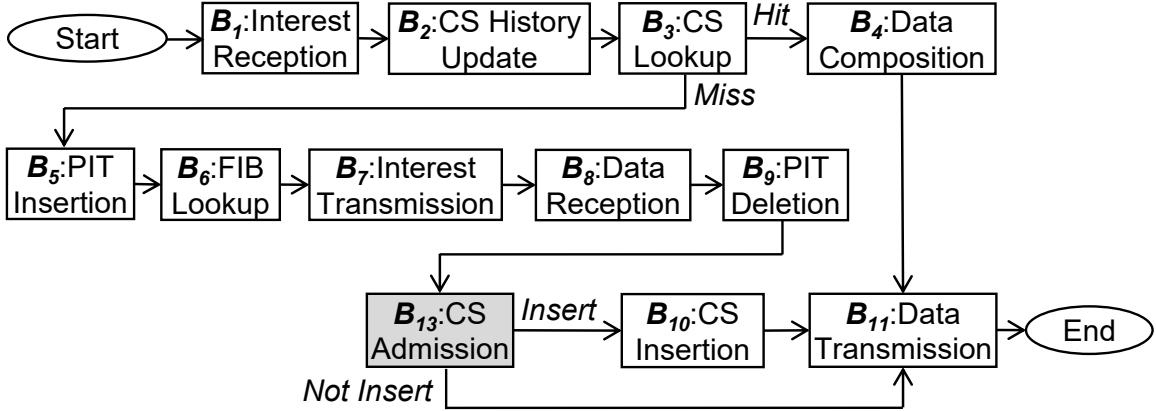

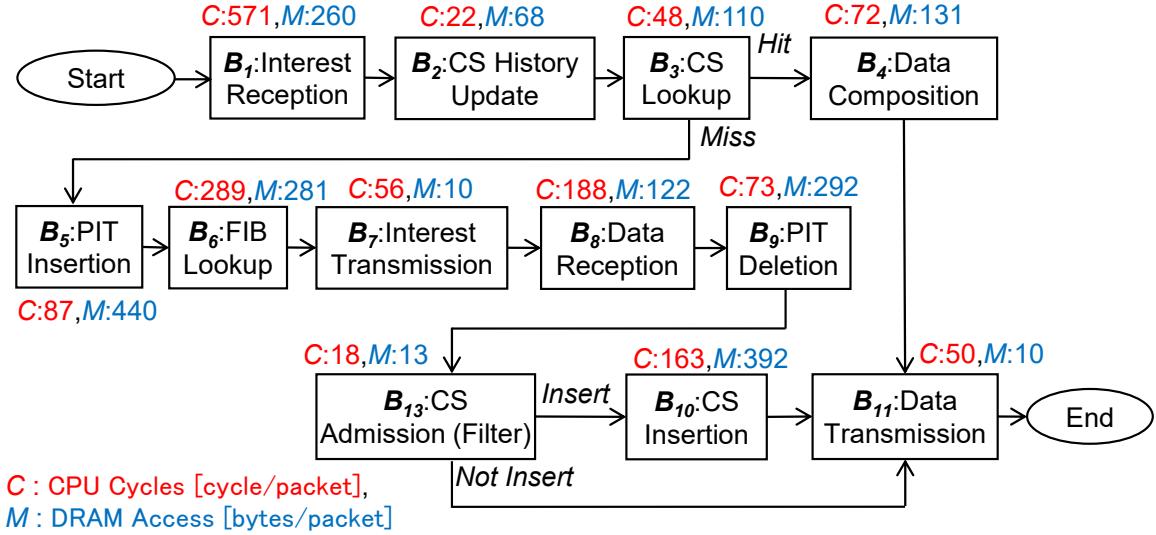

| 5.1      | Computation Time Analysis of Cache Algorithms . . . . .                                   | 50        |

| 5.1.1    | NDN Packet Processing with Cache Algorithms . . . . .                                     | 50        |

|          |                                                                            |           |

|----------|----------------------------------------------------------------------------|-----------|

| 5.1.2    | Cache Eviction vs. Cache Admission . . . . .                               | 52        |

| 5.2      | Design of Cache Admission Algorithm . . . . .                              | 53        |

| 5.2.1    | Overview . . . . .                                                         | 53        |

| 5.2.2    | Design Rationale . . . . .                                                 | 53        |

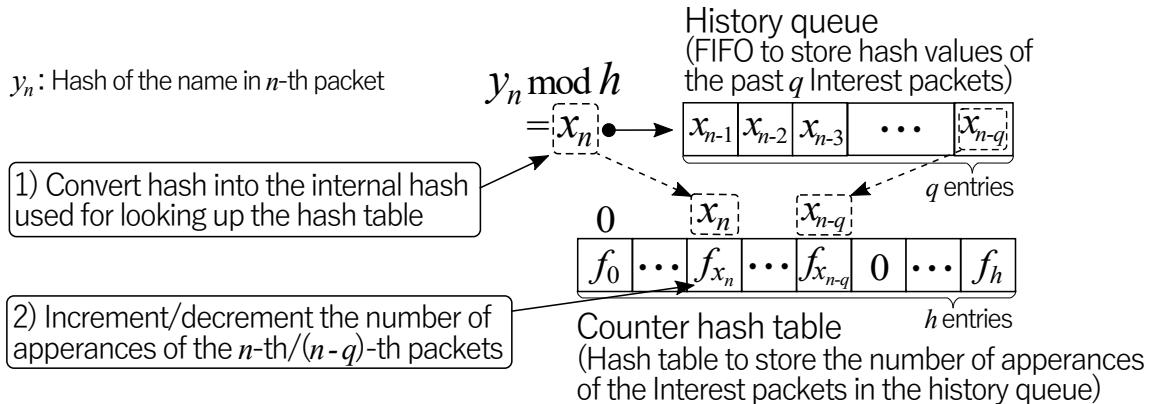

| 5.2.3    | Design of Filter . . . . .                                                 | 54        |

| 5.2.4    | Comparison with TinyLFU . . . . .                                          | 56        |

| 5.3      | Characteristic Analysis of Filter . . . . .                                | 56        |

| 5.3.1    | Overview . . . . .                                                         | 56        |

| 5.3.2    | Analysis Model . . . . .                                                   | 57        |

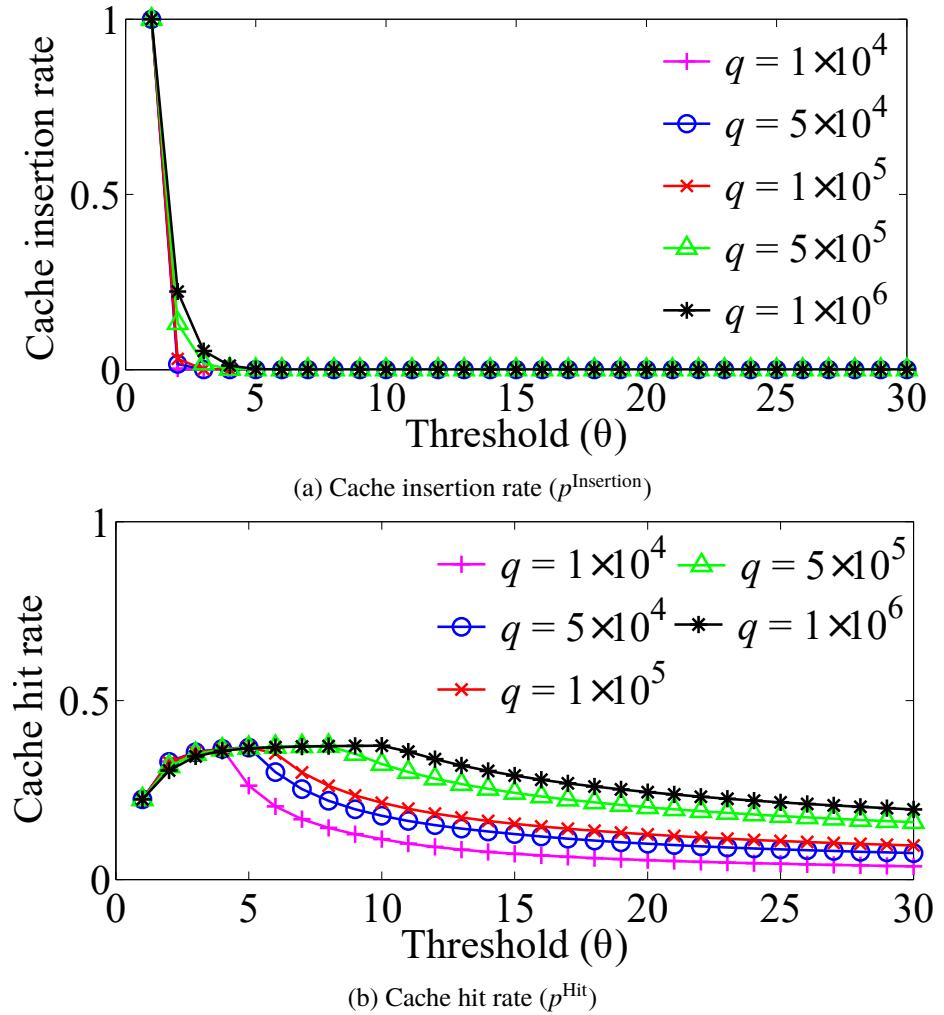

| 5.3.3    | Threshold Value . . . . .                                                  | 58        |

| 5.3.4    | Analysis Results . . . . .                                                 | 59        |

| 5.4      | Performance Evaluation . . . . .                                           | 59        |

| 5.4.1    | Evaluation Conditions . . . . .                                            | 59        |

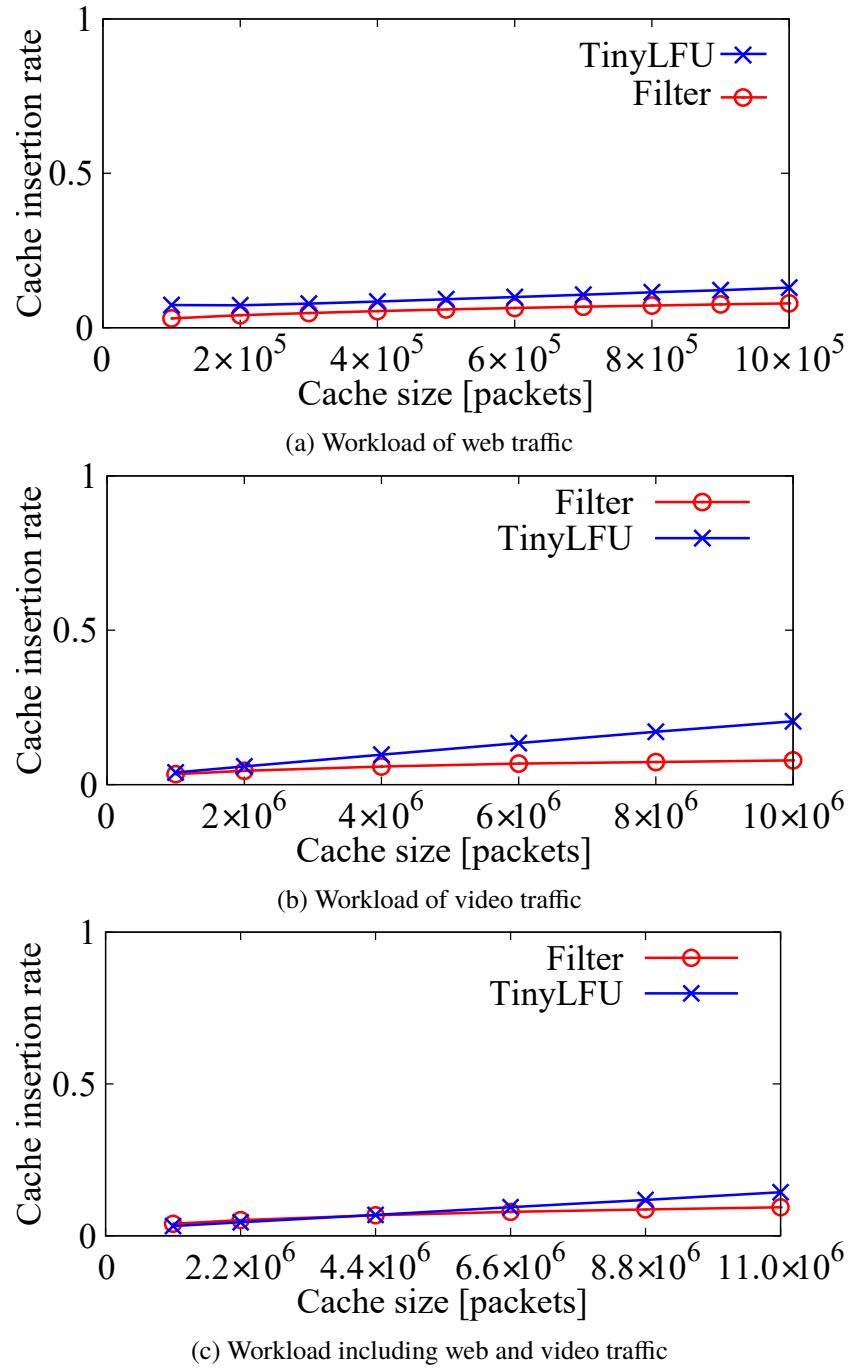

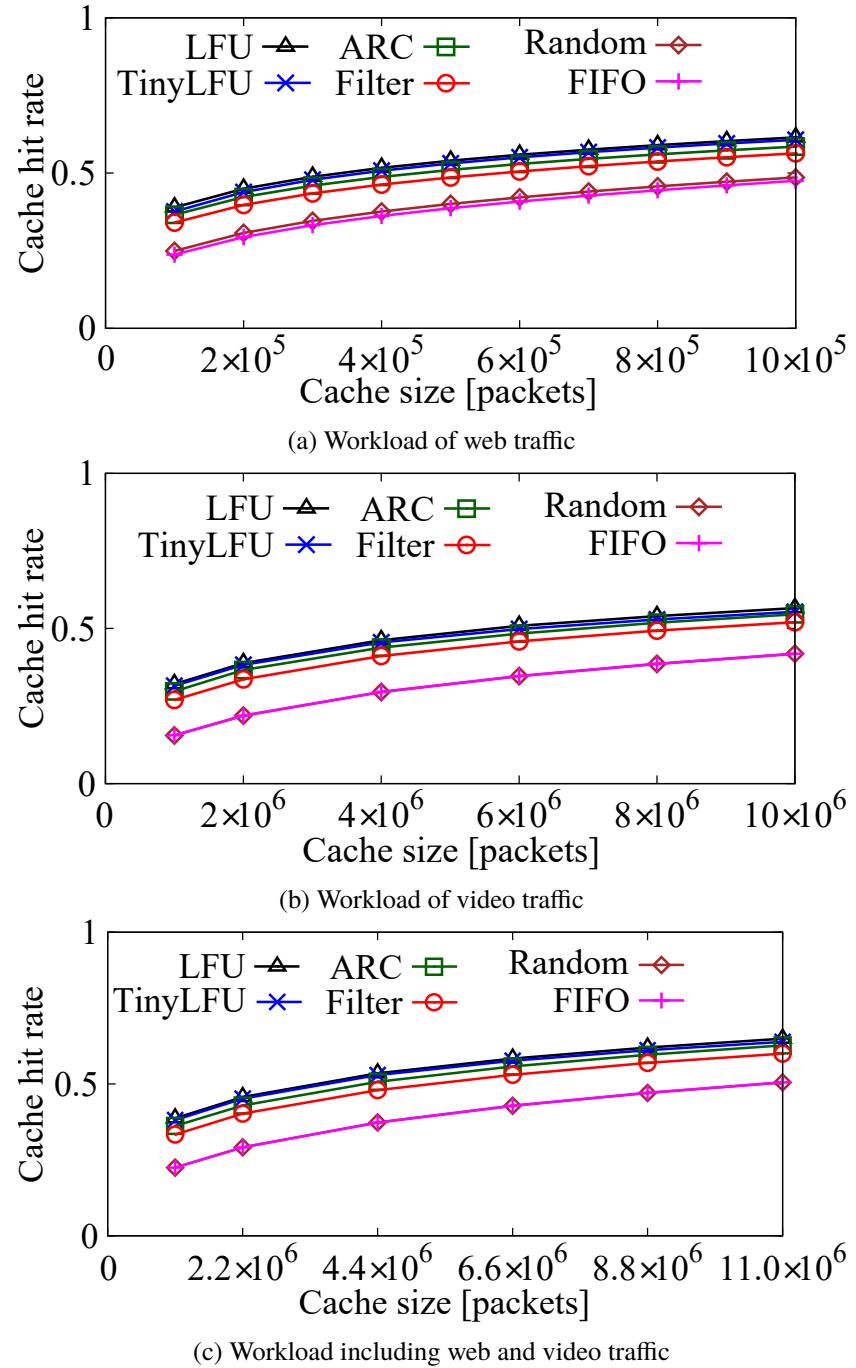

| 5.4.2    | Cache Insertion and Hit Rates . . . . .                                    | 61        |

| 5.4.3    | CPU Cycles Spent for NDN Packet Processing . . . . .                       | 62        |

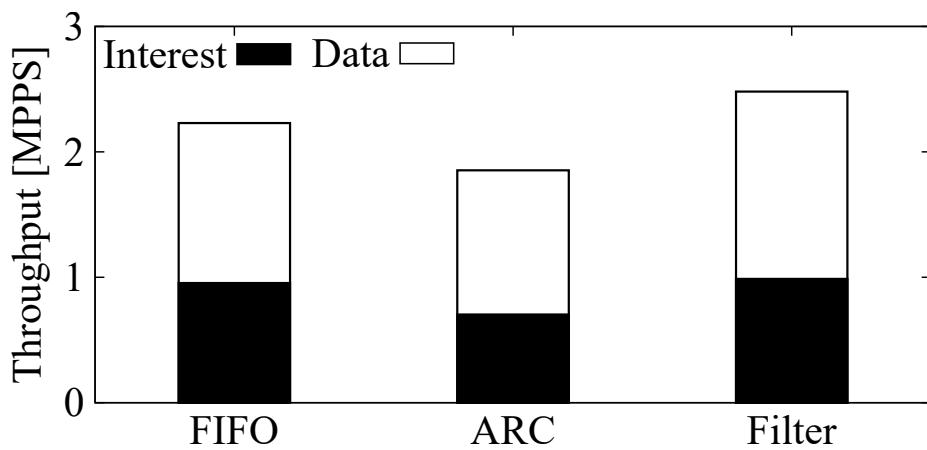

| 5.4.4    | Forwarding Speed . . . . .                                                 | 63        |

| 5.5      | Conclusion . . . . .                                                       | 64        |

| <b>6</b> | <b>Power Efficiency of NDN Software Routers Due to CPU Cycle Reduction</b> | <b>69</b> |

| 6.1      | Introduction . . . . .                                                     | 69        |

| 6.2      | Reference Architecture . . . . .                                           | 71        |

| 6.2.1    | Hardware Platform . . . . .                                                | 71        |

| 6.2.2    | Software Platform . . . . .                                                | 71        |

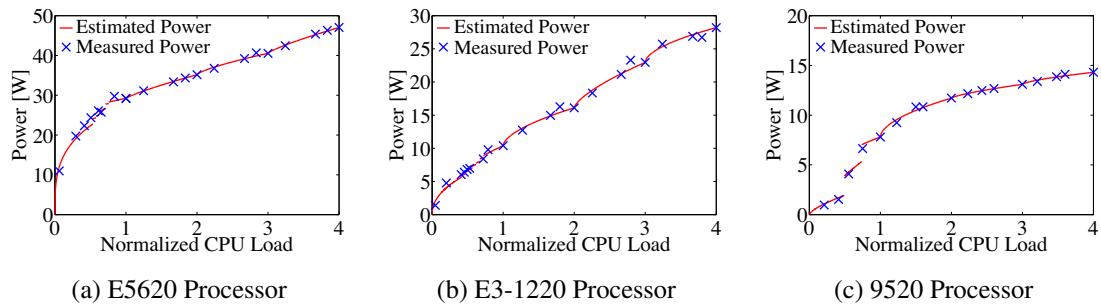

| 6.3      | Power Consumption Model . . . . .                                          | 72        |

| 6.3.1    | Formulation . . . . .                                                      | 73        |

| 6.3.2    | Power Consumed by Chassis . . . . .                                        | 74        |

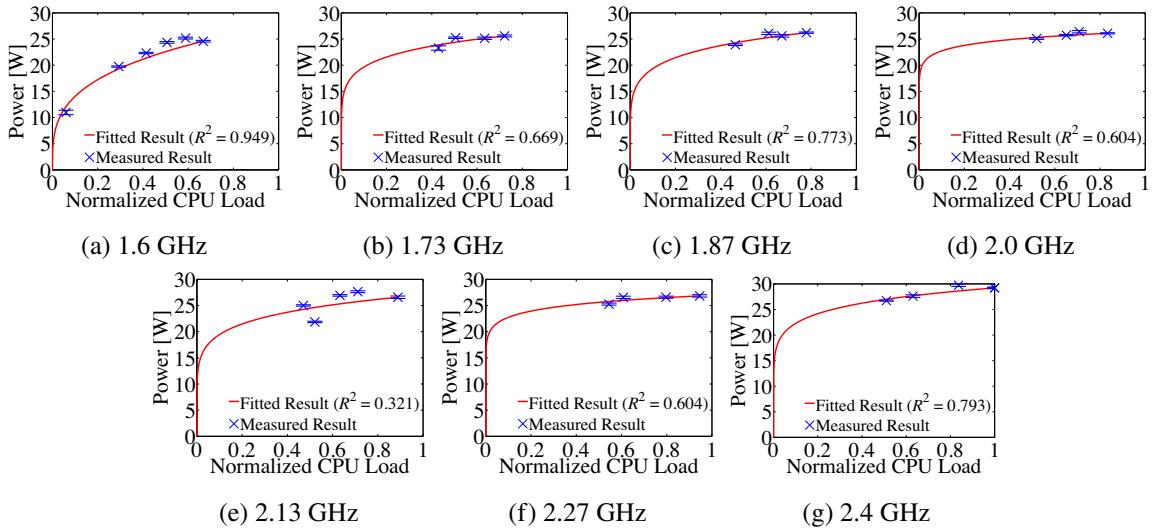

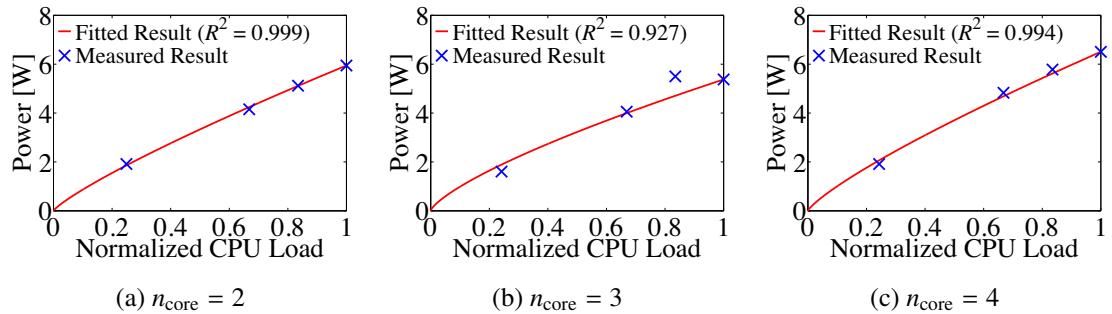

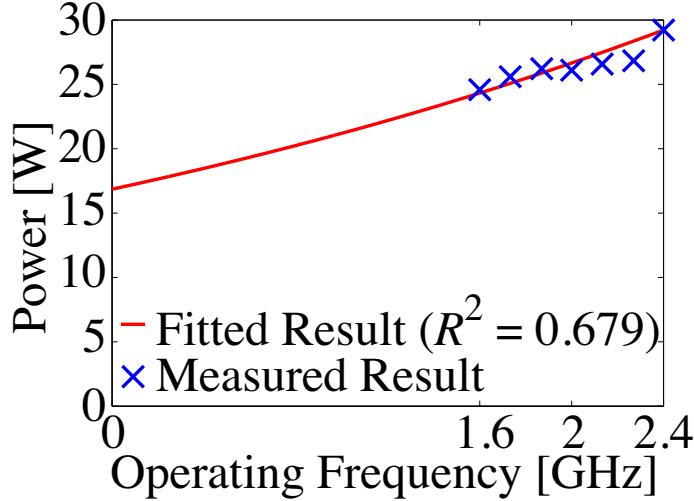

| 6.3.3    | Power Consumed by CPU Devices . . . . .                                    | 74        |

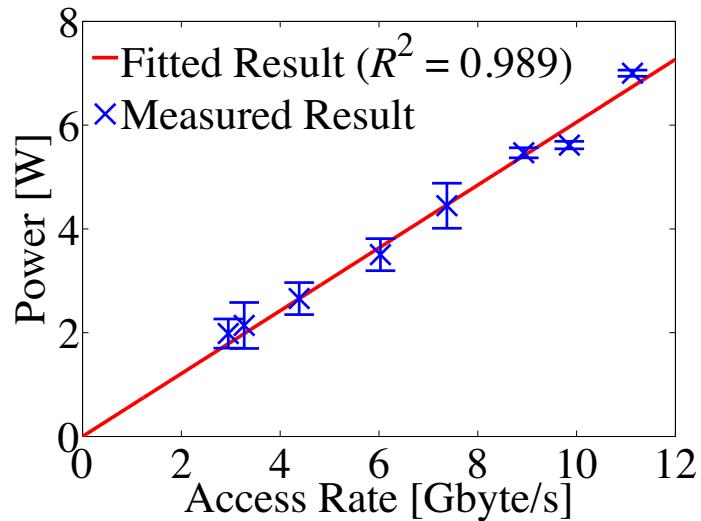

| 6.3.4    | Power Consumed by Memory Device . . . . .                                  | 83        |

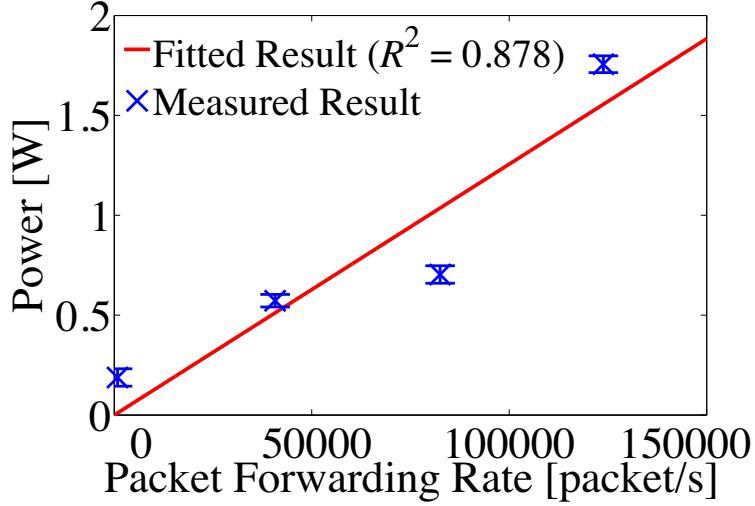

| 6.3.5    | Power Consumed by NIC . . . . .                                            | 84        |

| 6.4      | Packet Forwarding Analysis . . . . .                                       | 84        |

| 6.4.1    | Calculation Method for Naive Router . . . . .                              | 85        |

| 6.4.2    | IP Packet Forwarding Rate . . . . .                                        | 87        |

| 6.4.3    | Calculation Method for Optimized Router . . . . .                          | 87        |

|                     |                                                             |           |

|---------------------|-------------------------------------------------------------|-----------|

| 6.4.4               | Measured Numbers of CPU Cycles and Accesses Bytes . . . . . | 89        |

| 6.5                 | Case Study . . . . .                                        | 90        |

| 6.5.1               | Server Platform . . . . .                                   | 90        |

| 6.5.2               | Scenario . . . . .                                          | 90        |

| 6.5.3               | Power Reduction Analysis . . . . .                          | 91        |

| 6.5.4               | Lessons Learned . . . . .                                   | 92        |

| 6.6                 | Conclusion . . . . .                                        | 93        |

| <b>7</b>            | <b>Conclusion</b>                                           | <b>95</b> |

| <b>Bibliography</b> |                                                             | <b>99</b> |

# List of Tables

|     |                                                                                                                        |    |

|-----|------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | The consumption of CPU cycles and I/O bandwidth for processing one Interest or Data packet . . . . .                   | 24 |

| 3.2 | The number of CPU cycles spent in the instruction pipeline (Entire pipeline) . . . . .                                 | 25 |

| 3.3 | The number of CPU cycles spent in the instruction pipeline (Backend) . . . . .                                         | 25 |

| 3.4 | The number of CPU cycles spent in the instruction pipeline (Load Unit) . . . . .                                       | 26 |

| 3.5 | The number of retired load instructions . . . . .                                                                      | 26 |

| 3.6 | The number of CPU cycles against the number of threads . . . . .                                                       | 27 |

| 5.1 | CPU cycles spent for processing blocks of packet processing shown in Figs. 5.1 and 5.2                                 | 63 |

| 5.2 | CPU cycles spent for processing blocks of cache eviction and admission algorithms shown in Figs. 5.1 and 5.2 . . . . . | 63 |

| 6.1 | Parameters of $\phi_{\text{cpu}}(c_{\text{ndn}})$ for E5620 Processor . . . . .                                        | 79 |

| 6.2 | Parameters of $\phi_{\text{cpu}}(c_{\text{ndn}})$ for E3-1220 Processor . . . . .                                      | 79 |

| 6.3 | Parameters of $\phi_{\text{cpu}}(c_{\text{ndn}})$ for 9520 Processor . . . . .                                         | 80 |

# List of Figures

|     |                                                                                                                                                |    |

|-----|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 3.1 | Router hardware architecture . . . . .                                                                                                         | 17 |

| 3.2 | Hardware units on a CPU and four main stages of instruction pipeline . . . . .                                                                 | 21 |

| 3.3 | NDN software block diagram and analysis of computation time . . . . .                                                                          | 23 |

| 4.1 | Flow of Exact Matching Algorithm . . . . .                                                                                                     | 33 |

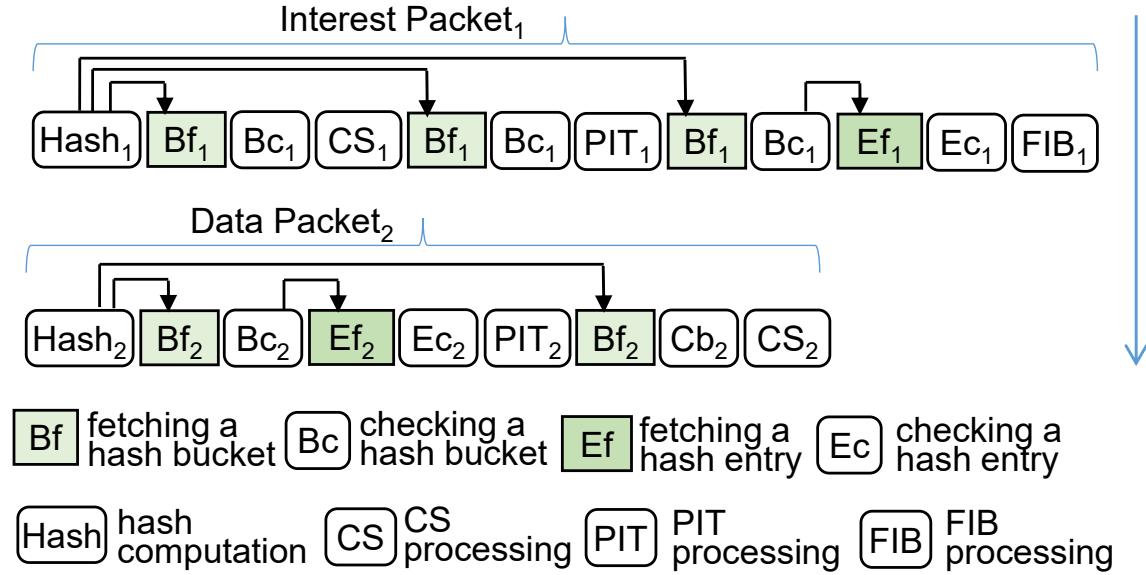

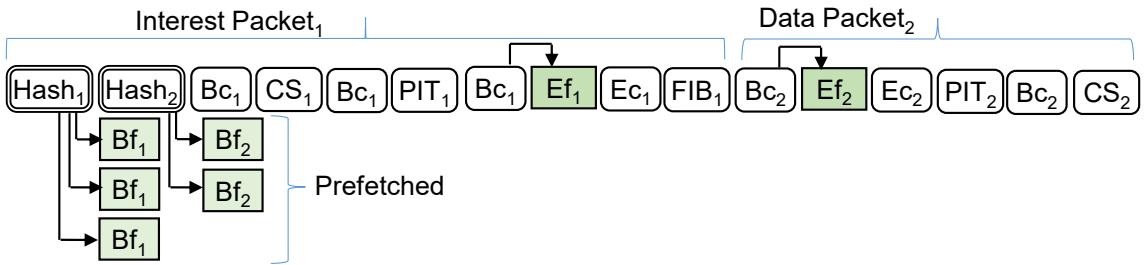

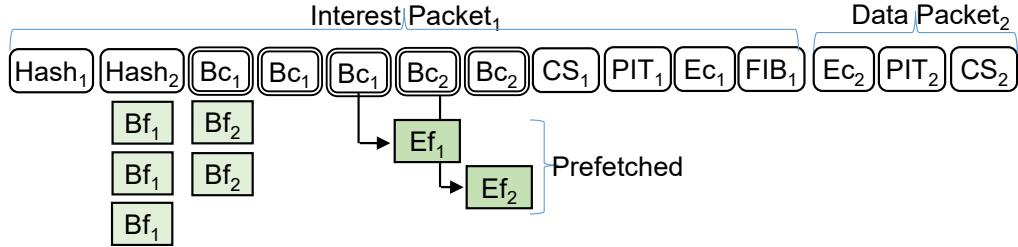

| 4.2 | Conventional packet processing flow . . . . .                                                                                                  | 40 |

| 4.3 | Prefetch-friendly packet processing flow with Pre-Hash Computation . . . . .                                                                   | 41 |

| 4.4 | Prefetch-friendly packet processing flow with Speculative Hash Table Lookup (and Pre-Hash Computation) . . . . .                               | 42 |

| 4.5 | The number of CPU cycles for processing one NDN packet in the single-threaded case                                                             | 44 |

| 4.6 | The number of CPU cycles for processing one NDN packet in the multi-threaded case (20 threads) . . . . .                                       | 45 |

| 4.7 | The forwarding speed against the number of threads . . . . .                                                                                   | 46 |

| 5.1 | Packet processing flow with cache eviction . . . . .                                                                                           | 51 |

| 5.2 | Packet processing flow with cache admission . . . . .                                                                                          | 52 |

| 5.3 | Schematic of data structures of Filter . . . . .                                                                                               | 55 |

| 5.4 | Effects of the length of the history queue $q$ and the threshold $\theta$ on insertion rates, and hit rates . . . . .                          | 65 |

| 5.5 | Comparisons of cache insertion rate for Filter and TinyLFU admissions . . . . .                                                                | 66 |

| 5.6 | Comparisons of cache hit rate for FIFO eviction, Random eviction, LFU eviction, ARC eviction, Filter admission and TinyLFU admission . . . . . | 67 |

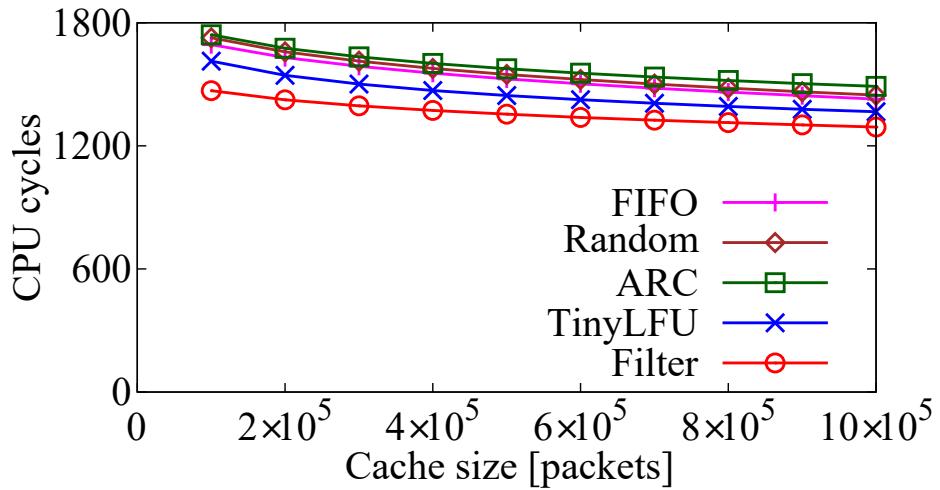

| 5.7 | Comparison of the average CPU cycles for NDN packet processing with Filter, TinyLFU, FIFO, Random and ARC under various cache sizes . . . . .  | 68 |

| 5.8 | Packet forwarding speeds of NDN routers with Filter, ARC and FIFO . . . . .                                                                    | 68 |

|      |                                                                                                                                                |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.1  | Power Consumed by CPU (E5620) Cores at Each P-state . . . . .                                                                                  | 81 |

| 6.2  | Power Consumed by CPU (E5620) in the Case of $n_{\text{core}} \geq 2$ . . . . .                                                                | 81 |

| 6.3  | Maximum Power Consumed by one CPU Core (E5620) in Each P-state . . . . .                                                                       | 82 |

| 6.4  | Power Consumption by CPU Device . . . . .                                                                                                      | 82 |

| 6.5  | Power Consumed by DDR3 Device . . . . .                                                                                                        | 85 |

| 6.6  | Power Consumed by NIC . . . . .                                                                                                                | 86 |

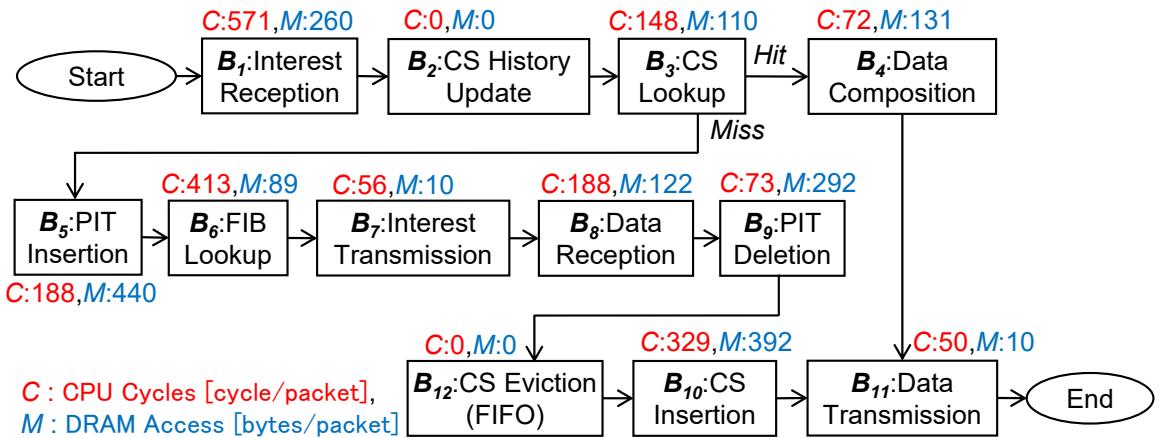

| 6.7  | Software block diagram of naive router (without prefetch algorithms and Filter) and the consumption of CPU cycles and DRAM accesses . . . . .  | 87 |

| 6.8  | Software block diagram of optimized router (with prefetch algorithms and Filter) and the consumption of CPU cycles and DRAM accesses . . . . . | 88 |

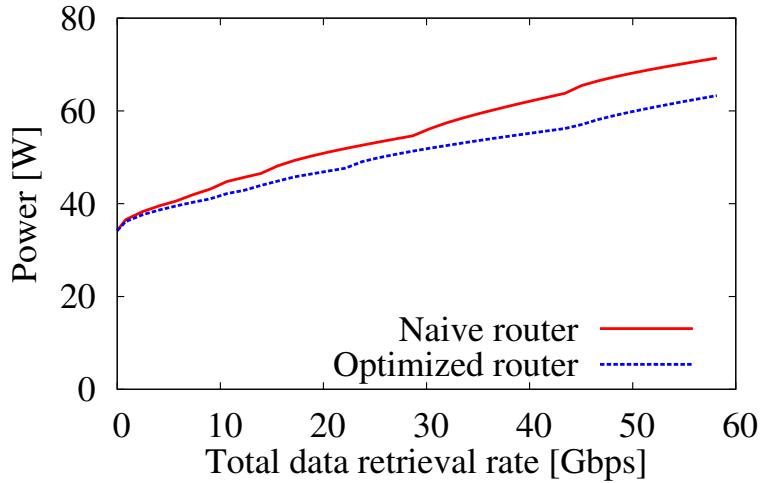

| 6.9  | The power consumption of the naive and the optimized routers . . . . .                                                                         | 92 |

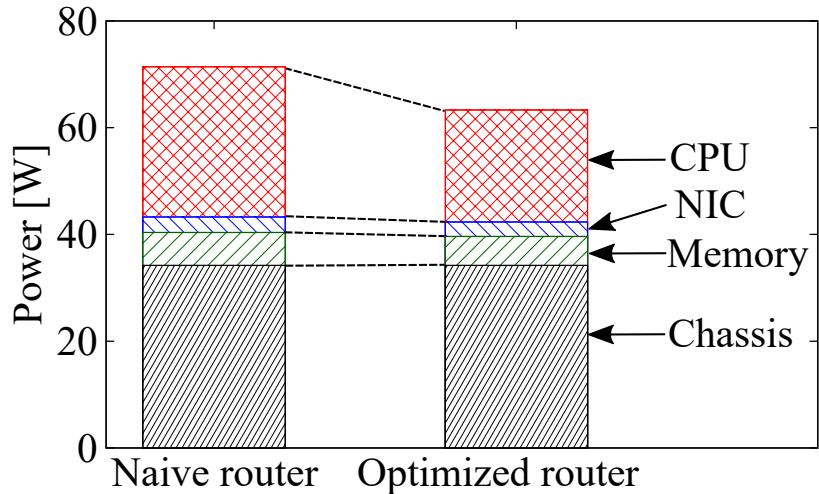

| 6.10 | The power consumption of individual devices of the naive and the optimized routers                                                             | 93 |

# Chapter 1

## Introduction

### 1.1 Background

A software router, which is built on a hardware platform based on a commercial off-the-shelf (COTS) computer, becomes feasible because of recent advances in multi-core CPUs and fast networking technologies for COTS computers. For notation simplicity, hereinafter, a COTS computer is simply referred to as a computer. Fast IP packet forwarding has been a research issue for a long time and hardware architecture designed based on a CPU device with fast memory devices like static random access memory (SRAM) devices [1, 2] shows that storing data structures for IP forwarding on SRAM devices enables fast IP forwarding for about  $5 \times 10^4$  IP prefixes. Inspired by the success, fast IP forwarding on software routers is being studied to keep up with the increasing number of IP prefixes in the Internet. Dobrescu et al. [3] exploit parallelism by leveraging multiple CPU cores or servers. The success of forwarding engines, which the studies assume to be built on current COTS computers, shows feasibility of fast packet forwarding of software routers without using special devices like general-purpose computing on graphics processing unit (GPGPU) devices [4]. As a consequence, compact data structures have become a research issue and many trie-based data structures have been designed. Among them, Degermark et al. [5] designed multi-bit trie data structures by replacing consecutive elements in a trie to a single element. Such efforts enable it to store an increasing number of IP prefixes, e.g.,  $7 \times 10^5$  prefixes [6], on the latest SRAM devices. In summary, high-speed IP forwarding on COTS computers is an almost solved research question because IP prefixes are able to be stored on fast SRAM devices.

Recently, studies on high-speed algorithms and compact data structures are being revisited due to the emergence of the new Internet architecture called Named Data Networking (NDN) [7].

High-speed NDN packet forwarding is not trivial compared to IP packet forwarding in terms of space and time complexity because name-based forwarding and packet caching, which are key components of NDN, need much larger data structures than IP forwarding. The number of names in the NDN-based Internet is believed to be at least the same that of unique domain names and the number as of December 2017 is about  $2.1 \times 10^8$  [8]. Such a large number of name prefixes needs large memory space and heavy computation. In addition to name-based forwarding, caching needs extra data structures for managing packets in a router's cache and computation for it. Handling variable-length and human-readable names and stateful forwarding also incur heavy computation.

Heavy name-based forwarding and caching result in poor performance of NDN forwarding on computers. The goal of this thesis is to identify what a high-speed NDN forwarding engine on a computer is supposed to be.

## 1.2 Approaches

In this thesis, the author identifies bottlenecks for high speed forwarding by carefully analyzing the existing NDN forwarding engine in terms of hardware and software constraints. First of all, the author carefully analyzes what is the most significant constraint among the following three ones: the computation capability of a CPU device, bandwidths of Dynamic Random Access Memory (DRAM) devices and bandwidths of Input/Output (I/O) devices. This analysis reveals that the bottleneck is not the memory bandwidth but the number of CPU cycles, and hence reducing the number of CPU cycles is a key to high speed NDN forwarding.

In order to know bottlenecks for CPU cycle consumption, the author carefully analyzes how NDN packet processing consumes CPU cycles at the level of CPU pipelines and instructions and identifies two bottlenecks. The first bottleneck is the pipeline stall. More precisely, the stall to wait data to be fetched from the DRAM device is the most significant bottleneck among all of pipeline stalls like the instruction fetch stall and the instruction execution stall. The above analysis also reveals that the stall due to data fetches is caused by accessing forwarding tables, which include tables for both name-based forwarding and caching, and they are placed on the slow DRAM device. This implies that eliminating the DRAM access latency due to forwarding table accesses is a key to high-speed NDN forwarding.

The second bottleneck is redundant computation of cache eviction. From the perspective of software constraints, the author analyzes how each function of NDN packet processing consumes CPU cycles and found the two facts related to wasteful cache eviction. The first fact is that the packet

processing flow in the case of a cache miss consumes more CPU cycles than that in the case of a cache hit because a router consumes CPU cycles for forwarding an Interest packet<sup>1</sup>, which would not be needed if the Interest packet hit the cache. The second fact is that the function of cache eviction and insertion for Data packets consumes many CPU cycles among functions constituting the packet processing flow in the case of a cache miss. The above two facts imply that cache algorithms need to increase cache hit rate without incurring computation overheads for high-speed NDN forwarding.

According to the above two implications, in this thesis, the author addresses to eliminate the DRAM access latency due to forwarding table accesses and to realize cache algorithm with fast computation and high cache hit rate.

### 1.2.1 Elimination of DRAM Access Latency

The first issue is how to eliminate the DRAM access latency due to forwarding table accesses. Significant efforts have been directed toward compact data structures and algorithms of name-based forwarding [9–12] to eliminate the DRAM access latency. A research issue of special concern is designing compact data structures and some studies show that trie-based data structures can be designed to be so compact that can be stored on SRAM devices by using a bit as a component of a trie [12]. Although the assumption that data structures are placed on fast memory devices is reasonable for NDN hardware routers, it is not reasonable for NDN software routers. Unlike on hardware routers, data cannot be pinned at CPU caches on computers since eviction and replacement in CPU caches are governed by their CPUs rather than user-space programs and operating systems.

The argument in the last paragraph implies that hiding DRAM access latency is a vital key to high speed NDN packet forwarding rather than compactness of the data structures. This is because the number of DRAM accesses never gets zero even though the sophisticated data structure and algorithm are adopted. Latest CPUs support *instruction and data prefetch*, which allows instructions and data to be fetched to CPU caches in advance of actual use. With the prefetch mechanism, NDN software routers can hide the large DRAM access latency. In order to exploit the prefetch mechanism, the address of data to be prefetched must be known in advance. In the case of a trie-based data structure, it is hard to hide the DRAM access latency with the prefetch mechanism because where to access cannot be estimated in advance of its access. More precisely, since a trie is searched by traversing vertices from its root, the address of the next vertex to be traversed cannot be estimated before its parent is fetched. In contrast, in the case of a hash table-based data structure, to hide

---

<sup>1</sup>Interest and Data packets are request and response packets in NDN, respectively. Interest packets transfer requests of consumer and Data packets do the corresponding data objects.

the DRAM access latency is easier than in the case of a trie-based one since access patterns of the hash table are predictable if hashes of keys are available in advance. Thus, a hash table-based data structure is more promising than a trie-based data structure.

In this thesis, the author addresses to hide the DRAM access latency as follows: First, the author carefully compares existing data structures and algorithms both for name-based forwarding and caching from the viewpoint of the ease of hiding DRAM access latency and chooses a hash table-based algorithm and a frequency-based cache admission algorithm for name-based forwarding and caching, respectively. Second, the author designs a prefetch algorithm for hiding most of the DRAM access latency for both name-based forwarding and caching. The prefetch algorithm reorders instruction executions for packets so that the DRAM access latency due to data fetches is successfully hidden by execution time of instructions independent of the data fetches. Finally, the author implements a proof-of-concept prototype and empirically proves that forwarding speed with the prefetch algorithm increases linearly as the number of CPU cores increases, whereas that without the prefetch algorithm does not increase so. A detailed analysis at the level of CPU pipelines and instructions reveal that most DRAM access latency are successfully hidden by the prefetch algorithm.

### 1.2.2 Fast Cache Algorithm with High Cache Hit Rate

The second issue is how to design fast cache algorithm with high cache hit rate. As the first step, the author carefully analyzes how two types of cache algorithms, i.e., cache eviction and admission algorithms, consumes CPU cycles in NDN packet processing and identifies the two obstacles of fast cache algorithm. First, cache insertion of a Data packet is relatively time-consuming among function blocks which are executed when a cache miss occurs. It means that insertion of unpopular Data packets which are not hit later wastes many CPU cycles. Second, sophisticated cache eviction algorithms like Adaptive Replacement Cache (ARC) [13] incur computational overheads for choosing a victim Data packet sophisticatedly, which will be evicted from the cache.

This implies that cache algorithms need to increase cache hit rate and reduce unpopular Data packet insertion rate simultaneously without incurring computation overheads for high-speed NDN software routers. The author proposes cache admission as a better candidate than cache eviction according to two reasons: First, cache admission obviously resolves the first obstacle because only the selected Data packets are inserted into the cache. Second, computation of cache admission is lighter than that of cache eviction to achieve high cache hit rate. The heavy computation of cache eviction comes from the fact that a cache eviction algorithm decides exactly one Data packet evicted from the cache by maintaining an eviction priority queue, where all the Data packets are sorted

according to their eviction priority values in the cache according to recency or frequency. On the other hand, a cache admission algorithm performs lighter computation such that it only decides whether an incoming Data packet should be inserted into the cache or not and hence it does not need to maintain the eviction priority queue.

In this thesis, the author develops a light-weight cache admission algorithm, *Filter*, and shows an example case that cache admission is better than cache eviction for an NDN router. *Filter* exploits frequency, which is the number of Interest packets for a Data packet, as a history of requests to Data packets. The average computation time handling one Interest packet is about a few tens of CPU cycles. Nevertheless, *Filter* with FIFO eviction achieves high cache hit rate similar to that of ARC eviction with the above small computation. The author implements a proof-of-concept prototype of an NDN software router with *Filter* and empirically evaluates the overall packet forwarding speed of an NDN router with *Filter* based on its prototype implementation.

### **1.2.3 Power Efficiency Due to CPU Cycle Reduction**

The above two approaches in Sections 1.2.1 and 1.2.2 address how to reduce the number of CPU cycles consumed by NDN packet processing in order to improve forwarding speed of NDN software routers. The author further addresses a positive effect of CPU cycle reduction from a different angle and to answer the question whether CPU cycle reduction contributes to improving power efficiency of NDN software routers. The author sheds light on power efficiency, which is also a crucial design issue of NDN routers as being addressed by many previous studies [14–17].

The author empirically models how NDN packet processing consumes power of hardware devices constituting an NDN software router on a computer. This model reveals that the CPU device consumes much power and that its consumed power is in proportion to its load, i.e., the number of consumed CPU cycles. This means that reducing the number of CPU cycles consumed by NDN packet processing contributes to power efficiency of an NDN software router. Based on the model, the author conducts a case study of analyzing power consumption of naive NDN software routers and those which use the proposed techniques. The case study reveals that reduction of the number of CPU cycles due to the proposed techniques contributes to power reduction of modern computers, which are energy proportional to their load.

## 1.3 Contributions

The main contributions of this thesis are summarized as follows: First, as far as the author knows, this is the first study that summarizes observations found in existing studies to build high-speed NDN routers on computers and compiles the observations into a design guideline. According to the guideline, the author reveals that a hash table-based algorithm and a frequency-based cache admission algorithm are suitable for name-based forwarding and caching, respectively. Second, the author designs a prefetch algorithm for hiding most of the DRAM access latency for both name-based forwarding and caching. The prefetch algorithm reorders instruction executions for a pair of packets so that the DRAM access latency due to data fetches is successfully hidden by execution time of instructions independent of the data fetches. Third, the author carefully designs a lightweight frequency-based cache admission algorithm, Filter, on the basis of the results of the empirical measurement of an NDN software platform. As the results of the careful design, Filter consumes a few tens of CPU cycles in average with providing as high cache hit rate as ARC. Fourth, the author implements a proof-of-concept prototype of an NDN software router with the proposed prefetch algorithm and the Filter admission algorithm and empirically proves that the router realizes a nearly optimal forwarding speed. Fourth, the author implements a proof-of-concept prototype of an NDN software router with the proposed two techniques and empirically proves that forwarding speed with the two techniques increases linearly as the number of CPU cores increases, whereas that without the two techniques does not increase linearly. A detailed analysis at the level of CPU pipelines and instructions reveal that most DRAM access latency are successfully hidden by the prefetch algorithm and that the number of CPU cycles of NDN packet processing is reduced by the Filter admission algorithm. Fifth, the author sheds light on power efficiency of NDN software routers as a positive effect of CPU cycle reduction at the different view point from forwarding speed improvement. By modeling how NDN packet processing consumes power of hardware devices on an NDN software router, the author reveals that reducing the number of CPU cycles for high speed NDN forwarding contributes to power consumption reduction of an NDN software router.

## 1.4 Outline

The rest of this thesis is organized as follows. Chapter 2 summarizes related work. Chapter 3 identifies true bottlenecks for high speed forwarding based on the instruction level analysis after explaining a state-of-the-art software NDN implementation used for the analysis. Chapter 4 designs

a prefetch algorithm after choosing data structures and algorithms for name-based packet forwarding and caching among the existing algorithms from the view point of the ease of hiding DRAM access latency. Chapter 5 proposes an NDN packet forwarding scheme with the cache admission based on Filter after introducing a problem of wasteful caching computation. Chapter 6 models how hardware devices of NDN software routers consume power and then reveals that the CPU cycle reduction due to prefetch and Filter mechanisms contribute to reducing power consumed by NDN software routers. Finally, Chapter 7 concludes this thesis.

# Chapter 2

## Related Work

The thesis is compared with the four series of studies: name-based forwarding, caching, software packet processing, and power efficiency of routers.

### 2.1 Name-based Forwarding

Perino and Varvello investigate Content-Centric Networking (CCN) software in detail and claim that CCN deployment is feasible at ISP scale, whereas today's technology is not yet ready to support an Internet scale deployment of NDN/CCN [18]. To achieve high-speed NDN packet processing, many researches attack issues of heavy NDN functions, focusing on heavy name-based forwarding and caching.

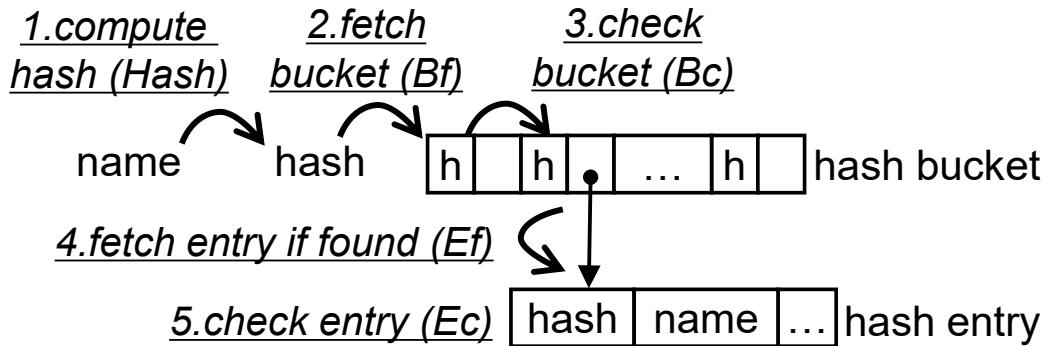

To cope with the issue of heavy name-based forwarding, previous studies address efficient data structures of name-based forwarding and its efficient longest prefix match algorithms. Regarding efficient data structures, the author has enough design choices such as *Bloom filter-based*, *trie-based*, and *hash table-based* data structures. Dai et al. [9] propose a counting bloom filter-based data structure with the unified index of all of NDN forwarding tables, i.e., CS, PIT and FIB, so that the data structure is stored in the SRAM device. Song et al proposes a binary patricia trie using a bit as a component of a trie so that all of rules of name-based FIB is stored in the compact data structure [11]. So et al. propose a hash table with fast collision-resistant hash computation and compact arrays in order to reduce the number of DRAM accesses. Bloom filter-based and trie-based data structures address compactness of data structures of name-based forwarding, whereas the compactness is not suitable for an NDN software router because the number of DRAM accesses never gets zero on the NDN software router. From the ease of hiding DRAM access latency, the author chooses a

hash table-based data structure [10], whereas its naive design incurs a few of unhidden data fetches, which are the root cause of forwarding speed degradation. In this thesis, the author designs prefetch techniques so that the DRAM access latency due to such unhidden data fetches is successfully hidden.

Regarding efficient longest prefix match algorithms, Yuan and Crowley propose a longest prefix matching algorithm based on binary search of hash tables, which reduces the worst case computation complexity [12]. So et al. design an efficient FIB lookup algorithm that provides good average and worst case FIB lookup time complexity. Fukushima et al. design a protocol that avoids redundant longest prefix matching by exploiting neighboring router's cooperation [19]. Although these studies successfully reduce the average time-complexity of longest prefix matching, these incur unhidden data fetches, of which latency is difficult to be hidden. From the ease of hiding DRAM access latency, the author proposes to use a simple longest-first search algorithm, as used in [20].

## 2.2 Caching

In contrast to name-based forwarding, only a few studies focus on fast computation of caching [21,22]. These studies address the large access latency to the secondary memory device like the Solid State Drive (SSD) storage, which is used for the packet cache of the NDN router. So et al. [21] propose to explicitly separate CPU cores for accessing the slow SSD storage and those for fast name-based forwarding to mitigate forwarding speed degradation of an entire NDN router. Mansilha et al. propose a caching algorithm which hides insufficient memory bandwidth between the main memory device and the secondary memory device used for a per-packet caching [22]. Both approaches use one or more CPU cores exclusively to compensate the large access latency to SSDs and thus it requires heavy computation with multiple CPU cores.

In this thesis, the author proposes to use cache admission according to the observation that handling Data packets of unpopular content is wasteful. At first, cache admission algorithms [23–25] are designed by leveraging cooperation of caches of routers in a network so that the same Data packet is not likely to be inserted into different caches. ProbCache [23] and Betweenness [25] insert Data packets equally into caches on a delivery path, whereas Leave Copy Down (LCD) [24] focuses on off-path caching. Nevertheless, the author uses cache admission algorithms without such cooperation, i.e., cache admission algorithms working independently on individual routers, being inspired by the observation found by Sun et al. [26] that the LFU-based cache algorithms without such cooperative cache admission achieves higher traffic reduction in a whole network as well as sufficiently similar cache hit rate compared with the cache admission algorithms with cooperation. A cache admission

algorithm without such cooperation is simply referred to as a cache admission algorithm, hereafter.

Precisely, the author adopts a frequency-based cache admission algorithm which is executed independently from the other caches. TinyLFU [27] is a frequency-based cache admission algorithm and inserts Data packets which are received often recently into a cache. Although Filter of this thesis is also a frequency-based cache admission, Filter focuses on fast computation of cache admission itself compared to the TinyLFU, as the author will discuss later in Section 5.2.

## 2.3 Software Packet Processing

Prototypes of NDN software routers have been developed. Kirchner et al. [28] have implemented their NDN software router, named Augustus, in two different ways: a standalone monolithic forwarding engine based on the DPDK framework [29] and a modular one based on the Click framework. Though the forwarding speed of Augustus is very high, it does not approach the potential forwarding speed realized by computers. Hence, analyzing the bottlenecks of NDN software routers remains an issue.

How to exploit CPU caches is an important issue to realize the fast packet processing. Vector packet processing (VPP) [30] enhances packet processing speed by processing a vector of packets at once rather than processing each of them individually. The key idea behind VPP is to reduce the processing time by increasing the hit probability at the instruction caches. However, in the case of the NDN software router, the instruction cache misses, i.e., the instruction pipeline stalls at the frontend stage, do not occupy a significant proportion of the overall pipeline stalls. Furthermore, unlike VPP, approaches of this thesis focus on hiding the DRAM access latency, assuming that data cannot be pinned on the caches.

Fast packet processing is also a hot research topic in the area of networked applications. Li et al. [31] developed a multi-threaded in-memory key-value store that exploits DPDK and RSS. They have revealed that the number of cache misses at the L3 cache increases as the number of threads increases. However, NDN software implementation designed in this thesis scales up to 20 threads without increasing the number of L3 cache misses.

This thesis addresses the two research issues for high-speed forwarding of NDN software routers. First, high speed hash table handling is also an important issue in hash table-based systems such as key-value store systems [32] and OpenFlow switches [33] as well as high speed NDN software routers. These studies focus on fast mutual exclusion for read-intensive workloads because hash table lookups dominate most of operations, whereas this thesis avoids such mutual exclusion by having threads not access the same hash table at the same time. On the contrary, hiding long DRAM access

latency in hash table handling is important for the both hash table-based systems. The author believes that the proposed prefetch technique for hiding DRAM access latency is applicable to the other hash table based systems. Second, a lightweight cache admission algorithm, filter, proposed in Section 5, is used together with cash algorithms of the above systems such as key-value store [32] and reverse proxy [34]. The studies focus on reducing meta data structures which are stored at caches because such data structures are larger than data pieces themselves, e.g., 64 bytes data pieces, whereas the filter focuses on reducing the number of data pieces stored at caches.

## 2.4 Hardware Packet Processing

Due to the trend that the integration degree of transistors has not increased on the CPU device recently [35], hardware packet processing with the ASIC-based chip becomes a hot research topic [36, 37]. A programmable switch hardware with the ASIC-based chip is being released by Barefoot Networks [38] and the switch hardware realizes both high processing speed by 6.4 Tbps and the programmability that various types of network applications like IP router [36] and network load balancer [37] can be implemented. The switch hardware typically implements packet processing as on-chip operations where all of data structures are pinned on SRAM or TCAM devices and packets are processed on ASICs using the data structures [36]. Most of network applications using the switch hardware sheds light on compact data structures to place them on on-chip SRAM or TCAM devices [37].

The programmable switch hardware is considered to be a promising platform for future NDN routers requiring about 1 Tbps forwarding speed [39]. However, many issues should be resolved so that NDN packet processing is implemented on the switch hardware. Among them, a large amount of NDN data structures raises an implementation issue since all of NDN data structures cannot be placed on on-chip TCAM and SRAM devices, as discussed in Section 1.1. This means that a part of NDN data structures must be placed on the off-chip DRAM device of the switch hardware like [36] or the remote DRAM device of the COTS computer connected to the switch hardware like [40]. In such the cases, the ASICs need to fetch data pieces of the data structures from the DRAM device to on-chip SRAM or TCAM devices before using them. Thus, the latency to fetch data from the DRAM device becomes a issue of high-speed NDN packet processing on the programmable switch hardware in similar to the COTS computer hardware. The author believes that the data prefetch techniques proposed in Section 4.3 contribute to hiding such the latency on the programmable switch hardware.

## 2.5 Power Efficiency of Routers

Many studies which address power efficiency of NDN routers and networks focus on the caching function because its traffic reduction would contribute to energy savings. Lee et al. [14, 15] investigated how much power is reduced by reducing hop counts to obtain contents. In their simulations, they used a power consumption model which only considers the power consumed by lower layer packet forwarding devices. Choi et al. [16] show that the power consumed by memory devices used for caching and for the forwarding processes is not insignificant. Imai et al. [17] proposed a method of determining capacities of NDN routers' memory devices so that the power they consume is minimized.

Many power consumption models focus on the power consumed by memory devices because they are power-hungry even while in idle state. In contrast, the author focuses on the power consumed by the CPU device for packet forwarding, taking into account the trend towards low power consumption by memory devices [41, 42].

Bolla et al. [43, 44] model the power consumed by a CPU device with power optimization techniques by considering two power management states. Although the study of this thesis is partially motivated by [43, 44], in this thesis, the author models multiple CPU devices (compared to only one in [43, 44]) and empirically validates the developed model by applying it to two different commercial CPU devices. Finally, the author takes into account all elements of the router (*e.g.*, chassis, memory devices and CPU), in contrast to [43, 44], where only the CPU is taken into account.

## Chapter 3

# Microarchitectural Bottleneck Analysis of an NDN Software Router

As the first step to achieve a high-speed NDN software router, in this chapter, the author identifies true bottlenecks of NDN packet forwarding on a computer from the perspectives of hardware and software constraints as described below: First, the author considers what is the most significant constraint among the constraints on the computation capability of a CPU device, bandwidths of DRAM devices and bandwidths of Input/Output (I/O) devices by analyzing how a current state-of-the art NDN software router implementation behaves on a computer. From the analysis, the author reveals that computation on a CPU is the most significant constraint. Second, the author analyzes how individual hardware components of the CPU spend time for processing NDN packets at the level of instructions and instruction pipelines. By carefully analyzing the behavior at the level of CPU pipelines and instructions, the author identifies two types of bottlenecks of NDN packet forwarding. The first bottleneck is the unhidden DRAM access latency due to forwarding table accesses and the other one is the number of instructions executed for NDN packet processing. Third, the author analyzes how each of NDN functions consumes CPU cycles for processing a packet in order to identify the cause of the large number of executed instructions. The analysis reveals that packet processing flow in the case of a cache miss consumes many CPU cycles and that among functions constituting the packet processing flow in the case of a cache miss, a function of cache eviction and insertion consumes many CPU cycles. Finally, the author compiles the above analysis results into two design rationales for high-speed NDN packet forwarding. The first rationale is that data structures and algorithms for NDN packet processing should be designed so that the DRAM access

latency is hidden. The second rationale is that cache algorithm should be designed so that high cache hit rate is achieved with fast computation.

The rest of this Chapter is organized as follows. The author explains NDN packet forwarding behavior and a state-of-the-art software NDN implementation used for the bottleneck analysis in Section 3.1. In Section 3.2, the author identifies bottlenecks for high speed forwarding based on the instruction level analysis from the perspective of hardware constraints. In Section 3.3, the author identifies bottlenecks of computation time of NDN packet processing from the perspective of software constraints. Based on analysis results, the author finally provides design rationales for a high speed NDN router in Section 3.4.

## 3.1 Hardware and Software Platforms

After describing a hardware platform, this section summarizes software design practices to exploit the parallel computation capabilities of CPU cores, which are essential to high-speed NDN packet forwarding.

### 3.1.1 Hardware Platform

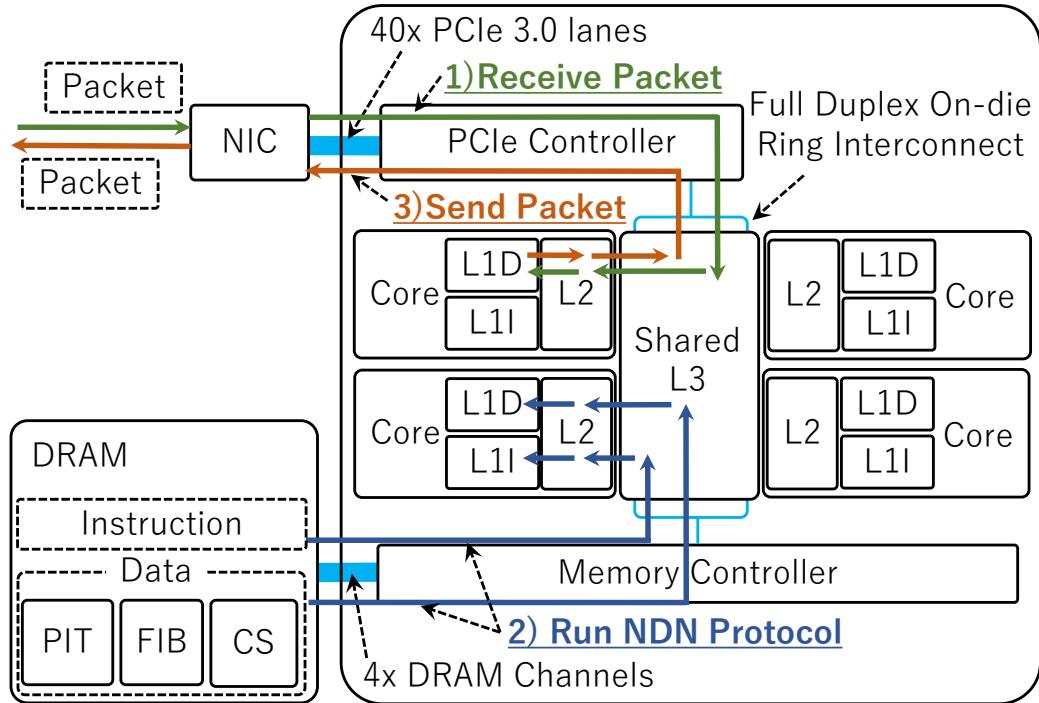

A reference hardware platform is illustrated in Fig. 3.1. It is based on Intel Xeon family CPUs [45], double data rate fourth-generation synchronous (DDR4) DRAM devices, and latest network interface cards (NICs).

**CPU Cores and Caches** Each CPU has several CPU cores, and they are interconnected with one or two full-duplex on-die ring interconnects. The CPU has L1 instruction, L1 data, L2, and L3 caches. For the sake of notation simplicity, L1 instruction and L1 data caches are referred to as L1I and L1D caches, respectively. In contrast to the L3 cache, which is shared with all CPU cores, each of the CPU cores has exclusive L2, L1I, and L1D caches.

**Data Transfer between CPU and NIC/DRAM** The DRAM and NICs are connected with the CPU via a memory controller and a PCI express (PCIe) 3.0 controller on its die. PCIe devices, such as network interface cards (NICs), are connected via the PCIe controller. The CPUs and NICs support the Intel Data Direct I/O (DDIO) technology [46], which allows data to be transferred directly between NICs and the L3 cache without passing through the DRAM device. The data transfer rate via the PCIe controller is 96 Gbytes/s and data is prefetched at any time after all packets in the NIC

Figure 3.1: Router hardware architecture

are transferred to the L3 cache in a batch. The memory controller supports DDR4 DRAM devices and has four DDR4 DRAM channels. The allocation rule of memory requests from the memory controller to the DRAM channels is determined by the memory management library provided by DPDK [29]. Data, including NDN tables and instructions, is placed on the DRAM device and it is fetched via the memory controller. The access latency to the DRAM device is one or more orders of magnitude greater than that to CPU caches. To hide the DRAM access latency, the CPU has two types of prefetch mechanisms: *hardware* and *software prefetch mechanisms*. The CPU automatically fetches instructions and data with the hardware prefetch mechanism if their accesses can be predicted in advance. In addition, data can be speculatively fetched to the caches using the software prefetch mechanism, which is controlled by the software with the PREFETCH instruction [47]. How to issue the PREFETCH instruction is vital to hiding the large DRAM access latency.

### 3.1.2 NDN Packet Forwarding

The packet forwarding flow of NDN on the above router hardware is illustrated in Fig. 3.1. When a packet arrives at a NIC, it is directly transferred from the NIC to the L3 cache. Then, the packet is

fetched from the L3 cache to a CPU core and NDN protocol processing is performed for the packet. Finally, the packet is transmitted from the L3 cache to a NIC. To fully exploit the computation capabilities made possible by many CPU cores, received packets are processed by several threads in parallel. the author briefly describes NDN in the following paragraphs.

NDN realizes request/response communication of a named object using two types of packets: an Interest packet and a Data packet, which correspond to a request packet and a response packet, respectively. Both Interest and Data packets have a name which uniquely identifies a piece of an object and only the Data packet has the piece of an object.

NDN protocol processing mainly consists of Content Store (CS), Pending Interest Table (PIT) and Forwarding Information Base (FIB). CS is a cache memory<sup>1</sup> which stores previously processed Data packets. FIB is a forwarding table which stores outgoing interfaces for Interest packets. PIT is a table which stores arrival interfaces of pending Interest packets and it is used as a forwarding table for Data packets. An NDN router realizes NDN protocol processing by using the above three components as follows: When an Interest packet arrives, the router looks up a piece of an object from its exact name in the CS. If the router finds the piece, it sends back a Data packet with the piece to the arrival interface of the Interest packet. Otherwise, the router inserts the arrival interface with the name of the Interest packet into the PIT. Finally, the router looks up the outgoing interface having the longest name prefix of the name of the Interest packet and sends the Interest packet to the interface. When a Data packet arrives, the router looks up its outgoing interface from its exact name in the PIT and deletes it from the PIT. Then, the router inserts the Data packet into the CS and evict the most unpopular Data packet from the CS according to cache algorithms, i.e., cache eviction and admission. Finally, the router sends the Data packet to the outgoing interface.

### 3.1.3 Practices to Exploit Parallel Computation

Exploiting the parallel computation capabilities of CPU cores is the key to high-speed NDN packet forwarding, which is more complex than IP packet forwarding. To exploit capabilities of computers, the software must eliminate obstacles as follows: 1) *mutual exclusion*, 2) *hardware interrupts*, 3) *instruction pipeline stalls*, and 4) *time complexity*. Obstacles due to mutual exclusion 1) and hardware interrupts 2) have already been resolved by existing studies. The author summarizes the design practices for the first two obstacles in the rest of the section, and then addresses the last two obstacles in the rest of this thesis. These are the main research issues of this thesis.

---

<sup>1</sup>To avoid confusion, hereinafter, the author refers to caches on a CPU and an NDN router as *cache*, which is the only SRAM device in a computer, and *content store (CS)*, respectively.

## Eliminating Mutual Exclusion

When an area on memory devices is locked with mutual exclusion, threads waiting for the area to become free is being idle. In a similar way, hardware interrupts and instruction pipeline stalls also make threads being idle. One way to compensate for such idle time is to increase the concurrency, i.e., the number of threads, so that other threads can use idle computing units. For instance, a prototype NDN software router, named Augustus [28], uses Hyper-Threading Technology. However, this approach may introduce many context switches, and the context switches also results in significant overheads. In this sense, the author suggests that the number of threads should be kept equal to or less than the number of CPU cores.

To utilize computing capabilities derived from multi-core CPUs, multi-threading strategies must be designed carefully. The author chooses the strategy of assigning one thread to one NDN packet rather than assigning a sequence of threads to one packet as a pipeline to prevent the pipeline from being disturbed by I/O waits. The author focuses on two important issues for the multi-threading strategies: elimination of mutual exclusion and balancing the workloads for processing packets equally across all threads. To resolve two issues, the author adapts exclusive NDN tables and packet-level sharding. Mutual exclusion for any shared data would result in serious performance degradation.

To eliminate mutual exclusion, each thread exclusively has its own FIB, PIT, and CS, thereby preventing it from accessing the tables of the other threads, as the existing prototypes of NDN software routers adopt [10, 28].

Arriving packets are forwarded to threads according to their names by using receiver side scaling (RSS), which allows NICs to send different packets to different queues to distribute the workloads among CPUs. As Saino et al. [48] revealed in their investigation, packet-level sharding, which distributes Data packets to CSs based on the result of a hash function computed on the names of the packets, distributes them equally to each CS. Based on their results, the author assumes in this thesis that the software distributes packets equally to each thread according to the hashes of their names at the NICs by using RSS. Please note that partial name matching of Interest and Data names is not supported in this thesis because the sharding mechanism using RSS requires that a Data packet is explicitly requested by its exact name.

### Eliminating Hardware Interrupts

To eliminate hardware interrupts, the author adopts the DPDK user-space driver [29], which allows user-space software to bypass the protocol stacks of operating systems and provides a way to transfer data directly from NICs to the software.

### Remaining Issues

The remaining issues are twofold: one is to eliminate instruction pipeline stalls caused by NDN packet processing and the other is to design NDN packet processing itself to optimize its time complexity. To identify the main cause of instruction pipeline stalls, the author conduct a bottleneck analysis at the level of the instruction pipeline in Sec. 3.2. To address time complexity, the author identifies the root cause of such high time complexity in Sec. 3.3.

## 3.2 Microarchitectural Hardware Bottleneck Analysis

To identify a true bottleneck of NDN packet forwarding on a computer, the author conducts a *microarchitectural hardware analysis*, which analyzes how individual hardware components of the CPU spend time for processing NDN packets at the level of instructions and instruction pipelines, with the method described in the previous section.

### 3.2.1 Bottleneck Analysis Method

This subsection summarizes the microarchitectural analysis method.

#### Analysis of Packet Forwarding Flow

First, the author identifies which of the factors, computation time or I/O bandwidth, is the bottleneck limiting the maximum packet forwarding rate by defining how these two factors limit the maximum rate.

The packet forwarding rate,  $\lambda$  packet/s, is defined as the number of packets, including Interest and Data packets, forwarded per second. When the packet forwarding rate is  $\lambda$ , the consumed CPU cycles are derived as  $\lambda C$ , where  $C$  is the average number of CPU cycles consumed to process a packet. Assuming the load for processing packets is equally assigned to  $N$  CPU cores operating at a frequency of  $F$  Hz, the maximum packet forwarding rate,  $\lambda_{\max}$ , must satisfy  $\lambda_{\max} \leq NF/C$ . In the same way, the average number of bytes read from and written to DRAM devices for processing a

Figure 3.2: Hardware units on a CPU and four main stages of instruction pipeline

packet is expressed as  $M$  and it can be modeled similarly to the CPU cycles. The maximum packet forwarding rate  $\lambda_{\max}$  satisfy  $\lambda_{\max} \leq B/M$ , where  $B$  is the bandwidth of DRAM channels, thereby  $\lambda_{\max}$  satisfying

$$\lambda_{\max} \leq \min(NF/C, B/M). \quad (3.1)$$

If the maximum packet forwarding rate is  $NF/C$ , computation time is a bottleneck. Otherwise I/O bandwidth is a bottleneck.

### Analysis of Pipeline Stalls

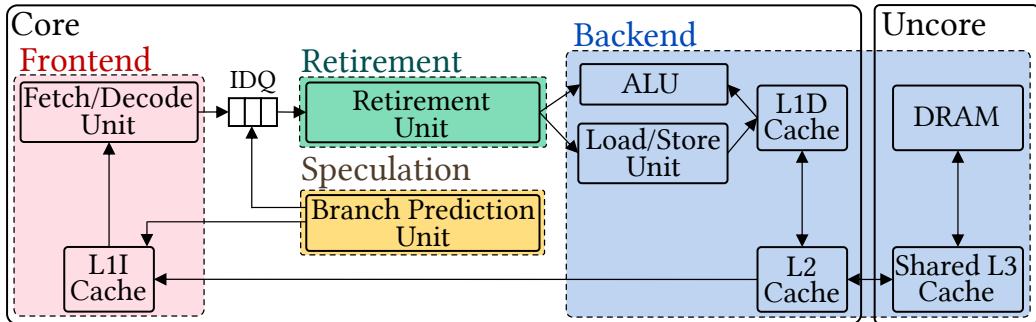

Second, the author analyzes the bottleneck for computation since computation time is the bottleneck, as shown later in Section 3.2.3. Specifically, the author analyzes where hazards occur in the pipeline and how long the pipeline is stalled due to the hazards. The author uses the top-down micro-architecture analysis method proposed by Yasin [49]. Before analyzing the pipeline hazards, the author explains the pipeline and flows of instructions and data on a CPU.

The pipeline has four main stages: *frontend*, *backend*, *speculation*, and *retirement*, as shown in Fig. 3.2. The frontend stage is responsible for fetching instructions from the DRAM device or the CPU caches and feeding them to the backend stage, and the speculation stage supports the frontend stage in its instruction fetches, using the branch prediction unit. In contrast, the backend stage is responsible for executing the instructions, fetching necessary data from the DRAM device or the caches and storing data on the caches. Finally, instructions executed successfully are retired at the retirement stage.

The CPU cycles spent for processing the pipeline are also categorized into four major parts: CPU cycles spent during the pipeline stalls at the *frontend* stage due to *instruction cache misses*, that spent during pipeline stalls at the *backend* stage due to *data cache misses*, that wasted at the *speculation*

stage due to *branch prediction misses*, and that spent when *instructions are successfully executed and retired* at the *retirement* stage. In the ideal case, where instructions are executed without pipeline stalls, the CPU cycles spent at all stages except for the retirement stage become zero. That is, the CPU cycles spent at the retirement stage are equivalent to the minimum computation time.

The pipeline stalls at each of the stages can be further broken down into more specific categories based on the reasons for the stalls. The pipeline stalls at the backend stage are divided into the following three categories: pipeline stalls due to waits at *load* units, at *store* units, and at *core* units, such as instruction execution units. Since the pipeline stalls at the backend stage dominate the overall pipeline stalls, the author omits any detailed investigation of the pipeline stalls at the frontend and speculation stages. Among them, the pipeline stalls due to waits at load units dominate the overall pipeline stalls at the backend stage, and hence the author further categorizes the pipeline stalls at the load units into the following four categories: pipeline stalls to wait for data to be fetched from the *L1D*, *L2*, *L3* caches, and the *DRAM* device.

### CPU Cycle Measurement Method

The number of CPU cycles spent at each of the pipeline stages are measured with a performance monitoring unit (PMU) on CPUs. A PMU has a set of counters, which count the number of occurrences of hardware events. Such events include pipeline stalls at the frontend, backend, and speculation stages and the instruction retirement at the retirement stage.

### 3.2.2 Experiment Settings

#### Prototype Implementation

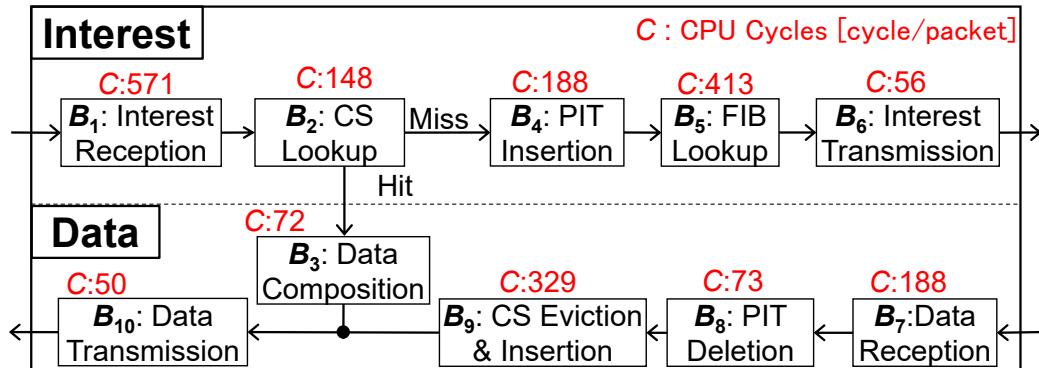

The author implements a prototype of basic NDN functions which include longest prefix match on FIB lookup, exact match on CS lookup and PIT lookup, and FIFO-based CS eviction according to a state-of-the-art software implementation [10]. The processing flow of the prototype is shown in Fig. 3.3. When an Interest packet is received, the prototype performs NDN functions in the same order as the block diagram of [7] except for the functions below. A nonce is not calculated because the number of CPU cycles needed for the calculation is much smaller than that of the whole Interest packet forwarding [50]. Only the Best Route Strategy is supported. Partial name matching of Interest and Data names and selectors are not supported because the goal of this thesis is fast name-based longest prefix match. The FIB does not have entries other than those for Interest forwarding such as those for RTT estimation because fast stateful forwarding is not a goal of this thesis. When a Data

Figure 3.3: NDN software block diagram and analysis of computation time