|              |                                                                                        |

|--------------|----------------------------------------------------------------------------------------|

| Title        | Thermal degradation mechanisms of package materials for high-temperature power modules |

| Author(s)    | 崔, 讚揚                                                                                  |

| Citation     | 大阪大学, 2020, 博士論文                                                                       |

| Version Type | VoR                                                                                    |

| URL          | <a href="https://doi.org/10.18910/76530">https://doi.org/10.18910/76530</a>            |

| rights       |                                                                                        |

| Note         |                                                                                        |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# **Doctoral Dissertation**

**Thermal degradation mechanisms of package materials

for high-temperature power modules**

**Chanyang Choe**

**January 2020**

**Department of Adaptive Machine Systems

Graduate School of Engineering

Osaka University**

Ph.D. Dissertation

Thermal degradation mechanisms of package materials

for high-temperature power modules

by

Chanyang Choe

Department of Adaptive Machine Systems

Graduate School of Engineering

Osaka University

January 2020

Approved by

Professor Katsuaki Saganuma

Professor Hiroshi Utsunomiya

Associate Professor Shijo Nagao

Associate Professor Tohru Sugahara

# Thermal degradation mechanisms in package materials for high-temperature power modules

## Abstract

Wide-bandgap (WBG) semiconductor materials, such as silicon carbide (SiC) and gallium nitride (GaN), are being increasingly used, and provide significant opportunities to develop power electronic systems with high power densities, high reliability in extreme environments, and high integration. The development of high-temperature-operating power devices enables the use of power modules at high temperatures ( $>250$  °C). The aforementioned power modules have a multi-layered packaging structure that comprises four main components, namely, semiconductors, joints, substrates, and wires. Under high-temperatures, large thermal stress occurs in the power module as coefficients of thermal expansion (CTE) mismatch among multiple layers, resulting in thermal damage. This thesis describes thermal degradation mechanisms in joints and substrates under high-temperature. In addition, a novel real-time monitoring method for damage via acoustic emission (AE) technique is presented.

First, to evaluate the thermal degradation mechanisms in sintered micro-porous silver (Ag), which is regarded as a promising joint material for fabricating high-temperature power modules because of its mechanical/electrical properties, its deterioration and microstructural variations were investigated under high-temperature and correlated with each other. Sintered Ag was fabricated in a specimen shape of a tension test by printing and sintering at 250 °C for 1 h in air without pressure. The sintered Ag was exposed to 250 °C for 1000 h. Subsequently, its tensile strength and electrical resistivity were measured. The tensile strength of the sintered Ag decreased initially, but recovered subsequently during the high-temperature exposure, while its electrical resistivity decreased. For microstructure evolution, sintered Ag grains, their porous structure and fracture surface were characterized by SEM and EBSD. The relationship between their microstructural variations and mechanical/electrical properties was discussed.

The thermal shock damage mechanisms in direct bonded aluminum (DBA) and active metal brazing (AMB) substrates with two types of plating—Ni electroplating and Ni–P electroless plating—were evaluated by thermal shock tests between  $-50$  °C and 250 °C. The AMB substrates with Al<sub>2</sub>O<sub>3</sub> and AlN fractured only after 10 cycles, but with Si<sub>3</sub>N<sub>4</sub> ceramic, they retained good thermal stability even after 1000 cycles, regardless of the metallization type. The Ni layer on the surviving AMB substrates with Si<sub>3</sub>N<sub>4</sub> was not damaged, while a crack occurred in the Ni–P layer. For the DBA substrates, fracture did not occur up to 1000 cycles for all kinds of ceramics. However, the Ni–P layer roughened and cracked because of the severe deformation of the aluminum layer, while the Ni layer was not damaged after the thermal shock tests. In addition, the deformation mechanism of an Al plate on a ceramic substrate was investigated both by microstructural observation and finite element method (FEM) simulation, which confirmed that grain boundary sliding was a key factor in the severe deformation of the Al layer. The deformation resulted in the cracking of the Ni–P layer. The fracture suppression in the Ni layer on DBA/AMB substrates can be attributed to its ductility and higher strength compared with those of Ni–P layer.

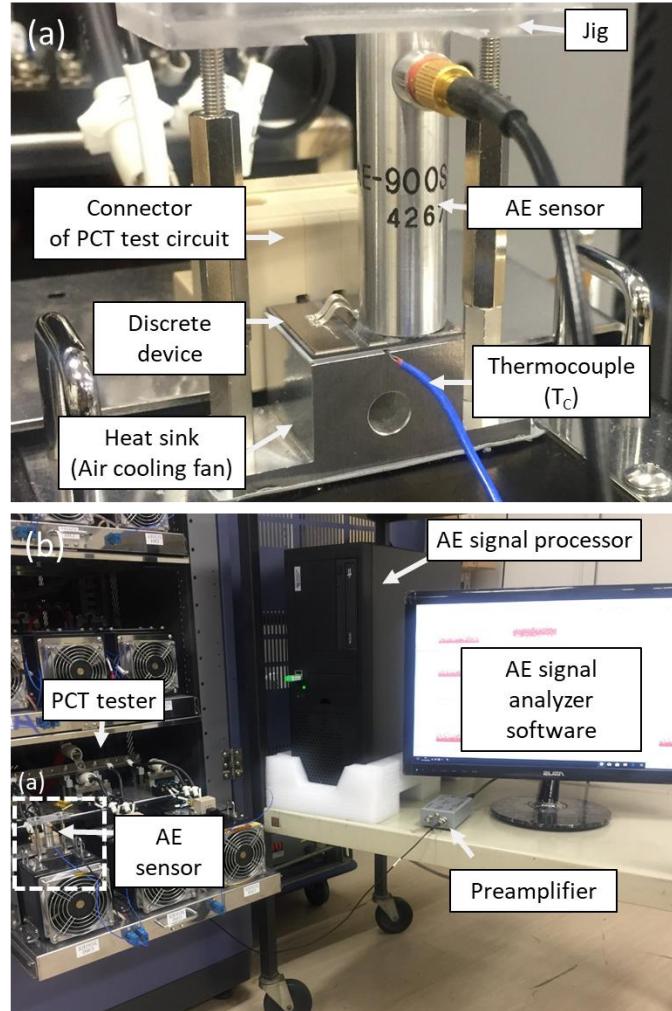

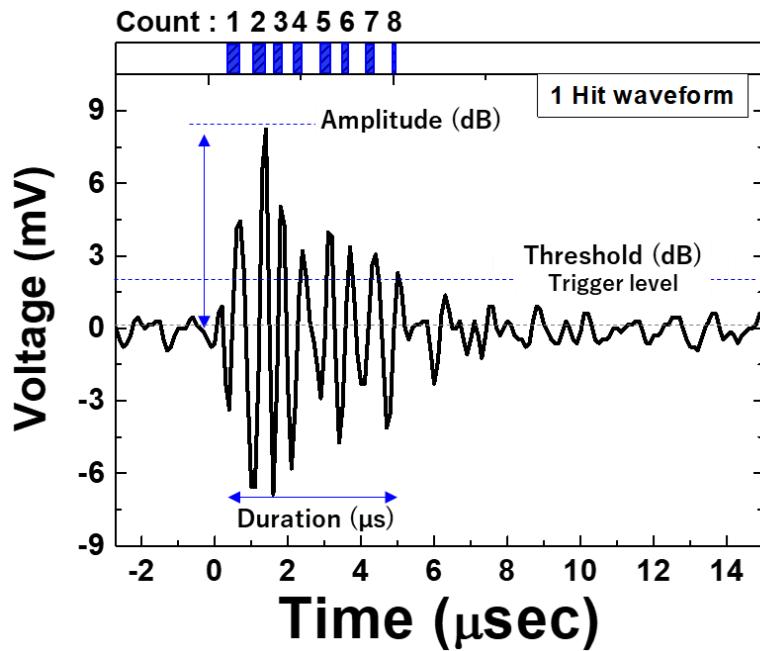

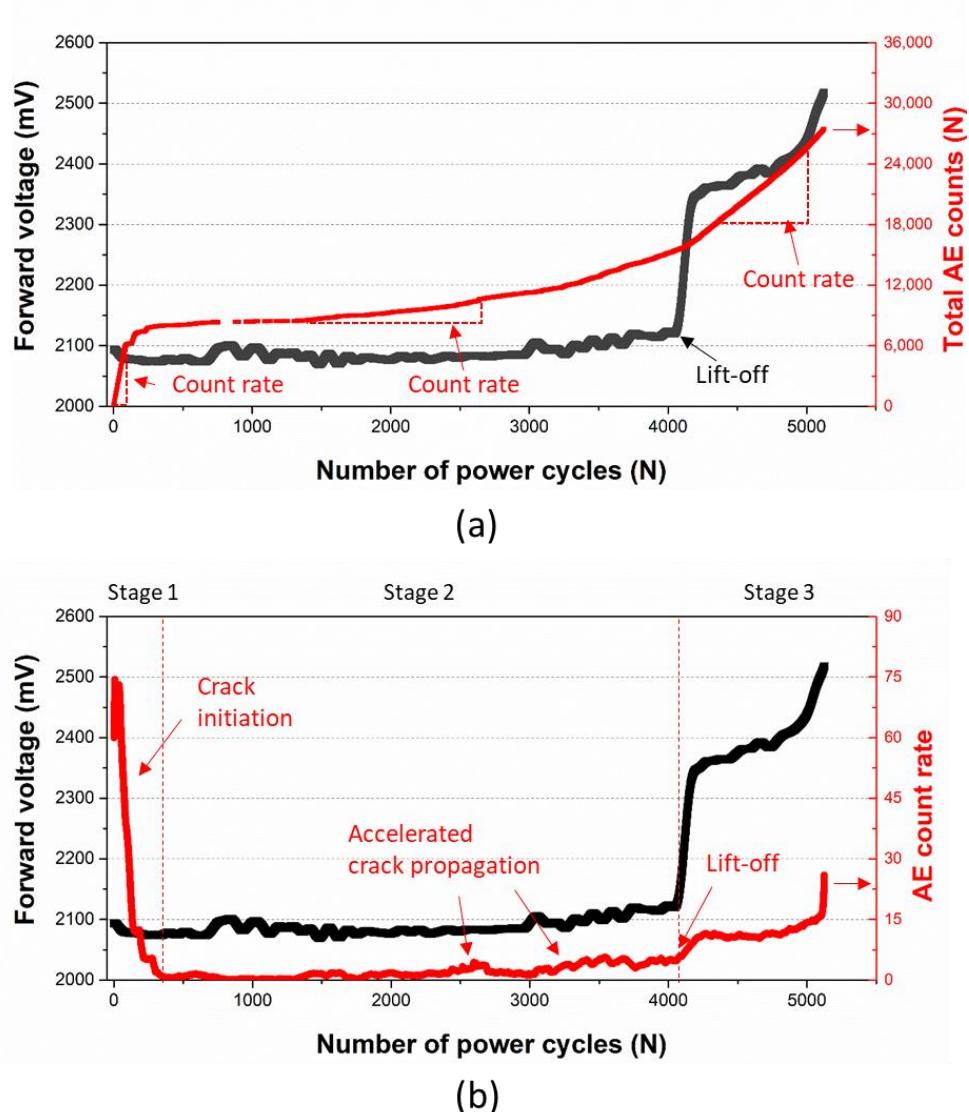

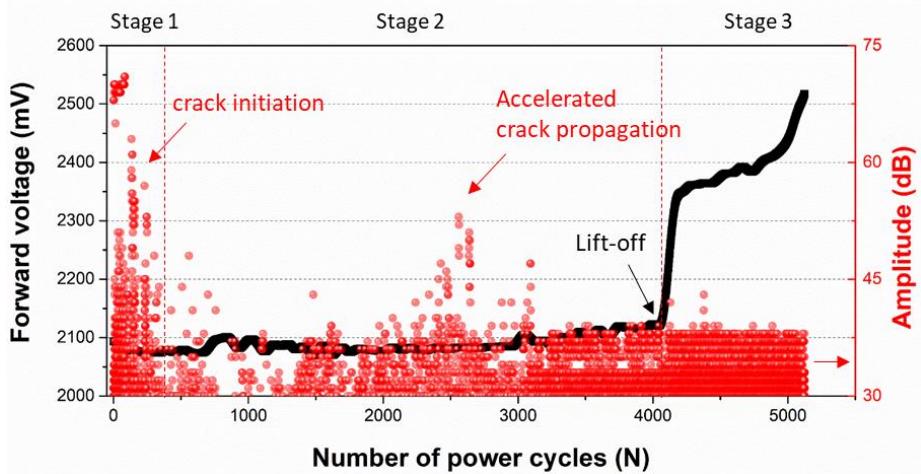

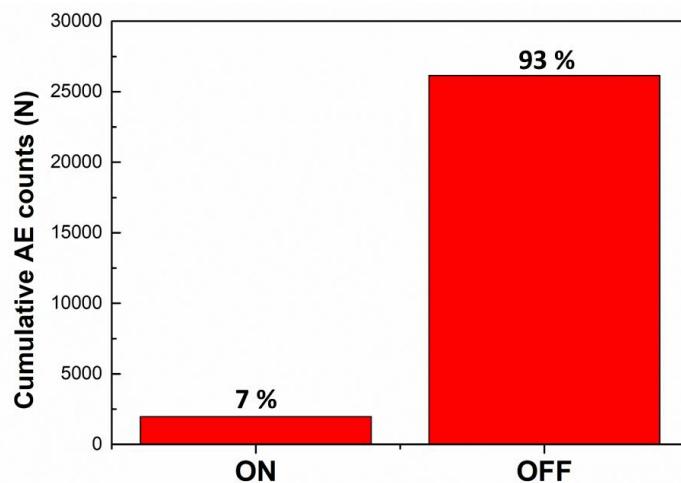

Finally, the wear-out damage mechanism in discrete SiC power devices was evaluated by performing a power cycling test (PCT), and acoustic emission (AE) technique was applied to monitor the damage in real-time for the first time. AE is an excellent method to monitor material damage during operation. The discrete devices were fabricated using a SiC diode, Ag sintering die-attachment, and Al ribbon interconnection. PCT was carried out with a harsh junction temperature swing of  $\Delta 150$  °C to accelerate the damage occurrence, and AE signals were collected simultaneously using an AE sensor that attached to the discrete devices. The AE cumulative counts, which represent the main characteristic of AE signals, were increased with the number of cycles during PCT, while the thermal fatigue crack propagated in the Al ribbon. The relationship between the AE count rate and the observed fatigue crack propagation was confirmed. The result demonstrates that AE evaluation can be used not only for

understanding the fatigue progress of Al ribbons but also for monitoring the failure of power electronic devices.

In this thesis, the results suggest new damage mechanisms for sintered micro-porous Ag and Ni metalized DBA/AMB substrates under high-temperature, and additionally, propose a novel AE monitoring method for analyzing the thermal fatigue damage in power modules.

# Table of contents

|                                                                                  |    |

|----------------------------------------------------------------------------------|----|

| <b>Abstract</b>                                                                  | I  |

| <b>Table of contents</b>                                                         | II |

| <b>List of tables</b>                                                            | V  |

| <b>List of figures</b>                                                           | VI |

| <b>Chapter 1 Introduction</b>                                                    | 1  |

| 1.1 Packaging materials and structure for high-temperature power modules         | 2  |

| 1.1.1 Next generation wide bandgap power semiconductors                          | 2  |

| 1.1.2 Packaging structure of power modules and reliability issue                 | 4  |

| 1.2.3 High-temperature packaging material and its failure mechanisms             | 6  |

| 1.2 Real-time monitoring of thermal fatigue damage                               | 8  |

| 1.2.1 Traditional failure precursor monitoring                                   | 8  |

| 1.2.2 Definition of acoustic emission (AE) monitoring                            | 10 |

| 1.2.3 Sources and characteristics of AE signals                                  | 12 |

| 1.2.4 AE system configuration                                                    | 14 |

| 1.2.5 AE signal characteristics and noise cancelling process                     | 15 |

| 1.3 Objective and outline of the thesis                                          | 17 |

| Reference                                                                        | 19 |

| <b>Chapter 2 Thermal degradation mechanism of micro-porous silver die-attach</b> | 25 |

| 2.1 Introduction                                                                 | 26 |

| 2.2 Experimental                                                                 | 28 |

| 2.2.1 Fabrication of sintered porous Ag specimens                                | 28 |

| 2.2.2 Characterization of mechanical/electrical properties                       | 29 |

| 2.2.3 Microstructural observation                                                | 29 |

| 2.3 Results and discussion                                                       | 32 |

| 2.3.1 Deterioration of tensile strength and electrical resistivity               | 32 |

| 2.3.2 Changes in Ag grains and porous structure                                  | 33 |

|                                                                                                           |           |

|-----------------------------------------------------------------------------------------------------------|-----------|

| 2.3.3 Relationship between mechanical/electrical properties and microstructural variation                 | 37        |

| 2.3.4 Evaluation of fracture surface                                                                      | 39        |

| 2.4 Conclusions                                                                                           | 40        |

| References                                                                                                | 41        |

| <b>Chapter 3 Thermal shock damage mechanism of DBA/AMB substrates plated with Ni and with Ni–P layers</b> | <b>44</b> |

| 3.1 Introduction                                                                                          | 45        |

| 3.2 Materials and methods                                                                                 | 47        |

| 3.3 Results and discussion                                                                                | 51        |

| 3.3.1 Thermal shock behavior                                                                              | 51        |

| 3.3.2 Cracking mechanism of Ni–P layer                                                                    | 59        |

| 3.3.3 FEM simulation                                                                                      | 61        |

| 3.4 Conclusion                                                                                            | 63        |

| References                                                                                                | 64        |

| <b>Chapter 4 Real-time Al ribbon fatigue monitoring by using AE</b>                                       | <b>68</b> |

| 4.1 Introduction                                                                                          | 69        |

| 4.2 Experiment                                                                                            | 72        |

| 4.2.1 The tested discrete devices                                                                         | 72        |

| 4.2.2 Power cycling test (PCT) system and setup                                                           | 74        |

| 4.2.3 Acoustic emission (AE) monitoring system and setup                                                  | 77        |

| 4.2.4 Background AE noise cancelling process and setup                                                    | 79        |

| 4.3 Power cycling test                                                                                    | 81        |

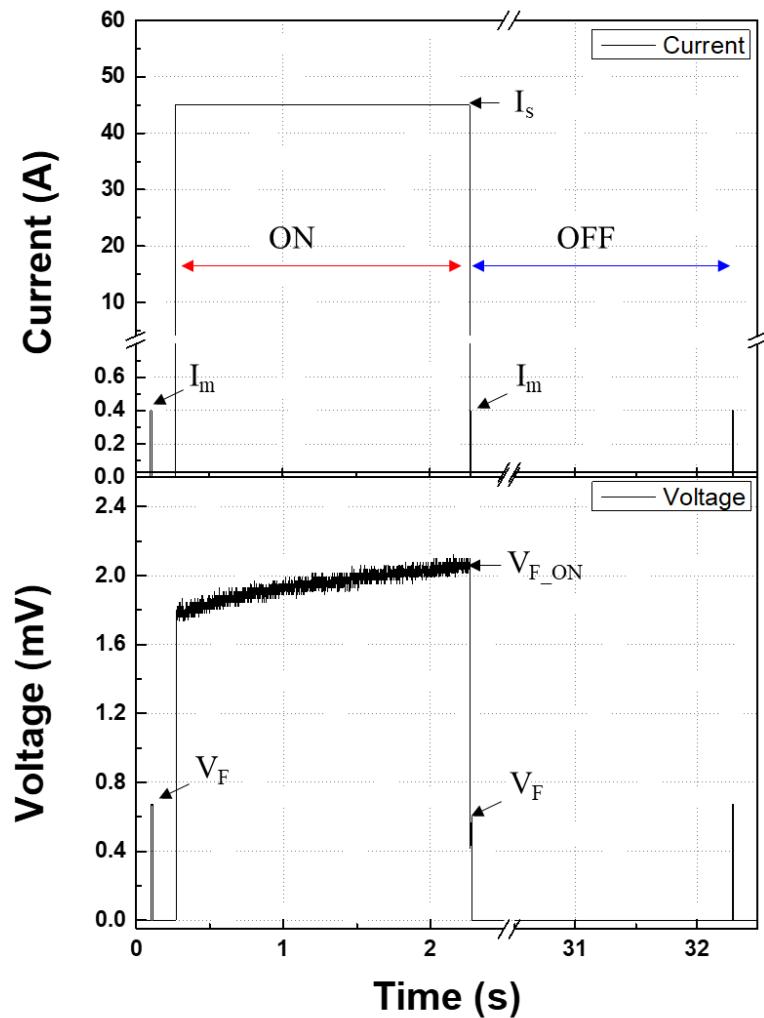

| 4.3.1 Voltage precursor parameter monitoring in power cycling test                                        | 81        |

| 4.3.2 Physics-of-failure analysis of the tested discrete devices                                          | 84        |

| 4.4 Acoustic emission monitoring test                                                                     | 87        |

| 4.4.1 The source of acoustic emission                                                                     | 87        |

| 4.4.2 Monitoring by acoustic emission parameter                                                           | 89        |

| 4.5 Conclusion                                                                                            | 93        |

| References                                                                                                | 94        |

|                                               |     |

|-----------------------------------------------|-----|

| <b>Chapter 5 Conclusions</b>                  | 100 |

| <b>List of Publications and Presentations</b> | 104 |

| <b>Acknowledgments</b>                        | 109 |

## List of tables

| Table                                                                                                     | Page |

|-----------------------------------------------------------------------------------------------------------|------|

| 1.1 Physical properties of Si and WBG semiconductors [4, 6].                                              | 3    |

| 1.2 Mechanism, causes, and precursors of failure in packaging components.                                 | 9    |

| 1.3 Factors affecting AE response [50].                                                                   | 13   |

| 1.4 Typical frequency range of noise in common industries.                                                | 16   |

| 3.1 Materials and dimensions of multilayered specimens.                                                   | 48   |

| 3.2 Mechanical and thermal properties of the various materials in Ni- and Ni–P-plated DBA/AMB substrates. | 50   |

| 4.1 Power cycling test condition.                                                                         | 76   |

## List of figures

| Figure                                                                                                                                                                                                                                                                               | Page |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| 1.1 Junction temperature limits according to the breakdown voltage of Si and WBG semiconductors [5]                                                                                                                                                                                  | 3    |

| 1.2 Packaging structure, materials, and their coefficients of linear thermal expansion (CTE) property in high-temperature power modules                                                                                                                                              | 5    |

| 1.3 Applications of the Ag sinter paste: (a) joint and clip bonding and (b) printed Ag sinter wire [17, 18].                                                                                                                                                                         | 7    |

| 1.4 AE signal generation, propagation, and detection [47].                                                                                                                                                                                                                           | 11   |

| 1.5 Burst and continuous AE signals [41].                                                                                                                                                                                                                                            | 13   |

| 1.6 Illustration of commonly used AE parameters [41].                                                                                                                                                                                                                                | 16   |

| 2.1 Fabrication process of Ag specimens for tensile and four probe tests (a-c) and its micro-porous structure observed by SEM (d).                                                                                                                                                   | 30   |

| 2.2 Configuration of a tensile test (a) and four probe resistivity measurement (b) for sintered Ag specimens.                                                                                                                                                                        | 30   |

| 2.3 Automatic measurement of pore area and number of sintered Ag.                                                                                                                                                                                                                    | 31   |

| 2.4 Deterioration of tensile strength and resistivity of sintered Ag during thermal exposure.                                                                                                                                                                                        | 32   |

| 2.5 EBSD observation of Ag specimens after different exposure times; (a) 0 h, (b) 200 h, (c) 500 h and (d) 1,000 h.                                                                                                                                                                  | 33   |

| 2.6 Variation in Ag grain size and number with thermal exposure time.                                                                                                                                                                                                                | 34   |

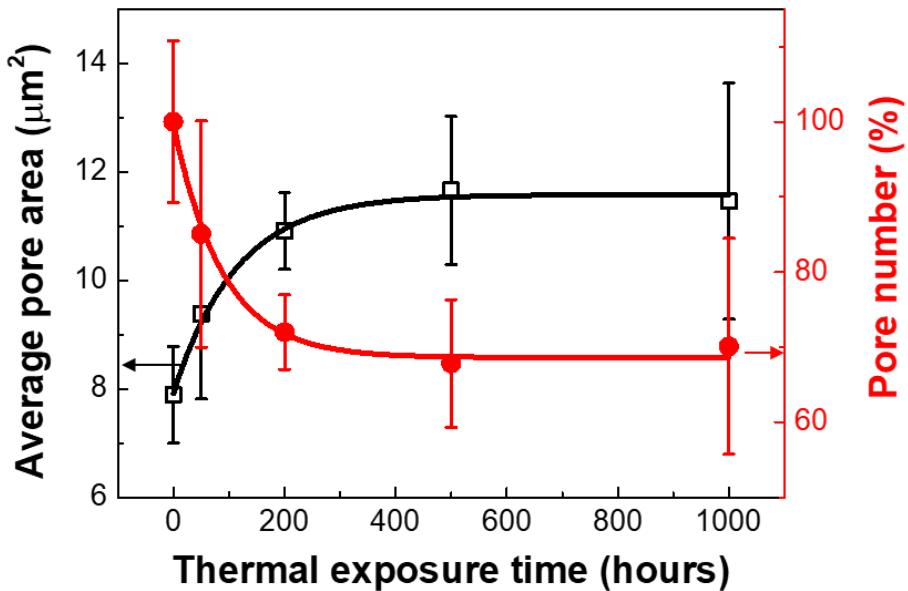

| 2.7 Variation in average pore area and number with thermal exposure time.                                                                                                                                                                                                            | 34   |

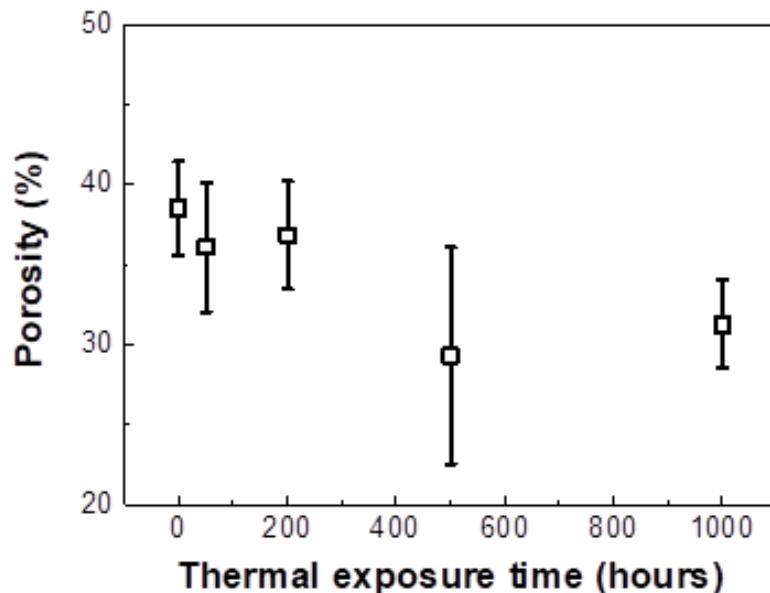

| 2.8 Variation in porosity of sintered Ag with thermal exposure time.                                                                                                                                                                                                                 | 36   |

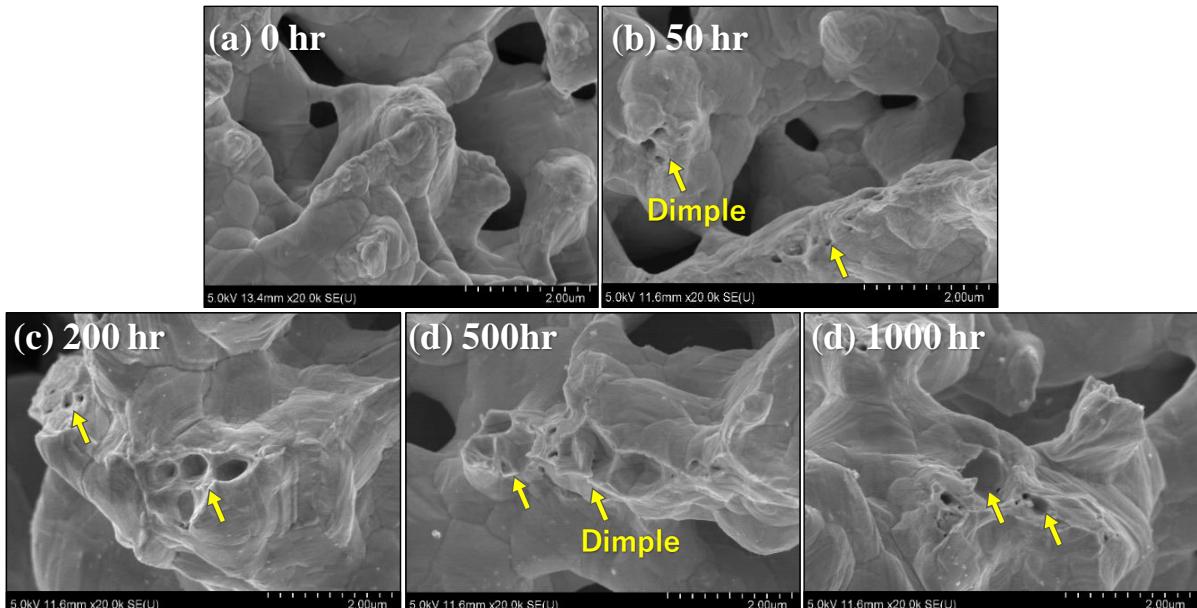

| 2.9 SEM observations of the fracture surface of Ag specimens aged for different exposure times; (a) 0 h, (b) 50 h, (c) 200 h, (d) 500 h and (d) 1000 h.                                                                                                                              | 39   |

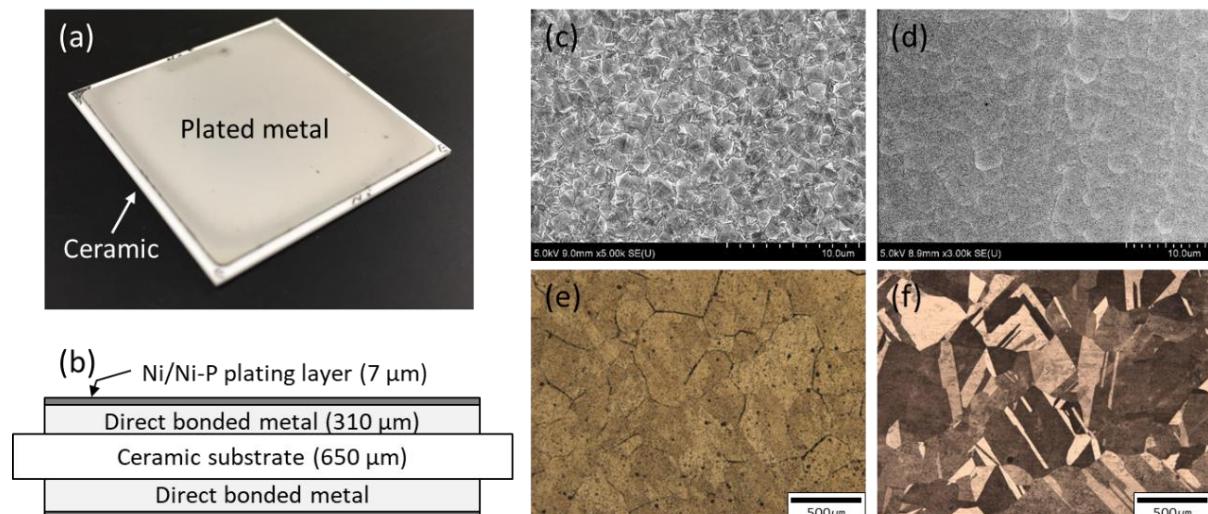

| 3.1 (a) Macrograph of a typical substrate specimen, (b) cross-section diagrams of the DBA/AMB substrates plated by Ni and Ni-P layers, surface morphology of Ni (c) and Ni-P (d) layer on the substrates, and surface microstructure of Al (e) and Cu (f) of the DBA/AMB substrates. | 48   |

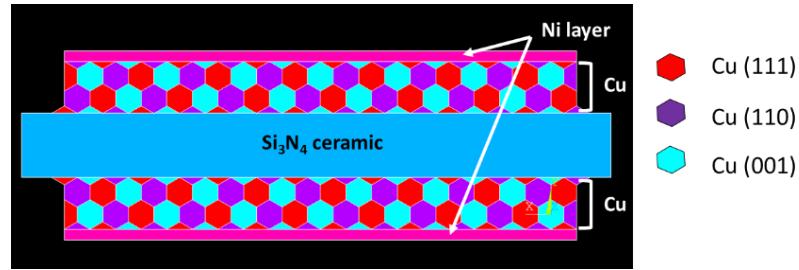

| 3.2 FEM model for thermal stress distribution simulation of an AMB substrate with $\text{Si}_3\text{N}_4$ .                                                                                                                                                                          | 50   |

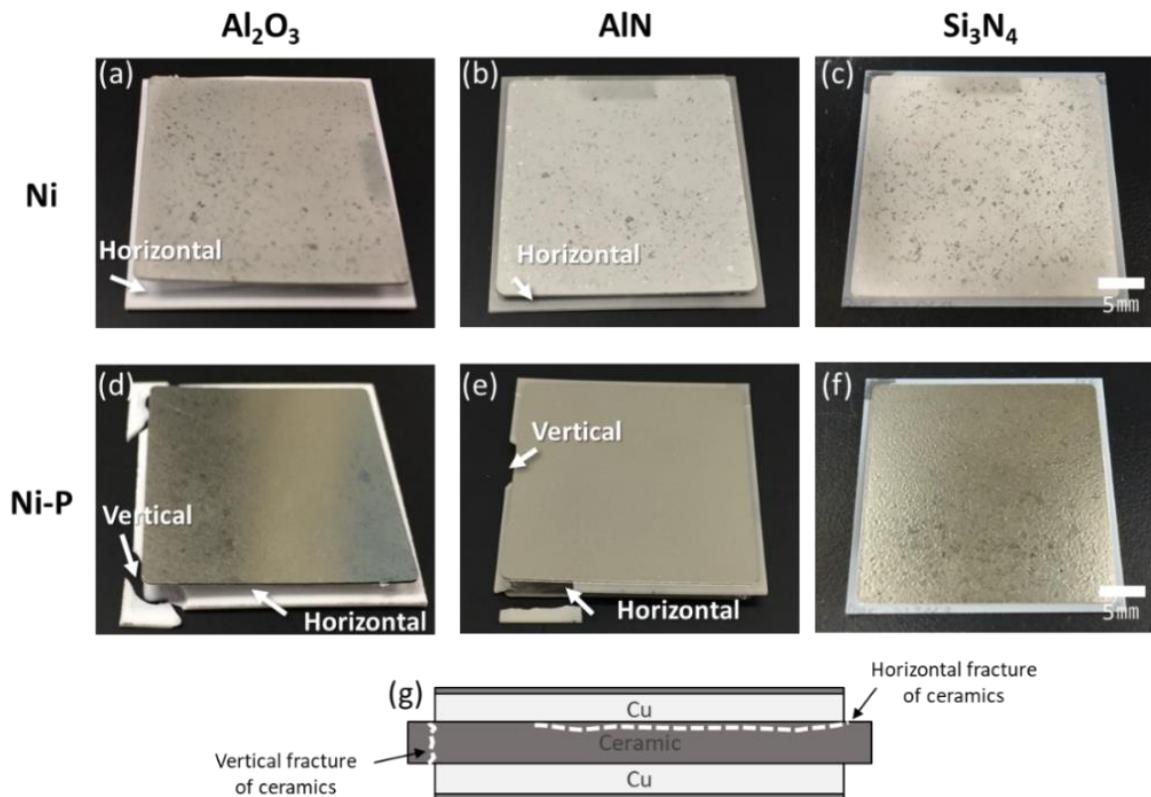

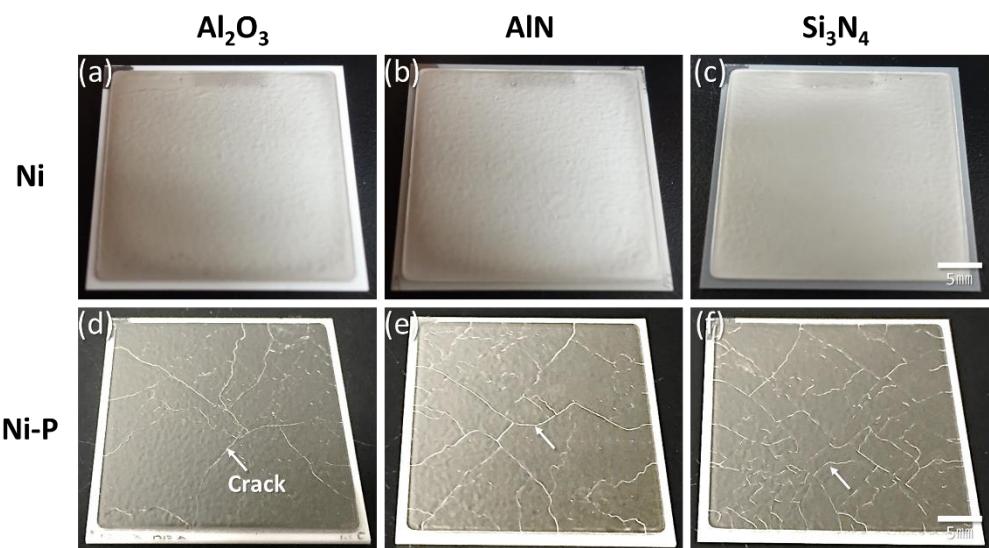

| 3.3 Destruktion AMB substrates with $\text{Al}_2\text{O}_3$ (a, d) and AlN (b, e) after 10 cycles, nondestructed AMB substrates with $\text{Si}_3\text{N}_4$ (c, f) after 1000 cycles plated with Ni (a-c) and Ni-P (d-f), and (g) fracture pattern of AMB substrates.               | 52   |

|      |                                                                                                                                                                                                                                                                                                       |    |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

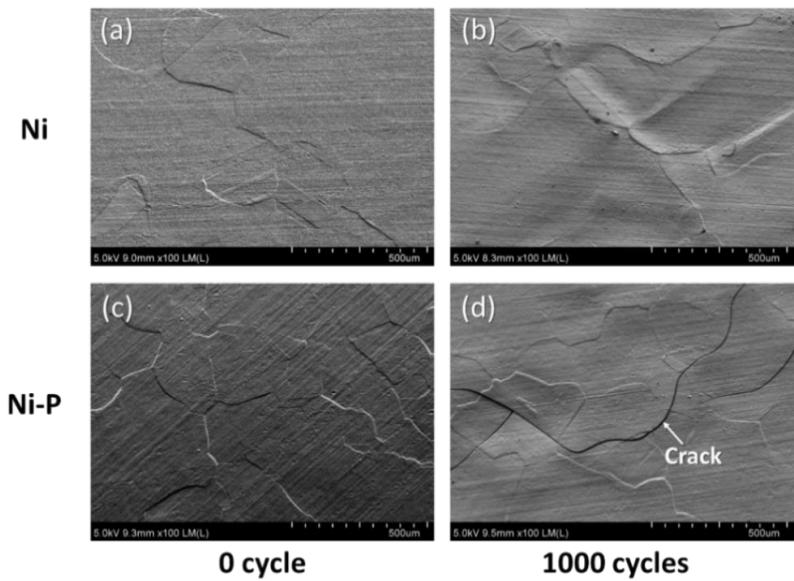

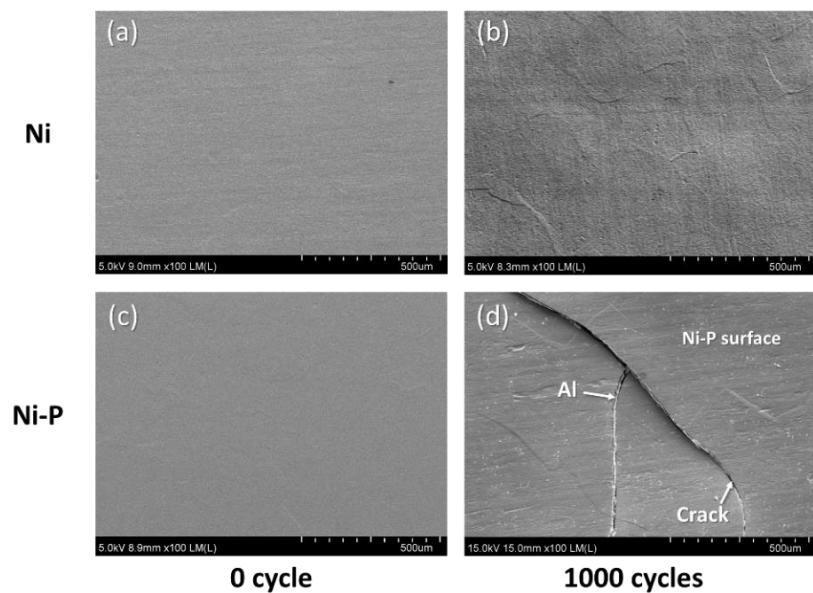

| 3.4  | Surface variation of Ni (a,b) and Ni–P (c,d) layers on AMB substrates with $\text{Si}_3\text{N}_4$ before and after 1000 cycles.                                                                                                                                                                      | 53 |

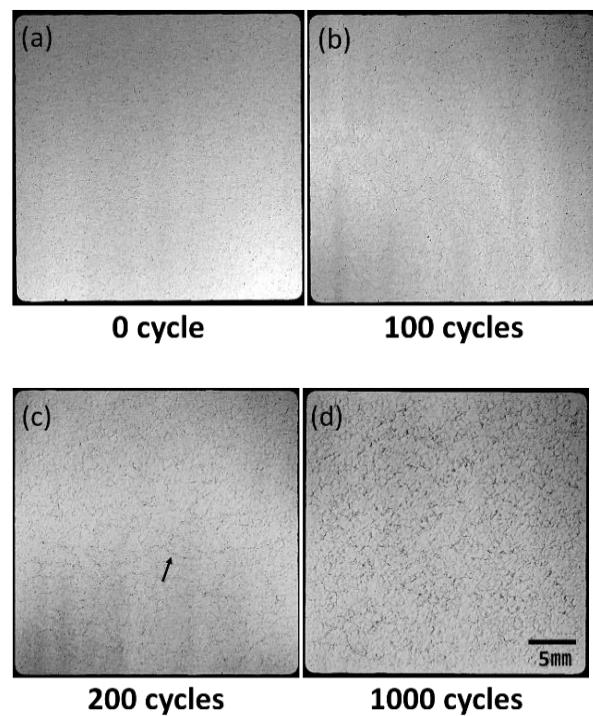

| 3.5  | Scanning acoustic tomography (SAT) observation of the surface morphology of the Ni–P layer on AMB substrates with $\text{Si}_3\text{N}_4$ after different thermal shock tests: 0, 50, 100, and 1000 cycles.                                                                                           | 53 |

| 3.6  | DBA substrates with $\text{Al}_2\text{O}_3$ , AlN, and $\text{Si}_3\text{N}_4$ after 1000 cycles, plated with Ni (a–c) and Ni–P (d–f).                                                                                                                                                                | 55 |

| 3.7  | Surface morphology of Ni (a,b) and Ni–P (c,d) layers on DBA substrates with $\text{Si}_3\text{N}_4$ before and after 1000 cycles.                                                                                                                                                                     | 55 |

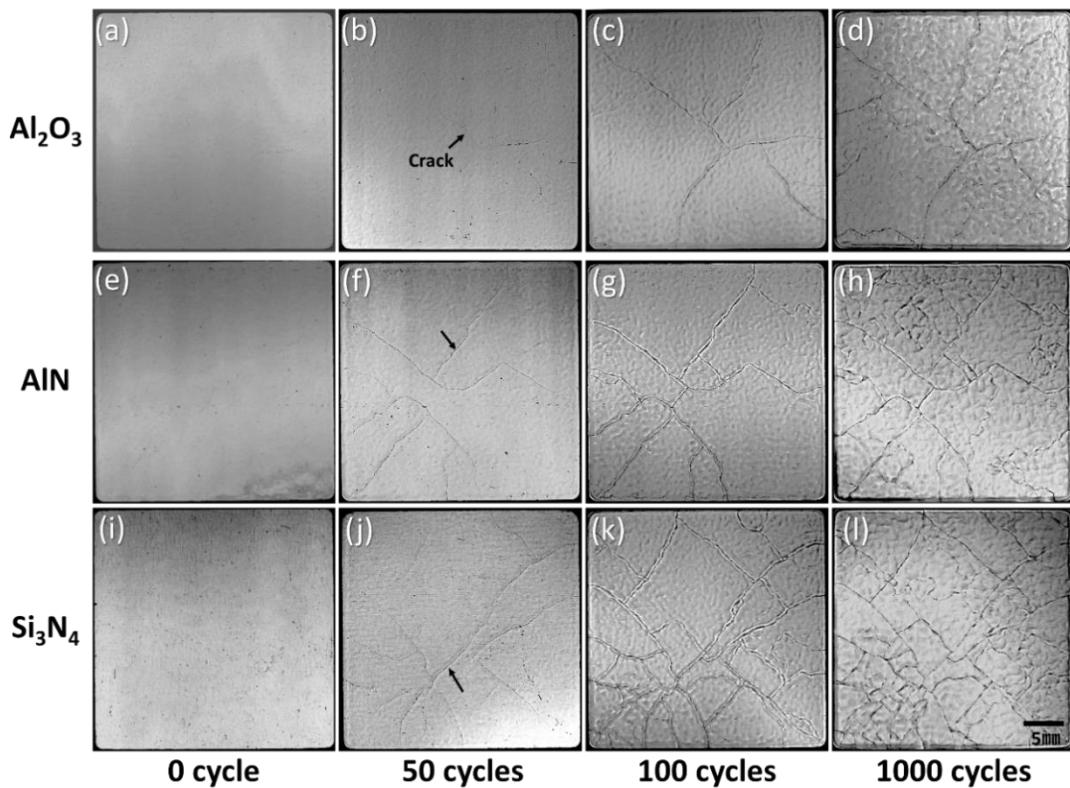

| 3.8  | SAT observation of the surface morphology of a Ni–P layer on DBA substrates with $\text{Al}_2\text{O}_3$ (a–d), AlN (e–h), and $\text{Si}_3\text{N}_4$ (i–l) after different thermal shock tests: 0, 50, 100, and 1000 cycles.                                                                        | 57 |

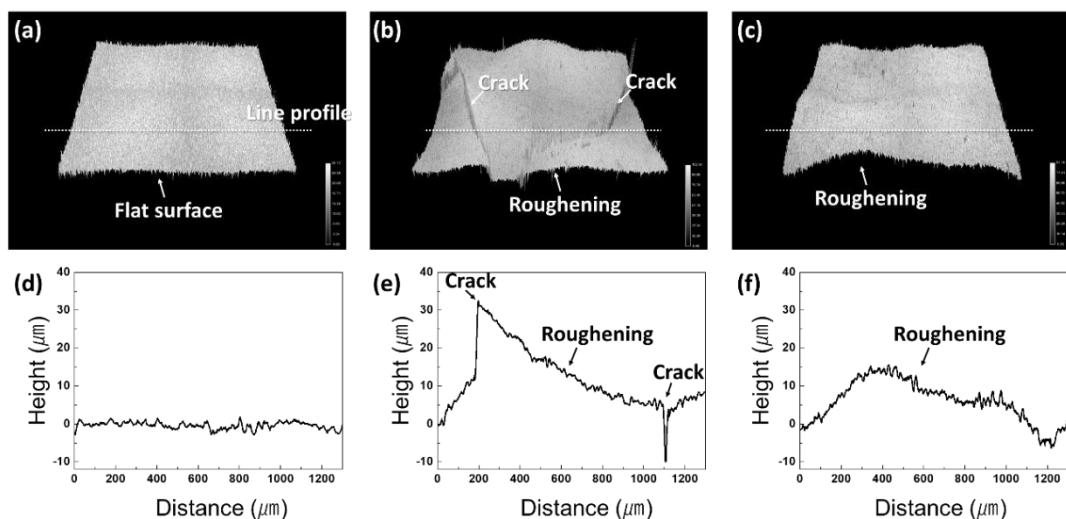

| 3.9  | Laser surface observation of the Ni–P layer on DBA substrates with $\text{Si}_3\text{N}_4$ at the initial state (a) and after 1000 cycles (b,c). Local area with cracked (b) and roughened (c) area, and its roughness profile (d–f) measured by a line profile corresponding to (a–c), respectively. | 57 |

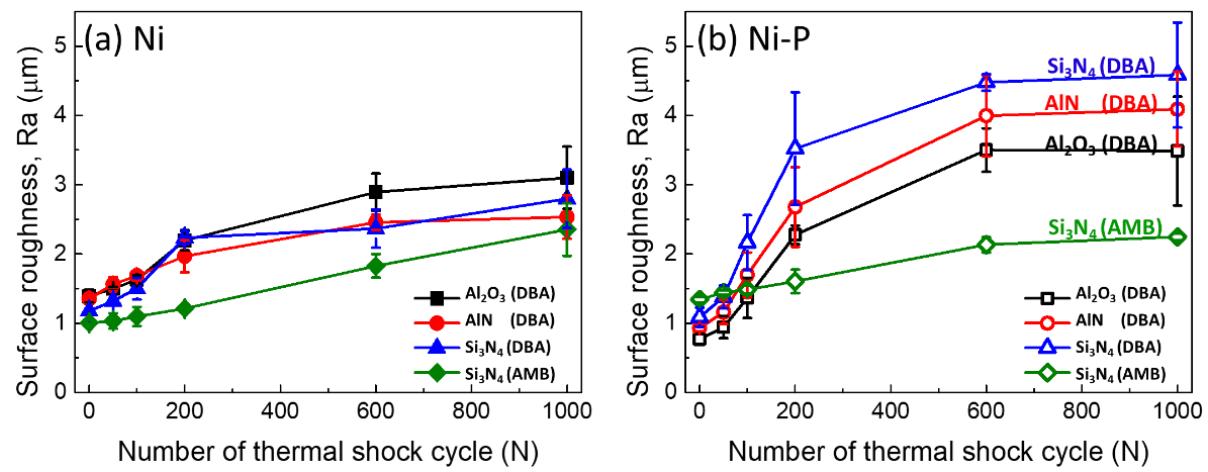

| 3.10 | Variation in surface roughness of Ni (a) and Ni–P (b) layers on DBA/AMB substrates with $\text{Al}_2\text{O}_3$ , AlN, and $\text{Si}_3\text{N}_4$ up to 1000 cycles.                                                                                                                                 | 58 |

| 3.11 | Variation in surface roughness of Ni (a) and Ni–P (b) layers on DBA/AMB substrates with $\text{Al}_2\text{O}_3$ , AlN, and $\text{Si}_3\text{N}_4$ up to 1000 cycles.                                                                                                                                 | 60 |

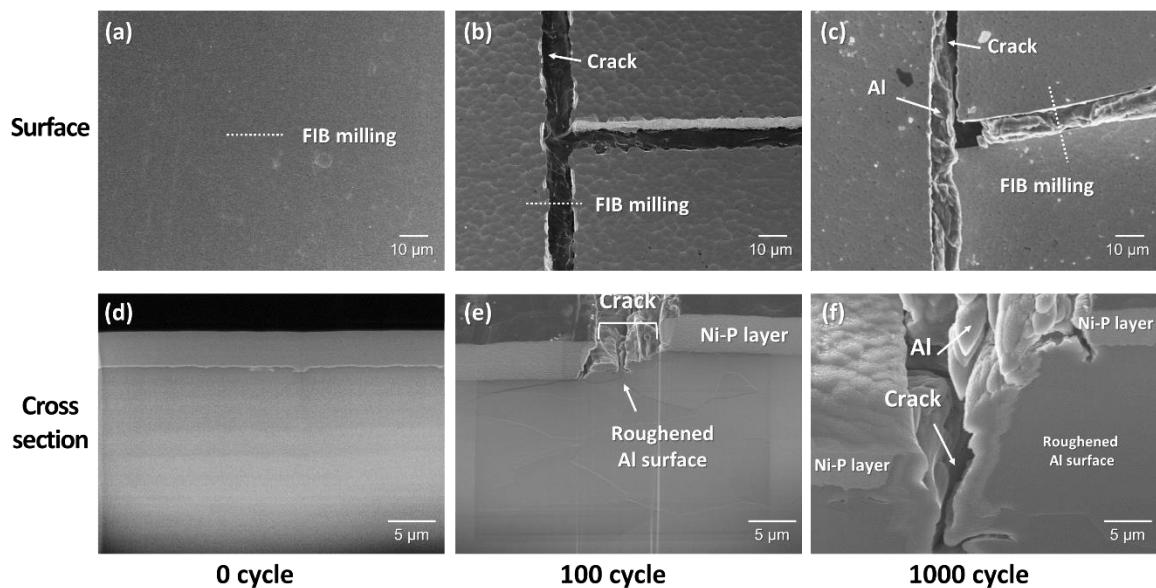

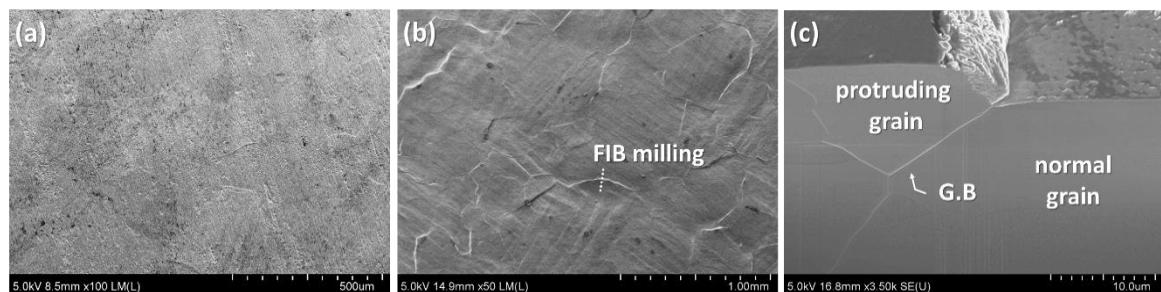

| 3.12 | SEM observation of bare aluminum surface in DBA substrates with $\text{Si}_3\text{N}_4$ at the initial state (a) and after thermal shock tests of 100 cycles (b), and FIB-milled cross section (c) at the location of surface deformation.                                                            | 60 |

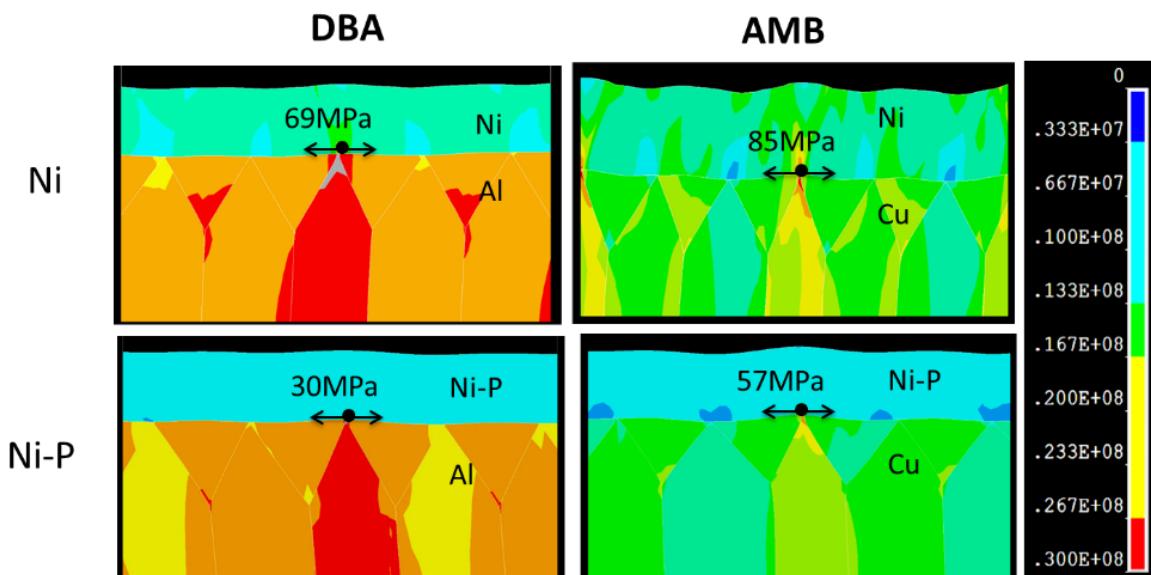

| 3.13 | Maximum principal stress distribution for Ni and Ni–P layers on DBA/AMB substrates with $\text{Si}_3\text{N}_4$ at 250 °C during thermal shock cycling test.                                                                                                                                          | 62 |

| 4.1  | Generation, propagation, and collection process of acoustic emission signals (i.e. elastic waves) in power electronics during PCT.                                                                                                                                                                    | 71 |

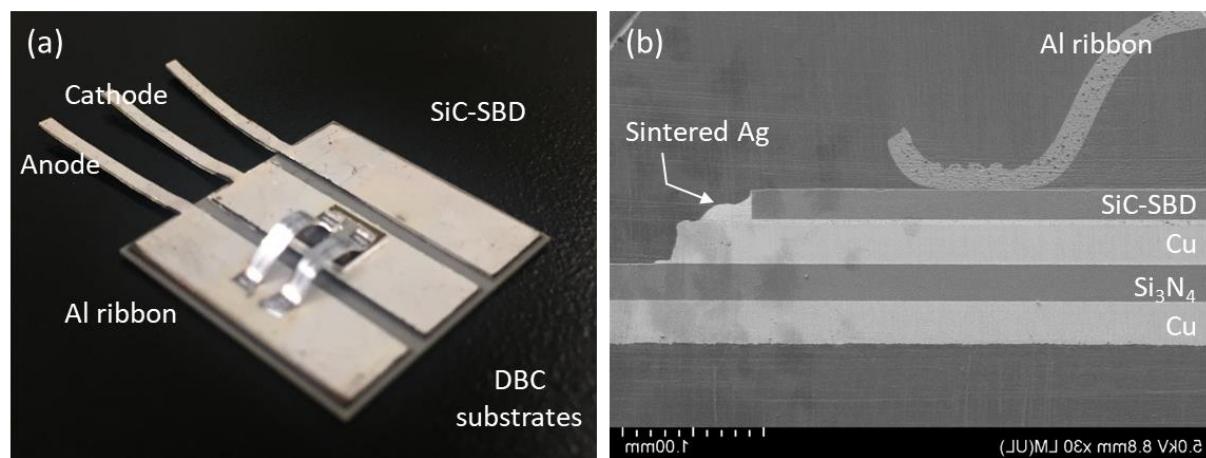

| 4.2  | Fabricated discrete SiC-SBD devices; (a) optical image and (b) its cross-section SEM image.                                                                                                                                                                                                           | 73 |

| 4.3  | Configuration of power cycling test system and real-time acoustic emission monitoring system.                                                                                                                                                                                                         | 75 |

| 4.4  | Profile of voltage and current during power cycling tests.                                                                                                                                                                                                                                            | 76 |

| 4.5  | Waveform of a collected AE signal and its characteristic including counts and amplitude.                                                                                                                                                                                                              | 78 |

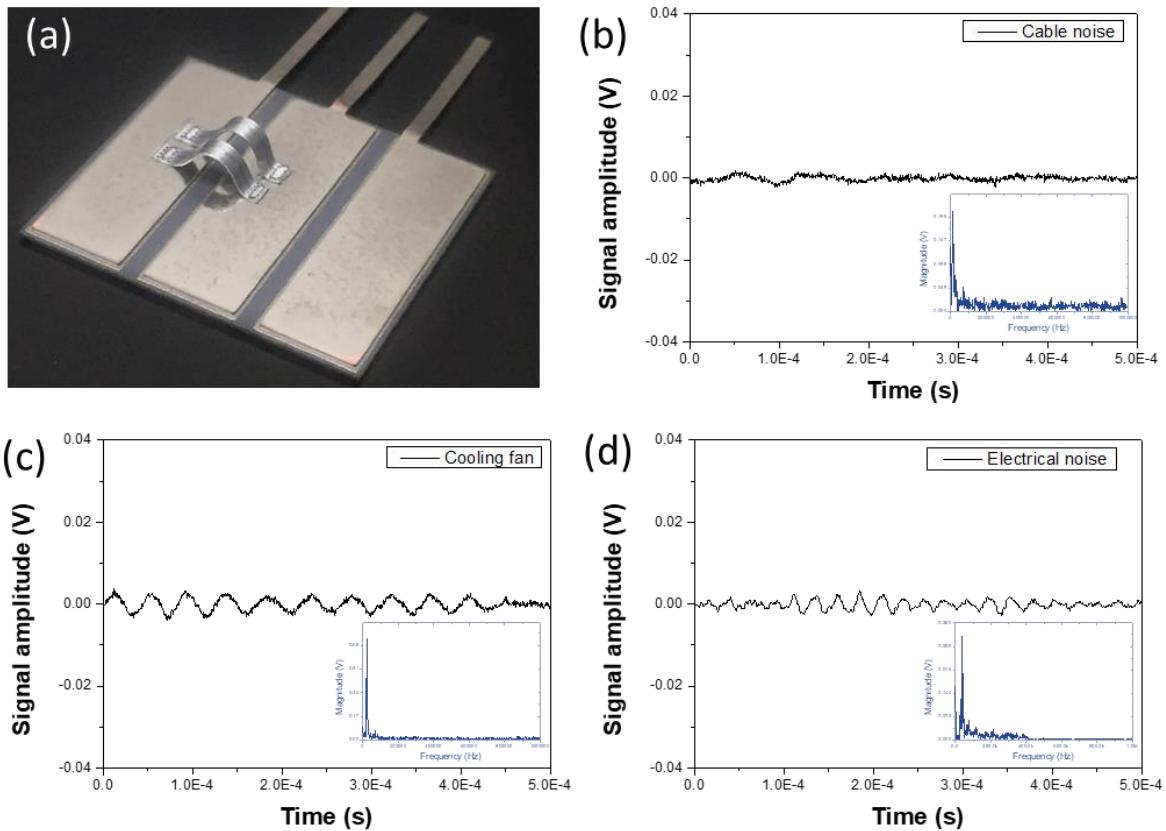

| 4.6  | Dummy specimens designed for noise cancelling and (b-d) Typical waveform and frequency spectrum of three types of collected noise; (a) cable noise, (b) cooling fan movement noise and (c) electromagnetic induction noise.                                                                           | 80 |

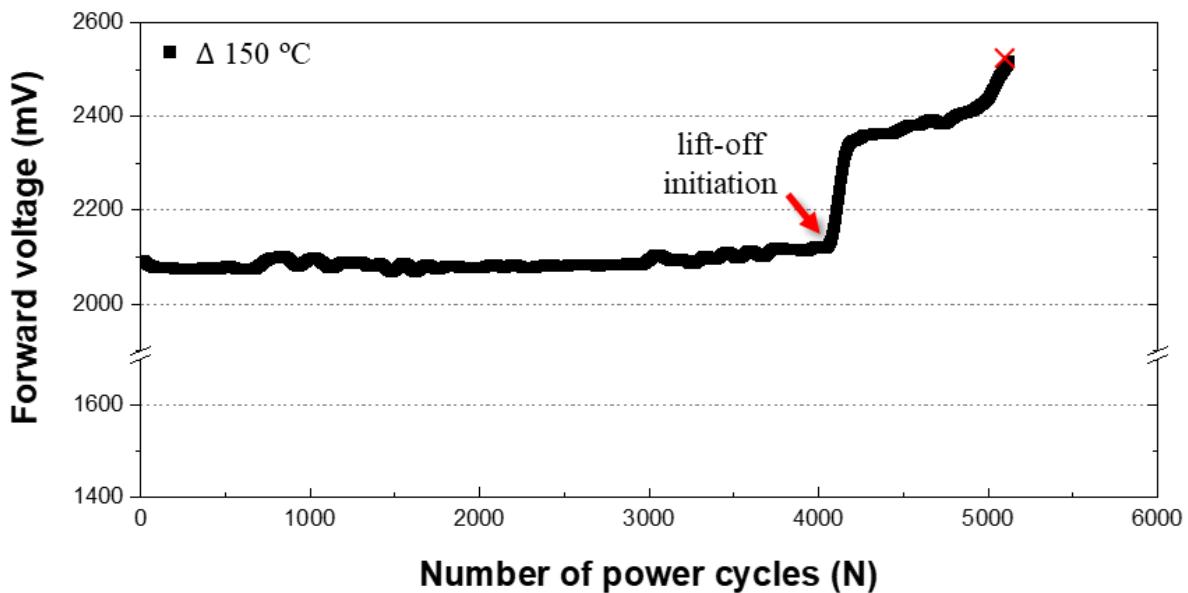

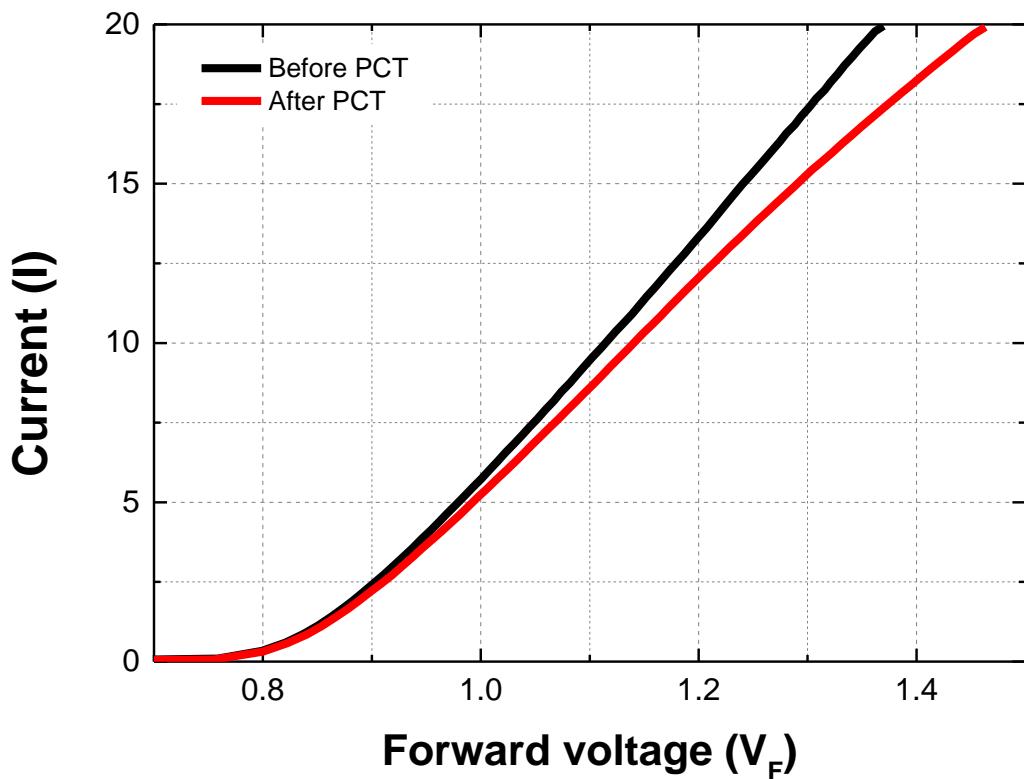

| 4.7  | Variation in forward voltage of a diode during PCT tests.                                                                                                                                                                                                                                             | 82 |

| 4.8  | I-V characteristics before and after PCT tests under.                                                                                                                                                                                                                                                 | 83 |

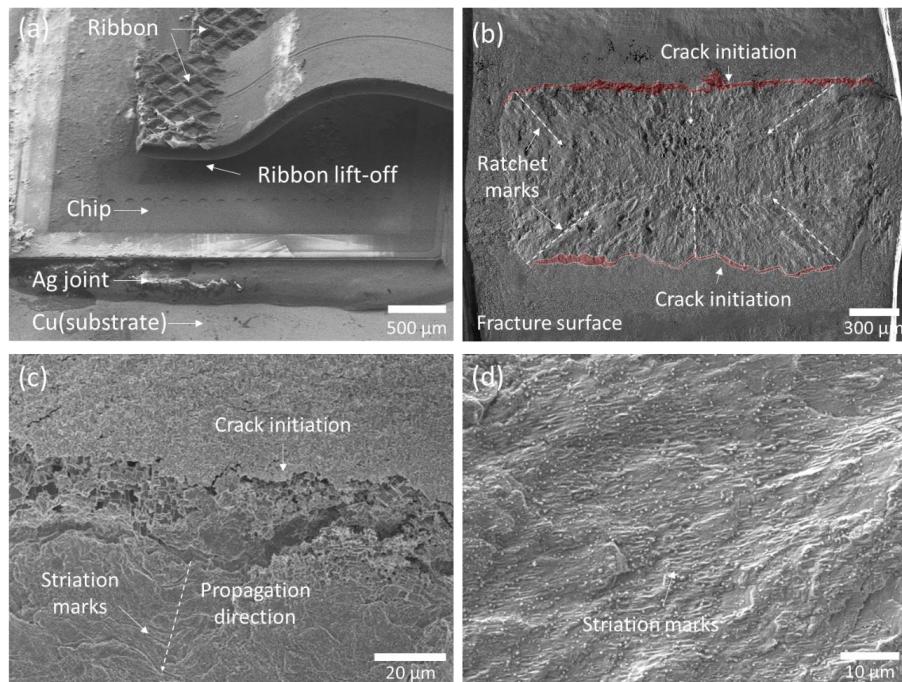

| 4.9  | Failure analysis results of failed discrete SiC-SBD devices after PCT tests; (a) lift-off failure of one Al ribbon, (b) fracture surface of lift-off ribbon, (c) magnified                                                                                                                            | 85 |

|                                                                                                                                                                                        |    |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| observation of crack initiation, and (d) magnified observation of fatigue fracture marks.                                                                                              |    |

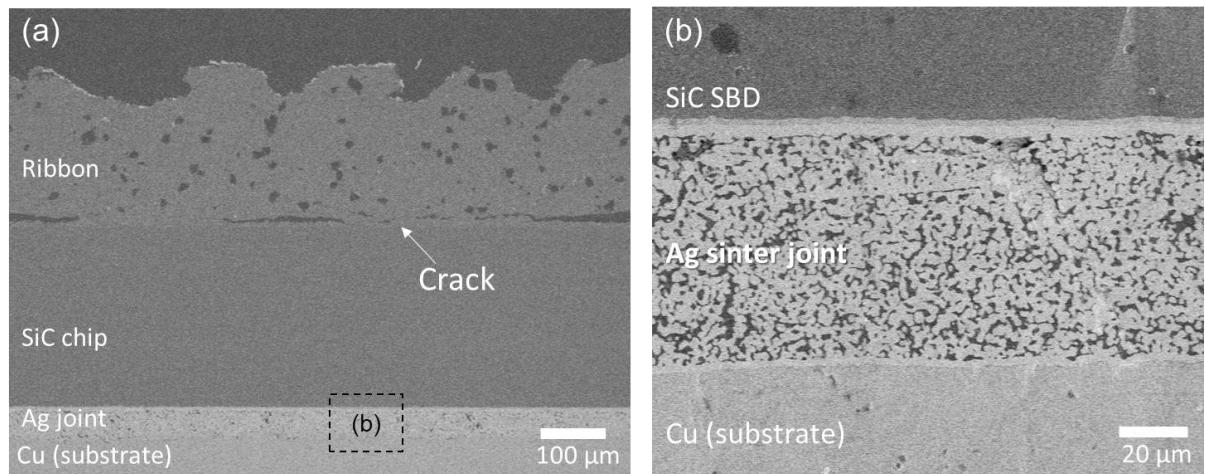

| 4.10 (a) Cross-section observation of another unfractured ribbon portion after PCT tests and (b) a magnified cross-section image of Ag sinter joint.                                   | 86 |

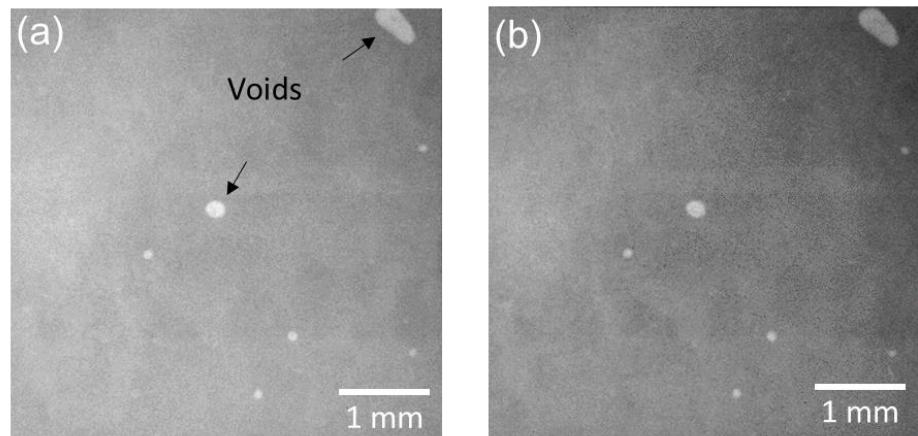

| 4.11 Micro-focused X-ray inspection results of Ag sinter joint in devices before (a) and after (b) PCT tests.                                                                          | 86 |

| 4.12 (a) Dummy specimens designed for noise cancelling and (b) typical waveform and frequency spectrum of three types of collected noise.                                              | 88 |

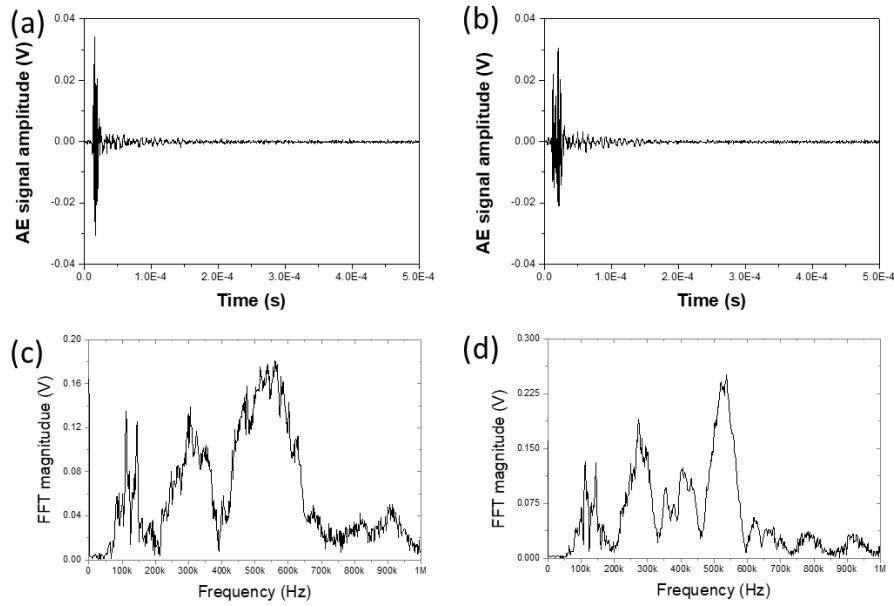

| 4.13 Waveform (a-b) and its corresponding frequency spectrum (c-d) of typical AE signals collected during PCT tests.                                                                   | 88 |

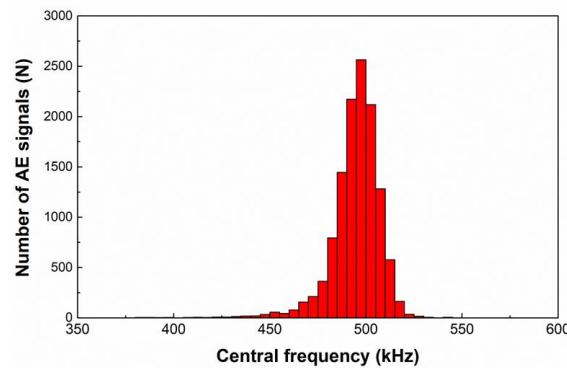

| 4.14 Histogram of the measured central frequency of collected AE signals.                                                                                                              | 91 |

| 4.15 Monitoring result of time-domain parameters during PCT tests with the monitoring results of forward voltage; (a) cumulative counts, (b) cumulative count rate, and (c) amplitude. | 92 |

| 4.16 Cumulative counts of collected AE signals during switching ON and OFF period of PCT tests.                                                                                        | 92 |

# **Chapter 1**

## ***Introduction***

### **1.1.1 Next generation wide bandgap power semiconductors**

Power electronic modules, such as converter and inverter systems, have been widely used in transportation applications, such as electric vehicles, aircrafts, and high-speed trains. Owing to the increasing demand for power density, efficiency, and switching frequency, traditional power modules based on Si materials cannot satisfy these demands because of the theoretical performance limit of Si materials [1–3]. Therefore, to address the high-performance challenges of power modules, Si devices have been replaced with wide bandgap (WBG) devices containing materials such as silicon carbide (SiC) and gallium nitride (GaN) because of their remarkable physical properties, as listed in Table 1.1 [4–6].

Many researchers have reported the high performance of power modules that are based on WBG devices. Compared with Si IGBTs, SiC MOSFETs achieve higher efficiency and switching frequency, since they reduce the switching loss. Although the converters based on Si IGBTs and Si MOSFETs are operated at a switching frequency less than 10 kHz, converters based on SiC MOSFETs can be operated at a frequency higher than 150 kHz using the same power [7, 8].

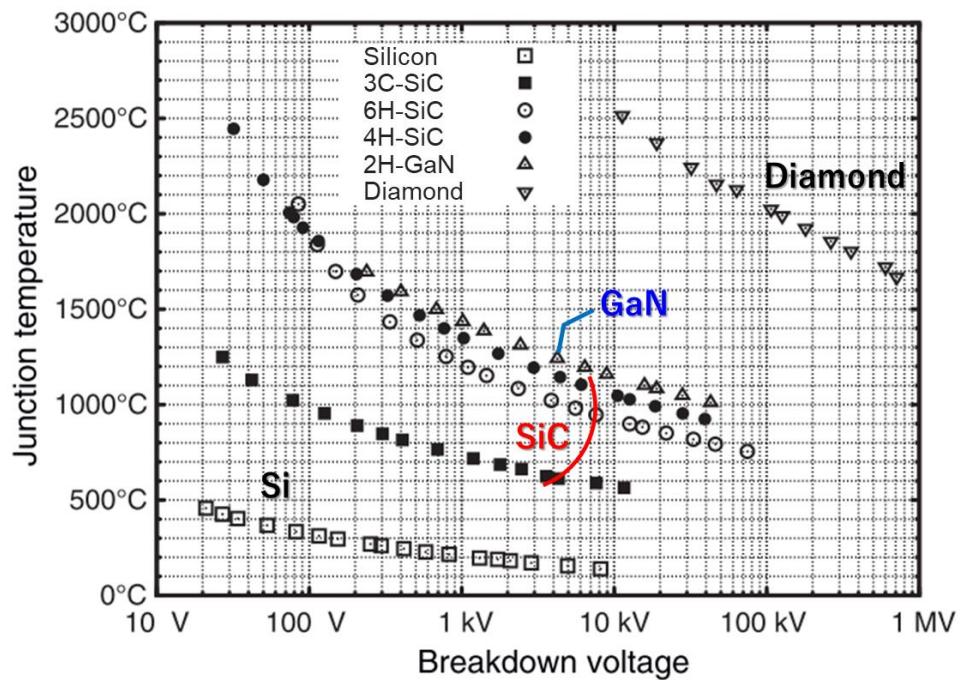

In addition, WBG semiconductors conveniently perform high temperature and high power density operations because of their higher breakdown temperature and voltage. Fig. 1.1 shows the minimum junction temperature at which breakdown failure occurs. WBG semiconductors enable operations at high-voltages up to 100 kV, as they can perform even at the high-temperature of 400 °C without device breakdown failure. However, Si devices are limited to only a few hundred voltages and lower junction temperature because of their breakdown failure [9–11].

Table 1.1 Physical properties of Si and WBG semiconductors [4, 6].

|                                                                        | Si   | 3C-SiC | 4H-SiC | 3C-GaN | 2H-GaN | Diamond |

|------------------------------------------------------------------------|------|--------|--------|--------|--------|---------|

| Bandgap energy, $E_g$ (eV)                                             | 1.12 | 2.2    | 3.26   | 3.27   | 3.39   | 5.45    |

| Critical electric field, $E_c$ (Vcm $^{-1}$ )                          | 11.8 | 9.6    | 10     | 1      | 3.3    | 5.6     |

| Electrical mobility, $\mu_n$ (cm $^2\cdot$ V $^{-1}\cdot$ s $^{-1}$ )  | 1350 | 900    | 720    | 1000   | 900    | 1900    |

| Saturation velocity, $v_{sat}$ (cm $\cdot$ s $^{-1}$ )                 | 1.0  | 2.0    | 2.0    | 2.6    | 2.5    | 2.7     |

| Thermal conductivity, $\lambda$ (W $\cdot$ cm $^{-1}\cdot$ K $^{-1}$ ) | 1.5  | 4.5    | 4.5    | 1.3    | 1.3    | 20      |

| Dielectric constant, $\epsilon_r$                                      | 11.8 | 9.6    | 10     | 9.9    | 8.7    | 5.5     |

Fig. 1.1 Junction temperature limits according to the breakdown voltage of Si and WBG semiconductors [5].

### **1.1.2 Package structure of power modules and reliability issue**

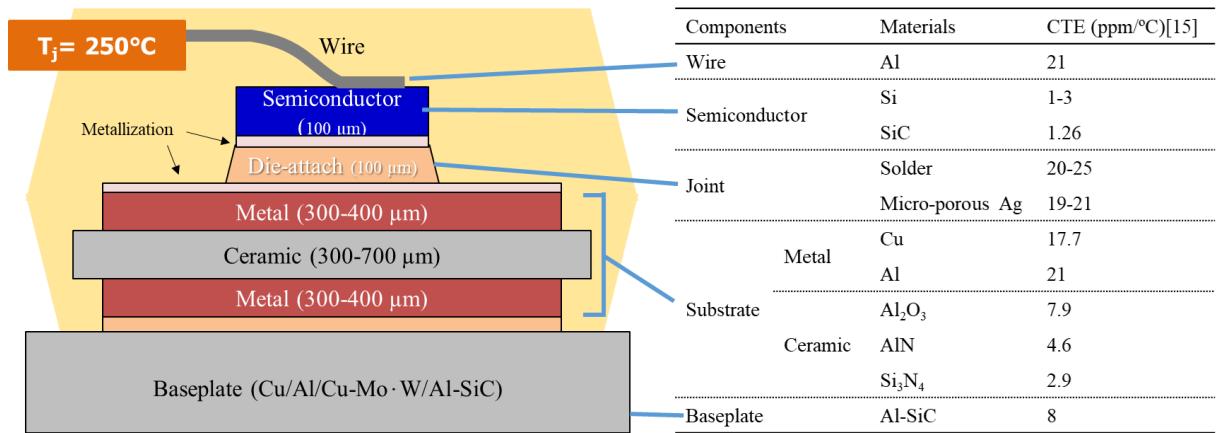

Generally, conventional power modules have a multi-layered packaging structure that includes five main components, namely, wires, semiconductor devices, die-attach joints, substrates, and baseplates, as shown in Fig. 1.2. Power devices are soldered to ceramic substrates such as direct bonded copper (DBC) and direct-bonded aluminum (DBA). Wires are interconnected between the devices and the metal layer in patterned substrates. Subsequently, the fabricated modules are bonded on a base plate by soldering.

Multilayered package structures are effective in reducing the volume of modules and dissipating heat. However, as seen in Fig. 1.1. To maximize the advantages of the power modules of WBG semiconductors, the modules must operate at a higher junction temperature of approximately 250 °C. In addition, its applications, such as automobiles, aircrafts, and space exploration, currently require power modules to operate in ambient thermal cyclic environments. In automobile industries, environment temperatures under the hood can reach or exceed 150 °C. It can also drop to – 40 °C and the temperature swing is repeated [12]. In aircrafts, the modules are thermally cycled using a wide temperature range from –55 °C to 300 °C and more [13, 14]. In such a high-temperature operating environment, high thermal stress occurs repeatedly at the interface of mutilated structure in a power module because of the mismatch of the coefficients of thermal expansion (CTE) among multiple layers, resulting in significant thermal damage and reliability problem. However, the existing conventional package materials are not appropriate, as they are limited to the maximum junction temperature of 175 °C.

To ensure the reliability of modules, new packaging materials with high damage resistance in extremely severe operation conditions must be developed, and their failure mechanism must be evaluated.

Fig. 1.2 Packaging structure, materials, and their coefficients of linear thermal expansion (CTE) property in high-temperature power modules.

### **1.1.3 High-temperature packaging material and its failure mechanisms**

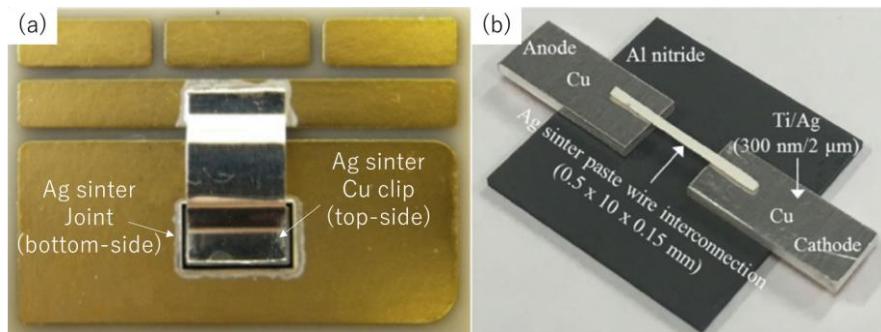

For high-temperature interconnection materials, several materials with excellent thermal and electrical properties, such as silver (Ag), gold, and copper (Cu), have been proposed as sinter joining pastes. Additionally, these materials have higher melting points than solder materials. Among them, Ag sinter pastes have been considered as the most promising joining materials because of their excellent characteristics. Ag sinter pastes exhibit a higher bonding strength, lower resistivity, and higher thermal reliability than Au–Sn solder and transient liquid phase (TLP) materials, which can be used at higher temperatures ( $> 250^{\circ}\text{C}$ ). Additionally, low-cost micron- and submicron-sized Ag pastes have been developed, thereby widening the possibility of using Ag sinter pastes in power electronics industries [16]. Recently, Ag pastes have been attempted to be widely used not only as joining materials but also for wire interconnections in the form of Ag clip bonding [17] and printed Ag sinter wire [18], as shown in Fig. 1.3.

The mechanism of property deterioration and microstructural changes in sintered Ag joints has been investigated under high temperature. In addition, grain growth, pore coarsening, and increasing porosity of sintered Ag joints in die attach have been studied as the mechanism of the strength decrease [19]. In a thermal shock environment, it was reported that a vertical crack occurred in a sintered Ag joint layer during a thermal shock test for temperatures from  $-50^{\circ}\text{C}$  to  $250^{\circ}\text{C}$  [20].

For power package substrates, both direct bonded aluminum (DBA) and active metal brazing (AMB) substrates have been considered as promising substrates for fabricating high-temperature power electronic modules because of their good thermal conductivity, low electrical resistance, and high insulation voltage. The aforementioned advantages are attributed to the metal/ceramic/metal sandwich structure of DBA/AMB substrates. Notably, DBA/AMB

substrates have a ceramic insulator plate composed of materials such as  $\text{Al}_2\text{O}_3$ ,  $\text{AlN}$ , and  $\text{Si}_3\text{N}_4$ . Both the sides of the insulator plate are metalized using aluminum (Al) or copper (Cu) to function as a thermal and electrical conductor layer. The as-prepared metal layer not only improves thermal conductivity but also creates electrical circuits on the insulator plate. However, the sandwich structure of DBA/AMB substrates also results in high thermomechanical stress, which is induced by the difference of CTEs between metal and ceramic in the sandwich structure during temperature cycling. Particularly, AMB substrates, which are bonded using a brazing process, have high thermal resistivity than that of the widely used direct bonded copper (DBC), which is bonded using eutectic bond. Although the need for high-temperature packaging technologies has been increasing, the reliability issues of DBA/AMB substrates still remain unaddressed.

Fig. 1.3 Applications of the Ag sinter paste: (a) joint and clip bonding and (b) printed Ag sinter wire [17, 18].

## **1.2 Real-time monitoring of thermal fatigue damage**

### **1.2.1 Traditional failure precursor monitoring**

Two types of lifetime prediction methods have been studied for power modules. The first method is based on failure mechanism. The lifetime prediction models are based on various failure mechanisms and describe the number of cycles to failure (Nf) as a function of failure-relevant temperature parameters such as the junction temperature swing ( $\Delta T_j$ ) and mean junction temperature (Tm). The second method is based on failure precursor parameters. Compared to the first method, this method is typically used to predict remaining useful life (RUL) and to monitor damage progress. Several studies have focused on thermal fatigue damage monitoring in both devices and packaging components, as listed in Table 1.2. However, there are certain disadvantages of second method:

1. It needs an additional electric circuit for monitoring [21].

2. It cannot predict the status of fatigue damage and time of failure [22].

3. Variation in one precursor parameter can affect the other parameters [23].

Table 1.2 Mechanism, causes, and precursors of failure in packaging components.

| Components         |                | Failure mode                      | Mechanism                      | Precursor parameter                                | Ref     |

|--------------------|----------------|-----------------------------------|--------------------------------|----------------------------------------------------|---------|

| Semiconductor      | Die            | - Short circuit                   | - Latch-up                     | - $V_{CE(ON)}$                                     |         |

|                    |                | - Burn-out                        | - Break-down                   | - $t_{off}$                                        | [24]    |

|                    |                | - Loss of gate control            |                                | - $G_E(t_{th})$                                    |         |

| Wire               | Bond pad       | - Void/Crack                      | - Metallization reconstruction | -                                                  | -       |

|                    |                |                                   |                                |                                                    |         |

|                    |                |                                   |                                |                                                    |         |

| Solder joint       | Bond interface | - Liftoff                         | - Fatigue<br>- Reconstruction  | - $t_{on}/t_{off}$<br>- $V_{CE(ON)}$<br>- $V_{GE}$ | [25-28] |

|                    |                |                                   |                                |                                                    |         |

|                    |                |                                   |                                |                                                    |         |

| Ceramic substrates | Heel           | - Heel cracking<br>- Wire burnout | - Fatigue<br>- Joule heating   | - $V_{CE(ON)}$                                     | [29]    |

|                    |                |                                   |                                |                                                    |         |

|                    |                |                                   |                                |                                                    |         |

| Ceramic substrates | Body           | - Void                            | - Stress corrosion             | -                                                  | -       |

|                    |                |                                   |                                |                                                    |         |

|                    |                |                                   |                                |                                                    |         |

| Ceramic substrates |                | - Crack<br>- Delamination         | - Fatigue or grain growth      | - $R_{th}$<br>- $V_{CE(ON)}$<br>- $t_{off}$        | [31-33] |

|                    |                |                                   |                                |                                                    |         |

|                    |                |                                   |                                |                                                    |         |

| Ceramic substrates |                | - Fracture                        | - Fatigue, Brittle fracture    | - $R_{th}$                                         |         |

|                    |                |                                   |                                |                                                    |         |

|                    |                |                                   |                                |                                                    |         |

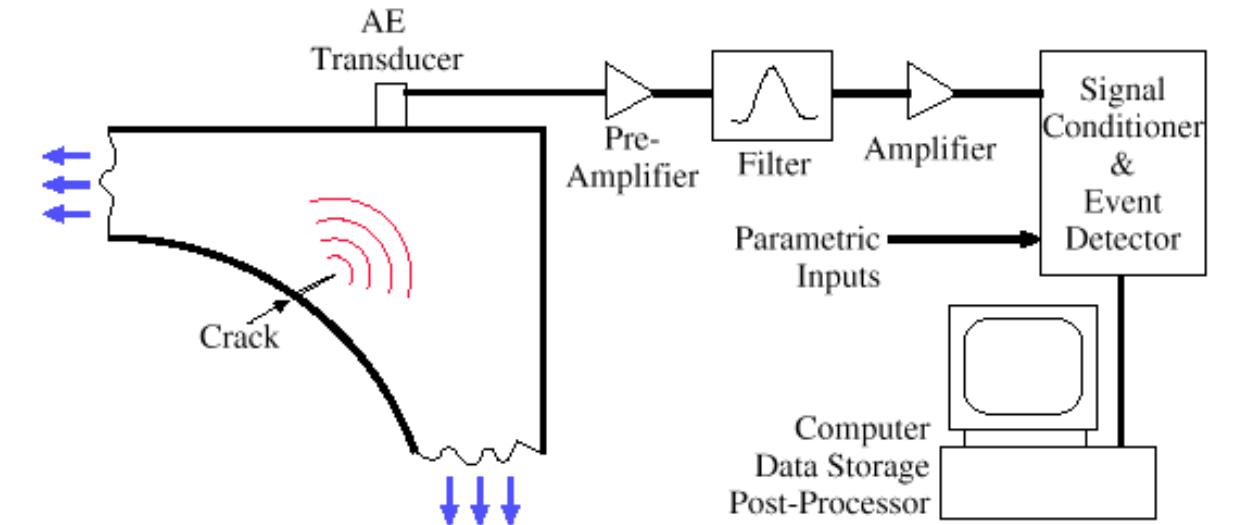

### **1.2.2 Definition and application of acoustic emission monitoring**

Acoustic emission is defined as a physical phenomenon that elastic energy is dynamically released as a result of material damage, as shown in Fig. 1.4. The released elastic energy propagates in the form of elastic waves inside the material. The waves that reach the surface cause surface deformations and can be detected using piezoelectric transducers. The detected elastic waves are transferred to electric signals called AE signals. AE signals contain damage information, as they result from a specific damage. The AE signals analysis enables various assessments. In the widest sense, acoustic emission is a technique for evaluating material damages by collecting and analyzing the released elastic waves [34, 35].

In metallurgical fields, the AE phenomenon was first studied in 1933 to evaluate the martensite transformation of Ni steel [36]. Thereafter, the AE system and method have been developed and extensively used for monitoring the damage of large structures such as bridges, pressure vessels, and wind turbines [37, 38]. Most AE methods have been standardized based on American Society for Testing and Materials (ASTM) standards (ASTM E 569, E 749, E 751, E 1067, E1139) [39]. In addition, several recent studies have applied the AE methods to evaluate fracture and cracks in advanced microelectronics such as ceramic-metal joints [40], lithium-ion batteries [41–43], multi-layered ceramic capacitors [44], and fuel cells [45].

An AE method is a nondestructive technique related to the passive monitoring of ultrasound. Passive-type AE methods offer significant advantage over other nondestructive techniques. Firstly, a sensor can measure damage in a wide area and the measurement system is much simpler. The AE signals arising from the damage can be detected by a sensor attached to the surface of a test object as the signals can spread in all directions within a solid. Secondly, standby power consumption is much lower for monitoring. Most nondestructive techniques usually input energy and collect the input energy after the reaction with test objects. The AE

method is a passive-type of technique, and thus, does not need to input energy. Thirdly, AE system is composed of fewer elements. Thus, it is easy to implement in industries. On the other hand, a modified scanning acoustic tomography (SAT) system was proposed to observe the degradation of power modules under power cycling test [46]. However, this system is still limited for the damage monitoring application of power modules in industries, as it is complex and bulky.

Fig. 1.4 AE signal generation, propagation, and detection [46].

### **1.2.3 Sources and characteristics of AE signals**

The AE signals are obtained from sources that rapidly release elastic energy. Based on the source mechanism, the AE sources can be broadly classified into three types: the primary source, the secondary source, and noise [48]. The following section describes the AE source mechanism and the characteristics of AE signals arising from the sources.

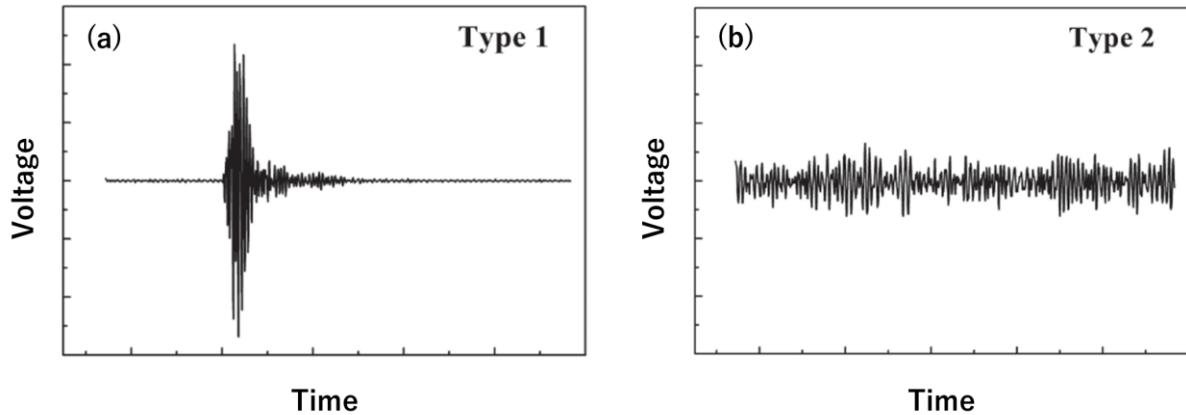

The primary sources produce AE signals when materials undergo permanent changes. The AE activity resulting from permanent changes can be explained based on the Kaiser effect [49]. Significant AE activity can be observed under a certain load. However, AE activity is not observed when a material is unloaded and reloaded, until the previous maximum load is reached. This indicates that permanent deformation in materials can release energy through elastic waves. Permanent changes are represented in the form of dislocation, deformation, crack initiation, and crack propagation. Such damages usually generate AE signals in the form of a discrete transient burst, as shown in Fig. 1.5(a). Burst AE signals have different characteristics depending on the source type. In particular, the amplitude of signals can significantly vary depending on both the deformation mechanism and material properties. The factors that affect the amplitude of an AE event are listed in Table 1.3 [50]. In secondary source mechanism, the AE signals are a result of frictional rubbing and bubbling, which accompany damages such as leaks and corrosion. These signals are commonly characterized by low amplitude and long duration as shown in Fig. 1.5(b).

Noise is defined as an elastic wave generated from a source that is not related to the purpose of AE monitoring. The noise cancelling technique for eliminating the signals arising from the noise sources is explained in section 1.3.4.

Fig. 1.5 Burst and continuous AE signals [41].

Table 1.3 Factors Affecting AE Response [50].

| Factors that increase the AE amplitude | Factors that decrease the AE amplitude |

|----------------------------------------|----------------------------------------|

| High strength                          | Low strength                           |

| High strain rate                       | Low strain rate                        |

| Low temperature                        | High temperature                       |

| Anisotropy                             | Isotropy                               |

| Non-homogeneity                        | Homogeneity                            |

| Thick sections                         | Thin sections                          |

| Brittle failure (cleavage)             | Ductile fracture (shear)               |

| Crack propagation                      | Plastic deformation                    |

| Large grain size                       | Small grain size                       |

#### 1.2.4 AE system configuration

The acoustic emission system consists of three parts: sensors for detecting the elastic waves, a preamp for amplifying the collected low-level signals, and a signal processing board for characterization and noise cancellation of the signals.

In general, elastic waves arising from these sources have frequencies from several kHz to 1 MHz. Elastic waves are detected by the AE sensor, which is usually fabricated using piezoelectric elements. Further, they are converted into electrical signals. Since the sensing characteristics of the sensors vary depending on the material of the piezoelectric element and its internal structure, it is important to use appropriate sensors considering the target damage event. Two types of AE sensors are used: broadband and narrowband (wideband) sensors. This division is based on the detectable frequency range of the elastic wave. The resonant sensor is used to collect the AE signals at certain frequencies with high sensitivity. However, the sensitivity characteristics of a particular frequency domain can also result in waveform deformation. Broadband sensors have sensitivity in a wide frequency band. They are used for waveform and frequency analysis without waveform deformation.

A preamplifier increases the sensitivity of the AE signals in the form of electrical signals (voltage-time curve), as shown in Fig. 1.5, compared to noise. The unit used for AE signals is  $\mu$ V, which can be expressed in decibels (dB). This is calculated using the logarithmic equation (1.1) based on the minimum perceived amplitude ( $V_0$ ) of 1  $\mu$ V (0 dB).

$$dB = 20\log \frac{V}{V_0} \quad (1.1)$$

The AE signals are analyzed in the final signal processing board, which is described in section 1.2.5.

### **1.2.5 AE signal characteristics and noise cancelling process**

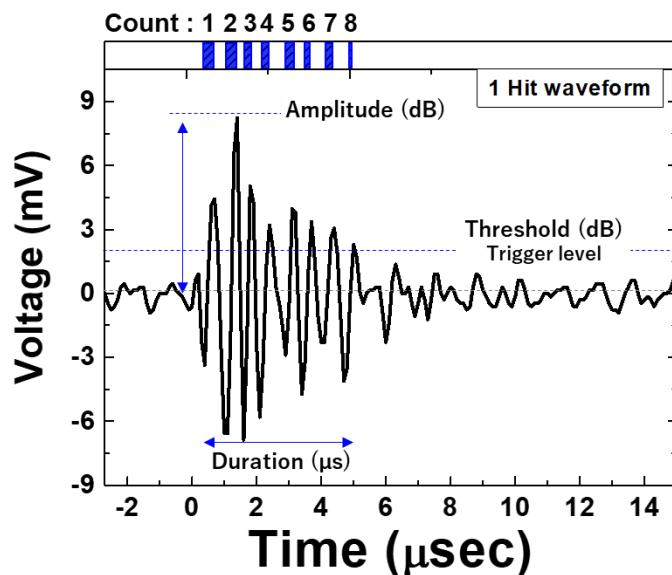

The characteristics of the AE signals can be used to evaluate material damage since these signals have an abundant amount of damage information. Fig. 1.6 shows an example of a signal waveform in time domain and the characteristic parameters extracted from the signal. The point at which the sound pressure is highest is defined as the peak and the sound pressure at this point is called amplitude. In particular, a signal is recorded when its amplitude is greater than or equal to the threshold value (i.e., threshold), which is the criterion for an effective signal. The recorded signal is called a hit. The number of times that a hit signal waveform exceeds the threshold is termed as counts. Counts and amplitude indicate the number and degree of damage, respectively, and are most often used as parameters for acoustic emission assessment. In addition, the length of time for which a sound pressure exceeds the threshold and stays above it is termed as duration.

Additionally, the frequency-domain characteristics of the AE signals can be analyzed using a fast Fourier transform (FFT) algorithm. Ideally, it is used to determine the AE source with the time-domain characteristics and to eliminate noise. In general, AE sources emit elastic waves with broadband frequencies ranging from 10 kHz to 1 MHz [51]. However, for common AE signals in metallic materials, the frequencies range from 100 kHz to 500 MHz [50]. The AE events arising from non-detrimental sources such as hydraulics and bearing movement are regarded as “background AE” or “noise”. These noise often occur at low frequencies (< 100 kHz) due to the nature of the source. Table 1.4 lists the frequency ranges of noise arising from various sources in nature and vehicle. The frequency for most of the noises ranges from several Hz to 100 kHz.

The noise cancelling method is performed in the following sequence: Firstly, the noise source is identified and fundamentally eliminated. Secondly, it should be noted that noise has a

lower level of amplitude compared to that of damage. Thus, when it is difficult to eliminate the noise sources, the noise is collected and noise amplitude is analyzed. Based on the amplitude of the collected noise, a reference voltage (i.e., threshold) is set. The signals are recorded when the amplitude of the signals exceeds this threshold. Thirdly, frequency range of the collected noise is analyzed. Noise can be filtered by using an analog high-pass filter (HPF) and low-pass filter (LPF) in a signal processing board. The filtering frequency value is set based on the frequency range database of the collected noise. The de-nosing process is most important in AE monitoring, as it can lead to major errors during accurate assessment of material damage.

Fig. 1.6 Illustration of commonly used AE parameters [41].

Table 1.4 Typical frequency range of noise in common industries.

| Source                | Frequency range (Hz) |

|-----------------------|----------------------|

| Suspension and wheels | 5–10                 |

| Engine                | 11–17                |

| Electric motor        | 50–80                |

| Human motion          | 0–40                 |

| Human voice           | 100–9500             |

| Music                 | 30–12000             |

### **1.3 Objective and outline of the thesis**

As mentioned in the previous sections, WBG power modules have demonstrated excellent potential toward achieving high efficiency and high power density performance for high-temperature operations. To ensure the reliability of WBG power modules at such high temperatures, the thermal degradation mechanism of high-temperature package materials such as sintered micro-porous Ag and DBA/AMB substrates must be understood. Therefore, this thesis focused on the study on the thermal degradation mechanism of package materials for high-temperature power modules. In addition, the real-time monitoring method for analyzing thermal damages in power modules was studied using the AE technique.

In Chapter 1, a brief description of the background of power electronics and emerging issues associated with the use of WBG semiconductors is introduced. The current candidates for high-temperature package materials and their reliability issues are also introduced. The current understanding on AE monitoring is also briefly discussed.

In Chapter 2, the thermal aging mechanism of sintered micro-porous Ag, which is a promising high-temperature joint material, is explored. The tensile strength and electrical resistivity of sintered Ag are evaluated during the thermal exposure at 250 °C. In addition, the changes in the grain and porous structure of sintered Ag are quantitatively characterized. Thermal aging mechanisms in sintered micro-porous Ag are discussed on the basis of the relationship between microstructural variations and mechanical/electrical properties.

In Chapter 3, the thermal shock damage mechanisms of DBA/AMB substrates with three types of ceramic plates and two types of Ni metallization are studied. The thermal shock resistance of DBA/AMB substrates is evaluated according to various material combinations. The mechanism of fractures, which are attributed to the Al creep deformation in DBA substrates, in Ni and Ni–P plating layers are discussed.

In Chapter 4, an attempt was made to monitor the fatigue damage occurring in the Al ribbon interconnection of discrete SiC Schottky barrier diode devices for the first time. The electrical switching noise signals are eliminated by a noise-cancelling process. During the power cycling test, AE signals were successfully collected. In addition, AE counts, which represent one of the time-domain parameters of AE signals, increased with the number of power cycles while fatigue cracks propagated in the Al ribbon. The AE count rate was significantly correlated with crack growth rate. On the basis of the relationship between AE activities and fatigue crack propagation, it is discussed that AE monitoring can be used for not only for understanding the fatigue propagation in Al ribbons but also monitoring the failure of power electronic devices.

In Chapter 5, a summary of the failure mechanisms in high-temperature power modules was presented. In addition, a real-time AE monitoring method was proposed as a novel monitoring technique for next-generation power modules.

## Reference

- [1] X. She, A. Q. Huang, and B. Ozpineci, “Review of silicon carbide power devices and their applications,” *IEEE Trans. Ind. Electron.*, vol. 64, no. 10, pp. 8193–8205, 2017.

- [2] J. Millan, P. Godignon, X. Perpina, A. Perez-Tomas, and J. Rebollo, “A survey of wide bandgap power semiconductor devices,” *IEEE Trans. Power Electron.*, vol. 29, no. 5, pp. 2155–2163, 2014.

- [3] J. Biela, M. Schweizer, S. Waffler, and J. W. Kolar, “SiC versus Si - evaluation of potentials for performance improvement of inverter and DCDC converter systems by SiC power semiconductors,” *IEEE Trans. Ind. Electron.*, vol. 58, no. 7, pp. 2872–2882, 2011.

- [4] M. Bhatnagar and B. J. Baliga, “Comparison of 6H-SiC, 3C-SiC, and Si for power devices,” *IEEE Trans. Electron Devices*, vol. 40, no. 3, pp. 645–655, 1993.

- [5] C. Buttay, D. Planson, B. Allard, D. Bergogne, P. Bevilacqua, C. Joubert, M. Lazar, C. Martin, H. Morel, D. Tournier, et al., “State of the art of high temperature power electronics,” *Mater. Sci. Eng. B Solid-State Mater. Adv. Technol.*, vol. 176, no. 4, pp. 283–288, 2011.

- [6] T. P. Chow, “High-voltage SiC and GaN power devices,” *Microelectron. Eng.*, vol. 83, no. 1 SPEC. ISS., pp. 112–122, 2006.

- [7] C. K. Chung, Y. J. Chen, W. M. Chen, and C. R. Kao, “Origin and evolution of voids in electroless Ni during soldering reaction,” *Acta Mater.*, vol. 60, no. 11, pp. 4586–4593, 2012.

- [8] S. Hazra, A. De, L. Cheng, J. Palmour, M. Schupbach, B. A. Hull, S. Allen, and S. Bhattacharya, “High switching performance of 1700-V, 50-A SiC power MOSFET over Si IGBT/BiMOSFET for advanced power conversion applications,” *IEEE Trans. Power Electron.*, vol. 31, no. 7, pp. 4742–4754, 2016.

- [9] M. R. Werner and W. R. Fahrner, “Review on materials, microsensors, systems, and devices for high-temperature and harsh-environment applications,” *IEEE Trans. Ind. Electron.*, vol. 48, no. 2, pp. 249–257, 2001.

- [10] P. Diaz Reigosa, H. Luo, and F. Iannuzzo Ge, “Implications of ageing through power cycling on the short circuit robustness of 1.2-kV SiC MOSFETs,” *IEEE Trans. Power Electron.*, vol. 8993, no. c, pp. 1–1, 2019.

- [11] P. Ning, R. Lai, D. Huff, F. Wang, K. Ngo, V. Immanuel, and K. Karimi, “SiC Wirebond Multichip Phase-Leg Module Packaging Design and Testing for Harsh Environment,” *IEEE Trans. Power Electron.*, vol. 25, no. 1, pp. 16–23, 2010.

- [12] B. J. Watson and G. Castro, “High-temperature electronics pose design and reliability challenges,” *Analog Dialogue*, vol. 46, no. 2, pp. 1–7, 2012.

- [13] D. Spry1, P. Neudeck, L. Chen, G. Beheim, R. Okojie, C. Chang, R. Meredith, T. Ferrier, and L. Evans, “Fabrication and testing of 6H-SiC JFETs for prolonged 500 °C operation in air ambient,” *Mater. Sci. Forum*, vol. 600–603, pp. 1079–1082, 2009.

- [14] P. G. Neudeck, R. S. Okojie, and L. Y. Chen, “High-temperature electronics - A role for wide bandgap semiconductors?,” *Proc. IEEE*, vol. 90, no. 6, pp. 1065–1076, 2002.

- [15] C. Choe, C. Chen, S. Noh, K. Suganuma, “Thermal shock performance of DBA/AMB substrates plated by Ni and Ni–P layers for high-temperature applications of power device modules,” *Materials*, vol. 11, pp. 2394-1-13, 2018

- [16] K. Suganuma, S. Sakamoto, N. Kagami, D. Wakuda, K. S. Kim, and M. Nogi, “Low-temperature low-pressure die attach with hybrid silver particle paste,” *Microelectron. Reliab.*, vol. 52, no. 2, pp. 375–380, 2012.

[17]S. Kraft, A. Schletz, and M. März, “Reliability of silver sintering on DBC and DBA substrates for power electronic applications,” *Integr. Power Electron. Syst. (CIPS)*, 2012 7th Int. Conf., no. December 2015, pp. 1–6, 2012.

[18]S. Noh, C. Choe, C. Chen, H. Zhang, and K. Suganuma, “Printed wire interconnection using Ag sinter paste for wide band gap power semiconductors,” *J. Mater. Sci. Mater. Electron.*, vol. 29, no. 17, pp. 15223–15232, 2018.

[19]H. Zhang, S. Nagao, K. Suganuma, H. J. Albrecht, and K. Wilke, “Thermostable Ag die-attach structure for high-temperature power devices,” *J. Mater. Sci. Mater. Electron.*, vol. 27, no. 2, pp. 1337–1344, 2016.

[20]C. Chen, C. Choe, D. Kim, Z. Zhang, and K. Suganuma, “Low-stress design of bonding structure and its thermal shock performance (– 50 to 250 °C) in SiC/DBC power die-attached modules,” *J. Mater. Sci. Mater. Electron.*, vol. 29, no. 16, pp. 14335–14346, 2018.

[21]U. M. Choi, F. Blaabjerg, and S. Jørgensen, “Power cycling test methods for reliability assessment of power device modules in respect to temperature stress,” *IEEE Trans. Power Electron.*, vol. 33, no. 3, pp. 2531–2551, 2018.

[22]A. Lahyani, P. Venet, G. Grellet, and P. J. Viverge, “Failure prediction of electrolytic capacitors during operation of a switchmode power supply,” *IEEE Trans. Power Electron.*, vol. 13, no. 6, pp. 1199–1207, 1998.

[23]H. Huang and P. A. Mawby, “A lifetime estimation technique for voltage source inverters,” *IEEE Trans. Power Electron.*, vol. 28, no. 8, pp. 4113–4119, 2013.

[24]N. Patil, J. Celaya, D. Das, K. Goebel, and M. Pecht, “Precursor parameter identification for insulated gate bipolar transistor (IGBT) prognostics,” *IEEE Trans. Reliab.*, vol. 58, no. 2, pp. 271–276, 2009.

[25]M. Held, P. Jacob, G. Nicoletti, P. Scacco, and M.-. Poech, “Fast power cycling test of IGBT modules in traction application,” in Proceedings of Second International Conference on Power Electronics and Drive Systems, 1997, vol. 1, pp. 425–430 vol.1.

[26]L. Zhou, S. Zhou, and M. Xu, “Investigation of gate voltage oscillations in an IGBT module after partial bond wires lift-off,” *Microelectron. Reliab.*, vol. 53, no. 2, pp. 282–287, 2013.

[27]V. Smet, F. Forest, J. J. Huselstein, A. Rashed, and F. Richardeau, “Evaluation of  $V_{ce}$  monitoring as a real-time method to estimate aging of bond wire-IGBT modules stressed by power cycling,” *IEEE Trans. Ind. Electron.*, vol. 60, no. 7, pp. 2760–2770, 2013.

[28]M. Tounsi, A. Oukaour, B. Tala-Ighil, H. Gualous, B. Boudart, and D. Aissani, “Characterization of high-voltage IGBT module degradations under PWM power cycling test at high ambient temperature,” *Microelectron. Reliab.*, vol. 50, no. 9–11, pp. 1810–1814, 2010.

[29]U. M. Choi, F. Blaabjerg, and S. Jørgensen, “Study on effect of junction temperature swing duration on lifetime of transfer molded power IGBT modules,” *IEEE Trans. Power Electron.*, vol. 32, no. 8, pp. 6434–6443, 2017.

[30]U. M. Choi, S. Jorgensen, and F. Blaabjerg, “Advanced accelerated power cycling test for reliability investigation of power device modules,” *IEEE Trans. Power Electron.*, vol. 31, no. 12, pp. 8371–8386, 2016.

[31]D. Xiang, L. Ran, P. Tavner, A. Bryant, S. Yang, and P. Mawby, “Monitoring solder fatigue in a power module using case-above-ambient temperature rise,” *IEEE Trans. Ind. Appl.*, vol. 47, no. 6, pp. 2578–2591, 2011.

[32]D. Xiang, L. Ran, P. Tavner, S. Yang, A. Bryant, and P. Mawby, “Condition monitoring power module solder fatigue using inverter harmonic identification,” *IEEE Trans. Power Electron.*, vol. 27, no. 1, pp. 235–247, 2012.

[33] Y. Xiong, X. Cheng, Z. J. Shen, C. Mi, H. Wu, and V. K. Garg, “Prognostic and warning system for power-electronic modules in electric, hybrid electric, and fuel-cell vehicles,” *IEEE Trans. Ind. Electron.*, vol. 55, no. 6, pp. 2268–2276, 2008.

[34] T. F. Drouillard and F. J. Laner, “Acoustic Emission: A Bibliography With Abstracts,” Springer US, 1979.

[35] U. S. A. Drouillard, Thomas F. “Acoustic emission: The first half century,” EG&G Rocky Flats, Inc., Golden, Colorado 80402, 1994.

[36] F. Förster and E. Scheil, “Acoustical study of formation of martensite needles,” *Naturwissenschaften*, vol. 28, no. 9, pp. 245–247, 1936.

[37] M. Eaton, “Acoustic Emission (AE) monitoring of buckling and failure in carbon fibre composite structures,” Cardiff University, 2007.

[38] S. K. J. Al-jumaili, “Damage assessment In complex structures using acoustic emission.,” Cardiff University, 2016.

[39] M. F. Carlos, “Overview of current and developing ASTM acoustic emission (AE) standards,” *J. Acoust. Emiss.*, vol. 28, pp. 229–233, 2010.

[40] S. Katsuaki, O. Taira, K. Mitsue, and S. Masahiko, “Acoustic emission from ceramic/metal joints on cooling,” *Am. Ceram. Soc. Bull.*, vol. 65, no. 7, pp. 1060–1064, 1986.

[41] C.-Y. Choe, W.-S. Jung, and J.-W. Byeon, “Damage evaluation in lithium cobalt oxide/carbon electrodes of secondary battery by acoustic emission monitoring,” *Mater. Trans.*, vol. 56, no. 2, pp. 269–273, 2015.

[42] K. Rhodes, N. Dudney, E. Lara-Curzio, and C. Daniela, “Understanding the degradation of silicon electrodes for lithium-ion batteries using acoustic emission,” *J. Electrochem. Soc.*, vol. 157, no. 2, pp. A1354–A1360, 2010.

[43]C. Villevieille, M. Boinet, and L. Monconduit, “Direct evidence of morphological changes in conversion type electrodes in Li-ion battery by acoustic emission,” *Electrochemistry Communications*, vol. 12, no. 10. pp. 1336–1339, 2010.

[44]S. Levikari, T. J. Karkkainen, C. Andersson, J. Tamminen, and P. Silventoinen, “Acoustic phenomena in damaged ceramic capacitors,” *IEEE Trans. Ind. Electron.*, vol. 65, no. 1, pp. 570–577, 2018.

[45]B. Legros, P. X. Thivel, Y. Bultel, M. Boinet, and R. P. Nogueira, “Acoustic emission: Towards a real-time diagnosis technique for Proton exchange membrane fuel cell operation,” *J. Power Sources*, vol. 195, no. 24, pp. 8124–8133, 2010.

[46]A. Watanabe, M. Tsukuda, and I. Omura, “Real time degradation monitoring system for high power IGBT module under power cycling test,” *Microelectron. Reliab.*, vol. 53, no. 9–11, pp. 1692–1696, 2013.

[47]H. Miinshiou, J. Liang, K. L. Peter, R. B. Charlie, S. Rodger, and L. K. Dwaine, “Using acoustic emission in fatigue and fracture materials research,” *Journal Eng. Mater.*, vol. 50, no. 11, pp. 1–14, 1988.

[48]J. R. Naumann, “Acoustic emission monitoring of small wind turbine blades,” *The University of Sheffie*, 2014.

[49]Knud G. Bøving, “Non-destructive examination methods for condition monitoring: Acoustic emission,” Butterworth-Heinemann, pp. 17–23, Jan. 1989.

[50]R. K. Miller and P. McIntire, “Acoustic emission testing, volume 5 of nondestructive testing handbook”, 2nd editio. American Society of Nondestructive Testing, 1987.

[51]P. T. Cole, “NDT Part 7. Acoustic emission,” *The British Institute of Non-Destructive Testing*, 1988.

## **Chapter 2**

### ***Thermal degradation mechanism of micro-porous silver die-attach***

## **2.1 Introduction**

To address high performance challenges of power modules, Si devices have been replaced with wide band-gap (WBG) semiconductors including silicon carbide (SiC) and gallium nitride (GaN), which allow power modules to be operated at high power densities and high temperatures above 250 °C [1][2]. Normally, power modules are manufactured by bonding semiconductors on power substrates with interconnect materials. However, the existing conventional solders are not suitable for WBG interconnect materials due to their poor reliability at high temperatures [3]. To ensure high temperature operation of WBG semiconductors, numerous joint materials with high melting points, excellent thermal and electrical properties such as silver, gold and copper have been proposed.

Silver (Ag) sinter pastes have been considered as promising joint materials due to various advantages such as high bonding strength, low resistivity and excellent thermal reliability, compared with Au-Sn solder and nano copper sinter paste, all of which can be used at higher temperature (>250 °C) [4][5]. Additionally, low-cost micron- and submicron-sized Ag pastes have been developed in recent [6] compared to high-cost nano Ag sinter paste, enlarging the possibility of Ag sinter paste in the power industries. However, a large amount of thermal stress induced by the mismatch in coefficients of thermal expansion (CTE) causes various microstructural changes and properties deterioration in sintered Ag joints during long-term high temperature exposure.

The mechanism of properties deterioration and microstructural changes in sintered Ag joints have been investigated under high temperature exposure [7][8]. Grain growth, pore coarsening, increasing porosity of sintered Ag joints in a die-attach have been studied as the mechanism of strength decreases [9][10][11]. However, the strength decreases of a die-attachment structure can be affected by degradation of sintered Ag joints as well as the other

components including chips, metallization and substrates. For this reason, it is difficult to certainly understand relationship between strength decreases, and observed microstructure changes. Moreover, changes in grain and pore structure were also related with electrical properties which is another most important properties for joint materials. However, the effect of thermal exposure on electrical properties were not reported. Therefore, it is important to investigate relationship between mechanical/electrical properties deterioration and microstructure variation during high temperature exposure by using sintered Ag specimens, in order to eliminate other component effect and understand the relationship.

In this work, the effect of thermal exposure on mechanical and electrical properties and microstructural changes on sintered porous Ag during thermal exposure was demonstrated. The tensile strength and electrical resistivity of sintered Ag were evaluated. Changes in grains and porous structure of sintered Ag were quantitatively characterized. This relationship between microstructural variations and mechanical and electrical properties were discussed.

## **2.2 Experimental**

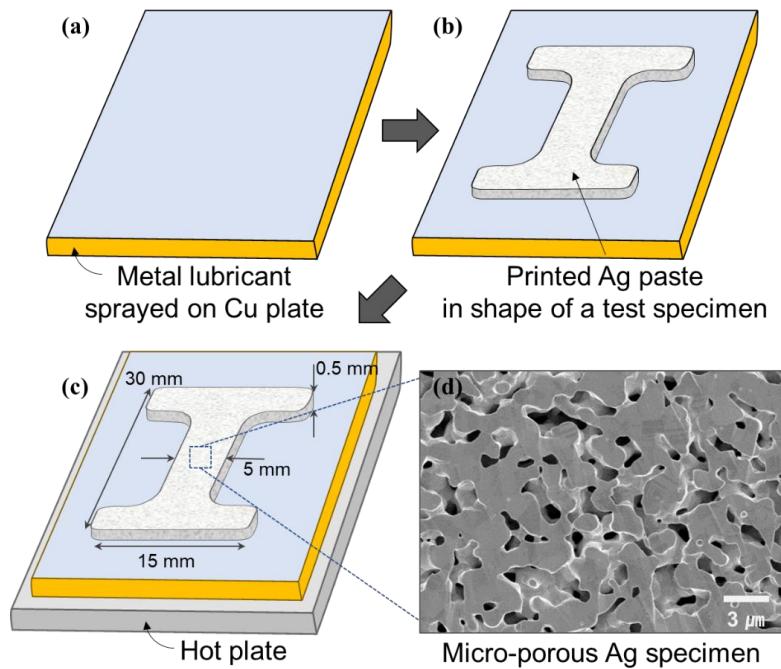

### **2.2.1 Fabrication of sintered porous Ag specimens**

Two types of Ag particles with different sizes and shapes were mixed to be a “Hyblid paste”. Ag flakes have an average lateral length of 5  $\mu\text{m}$  and thickness of 260 nm (Fukuda metal Co.). The others are Ag spherical particles with an average diameter of 400 nm (Mitsuimining and smelting Co.) [6]. The Ag paste was made by mixing them and ethylene glycol (EG) at a weight ratio of 5:5:1 to control paste viscosity. Fig. 2.1 (a-c) show the manufacturing process of Ag specimens for tensile strength and electrical resistivity measurements. First, Cu plates were sprayed with boron nitride lubricant to prevent bonding between Ag paste and Cu plates during a sintering process (Fig. 2.1 (a)). Ag paste was printed in the shape of a test specimen by using screen mask on the pre-treated Cu plates as shown in Fig. 2.1 (b). Afterwards, the Ag paste was sintered at 250  $^{\circ}\text{C}$  for one hour without pressure on the hot plate as shown in Fig. 2.1 (c). After sintering, Ag specimens were easily detached from Cu plates. The width and thickness of the sintered Ag specimens were 5 mm and 0.5 mm, respectively. The micro-porous structure of sintered Ag specimens was confirmed by SEM observation, as shown in Fig. 2.1 (d).

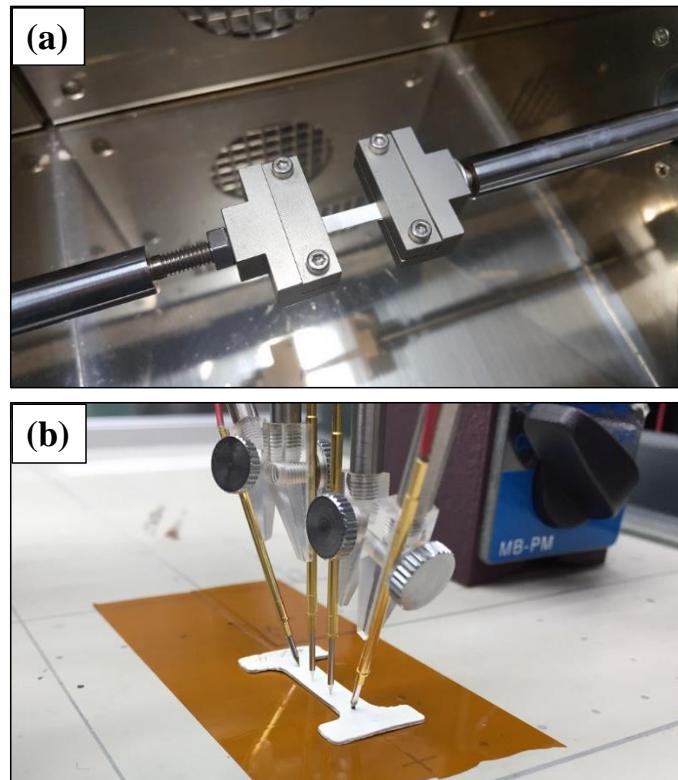

### 2.2.2 Characterization of mechanical/electrical properties

To characterize changes in sintered Ag during thermal exposure, Ag specimens were exposed at 250 °C for different exposure times of 0, 50, 200, 500, and 1000 hours in air. To evaluate the deterioration of mechanical and electrical properties, tensile tests and electrical resistivity measurements were conducted on the aged Ag specimens, as shown in Fig. 2.2 (a) and (b), respectively. Tensile strength was tested by a universal testing machine (Tytron 250, MTS Co.) at a strain rate of  $1.0 \times 10^{-5}$ /s. Electrical resistivity was measured by a four probe test with span distance of 5 mm. Source currents were supplied from 500 mA to 1,000 mA.

### 2.2.3 Microstructural observation

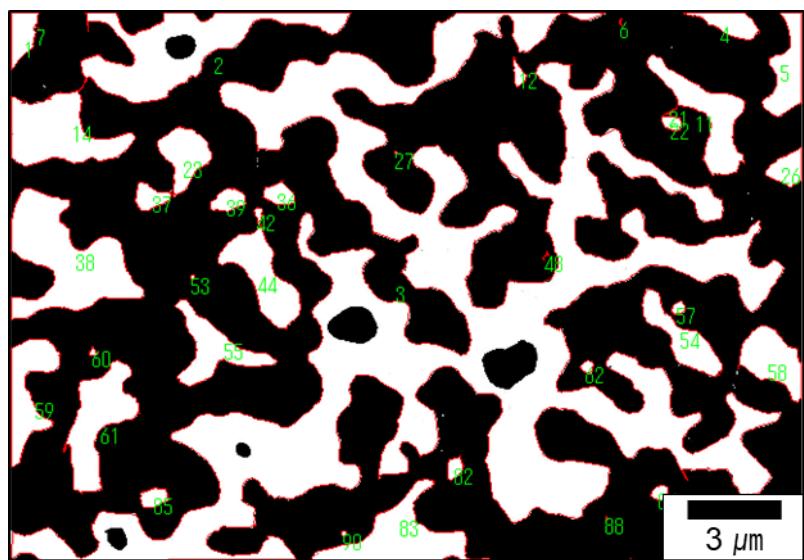

To observe microstructural changes, Ag grains and porous structure of the aged Ag specimens were evaluated. The cross-section of each Ag specimen being aged for different thermal exposure times was prepared by ion-milling. The Ag grain size and number was characterized by electron backscatter diffraction (EBSD). EBSD data for aged Ag specimens was collected using a step size of 0.1  $\mu$ m. The porous structure including pore size, number and porosity was observed by a field emission scanning electron microscope (FE-SEM) as shown in Fig. 2.1 (d). To automatically distinguish between sintered Ag and pores, the observed SEM images were processed into black and white by using image-processing software (IPWin) as shown in Fig. 2.3. The sintered Ag and pore area were transformed to black and white, respectively. Afterwards, pore size, number and porosity were measured. The average area of a pore was used as pore size. To evaluate fracture mode, fracture surface was observed by FE-SEM after tensile test.

Fig. 2.1 Fabrication process of Ag specimens for tensile and four probe tests (a-c) and its micro-porous structure observed by SEM (d).

Fig. 2.2 Configuration of a tensile test (a) and four probe resistivity measurement (b) for sintered Ag specimens.

Fig. 2.3 Automatic measurement of pore area and number of sintered Ag.

## 2.3 Results and discussion

### 2.3.1 Deterioration of tensile strength and electrical resistivity

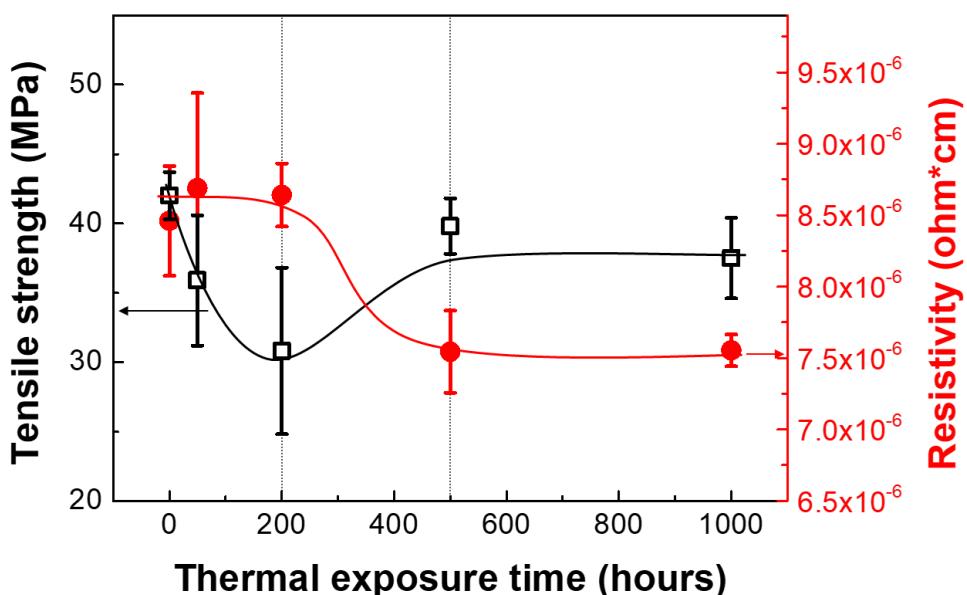

Fig. 2.4 shows changes in tensile strength and electrical resistivity under high temperature exposure. Initial porous Ag has a tensile strength of 42 MPa and an electrical resistivity of  $8.5 \times 10^{-6} \Omega\text{cm}$  after being sintered at  $250^\circ\text{C}$  for 1 hour. The tensile strength was altered during thermal exposure time. According to the strength change trends, the change in the tensile strength was divided into three distinct stages. Tensile strength gradually decreased during thermal exposure time up to 200 hours. However, the reduced strength of aged Ag almost fully returned to its initial value during thermal exposure time from 200 hours to 500 hours. The recovered strength was maintained for up to 1000 hours of thermal exposure time. On the other hand, the electrical resistivity of sintered Ag did not change during the first 200 hours of thermal exposure, but significantly decreased from 200 to 500 hours and kept the reduced resistivity. This change tendency of both strength and resistivity occurs in the same exposure time of 200 and 500 hours. To investigate the reason of properties change, microstructure after each exposure time was observed.

Fig. 2.4 Deterioration of tensile strength and resistivity of sintered Ag during thermal exposure.

### 2.3.2 Changes in Ag grains and porous structure

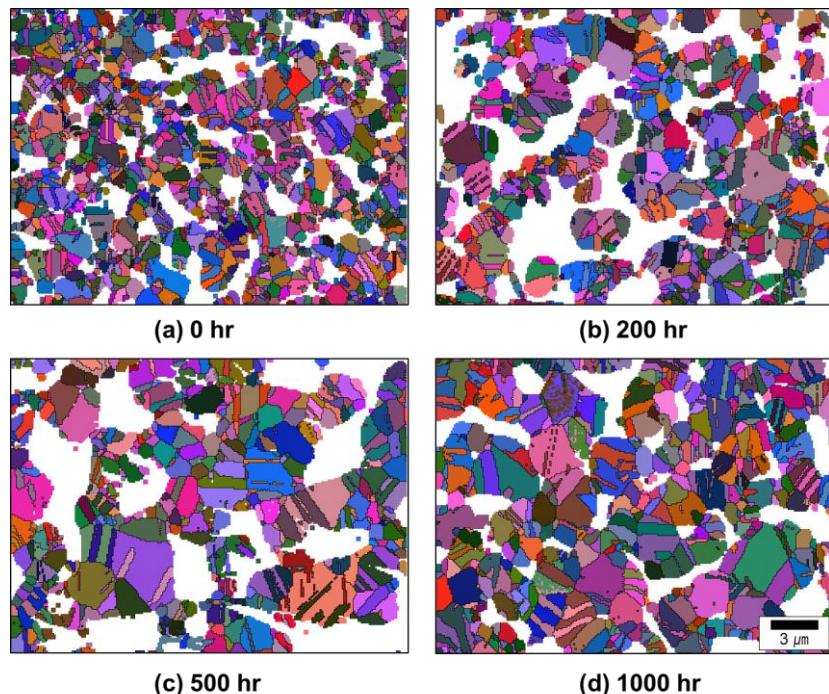

Fig. 2.5 shows grains of sintered Ag at different thermal exposure times. Pores were indicated in white areas. At the initial state, sintered Ag had numerous fine Ag grains as shown in Fig. 2.5 (a). After thermal exposure, the Ag grains became bigger and fewer. To quantitatively evaluate microstructure changes including Ag grains and pores, their size and number were measured and the results are shown in Fig. 2.6 and Fig. 2.7, respectively.

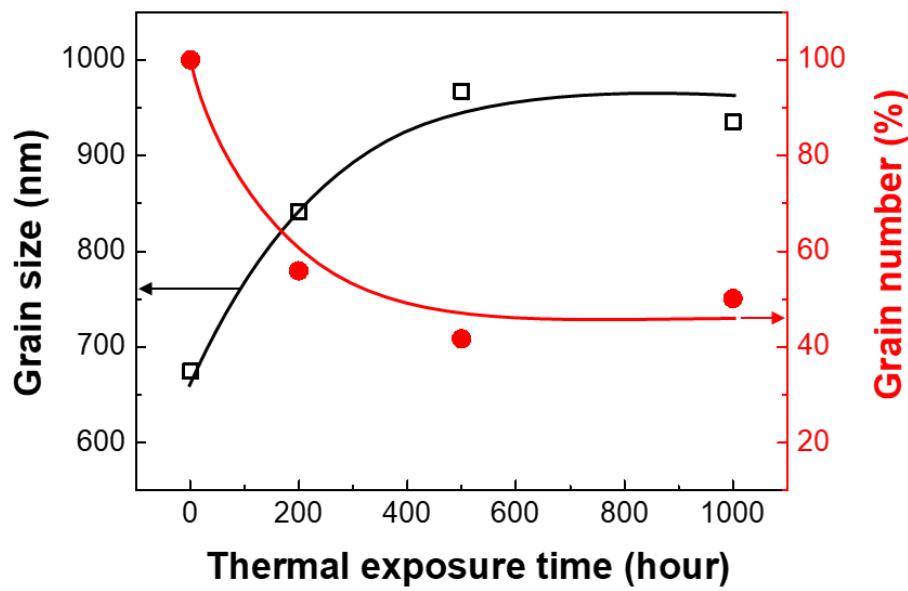

Fig. 2.6 quantitatively shows the changes in grain size and number of sintered Ag in thermal exposure. The average Ag grain size increased with thermal exposure time up to 500 hours, while the grain number decreased. The Ag grain growth indicated an exponential increase, and its trend was similar with that of general fine-grained materials. Fig. 2.7 shows the changes in pore average area and number of sintered Ag during thermal exposure time. The average area of pores was used to represent pore size. The pore number at different thermal

Fig. 2.5 EBSD observation of Ag specimens after different exposure times; (a) 0 h, (b) 200 h, (c) 500 h and (d) 1,000 h.

Fig. 2.6 Variation in Ag grain size and number with thermal exposure time.

Fig. 2.7 Variation in average pore area and number with thermal exposure time.

exposure time was automatically counted in  $17\mu\text{m} \times 25\ \mu\text{m}$  area, and it was expressed in percentiles based on the initial pore number. This pore size increased with increasing thermal exposure time, while the pore number decreased. Although the most pore coarsening occurred before 200 hours, pore coarsening with pore number reduction occurred until 500 hours.

Fig. 2.8 shows the change in porosity of sintered Ag during thermal exposure time. Porosity was measured by calculating the ratio of pore area to observed area of  $425\ \mu\text{m}^2$  [12]. The porosity of sintered Ag that was exposed for 0, 200, 500 and 1000 hours was 38 %, 37 %, 29 % and 31 %, respectively. The porosity of sintered Ag decreased with exposure time up to the first 500 hours. In the whole of thermal exposure period, most of the porosity reduction of sintered Ag occurred from 200 hours to 500 hours of thermal exposure time.

Grain growth, pore coarsening and porosity reductions occurred in thermal exposure. Among them, the size of grain and pore simultaneously increased with thermal exposure time. When polycrystalline materials are exposed to high temperature, grain size grows to reduce the interface energy of numerous grain boundaries through the migration of these grain boundaries [13]. During this grain growth process, pores also simultaneously migrate along with the migration of grain boundaries, resulting in pore coarsening [14]. This driving force to reduce the surface energy promotes Ag grain growth as well as pore coarsening. As a result, Ag grain growth and pore coarsening seems to occur at the same time.

On the other hand, the most porosity reduction in sintered Ag occurred in the thermal exposure period from 200 to 500 hours. Such silver porosity reduction was observed in sintered Ag joints [8]. The porosity in sintered Ag joints decreased with thermal exposure time, especially from 100 to 500 hours, which is similar with that observed in bare sintered Ag from 200 to 500 hours. When sintered Ag is exposed to high temperatures, its porosity reduction is generated by a driving force to reduce surface energy [15]. The driving force is the same with those of grain

growth and pore coarsening. The porosity reduction in sintered Ag seems to be related with grain growth and pore coarsening.

The grain growth, pore coarsening and porosity reduction occurred between exposure times of 200 and 500 hours, similarly with deterioration trends in mechanical/electrical properties as shown in Fig. 2.4.

Fig. 2.8 Variation in porosity of sintered Ag with thermal exposure time.

### 2.3.3 Relationship between mechanical/electrical properties and microstructural variation