|              |                                                                                             |

|--------------|---------------------------------------------------------------------------------------------|

| Title        | Proactive Supply Noise Mitigation and Design Methodology for Robust VLSI Power Distribution |

| Author(s)    | 陳, 俊                                                                                        |

| Citation     | 大阪大学, 2020, 博士論文                                                                            |

| Version Type | VoR                                                                                         |

| URL          | <a href="https://doi.org/10.18910/76645">https://doi.org/10.18910/76645</a>                 |

| rights       |                                                                                             |

| Note         |                                                                                             |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

Proactive Supply Noise Mitigation and Design

Methodology for Robust VLSI Power Distribution

Submitted to

Graduate School of Information Science and Technology

Osaka University

January 2020

Jun CHEN

# Publications

## Journal Article (Refereed)

- [J1] Jun Chen, Hajime Kando, Toshiki Kanamoto, Cheng Zhuo, and Masanori Hashimoto, “A Multicore Chip Load Model for PDN Analysis Considering Voltage-Current-Timing Interdependency and Operation Mode Transitions,” *IEEE Transactions on Components, Packaging and Manufacturing Technology*, vol. 9, no. 9, pp. 1669–1679, Sept. 2019.

## International Conference Papers (Refereed)

- [I1] Jun Chen, Toshiki Kanamoto, Hajime Kando, and Masanori Hashimoto, “An on-chip load model for off-chip PDN analysis considering interdependency between supply voltage, current profile and clock latency,” in *2018 IEEE 22nd Workshop on Signal and Power Integrity (SPI)*, May 2018.

- [I2] Jun Chen and Masanori Hashimoto, “A Frequency-Dependent Target Impedance Method Fulfilling Both Average and Dynamic Voltage Drop Constraints,” in *2019 IEEE 23rd Workshop on Signal and Power Integrity (SPI)*, Jun. 2019.

## Domestic Conference Papers (Unrefereed)

- [D1] Toshiki Kanamoto, Koki Kasai, Masashi Imai, Atsushi Kurokawa, Masanori Hashimoto, Jun Chen, and Hajime Kando, “Optimization of Re distribution Layer and On chip Capacitors for LSI with FOWLP,” in *DA Symposium*, 2018 (in Japanese).

- [D2] Toshiki Kanamoto, Koki Kasai, Masashi Imai, Atsushi Kurokawa, Masanori Hashimoto, Jun Chen, and Hajime Kando, “LSI Package Board Power Delivery Network Modeling for Capacitor Placement Optimization at 15nm Node,” in *DA Symposium*, 2017 (in Japanese).

# Summary

With the scaling down of the technology node, both power consumption, and supply noise are continuously increasing in modern VLSI designs. The emergent power supply noise through the power delivery network (PDN) can eventually degrade the chip timing performance or even cause malfunction. Therefore, an effective supply noise mitigation system and PDN design methodology are critically important to ensure robust VLSI power distribution.

Designing a high-quality low noise PDN system is a complex and challenging task, which requires many efforts from PDN design stage to operation stage and extensive consideration throughout PDN components. For example, using switched capacitor voltage regulator (SCVR) as the power supply solution involves supply voltage ripple. Parasitic resistance and inductance of PDN can induce dynamic voltage drop by load current variation. At the chip load stage, supply noise degrades chip operation performance. Meanwhile, chip operation variation brings load current variation, which in turn, causes supply noise. Jointly considering these interdependent and heterogeneous aspects is the major difficulty in PDN design and noise mitigation.

Traditionally, PDN designers rely on a simple voltage guard bound as design guidance. Following such guidance, designers assume a max allowed voltage drop, and then determine the parameters of PDN components to meet the voltage drop constraints. To explore PDN parameters and verify the performance, considerable design time and run-time efforts are necessary. Next, a reactive noise mitigation system is introduced to dynamically regulate the load voltage such that the voltage guard bound is maintained during the operation stage. Nevertheless, designers just blindly believe the chip performance is ensured if voltage guard bound guidance is followed.

However, for large VLSI designs such as many-core systems, activity variation among multiple cores can result in considerable emergent large power requirements within tens of clock cycles. Therefore, the traditional voltage guard bound guidance is very difficult to meet at the PDN design stage because the allowed PDN impedance can be as small as micro Ohms across the wide frequency range. Moreover, during the system operation stage, the traditional reactive noise mitigation system fails to compensate such emergent supply noise due to systematic issues such as voltage sensing latency, voltage boosting latency through PDN, and limited voltage scaling capability. Finally, even with a dedicated noise mitigation control system and PDN design, the actual chip

performance impact is still invisible to PDN designers due to using the over-simplified load model. Such an issue can, in turn, mislead the PDN and noise mitigation system design, resulting in under- or over-designed PDN system and unexpected supply noise impact. Besides, with the rising popularity of machine learning technology, the proactive noise mitigation system based on chip load power/current prediction instead of reactive one is discussed to conceal the PDN latency. However, the mitigation solution either suffers from high hardware overhead or low prediction accuracy. Hence, the practical proactive supply noise mitigation and design methodology for off-chip PDN remains an open problem.

To put proactive noise mitigation into practical and improve the PDN design methodology, there are two major challenges need to be addressed. The first is negative loop challenge of proactive noise mitigation. A proactive noise mitigation controller requires a long-term accurate power/current prediction to conceal the PDN voltage setup latency. However, existing long-term prediction requires high computation cost and consequently long computation latency. Besides, traditional switched capacitor voltage regulator (SCVR) is a common off-chip power supply solution, but off-chip SCVR has limited voltage scaling flexibility and long response time. These two bottlenecks demand further longer-term prediction. Such a negative loop makes proactive noise mitigation suffer from either high hardware overhead or low prediction accuracy. Various works are proposed to address this challenge. For example, low dropout (LDO) voltage regulator is proposed to achieve fast noise mitigation response, but at the cost of heat generation and low energy efficiency. Multi-ratio SCVRs are also studied but the output ripple and limited voltage scaling level remain open problems. Till now, practical methodology to design a proactive noise mitigation system has not been established.

The second challenge is the design gaps in PDN design methodology. The first gap exists between PDN design constraints and target impedance design. Target impedance methodology is a common practice to bridge the PDN impedance with voltage drop constraints. However, actual PDN impedance is defined in the frequency domain while the voltage drop constraints are given in the time domain. Although the current spectrum tells us that dynamic power noise distributes within a certain frequency range, how to determine detailed frequency-dependent target impedance remains an open problem. The second gap exists between on-chip timing information, and off-chip PDN verification and exploration. Conventionally, very simple load models are provided to off-chip PDN designers, and hence on-chip behavior cannot be analyzed by them for PDN verification. Besides, supply voltage and clock frequency may be controlled for each core or a group of cores. Such a system behavior affects the power supply noise significantly, but due to its complexity, it is difficult for on-chip designers to construct even a simple chip load model for PDN configuration exploration purposes. Without the critical on-chip timing information, existing over-simplified PDN design methodology can mislead the PDN design, resulting in under- or over-designed PDN, and under- or over-estimated supply noise impact.

---

This dissertation proposes the proactive supply noise mitigation and PDN design methodology by addressing the above two challenges. For the first negative loop challenge, this dissertation manages to break the negative loop from two aspects. The first is to lighten the prediction cost by developing a lightweight short-term average current predictor. The second is to relieve the prediction length requirement by introducing a scalable major-minor voltage regulator (MMVR) structure. For the second design gap challenge, this dissertation proposes a frequency-dependent target impedance design methodology that considers the constraints of both average and dynamic voltage drops. A concept of magnitude equivalent frequency (MEF) is proposed to simplify the frequency-dependent target impedance design. To validate and explore the noise impact, this dissertation proposes a chip load model that can provide the on-chip timing information, replay detailed voltage-dependent current profile, and extensively explore the inter-core operation mode variation within a short run-time.

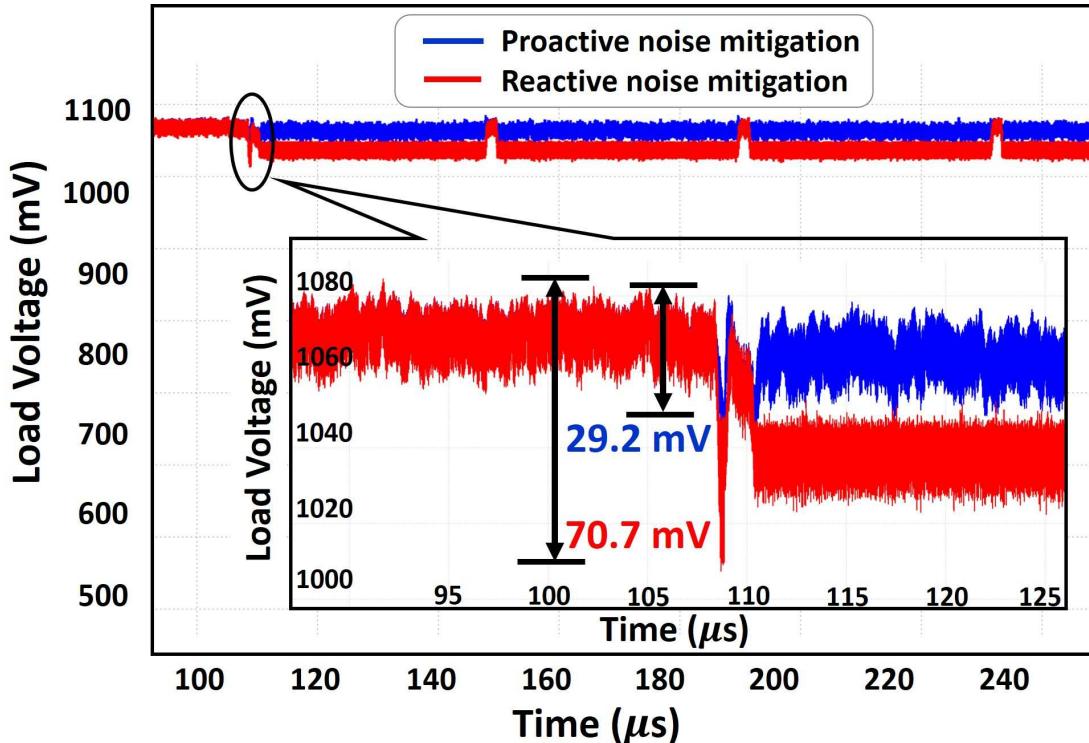

With the proposed methods, firstly a lightweight current predictor is derived, which consists of six-layer decision tree regressor and achieves over 0.99 correlation for 50-cycle-ahead prediction. Secondly, the proposed MMVR power supply solution achieved over 3X voltage scaling range compared with traditional SCVR while the ripple is within 16mV, which is 1.6% of load voltage. The proactive noise mitigation system is constructed using MMVR and predictor. Experimental results with a multi-core RISC-V design show that the proposed proactive mitigation system can mitigate the supply noise within 30mV while the noise exceeds 70mV with the conventional reactive mitigation. Also, the average supply voltage is compensated during the full operation period. Thirdly, the frequency-dependent target impedance is obtained which fulfills the voltage drop constraints. Experiments confirm that the synthesized target impedance satisfied the constraints with less than 0.1% error in the actual processor load case. Fourthly, a compact chip load model is derived, which is mostly described by Verilog-A. Experimental results show that the proposed model reproduces the current profile, current peak, and timing data well even while it achieves over 300X run-time reduction compared to a transistor-level model. It is also experimentally demonstrated that land side capacitor is helpful to improve processor timing performance in test cases.

The proactive noise mitigation methodology discussed in this dissertation helps to relieve the emergent supply noise so that the robustness for VLSI power distribution can be ensured. The methods proposed in this dissertation are also helpful for PDN designers to mitigate the over- or under-designed PDN impacts, and reduce the design cost and iteration time by facilitating the PDN verification and exploration process.

# Acknowledgments

First of all, I would like to express my deepest gratitude to Professor Masanori Hashimoto in Osaka University for providing me a precious opportunity and an excellent environment to study as a doctoral student in his laboratory. All of my productive researches are credited to none other than him. His advanced perspective and thoughtful advice led me to the achievements.

I would like to appreciate Professor Tatsuhiro Tsuchiya, Professor Tetsuya Hirose, and Associate Professor Hiromitsu Awano in Osaka University for detailed reviews and insightful suggestions.

I would like to appreciate Associate Professor Jaehoon Yu in Tokyo Institute of Technology, Professor Yoshinori Takeuchi in Kindai University, Professor Toshiki Kanamoto in Hirosaki University, Professor Cheng Zhuo in Zhejiang University for the precious suggestions and enormous help throughout my doctoral research.

My appreciation also goes to Mr. Hajime Kando in Murata Manufacturing Co., Ltd for technical discussions and suggestions on power delivery network modeling and chip load modeling.

I would like to express my sincere appreciation to Assistant Professor Yutaka Masuda in Nagoya University, and Dr. Wang Liao in Kochi University of Technology, for precious discussions and support.

I would like to thank other colleagues who belong or belonged to the Integrated System Design Laboratory in Osaka University for daily discussions and their support: Dr. Tomoki Sugiura, Dr. Koichi Mitsunari, Mr. Ryutaro Doi, Mr. Pei-Hao Chen, Mr. Tai-Yu Cheng, Mr. Ryo Shirai. I express my heartfelt thanks to all members of the Integrated System Design Laboratory in Osaka University for having an interesting and comfortable time in the laboratory. I would like to thank the laboratory secretary Mrs. Asako Murakami for her various support.

Finally, I would like to extend my gratitude to my parents (Yimin Chen and Guiying Liu), Miss Ziyan Li, other relatives and friends. They always support me and encourage me with their best wishes, inspiration, and suggestion.

# Contents

|          |                                                                        |           |

|----------|------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                    | <b>1</b>  |

| 1.1      | Background . . . . .                                                   | 1         |

| 1.1.1    | Power Delivery Network and Supply Noise . . . . .                      | 4         |

| 1.1.2    | Low Noise PDN Design Methodology . . . . .                             | 7         |

| 1.1.3    | Supply Noise Mitigation System . . . . .                               | 9         |

| 1.2      | Major Challenges for Robust Power Distribution . . . . .               | 10        |

| 1.2.1    | Negative Loop Challenge of Supply Noise Mitigation . . . . .           | 10        |

| 1.2.2    | Gap Challenge in PDN Design Methodology . . . . .                      | 13        |

| 1.3      | Objective and Organization . . . . .                                   | 18        |

| <b>2</b> | <b>Lightweight Short-Term Current Prediction</b>                       | <b>21</b> |

| 2.1      | Introduction . . . . .                                                 | 21        |

| 2.2      | Overall Structure of Proposed Proactive Noise Mitigation . . . . .     | 22        |

| 2.3      | Lightweight Short-Term Current Predictor . . . . .                     | 23        |

| 2.3.1    | Prediction Label Construction . . . . .                                | 23        |

| 2.3.2    | Prediction Feature Construction . . . . .                              | 25        |

| 2.3.3    | Predictor Engine and Implementation Cost . . . . .                     | 27        |

| 2.4      | Noise Mitigation Controller . . . . .                                  | 27        |

| 2.5      | Experimental Results . . . . .                                         | 28        |

| 2.6      | Extended Discussion on Out-of-Order Processor . . . . .                | 32        |

| 2.7      | Conclusion . . . . .                                                   | 33        |

| <b>3</b> | <b>Low-Latency Voltage Scaling Using Major-Minor Voltage Regulator</b> | <b>35</b> |

| 3.1      | Introduction . . . . .                                                 | 35        |

| 3.2      | Scalable Major-Minor Voltage Regulator . . . . .                       | 36        |

| 3.3      | Experimental Results . . . . .                                         | 38        |

| 3.3.1    | MMVR Performance Experiment . . . . .                                  | 39        |

| 3.3.2    | Proactive Versus Reactive Noise Mitigation . . . . .                   | 40        |

| 3.4      | Conclusion . . . . .                                                   | 42        |

|                                                                       |           |

|-----------------------------------------------------------------------|-----------|

| <b>4 Frequency-Dependent Target Impedance Methodology</b>             | <b>43</b> |

| 4.1 Introduction . . . . .                                            | 43        |

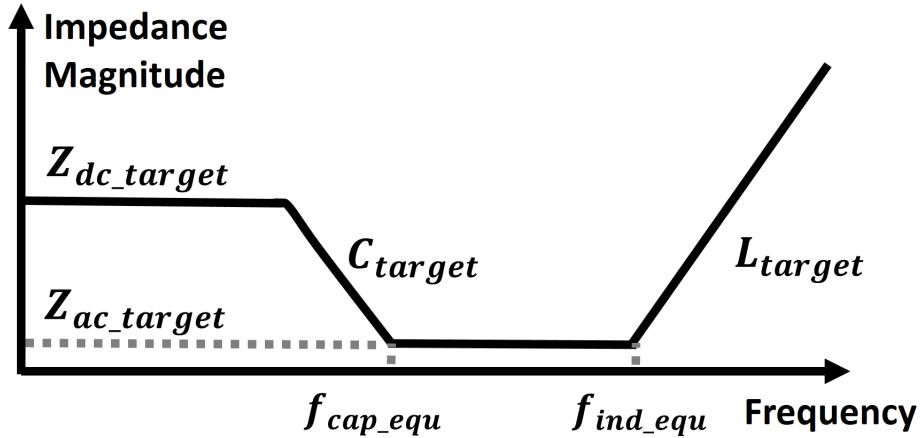

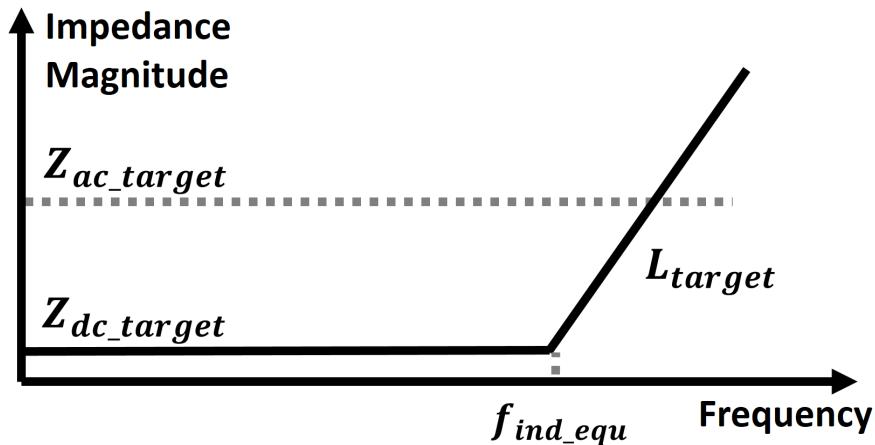

| 4.2 Overall Flow and Basic Impedance Shapes . . . . .                 | 44        |

| 4.3 Magnitude Equivalent Frequency (MEF) . . . . .                    | 46        |

| 4.3.1 MEF for Capacitance Dominant Impedance . . . . .                | 46        |

| 4.3.2 MEF for Inductance Dominant Impedance . . . . .                 | 47        |

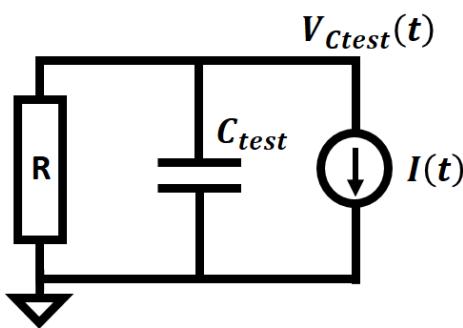

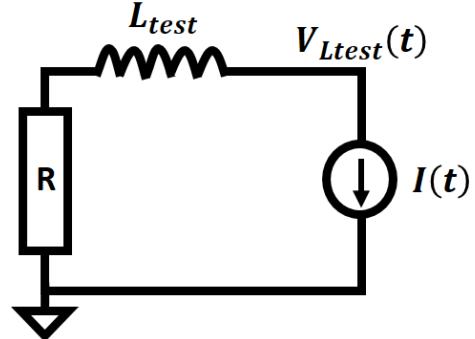

| 4.4 Derive Target Inductance and Target Capacitance . . . . .         | 49        |

| 4.5 Experimental Results . . . . .                                    | 50        |

| 4.5.1 Target Impedance Synthesis for Experiment . . . . .             | 50        |

| 4.5.2 Experimental Results Compared with Design Constraints . . . . . | 52        |

| 4.6 Conclusion . . . . .                                              | 53        |

| <b>5 Chip Load Model for PDN Verification and Exploration</b>         | <b>55</b> |

| 5.1 Introduction . . . . .                                            | 55        |

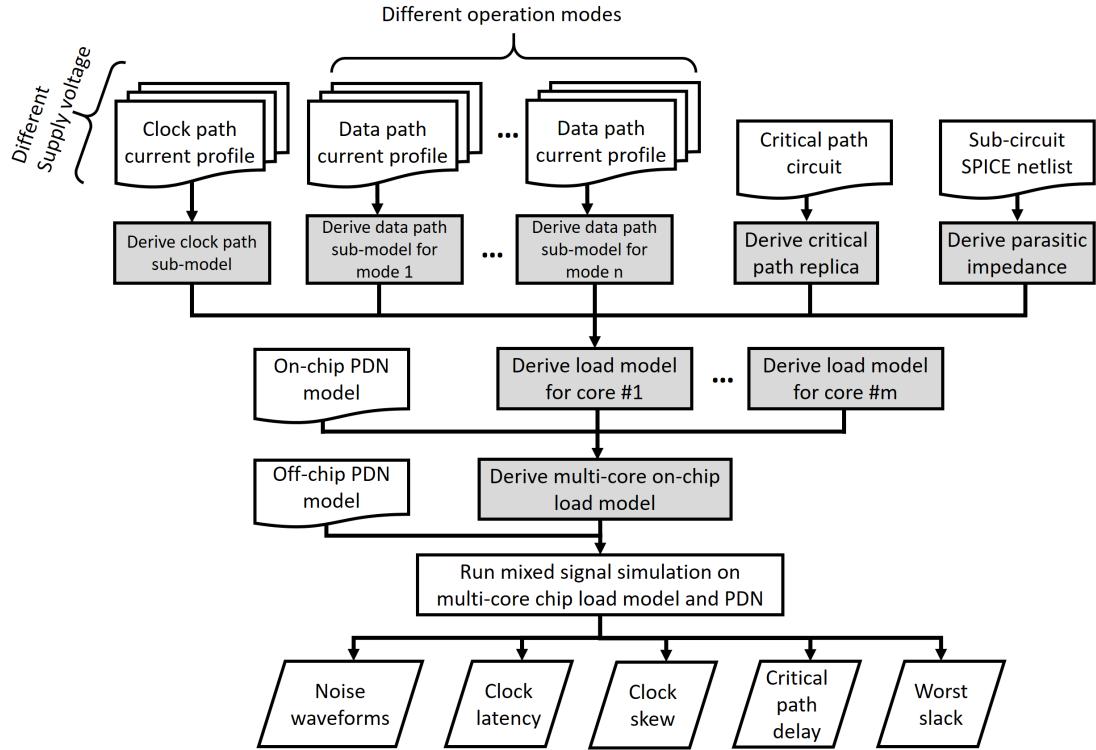

| 5.2 Multi-Core Chip Load Modeling . . . . .                           | 56        |

| 5.2.1 Overview of Chip Load Modeling Flow . . . . .                   | 56        |

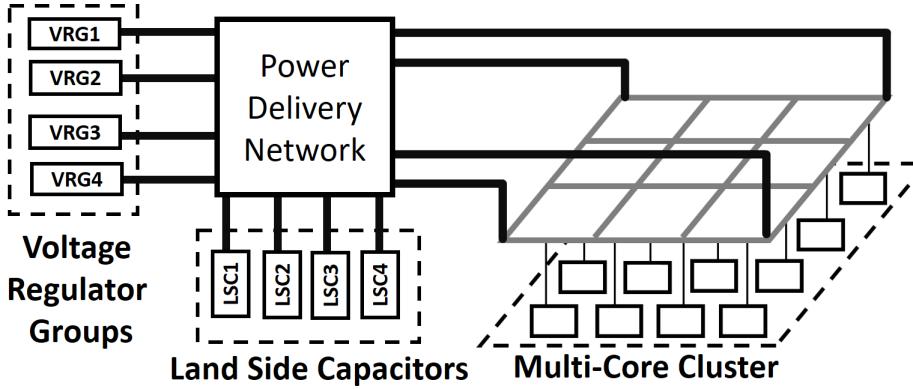

| 5.2.2 Target Multi-Core PDN System and Usage Model . . . . .          | 58        |

| 5.2.3 Individual Core Load Model . . . . .                            | 59        |

| 5.2.4 Core Load Model Characterization . . . . .                      | 66        |

| 5.2.5 Resistance Profile Simulation Procedure . . . . .               | 67        |

| 5.3 Experimental Results . . . . .                                    | 68        |

| 5.3.1 Individual Core Experiment . . . . .                            | 68        |

| 5.3.2 Multi-Core PDN System Experiment . . . . .                      | 71        |

| 5.4 Conclusion . . . . .                                              | 76        |

| <b>6 Conclusion</b>                                                   | <b>79</b> |

| <b>Appendix</b>                                                       | <b>83</b> |

| <b>Bibliography</b>                                                   | <b>91</b> |

# List of Figures

|      |                                                                                                  |    |

|------|--------------------------------------------------------------------------------------------------|----|

| 1.1  | Processor frequency and transistor count in the past 50 years. . . . .                           | 2  |

| 1.2  | IRDS prediction of board power, device supply voltage, and device threshold voltage. . . . .     | 3  |

| 1.3  | Overall diagram of a power delivery network (PDN) system. . . . .                                | 5  |

| 1.4  | PDN circuit model using lumped RLC components. . . . .                                           | 5  |

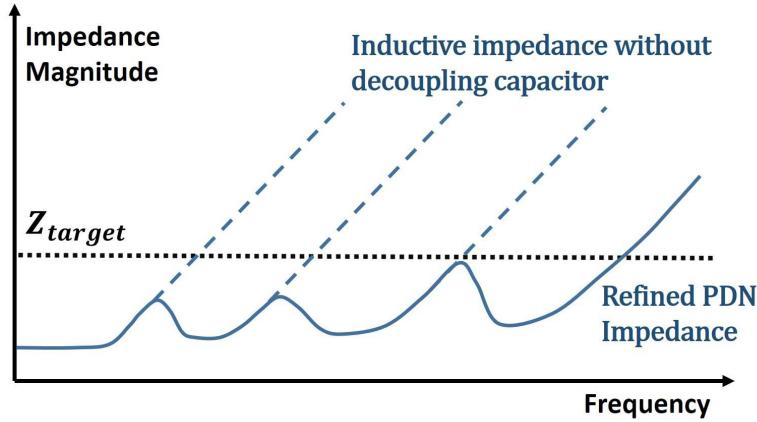

| 1.5  | Refining PDN impedance to meet target impedance constraint. . . . .                              | 8  |

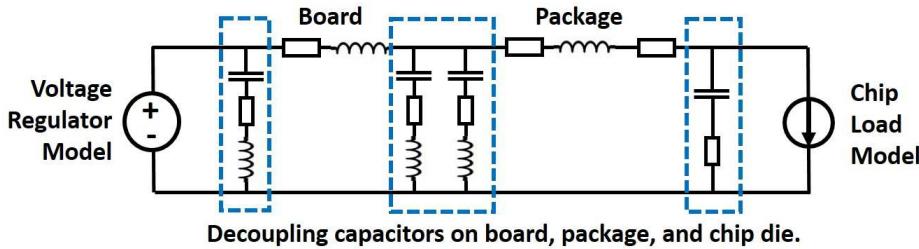

| 1.6  | Decoupling capacitors allocation at different stages of PDN to reduce the PDN impedance. . . . . | 8  |

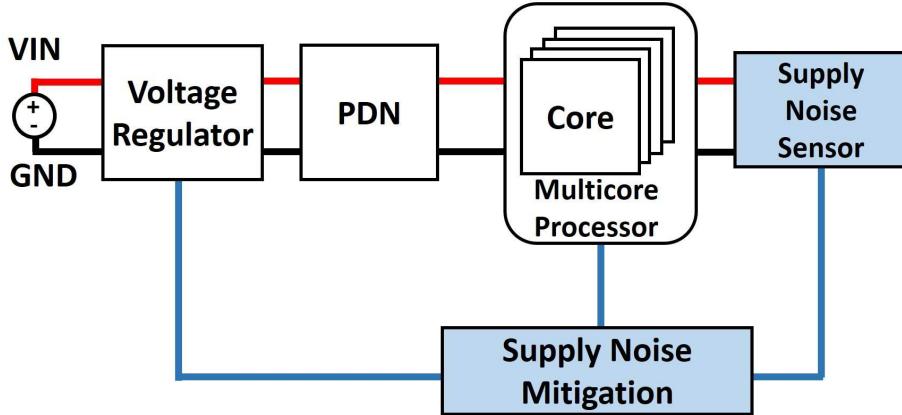

| 1.7  | Power delivery network (PDN) with reactive noise mitigation system. .                            | 9  |

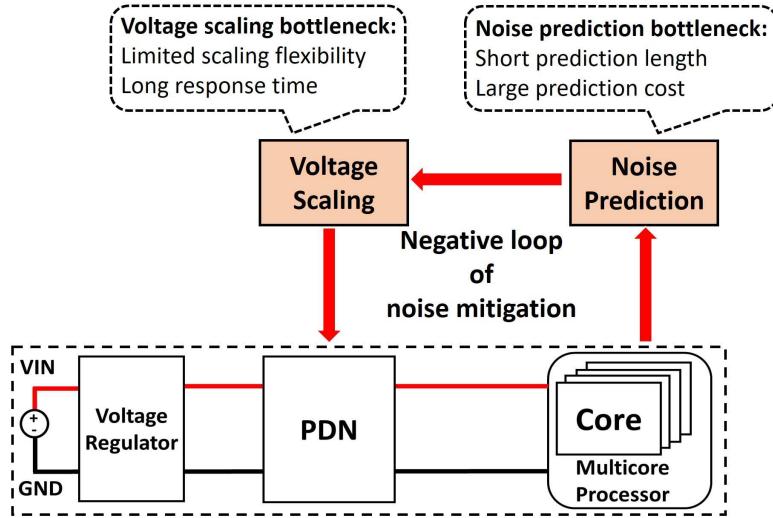

| 1.8  | Negative loop challenge of supply noise mitigation. . . . .                                      | 11 |

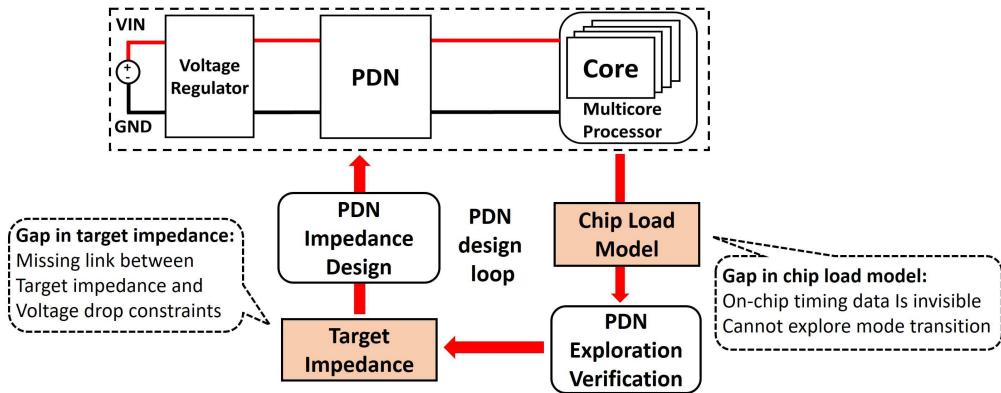

| 1.9  | PDN design gap challenge. . . . .                                                                | 13 |

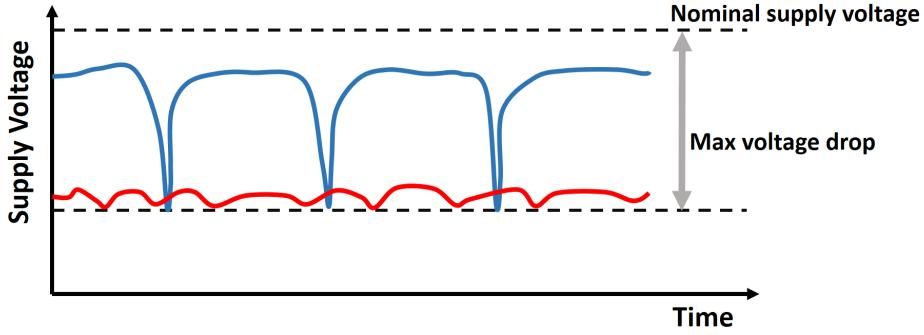

| 1.10 | Two voltage profiles with same maximum voltage drop. . . . .                                     | 14 |

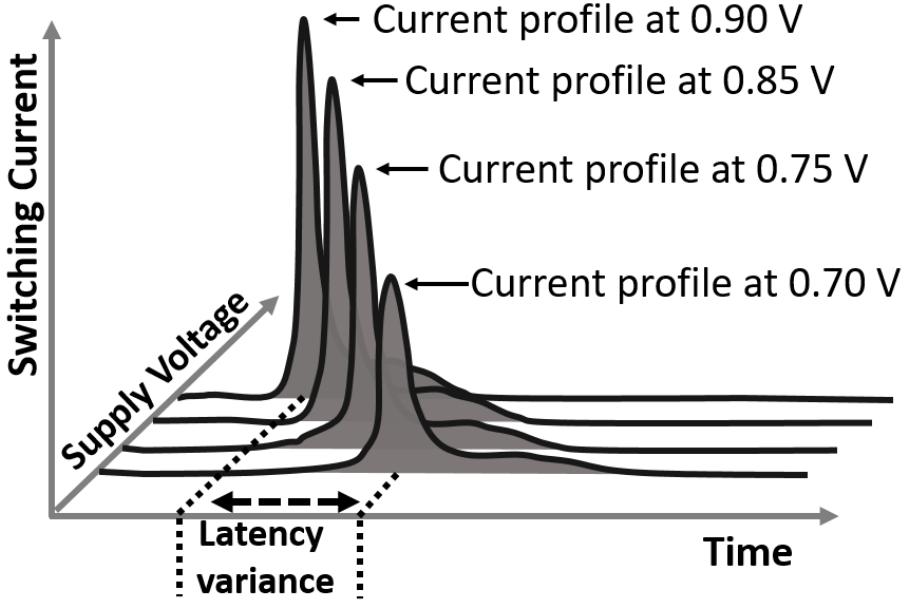

| 1.11 | Voltage-current-timing interdependency. . . . .                                                  | 16 |

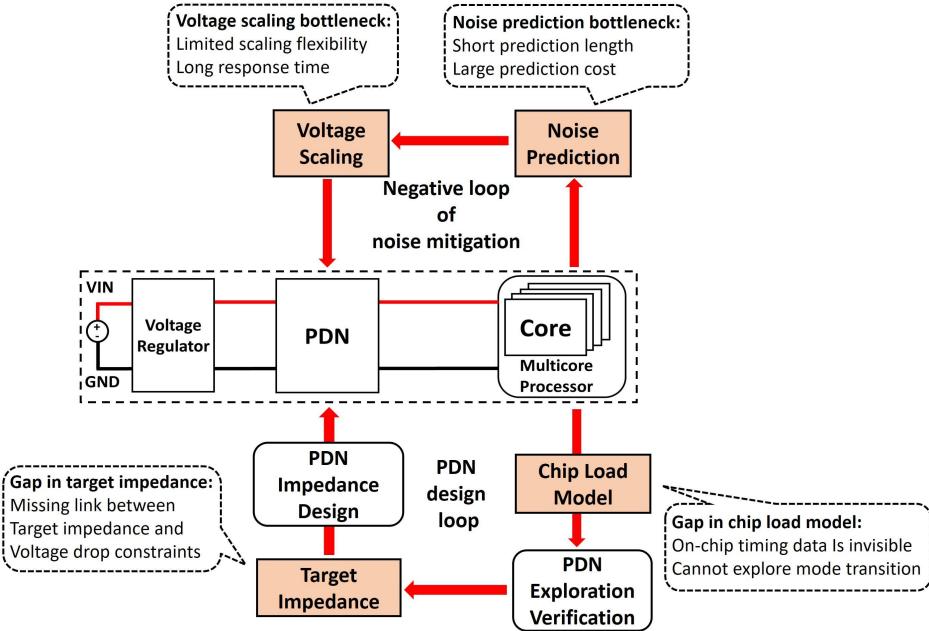

| 1.12 | Existing challenges for supply noise mitigation and PDN design. . . .                            | 17 |

| 1.13 | Proposed solutions for proactive noise mitigation and PDN design methodology. . . . .            | 17 |

| 2.1  | Proposed structure for proactive supply noise mitigation. . . . .                                | 22 |

| 2.2  | Training and prediction flows with current predictor. . . . .                                    | 24 |

| 2.3  | Determination of averaging period $P$ using voltage-current correlation. .                       | 25 |

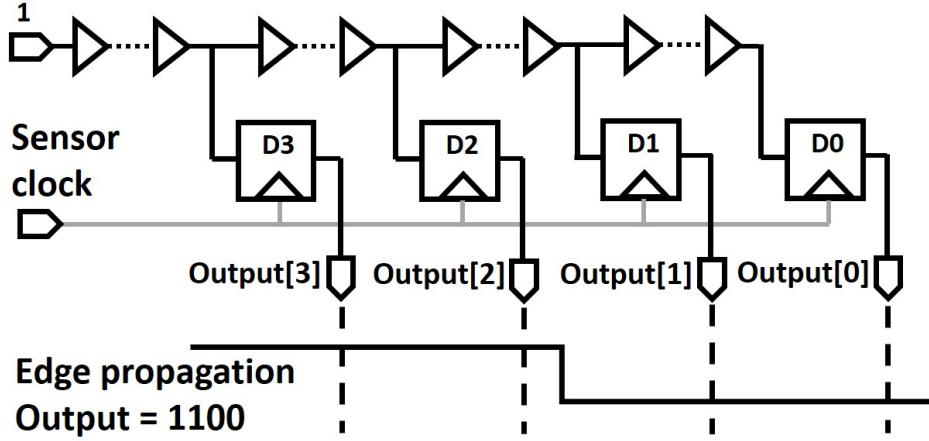

| 2.4  | Digital voltage sensor. . . . .                                                                  | 28 |

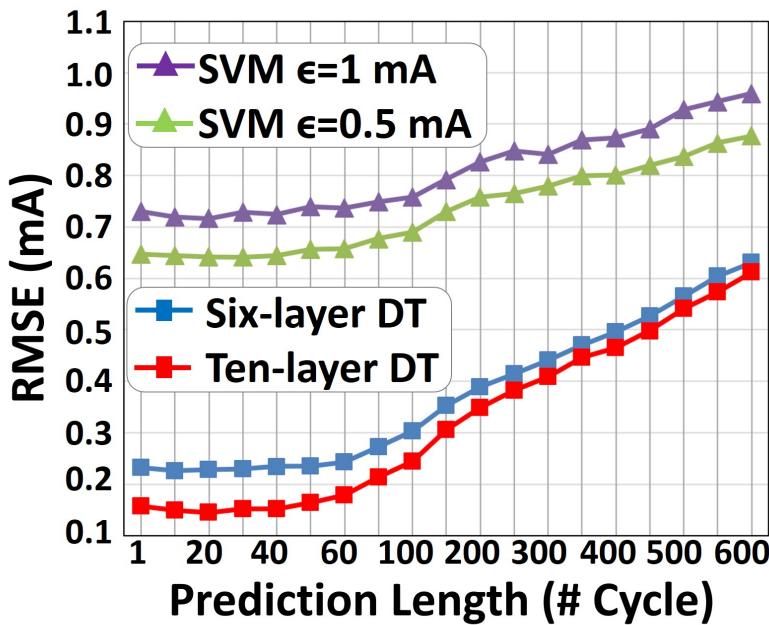

| 2.5  | RMSE versus prediction length. . . . .                                                           | 30 |

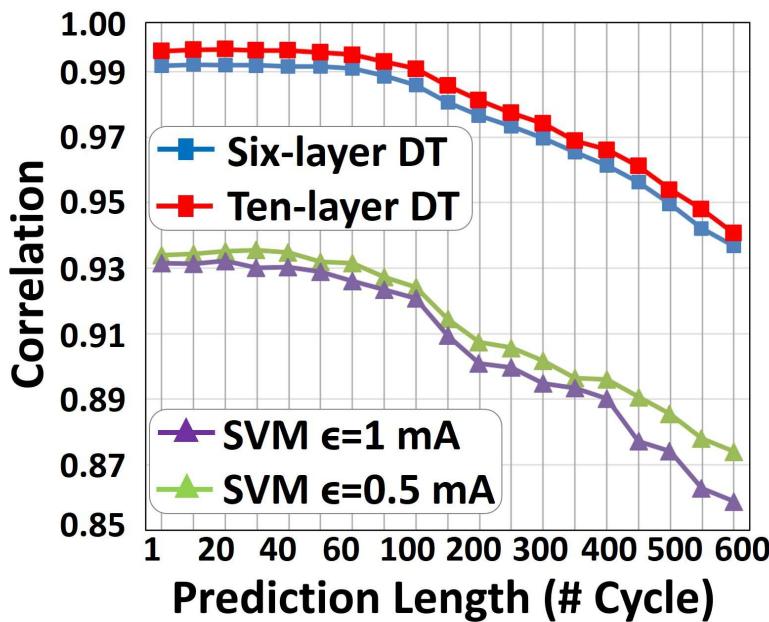

| 2.6  | Correlation versus prediction length. . . . .                                                    | 30 |

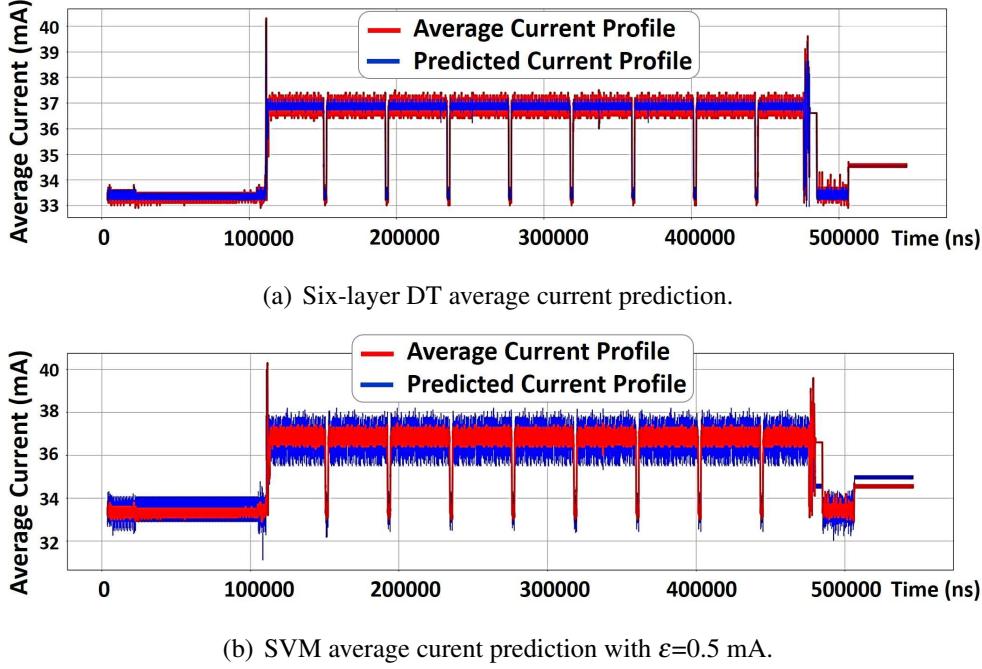

| 2.7  | Current prediction results with DT and SVM. . . . .                                              | 32 |

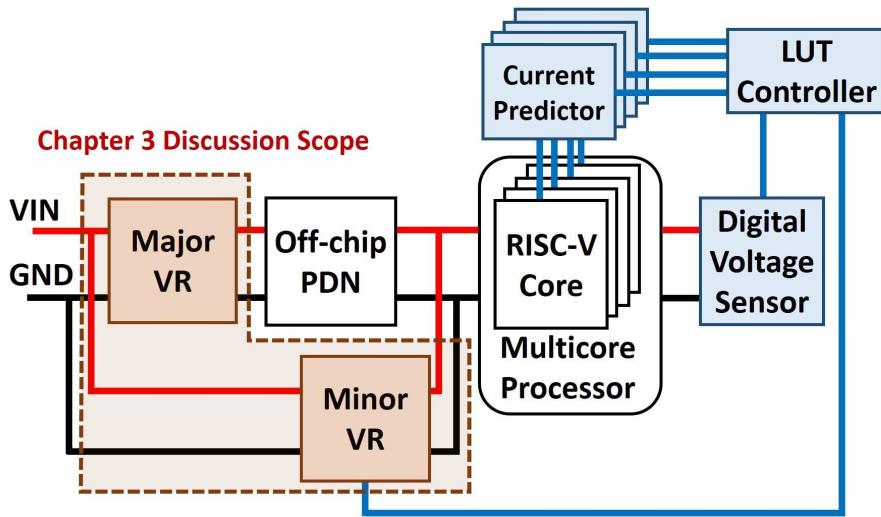

| 3.1  | Proposed voltage regulator in proactive supply noise mitigation system. .                        | 36 |

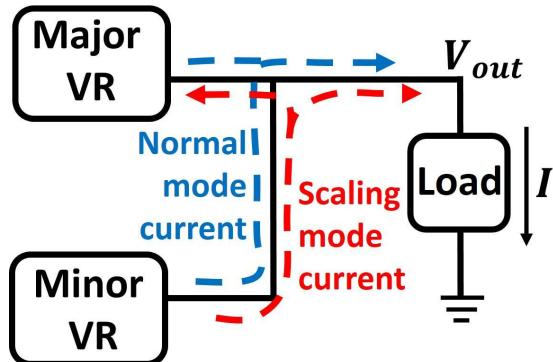

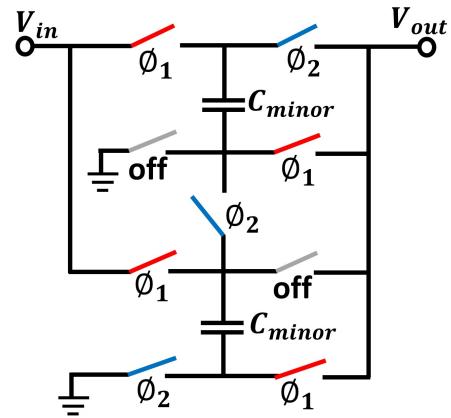

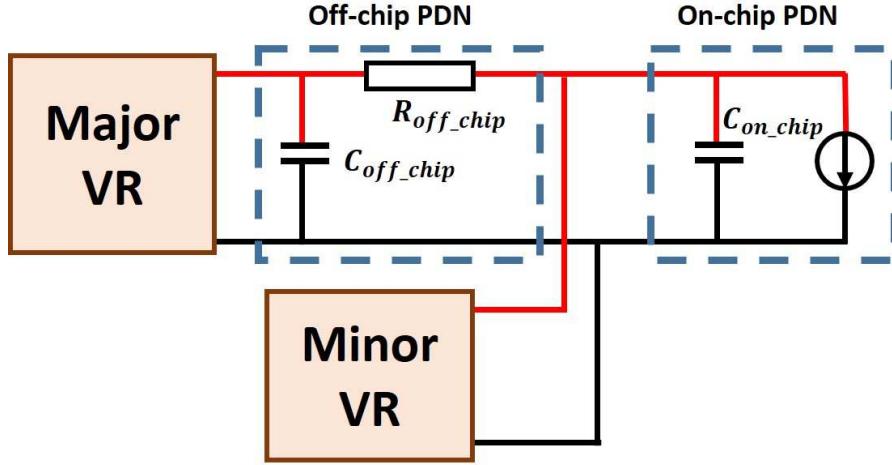

| 3.2  | MMVR connection diagram. . . . .                                                                 | 37 |

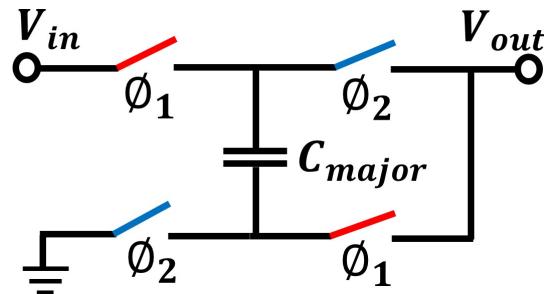

| 3.3  | Major VR with 2:1 conversion ratio. . . . .                                                      | 37 |

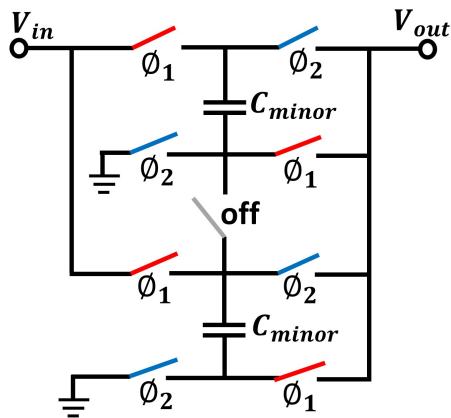

| 3.4  | Minor VR in normal mode with 2:1 conversion ratio. . . . .                                       | 37 |

| 3.5  | Minor VR in scaling mode with 3:2 conversion ratio. . . . .                                      | 37 |

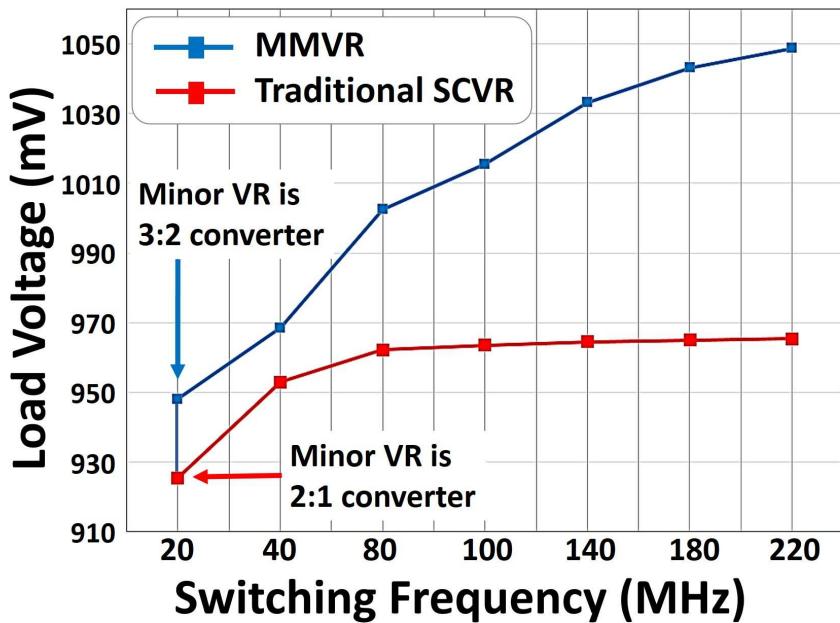

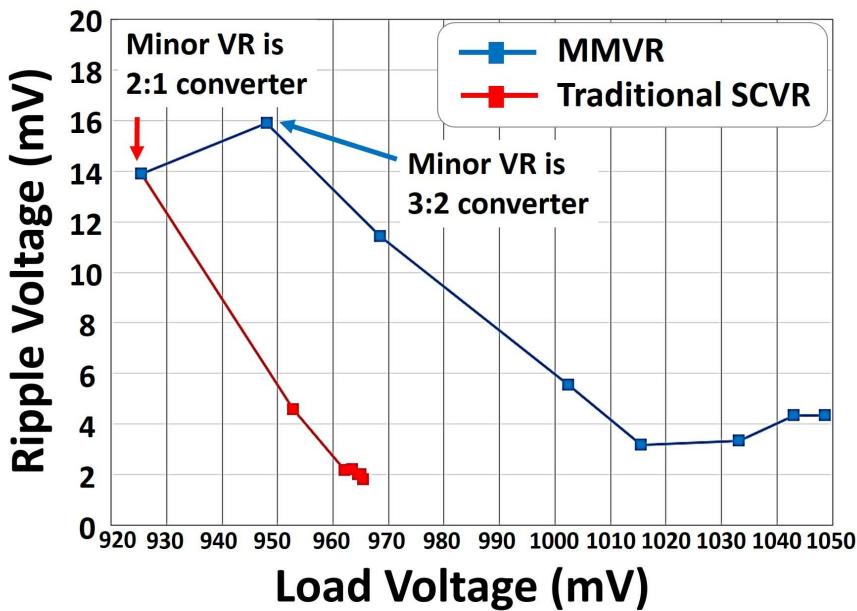

| 3.6  | MMVR performance test circuit. . . . .                                                           | 39 |

| 3.7  | Comparison in voltage scaling range. . . . .                                                     | 40 |

|      |                                                                                      |    |

|------|--------------------------------------------------------------------------------------|----|

| 3.8  | Comparison in ripple voltage. . . . .                                                | 40 |

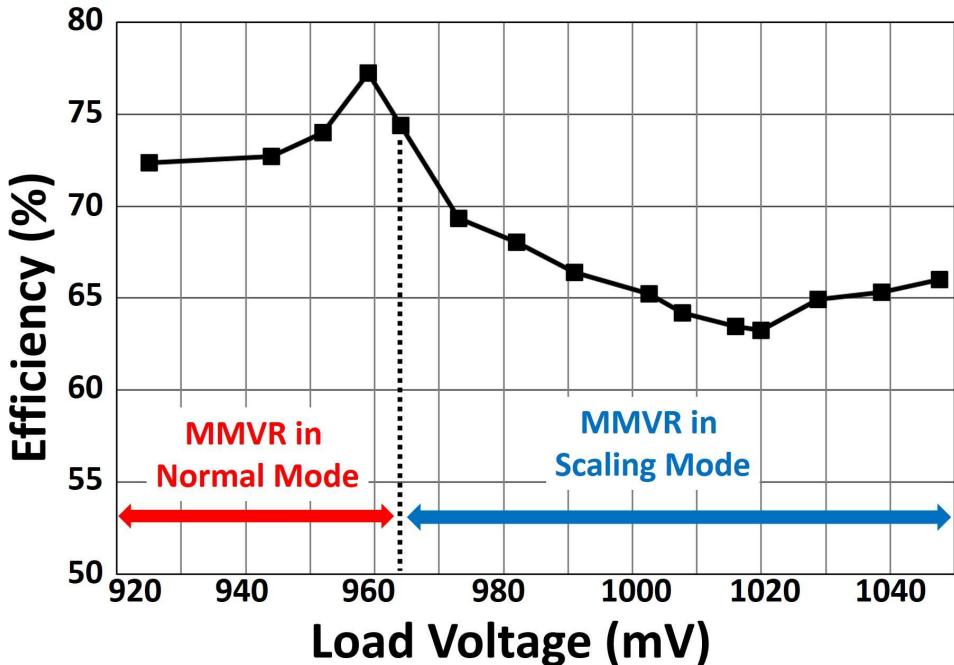

| 3.9  | MMVR efficiency versus load voltage. . . . .                                         | 41 |

| 3.10 | Noise mitigation result for multicore RISC-V PDN. . . . .                            | 42 |

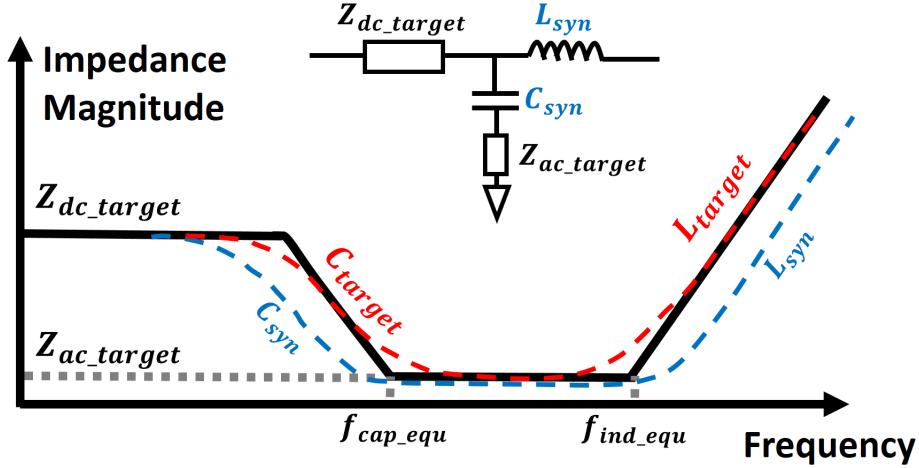

| 4.1  | RLC target impedance. . . . .                                                        | 44 |

| 4.2  | RL target impedance. . . . .                                                         | 44 |

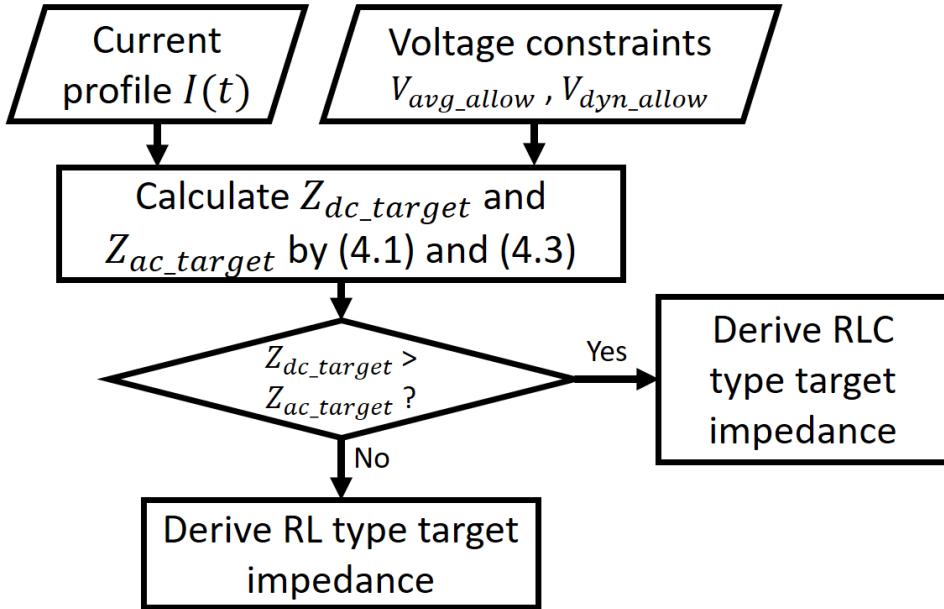

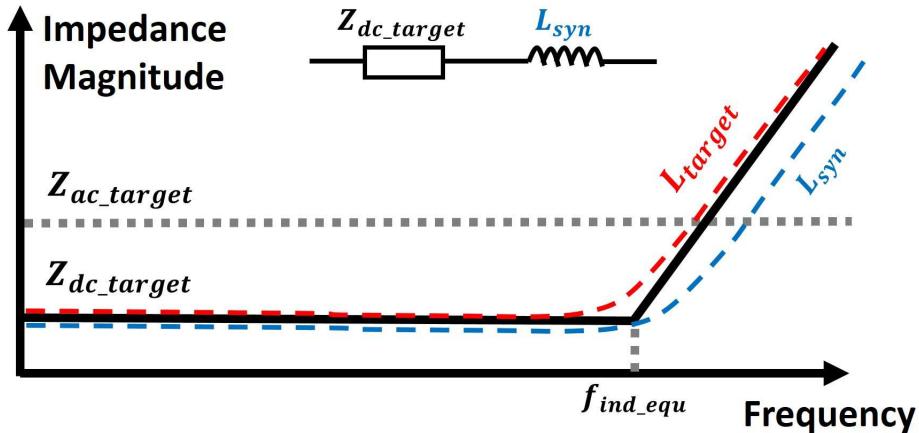

| 4.3  | Overall flow of frequency-dependent target impedance methodology. . . . .            | 45 |

| 4.4  | RC test circuit. . . . .                                                             | 49 |

| 4.5  | RL test circuit. . . . .                                                             | 49 |

| 4.6  | RLC-type target impedance synthesis. . . . .                                         | 51 |

| 4.7  | RL-type target impedance synthesis. . . . .                                          | 51 |

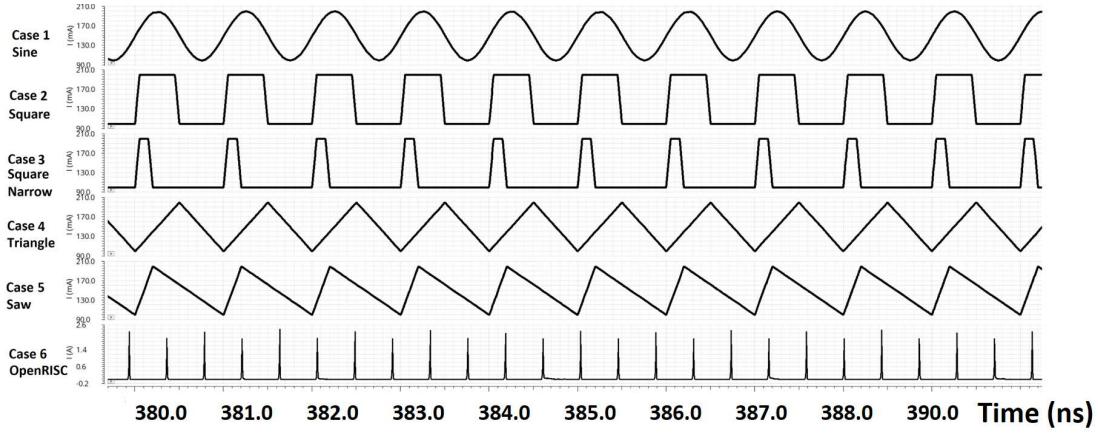

| 4.8  | Load current profiles at 1 GHz for experiments. . . . .                              | 52 |

| 5.1  | Flow of multi-core chip load modeling. . . . .                                       | 57 |

| 5.2  | An example of block diagram of power delivery network for multi-core system. . . . . | 58 |

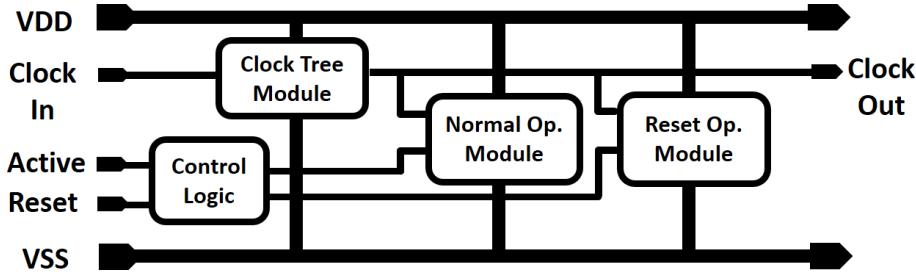

| 5.3  | Overall structure of individual core load model. . . . .                             | 59 |

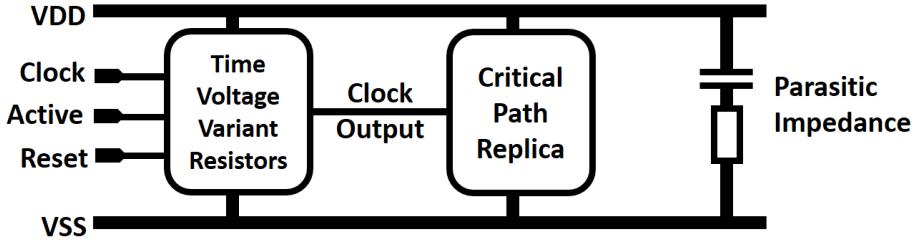

| 5.4  | Time voltage variant resistors model structure. . . . .                              | 60 |

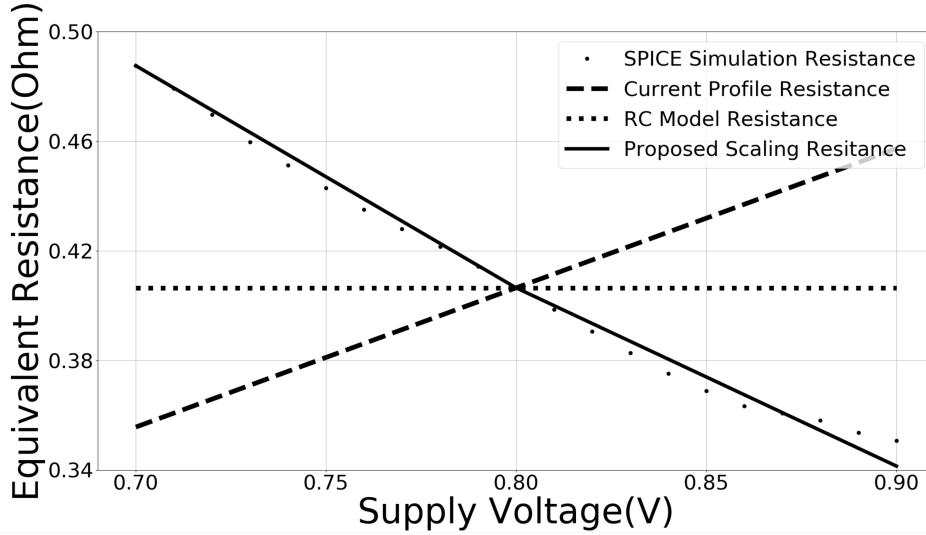

| 5.5  | Comparison of equivalent resistance during clock switching. . . . .                  | 62 |

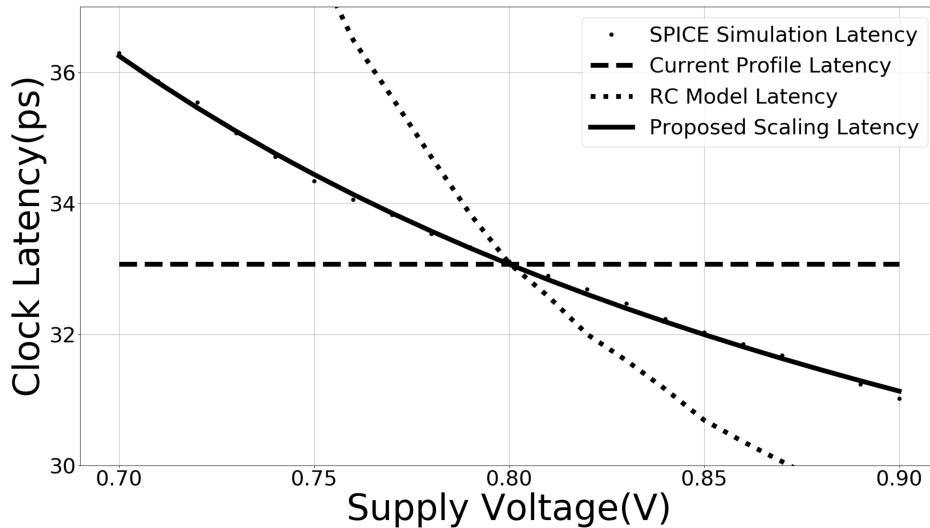

| 5.6  | Clock latency estimation comparison. . . . .                                         | 62 |

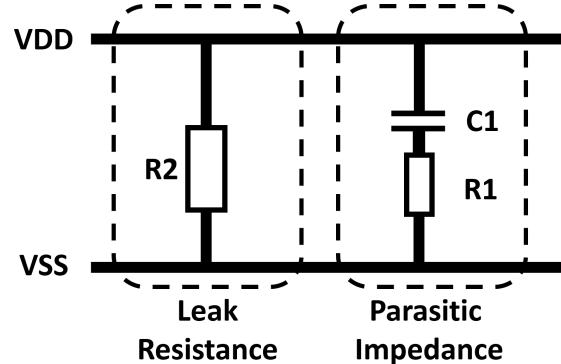

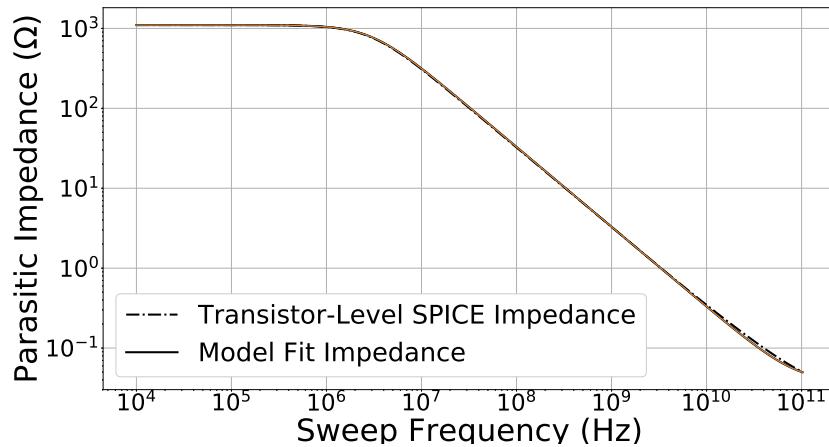

| 5.7  | Parasitic impedance model. . . . .                                                   | 65 |

| 5.8  | Parasitic impedance extracted by small signal analysis. . . . .                      | 65 |

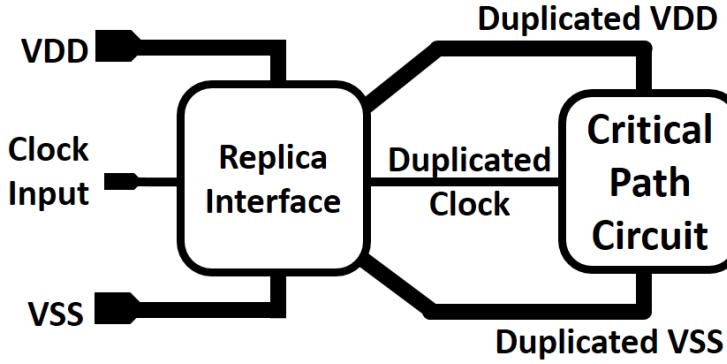

| 5.9  | Critical path replica model. . . . .                                                 | 66 |

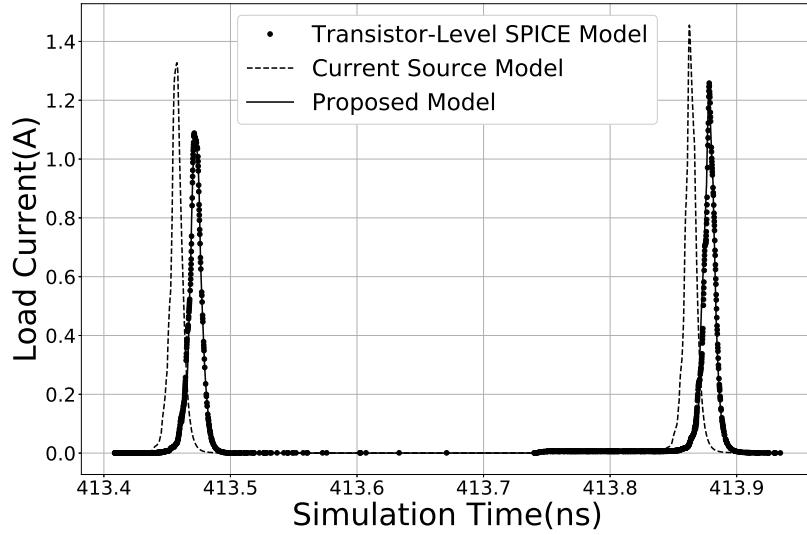

| 5.10 | Current waveform comparison within one clock cycle. . . . .                          | 69 |

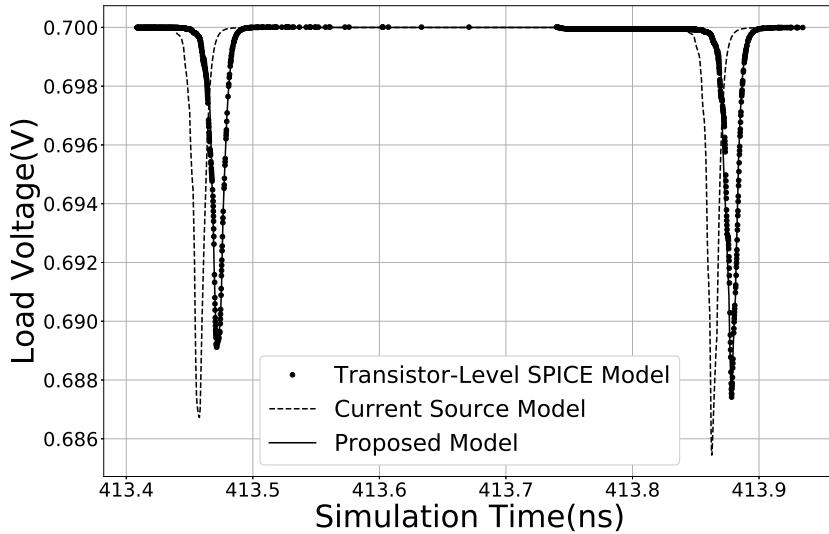

| 5.11 | Load voltage waveform comparison within one clock cycle. . . . .                     | 70 |

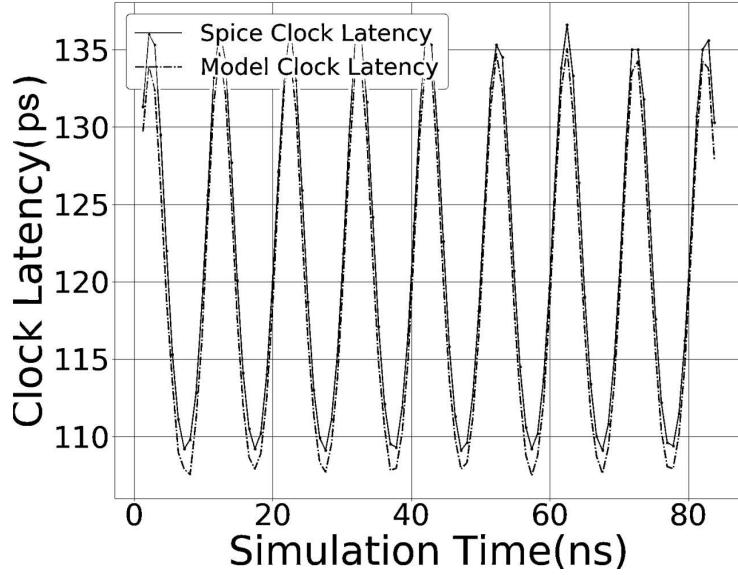

| 5.12 | Clock latency estimation with 100 MHz supply noise. . . . .                          | 71 |

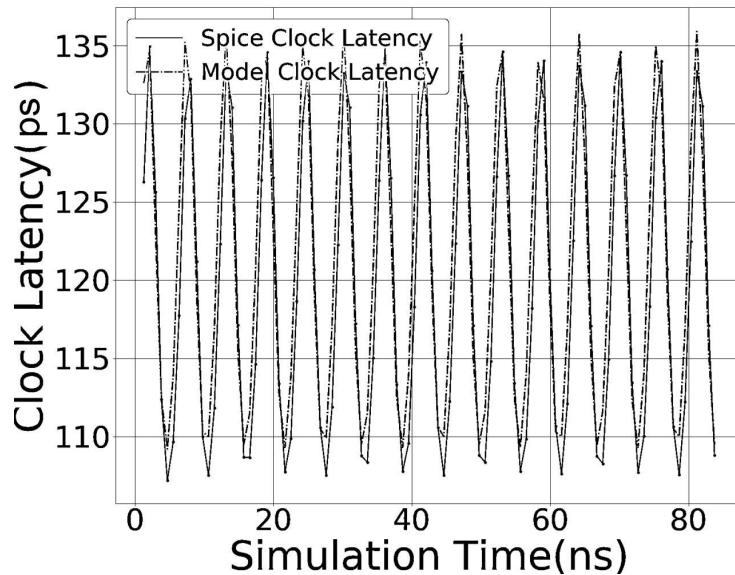

| 5.13 | Clock latency estimation with 1 GHz supply noise. . . . .                            | 72 |

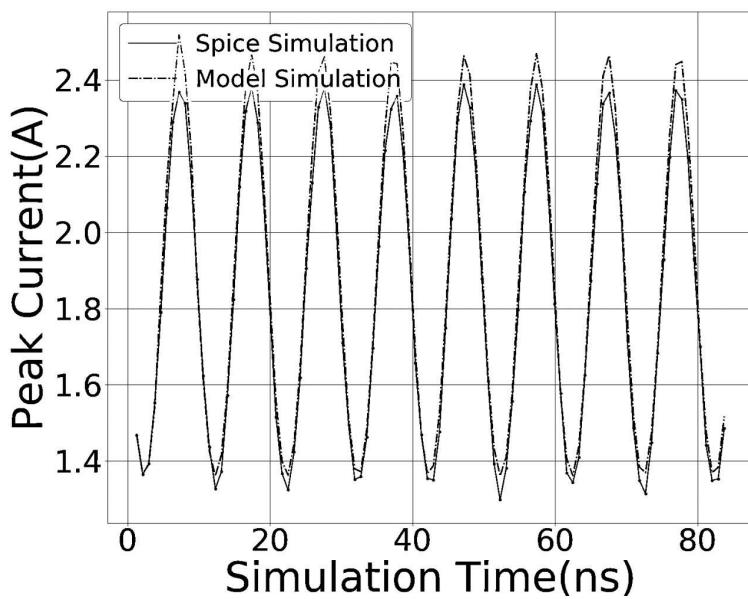

| 5.14 | Peak current estimation with 100 MHz supply noise. . . . .                           | 72 |

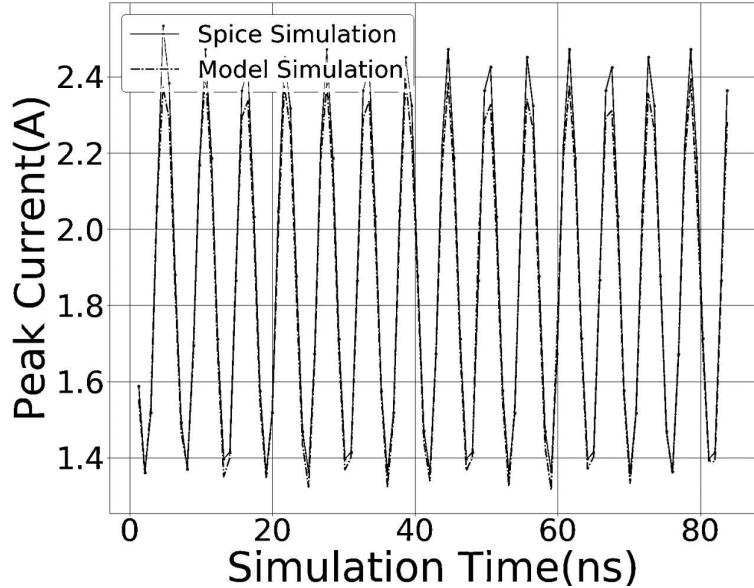

| 5.15 | Peak current estimation with 1 GHz supply noise. . . . .                             | 73 |

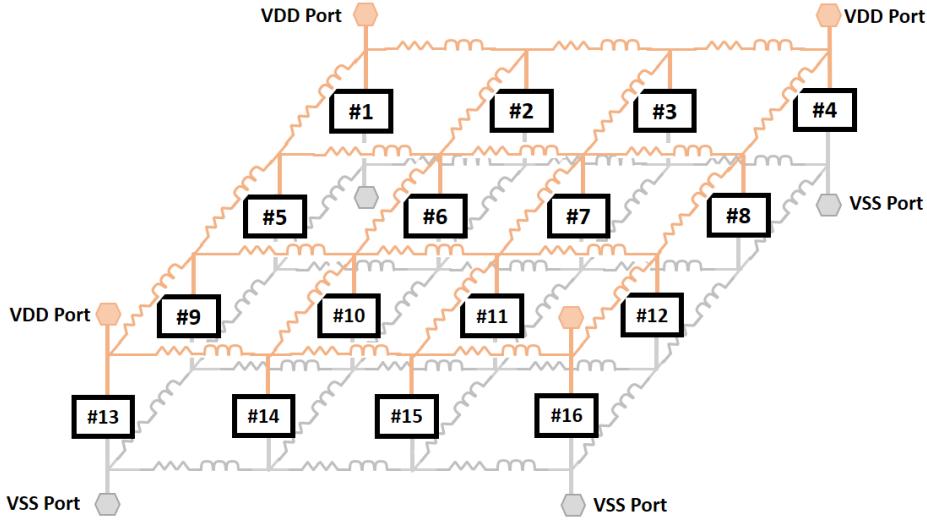

| 5.16 | 16-core cluster with power-ground mesh. . . . .                                      | 74 |

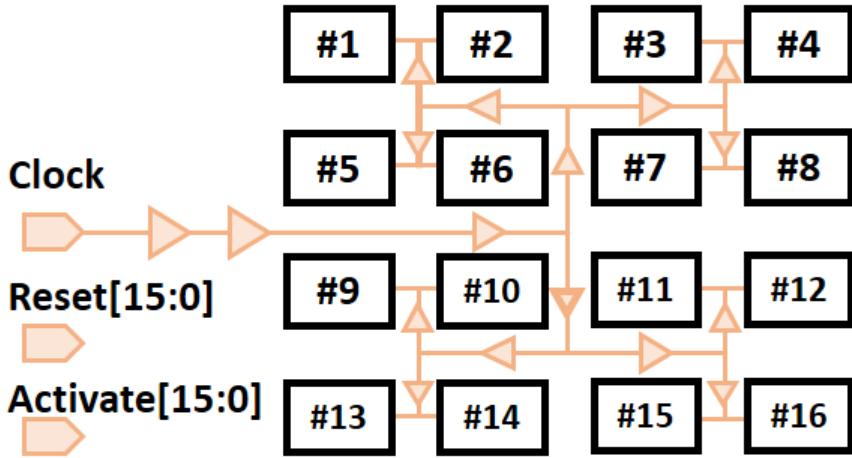

| 5.17 | 16-core cluster with clock tree and control signal. . . . .                          | 74 |

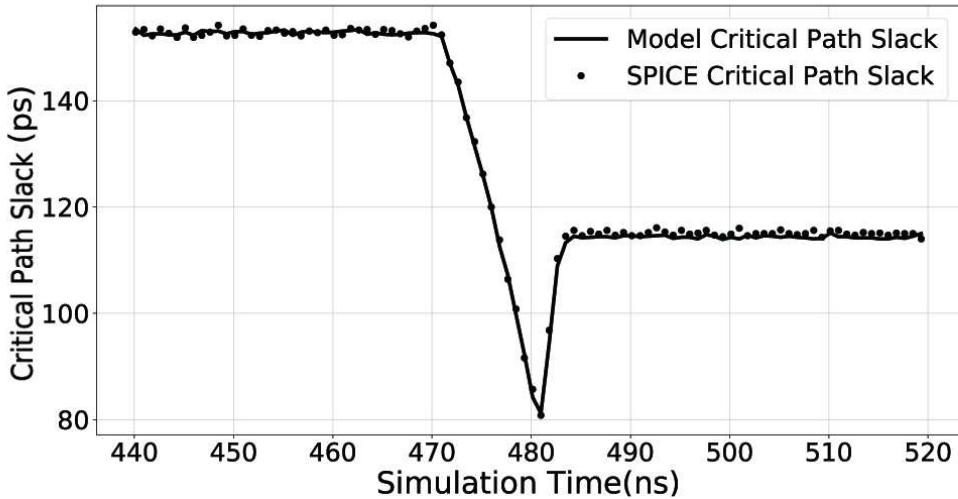

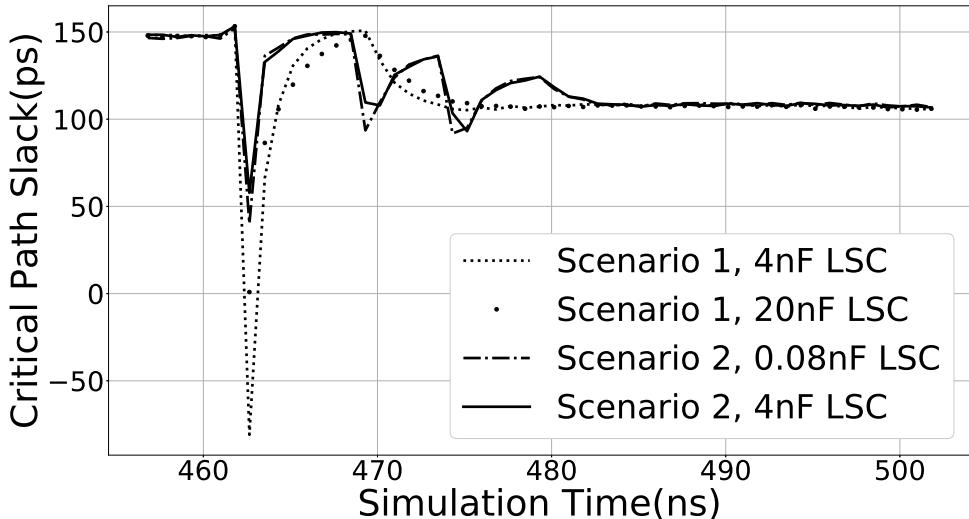

| 5.18 | Cycle-by-cycle critical path slack comparison during transient process. .            | 75 |

| 5.19 | Cycle-by-cycle critical path worst slack of core #6. . . . .                         | 75 |

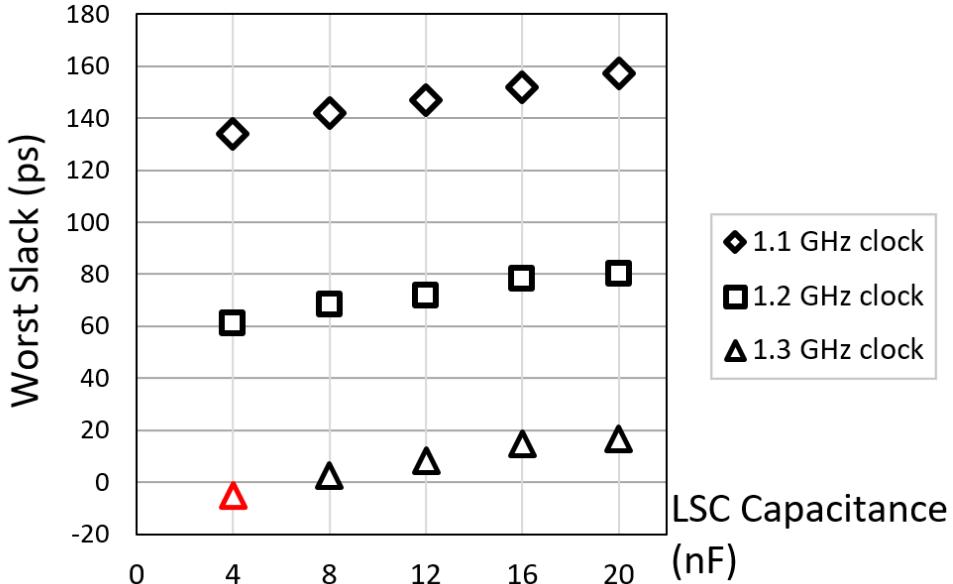

| 5.20 | Worst timing slack under different LSC configurations. . . . .                       | 76 |

# List of Tables

|     |                                                                                                    |    |

|-----|----------------------------------------------------------------------------------------------------|----|

| 2.1 | Instruction categorization for RISC-V. . . . .                                                     | 26 |

| 2.2 | Overriding rule table with sensor output. . . . .                                                  | 28 |

| 2.3 | Prediction performance and hardware cost. . . . .                                                  | 31 |

| 4.1 | Derived target impedance parameters, and average and minimal voltages. . . . .                     | 53 |

| 5.1 | Average peak load current and average clock latency comparison at various supply voltages. . . . . | 70 |

# Abbreviations

|              |                                                     |

|--------------|-----------------------------------------------------|

| <b>ALU</b>   | Arithmetic Logic Unit                               |

| <b>CMOS</b>  | Complementary Metal-Oxide Semiconductor             |

| <b>CPU</b>   | Central Processing Unit                             |

| <b>CRC</b>   | Cyclic Redundancy Check                             |

| <b>CSR</b>   | Control and Status Register                         |

| <b>decap</b> | Decoupling Capacitor                                |

| <b>DT</b>    | Decision Tree                                       |

| <b>DVFS</b>  | Dynamic Voltage and Frequency Scaling               |

| <b>EDA</b>   | Electronic Design Automation                        |

| <b>EMA</b>   | Exponential Moving Average                          |

| <b>FPGA</b>  | Field-Programmable Gate Array                       |

| <b>FPU</b>   | Floating-Point Unit                                 |

| <b>FU</b>    | Functional Unit                                     |

| <b>GPU</b>   | Graphics Processing Unit                            |

| <b>IC</b>    | Integrated Circuit                                  |

| <b>IoT</b>   | Internet of Things                                  |

| <b>IPC</b>   | Instructions per Cycle                              |

| <b>IRDS</b>  | International Roadmap for Devices and Systems       |

| <b>ITRS</b>  | International Technology Roadmap for Semiconductors |

|              |                                                     |

|--------------|-----------------------------------------------------|

| <b>LDO</b>   | Low Dropout                                         |

| <b>LSC</b>   | Land Side Capacitor                                 |

| <b>LUT</b>   | Lookup Table                                        |

| <b>MEC</b>   | Magnitude Equivalent Current                        |

| <b>MEF</b>   | Magnitude Equivalent Frequency                      |

| <b>MMVR</b>  | Major-Minor Voltage Regulator                       |

| <b>OoO</b>   | Out of Order                                        |

| <b>PC</b>    | Program Counter                                     |

| <b>PCB</b>   | Printed Circuit Board                               |

| <b>PDN</b>   | Power Delivery Network                              |

| <b>PG</b>    | Power Ground                                        |

| <b>PSN</b>   | Power Supply Noises                                 |

| <b>RMSE</b>  | Root-Mean-Square-Error                              |

| <b>RP</b>    | Resistance Profile                                  |

| <b>SCVR</b>  | Switched Capacitor Voltage Regulator                |

| <b>SMA</b>   | Simple Moving Average                               |

| <b>SOP</b>   | System-on-Package                                   |

| <b>SPICE</b> | Simulation Program with Integrated Circuit Emphasis |

| <b>SSN</b>   | Simultaneously Switching Noise                      |

| <b>SV</b>    | Support Vector                                      |

| <b>SVM</b>   | Support Vector Machine                              |

| <b>VCCS</b>  | Voltage-Controlled Current Source                   |

| <b>VLSI</b>  | Very Large Scale Integration                        |

| <b>VR</b>    | Voltage Regulator                                   |

| <b>VRG</b>   | Voltage Regulator Group                             |

# Chapter 1

## Introduction

This dissertation focuses on proactive supply noise mitigation and power delivery network design methodology. This chapter describes the research background and objectives of this dissertation. Section 1.1 will explain the background of the power delivery network (PDN) and supply noise impact, followed by the introduction of traditional noise mitigation system and PDN design methodology. Then, Section 1.2 discusses the main problems in existing methodology. Finally, the objectives and overall organization of this dissertation are presented in Section 1.3.

### 1.1 Background

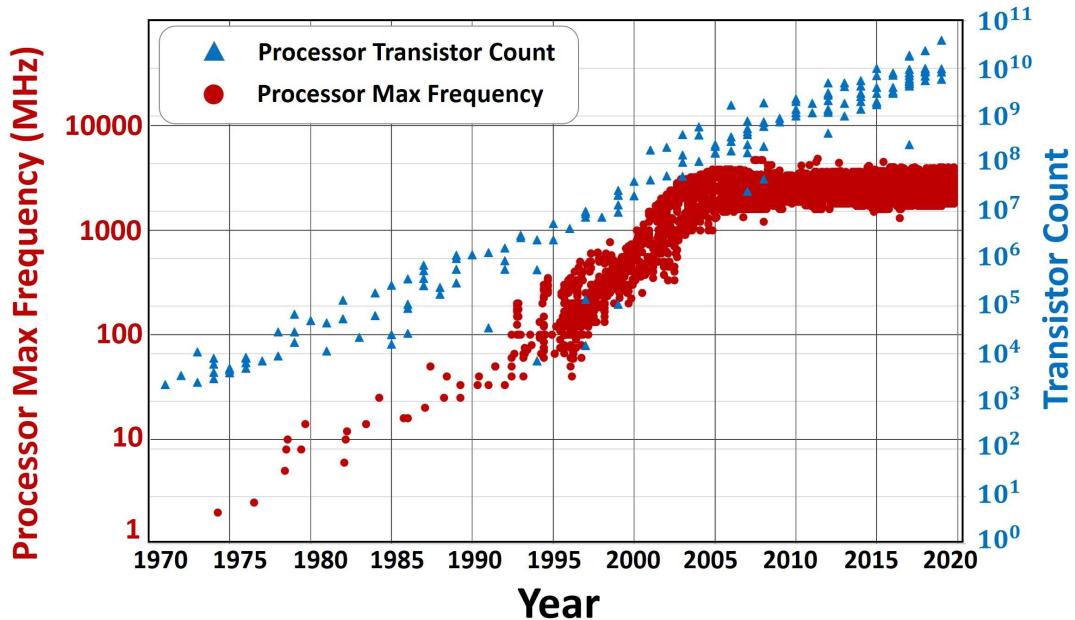

Moore's law has been driving the semiconductor industry for over 50 years. As is diagrammed in Fig. 1.1, the transistor count per die kept doubling in bi-annual pace [1–4]. Meanwhile, though clock frequency for single thread reached operation has reached a plateau around the year of 2006, it still keeps 15% to 20% increment per technology node generation [1,5]. Following the ITRS2.0 and IRDS prediction [6–9], to the 2030s, even for a low power mobile device, the number of GPU and CPU cores can increase 10X within a decade. Such a technology scaling trend pushes the future chip design to the power wall [3, 10, 11], because ever increased frequency and transistor count will eventually hit the physical limitation such as thermal dissipation limit and battery capacity limit. Hence, reduced power consumption becomes the major technology drivers for the coming decade [9].

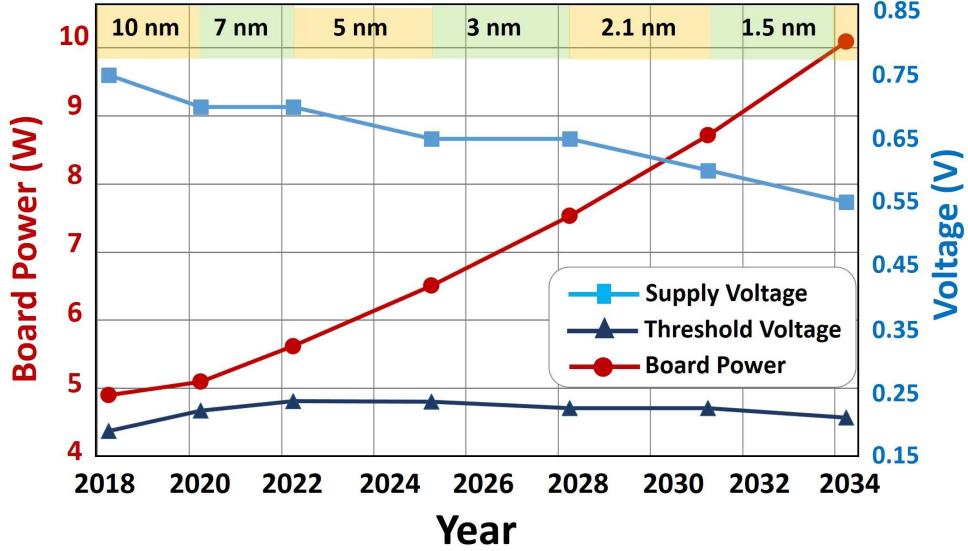

To continue the performance improvement under the power wall, aggressive supply voltage reduction is a necessity, especially for low power devices such as mobile phones and IoT devices [12–14]. According to the IRDS prediction of board power (for mobile device), device supply voltage, and threshold voltage shown as Fig. 1.2, the supply voltage of chip core logic can be as low as 0.55 V level to the year of 2034. Considering the threshold voltage keeps above 0.2 V, and ever increased power consumption, the noise margin will be continuously decreasing for the coming technology node.

Figure 1.1: Processor frequency and transistor count in the past 50 years. Blue triangles represent the transistor count on a processor, and red dots represent the maximum frequency<sup>1</sup>.

A high-quality low-noise power distribution system is critically important to ensure the performance of next-generation very large scale integration (VLSI) system. It is because the supply noise magnitude is continuously increasing with the transistor numbers on die, and timing sensitivity to noise becomes more and more severe with the scaling down of the technology node. For example, Ahmed *et al.* [15] reported over 15% voltage drop in at-speed delay test on 180 nm SoC. At 55-nm node, the peak supply noise can reach 20%-30% of nominal voltage [16]. The multi-core system makes voltage droop even larger. Taking the worst voltage droop as an example, a dual-core system may experience 50% larger droop than a single-core system [17]. As for the noise-timing sensitivity, Saint-Laurent [18] reported over 7% timing impact under 1.3% VDD supply voltage noise after the 90-nm technology node. Reddi *et al.* [19] reported over 33% frequency loss due to 20% extra noise margin. Bhowmik [20] reported 2 MHz chip frequency degradation for every millivolt drop in a four-core processor. Gnad [21] reported over 3% timing delay increment caused by voltage drop, which is caused by toggling 8% of the flip-flops in the field-programmable gate array (FPGA). The supply noise challenge is thought to become severer at the even smaller node [22].

<sup>1</sup>Here, the processor data before 1995 is collected from [1], and data starts from 1995 is collected from [2]. The maximum frequency data is measured with integer benchmarks.

Figure 1.2: IRDS prediction of board power, device supply voltage, and device threshold voltage. The blue square line is predicted logic supply voltage, the blue triangle line is predicted device threshold voltage, and the red line is predicted board power for the mobile device. Each prediction step corresponds to technology node generation.

The discussion on supply noise mitigation and low-noise PDN design can be traced back to the 1970's. Till earlier 1990's, supply noise is mainly focused on the package level I/O noise, when Rainal [23] and Katopis [24] discussed the typical delta-I noise caused by inductive bonding wires. With the advancement of transistor integration, the impact of simultaneous switching noise (SSN) on CMOS I/O circuits is analyzed from the 1990's [25–27]. Though in this period, Davidson [28] reported the package level noise impacts the system-level performance by affecting propagation delay and clock skews, the supply noise interaction with chip internal behavior is still assumed to be a minor factor, and on-chip PDN is mainly modeled by simple lumped RLC components.

From the 1990's to 2000's, researchers began to analyze the detailed on-chip timing impact by supply voltage noise. Various on-chip PDN model is proposed, but exposing the detailed on-chip timing information considering supply noise is still a very difficult task [29]. During this period, Chen *et al.* [30] and Zhao [31] use RLC grid to model the detailed on-chip PDN noise, Eo *et al.* [32] and Tang [33] reported the SSN becomes an important issue for VLSI PDN design, Garben [34], Zhou *et al.* [35], and Ahmad *et al.* [36] discussed the interaction between on-chip PDN noise and off-chip packages at resonant frequencies, and the measurement of noise impact on multi-core and 3D-IC chips are also conducted. During this period, the on-chip noise impact is usually modeled by RLC grid and distributed current sources. Meanwhile, PDN design mainly

relies on voltage guard bound methodology for worst-case voltage drop. Decoupling capacitors are widely used to mitigate the noise impact at PDN design stage [37–40].

In 2000’s, Rahal-Arabi *et al.* [41, 42] firstly reported that the actual noise impact on the chip performance is much more complex than the previous assumption since conventional worst-case voltage guard bound methodology can lead to significantly over-designed PDN. As presented in Rahal-Arabi’s experiment, in some scenarios, removing the on-chip decoupling capacitor (decap) cells can even improve the chip performance. Several explanations are proposed for this issue. Chen *et al.* [43] points out the over-inserted decap cells significantly increase the tunneling current and leakage power, Hashimoto *et al.* [44], Ogasahara *et al.* [45], and Azais *et al.* [46] found the averaged noise has higher impact on logic and timing path, and actual timing impact is related to many aspects such as library cell sensitivity, temporal and spatial characteristics of supply noise.

Meanwhile, the supply noise becomes a critical concern with the popularity of low power designs. Though off-chip voltage regulators can be modulated for dynamic voltage scaling purposes [47–52], they are not suitable for mitigating emergent supply noise because of the slow response time. Instead, on-chip low-dropout (LDO) voltage regulator [53–57] is commonly used to mitigate on-chip supply noise. Other researchers try to dynamically schedule core activation [58], schedule workloads [59], modulate clock toggling phase [20], or exploit clock-data compensation effect [60, 61] to mitigate the supply noise impact. These traditional noise mitigation systems are basically designed in reactive flavor, which relies on the sensor to detect the voltage drop and then trigger noise mitigation.

Recently, with the rising of machine learning technology, various new methods are proposed for resolving traditional PDN design and noise mitigation problems. For example, in [62–66], machine learning is applied to optimize library cell selection, allocate decoupling cells, and localize the worst supply noise region on the power ground mesh. Meanwhile, with the improvement of chip package integration technology, the on-chip voltage regulator becomes a feasible power supply solution. For example, Gu [67] and Wang *et al.* [68] use on-chip SCVRs for VLSI fine-grained voltage regulation purpose.

This dissertation proposes proactive noise mitigation system which is inspired by these emerging technologies. Before the detailed discussion, the following subsections will present the basics of the power delivery network, supply noise, PDN design methodology, and typical noise mitigation system.

### 1.1.1 Power Delivery Network and Supply Noise

This subsection presents the basics of traditional power delivery network (PDN) system, and power supply noise source throughout the PDN system.

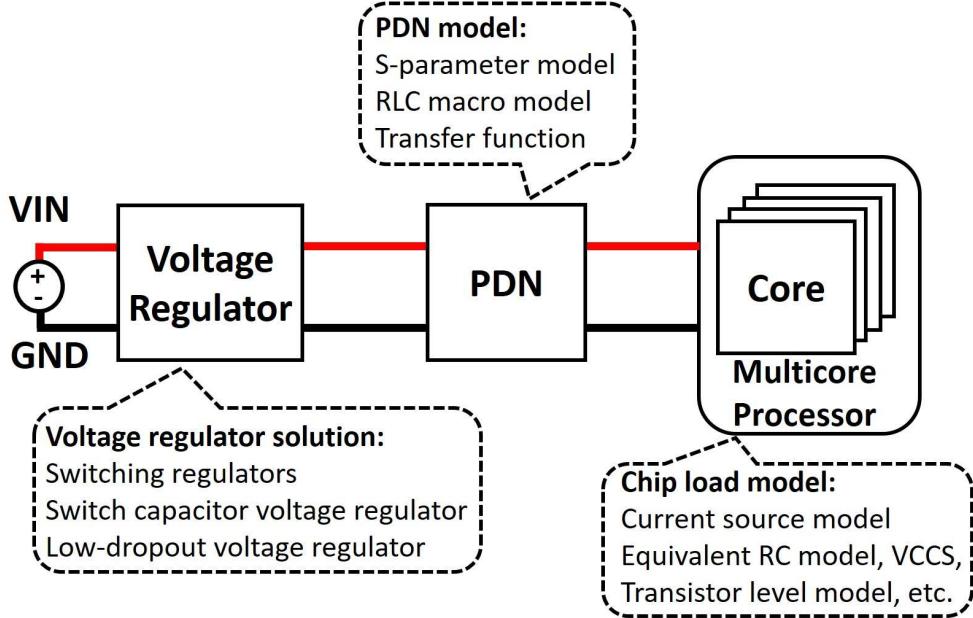

Figure 1.3: Overall diagram of a power delivery network (PDN) system. The red wire is power line, and the black wire is ground line.

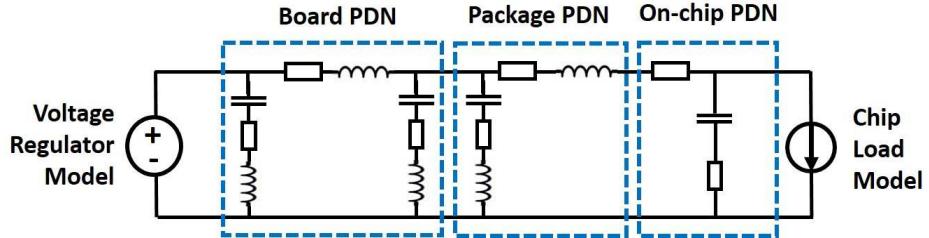

Figure 1.4: PDN circuit model using lumped RLC components.

### Power Delivery Network Structure

The overall PDN system structure used in this dissertation is well discussed in [22, 69–74], and can be diagrammed as Fig. 1.3, where the system is roughly divided into three components. Voltage regulator (VR) component serves as the power supplier, which converts higher DC voltage, usually from DC source or battery, to the lower DC voltage for VLSI use. The VR solution includes switching regulator (buck) [75, 76], low-dropout (LDO) voltage regulator [53–57], switched capacitor voltage regulator (SCVR) [48–52, 67, 77, 78], or combination with these solutions [56, 57, 79–81].

The role of the PDN component is to distribute supply voltage from the voltage regulator component to chip circuit elements such as logic gates and flip-flops(FFs) [82]. In a VLSI design, PDN circuit mainly corresponds to PCB and package. It usually consists

of passive components, and they are typically modeled by S-parameter model [83–86], RLC macro model [87, 88], or transfer function based methods [89–91]. An example PDN circuit model is shown as Fig. 1.4, where the conductors of the board, package, and on-chip circuit are modeled by lumped resistors and inductors. The decoupling capacitors between the power line and ground line are represented by series RLC components.

The chip load component can be modeled by current source model [92, 93], equivalent RC model [30, 94, 95], voltage-controlled current source model (VCCS) [96], or transistor-level SPICE model [97]. A typical PDN design task is to use the above models to assess the supply voltage noise for the chip load, then following the target impedance methodology [38–40] to refine the PDN impedance.

## Supply Noise Source

Power supply noise can arise from various parts of PDN. These noise sources include voltage regulator component, PDN component, and chip load component. Jointly considering the noise sources and mitigating the noise impact are usually a complex and challenging task.

Firstly, the voltage regulator component can induce supply noise. For the switching regulator, load current fluctuation can cause a large voltage drop across the inductor component. Hence, a large decoupling capacitor is necessary to suppress the output supply noise [74, 98]. For the switched capacitor voltage regulator (SCVR), during the SCVR operation, the flying capacitor is charged and discharged periodically, which results in voltage ripple at the VR output port [99–101]. Though the output ripple or VR output supply noise can be reduced by increasing the switching frequency or using a larger flying capacitor [78], the high switching frequency can degrade the power conversion efficiency, and the large flying capacitor can cause longer response time for voltage scaling.

Secondly, the PDN component causes voltage fluctuation. The PDN component noise mainly consists of IR drop and  $L(di/dt)$  drop, where R and L are equivalent resistance and inductance from the load side of PDN. The IR drop noise is proportional to the current drawn by the chip load. For high-performance chip design, the large number of simultaneously switching cells can cause considerable  $L(di/dt)$  drop and even dominate the supply noise [102, 103]. To reduce the PDN component noise, designers need to reduce PDN impedance by optimizing PDN circuits such as power ground mesh, power pads, and device package. The maximum allowed target impedance is derived to guide this process [40]. However, target impedance methodology, which will be explained in the next subsection, is increasingly difficult to fit with modern VLSI design [69], and can result in over- or under-designed PDN.

Thirdly, intra-core activity variation and inter-core interference can induce supply noise [17]. For example, simultaneous activity variation such as power-on or wake-up can happen on the individual cores and then, induce a significant local voltage droop

that can propagate to adjacent cores. Such a droop may reach 150 mV and may easily exceed the voltage guard bound [17, 104]. If a signal is propagating on a critical path in the victim core, the voltage droop causes extra path delay [105], or result in malfunction [106]. The inter-core noise-timing impact is even severer if the core is located far from power supply ports, such as at the center of shared power and ground mesh [107]. In another scenario, if adjacent cores stay in retention mode or idle mode, the parasitic capacitance in those cores can be used to mitigate the noise and consequent timing impact [108].

Finally, the above factors need to be considered jointly since each component is interdependent with each other. Hence, noise mitigation for a PDN system becomes a very difficult and complex problem. This dissertation will divide and conquer the problem in two aspects. The first aspect is the low noise PDN design methodology. The second aspect is the noise mitigation system. The background of these two aspects are presented in Section 1.1.2 and Section 1.1.3, respectively.

### 1.1.2 Low Noise PDN Design Methodology

Low noise PDN design is highly demanded for robust high-performance chip design. As is reported in [109], chip operation frequency can be improved by reducing the PDN impedance. Meanwhile, power consumption is a key concern of high-performance chip design. A low noise PDN design can reduce the overall power consumption, which in turn, decreases the hardware resource cost such as the number of power and ground pads [75, 110]. Therefore, for large scale and heterogeneous systems such as system-on-package (SOP) architectures, the requirement for sophisticated low-noise PDN will increase [22].

As a common practice, PDN design is based on target impedance methodology, which was first proposed by Smith *et al.* [40] in the 1990's. The basic idea of this methodology is to define an upper bound of PDN impedance, which is the target impedance. Target impedance  $Z_{target}$  can be defined as:

$$Z_{target} = \frac{V_{max\_drop}}{I}, \quad (1.1)$$

where  $V_{max\_drop}$  is the maximum allowable voltage drop, and  $I$  is the current requirement. In some works, the maximum allowed voltage drop is also noted as voltage guard bound, power supply tolerance, or noise margin. Depending on the design feature,  $V_{max\_drop}$  ranges from 5% to 10% of nominal voltage [40, 111]. The noise margin requirement is increasing with the advancement of technology and design complexity. For example, the necessary noise margin can reach 20%-30% of nominal voltage for 45nm and below IC chip design [16]. The current requirement  $I$  is selected as 50% of peak switching current [40], or maximum averaged current [69]. According to (1.1), if refined PDN impedance is smaller than  $Z_{target}$ , then the maximum voltage drop will be smaller than design constraints  $V_{max\_drop}$ .

Figure 1.5: Refining PDN impedance to meet target impedance constraint.

Figure 1.6: Decoupling capacitors allocation at different stages of PDN to reduce the PDN impedance.

The design flow of PDN impedance can be demonstrated as Fig. 1.5, where the target impedance magnitude is shown as the black dot line. PDN impedance magnitude is shown as the blue line. Since the impedance of board and package will be inevitably dominated by inductive impedance in high-frequency range, the original PDN impedance magnitude can exceed the target impedance, which is shown as dotted lines in Fig. 1.5.

The PDN impedance can be effectively reduced by allocating decoupling capacitors. This method was introduced in the early 1990's for mitigating the delta-I noise on the VLSI package I/O [37]. Later, various methods are proposed for allocating on-chip and off-chip decoupling capacitors considering different design constraints such as area, hardware cost, and maximum allowed voltage drop [38–40, 112, 113]. An example of decoupling capacitors allocation is depicted in Fig. 1.6, where the decoupling capacitor models are surrounded in the blue boxes. PDN designers need to consider design constraints and select various decoupling capacitors so that PDN impedance is lower than the target impedance from DC to at least the first harmonic of the clock frequency.

The target impedance methodology builds a simple, but over-simplified relation-

Figure 1.7: Power delivery network (PDN) with reactive noise mitigation system. Red wire is power line, black wire is ground line, and blue wire is control signal line.

ship between time-domain voltage drop constraints and frequency-domain PDN design guidance, and conveys a blind belief that, if maximum voltage drop is above the voltage guard bound, the chip load performance is ensured. However, such a belief usually causes over- or under-designed PDN. The details will be described in Section 1.2.2.

### 1.1.3 Supply Noise Mitigation System

With the trend of ever-increasing power consumption and decreasing supply noise margin shown as Fig. 1.2, the supply noise mitigation system becomes an important component for modern low power designs. The typical noise mitigation system is commonly designed in reactive flavor shown as Fig. 1.7, where the blue boxes represent the components of noise mitigation system including noise sensor component, and noise mitigation component. The noise mitigation system firstly measures the supply noise, and then, the measured result is sent to the noise mitigation component, which modulates various PDN components to mitigate supply noise. For the noise sensing part, compared with off-chip noise sensor structure [70, 74], on-chip sensor structures such as in-situ monitor [114–118] and on-chip path monitor [71, 72, 119, 120] have shorter response time.

For the noise mitigation component, off-chip voltage regulators can be modulated for dynamic voltage scaling purposes [47–52], but their response time is too slow compared with emergent supply noise in VLSI which can occur within tens of clock cycles. Low-dropout (LDO) voltage regulator [53–57] is commonly applied to suppress the supply noise, because LDO has simple structure and fast response time. Besides, Paul *et al.* [58] try to stagger the multi-core activation and achieved 10% less voltage droop. However, this method typically has over 100 ns transient process, which is not suitable for emergent noise droop. Meanwhile, staggering activation can cause even

larger voltage droop if the core activation is scheduled at the undershoot period of load voltage resonance [20]. Lam *et al.* [121] and Kaplan [122] intentionally schedule the clock skew to reduce the simultaneous switching cell count and hence, reduce peak supply voltage noise. Kim [60] exploits the clock-data compensation effect to relieve the voltage scaling requirement. Fan [61] applies the two-phase clock tree to reduce the simultaneous switching noise (SSN). Bhowmik [20] combines the staggering activation and frequency scaling to mitigate supply the noise. However, these methods require detailed on-chip clock and timing path design, which introduces additional design complexity and cost for the overall PDN system. Other researchers [123–125] use an analog amplifier to compensate supply noise. However, their methods still suffer from large area overhead or slow response time.

Though various methods are proposed for the reactive noise mitigation system, these methods often fail to compensate for emergent supply noise due to the long latency of PDN voltage boosting. To conceal such latency, proactive noise mitigation system using voltage scaling is studied in this dissertation. The details are described in Section 1.2.1.

## 1.2 Major Challenges for Robust Power Distribution

This section summarizes the major challenges for the existing PDN design methodology and supply noise mitigation system. This dissertation will focus on two major challenges for low-noise PDN design and supply noise mitigation system. The first challenge is related to supply noise mitigation. Existing long-term prediction requires high computation cost and consequently longer computation latency, which makes further longer-term prediction requirement. The challenge of negative noise mitigation loop makes proactive noise mitigation less effective. The second challenge is related to PDN design methodology. The traditional target impedance requirement is increasingly difficult to meet, and the timing impact is still invisible for off-chip PDN designers. These design gaps challenge can lead to over- or under- design PDN. The details and related works for these two major challenges are described in the followings.

### 1.2.1 Negative Loop Challenge of Supply Noise Mitigation

The negative loop challenge of noise mitigation is diagrammed in Fig. 1.8, where the original PDN system is shown in white boxes and bounded by dotted lines. Red arrows show the control flow of the proactive noise mitigation system, which consists of two steps marked in orange boxes. Firstly, noise prediction is performed, and then the noise mitigation decision is deduced and sent to the voltage scaling step to compensate for the incoming supply noise. In proactive mitigation system, the noise mitigation is performed before actual noise happens. The leading time of mitigation is denoted as prediction length, namely how far future is predicted. Meanwhile, the noise mitigation is usually delayed due to systematic issues such as voltage sensing latency or

Figure 1.8: Negative loop challenge of supply noise mitigation.

voltage boosting latency through PDN. The delayed time is denoted as PDN latency. To proactively mitigate the noise, the prediction length should be longer than PDN latency. However, there are bottlenecks in both noise prediction step and voltage scaling step, which result in long PDN latency and short prediction length, and hence form a negative design loop challenge.

### Noise Prediction Bottleneck

The first bottleneck exists in the noise prediction step. Proactive noise mitigation relies on accurate prediction with low hardware and computational cost, and the prediction is supposed to be deduced from hardware signal switching events [126]. In [127–129], power, voltage drop, and timing delay prediction are studied. These studies commonly use internal hardware signals such as control signal and pipeline status registers as input features, and use linear kernel support vector machine (SVM) as the prediction engine.

However, directly monitoring a large amount of chip internal signals can result in overwhelming hardware overhead. Even though hardware signal features are carefully selected using correlation analysis, the prediction length reaches only 16 cycles [129]. Meanwhile, accurate SVM prediction is often achieved with kernel functions and a large number of support vectors, which means high computational cost for floating-point multiplication and addition over many support vectors. This expensive computation causes large hardware overhead and longer computation time of over 40 cycles [127], which requires even longer prediction length. Thus, a negative design loop arises for noise mitigation system.

## Voltage Scaling Bottleneck

The second bottleneck exists in the voltage scaling step. Proactive noise mitigation requires quick and continuous voltage scaling with a wide scaling range and small voltage ripple. However, this requirement is difficult to meet by using traditional voltage regulator solutions such as switching regulator, LDO, and SCVR.

The switching regulator solution can achieve 80% to 90% efficiency with simple structure [130]. However, the inductor component and decoupling capacitor component cause very long transient time, which makes low-latency voltage scaling infeasible. Lin *et al.* [131] try to integrate switching regulator on SoC to scale the load voltage. However, the inductor and capacitor components in this work introduce over  $10\ \mu\text{s}$  voltage scaling latency, which is too long to mitigate emergent VLSI supply noise. The LDO solution is widely adopted for high-performance VLSI design because it has a simple structure, small area overhead, and quick response time [53–55]. However, LDO can only scale down the voltage at the cost of heat generation and energy loss. Besides, LDO drops out voltage using a resistor, and hence LDO efficiency degrades when the voltage scaling range is large.

The SCVR solution is promising for modern VLSI design, since the major advantage of SCVR is high efficiency and high integration capability with chip package. SCVR for VLSI solution is firstly proposed by Dickson [77]. Gu [67] introduced on-chip digital SCVR to stabilize supply voltage. Wang *et al.* use on-chip SCVR in multi-core SoC implementations to achieve fine-grained DVFS [132].

However, SCVR has limited voltage scaling flexibility due to the fixed conversion ratio, which is not desirable for wide-range continuous voltage-scaling purpose [133–135]. Besides, SCVR can introduce supply voltage ripples during the flying capacitance charge and discharging process. The ripple issue can be suppressed by using a large flying capacitor or increasing the switching frequency. However, the high switching frequency can degrade the power conversion efficiency, and a large flying capacitor pushes the SCVR away from chip load, resulting in slow voltage scaling response time. To mitigate the ripple, Jevtic [136] uses on-chip frequency scaling to cancel the ripple impact. Breussegem and Steyaert [49], and Lu [52] use multi-phase SCVR to reduce ripple. However, these efforts cannot improve the voltage scaling capability of SCVR.

To improve the voltage scaling capability of SCVR, researchers try to introduce the low-dropout (LDO) voltage regulator as a secondary linear regulator [56, 57, 79–81, 137, 138]. However, the low energy efficiency problem for LDO is not desirable for low power devices. Other researchers try to improve the voltage scaling capability by proposing various SCVR structures. For example, Eireiner [116] and Pillonnet [139] use multi-VDD SCVR to achieve voltage scaling. Souvignet [50], Andersen [51], and Nguyen [78] use multiple SCVRs with different conversion ratio to switch between different output voltage levels. However, these solutions only provide discrete voltage levels, and multi-SCVR solution can introduce over 100 mV ripple during voltage level during transient switching process [48]. Andersen [51] and Jiang [140] try

Figure 1.9: PDN design gap challenge.

to scale the voltage using multiple-conversion-ratio SCVRs or re-configurable SCVR. However, when dynamically switching the conversion ratio, the output ripple can be beyond 70 mV, which is 8.2% of load voltage [100]. Researchers also use multiple SCVRs to implement recursive SCVR structure [47, 141–144]. By dynamically reconfigure the connection between SCVRs, different output voltages can be obtained. However, recursive SCVR requires complex switching control circuits to avoid short current and to ensure the correct functionality of switches, resulting in extra hardware cost and efficiency loss, yet the output voltage ripple during voltage scaling is not well handled. Bang [101] tries to dynamically adjust flying capacitors according to load current, but this solution causes extra hardware cost to allocate many tiny capacitor groups.

In summary, SCVR has the advantage of high efficiency and high power density, though the voltage scaling and ripple issue are still open problems for traditional SCVR structure. This dissertation will use SCVR as a base structure for voltage scaling solution and overcome the limitations.

### 1.2.2 Gap Challenge in PDN Design Methodology

Traditional PDN design methodology usually results in under- or over-designed PDN, because there exists a gap challenge in the traditional PDN design loop. The design gap challenge can be diagrammed by Fig. 1.9, where the original PDN system is shown in white boxes and bounded by dotted lines. Red arrows show the PDN design loop and the design step with gap issues marked in red boxes. In this diagram, PDN designers firstly derive target impedance as design guidance. Then, PDN impedance is refined so that the target impedance constraint is satisfied. To verify and explore the PDN design under various chip load operation scenarios, a chip load model is needed to expose the impact of supply noise. PDN designers will further refine the PDN circuit according to the noise impact. Such a design loop can iterate several rounds to achieve the balance between PDN performance and cost.

Figure 1.10: Two voltage profiles with same maximum voltage drop.

However, in the target impedance design stage, there lacks a proper method to bridge the time-domain voltage drop constraints and frequency-domain target impedance guidance. Meanwhile, the existing chip load modeling method cannot provide on-chip timing information within a reasonable simulation time and hence, timing impact is invisible to PDN designers. Such gaps can result in under- or over-designed PDN, and unexpected supply noise impact.

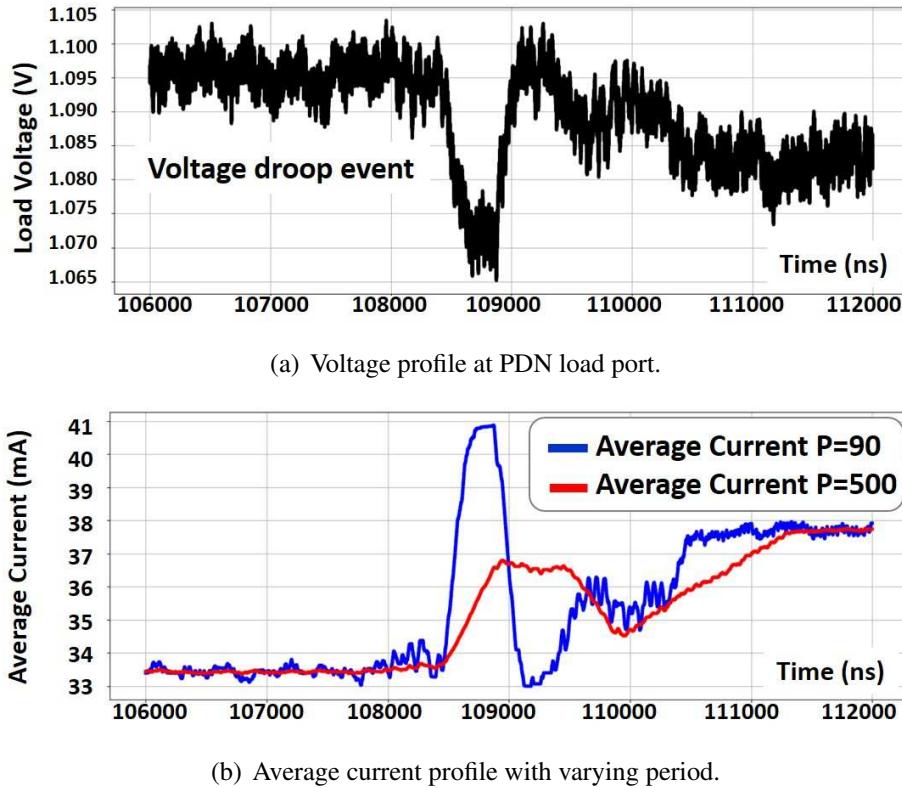

### Gap between Target Impedance and PDN Design Constraints

The first gap exists between target impedance and PDN design constraints, and ignoring the gap can result in under- or over-designed PDN. Such a gap problem arises because actual PDN impedance is defined in the frequency domain while the current profile and voltage drop constraint are given in time domain. Although the current spectrum tells us that dynamic power noise distributes within a certain frequency range, how to determine detailed frequency-dependent target impedance remains an open difficult problem. Besides, the average voltage drop constraint is not well handled in traditional target impedance, while the average drop can have a greater impact on chip performance than dynamic noise [18, 44, 94].

Let us take the voltage profiles in Fig. 1.10 to illustrate the gap impact. Here, given a load current profile, suppose two PDNs having different target impedance that satisfy the same maximum voltage drop constraint. Two voltage profiles corresponding to the different PDNs are depicted in red and blue. The red profile has lower average voltage and smaller ripple, which means chip performance is lower and the PDN for the red profile is over-designed in high-frequency range but under-designed in the low-frequency range.

To address this gap issue, researchers [145–150] try to approximate the time domain current profile as triangle or ramp so that the delta- $I$  noise, or  $L(di/dt)$  noise becomes a constant value and the PDN design flow is simplified. However, such approximation methods suffer from the fact that real current waveform may not be easily simplified to

the simple ramp or triangle shape. Oh *et al.* [151] use the current spectrum for deriving frequency-dependent target impedance. However, the constraint of the worst voltage drop, which is defined in the time domain, is difficult to convert into the frequency domain. Without a clear interpretation between the time domain and frequency domain, PDN designers have to rely on empirical methods such as iteration over the various resistor and capacitor configurations [152, 153].

### Gap between On-Chip Timing and Off-Chip PDN Verification Exploration

On-chip timing information is the primary metric in digital chip design. However, such timing information is usually invisible to off-chip PDN designers, which results in a design gap between on-chip timing and off-chip PDN design processes. As is discussed in [41, 42, 44–46], the worst voltage drop does not necessarily reflect the actual worst timing delay. Meanwhile, timing sensitivity to noise becomes severer with the scaling down of the technology [18–21], and therefore, ignoring such gap can mislead the PDN design.

The design gap problem is difficult to address because there lacks a simple yet accurate chip load model, which can expose the on-chip timing information while considering the voltage-current-timing interdependency and operation mode transition. The interdependency conception can be demonstrated in Fig. 1.11. In actual circuits, the supply noise interacts with chip timing performance such as clock latency and path delay [154, 155]. When supply voltage drops, signal propagation is delayed, clock latency gets longer, and the transistor switching current becomes smoother and smaller. When the load current becomes smaller due to the supply voltage drop, the dynamic noise becomes smaller, and its impact is naturally mitigated. However, simplified models such as the current source model in the piecewise linear format are irrelevant to voltage variance, and hence the supply noise is likely to be overestimated.

As for the operation mode transition requirement, in multi-core designs, there are many combinations of mode transitions. Also, their transition timings could affect noise magnitude and timing performance. To efficiently explore the impacts of modes and their transitions, the chip load model should have an interface that can easily and flexibly manipulate the operation modes of individual cores, which contributes to finding unexpected noise and consequent timing behaviors.

To fill the PDN-chip gap, researchers [16, 17, 120, 156–159] proposed various on-chip measurement modules that are used in the post-silicon validation stage. Modules such as critical path replica [157, 159, 160] and critical path monitor [120, 132] are developed to measure chip internal timing information. However, the inherent limitation of the post-silicon methodology is the silicon resource cost and the difficulty in design modification due to the late feedback. On the other hand, the pre-silicon simulation requires no silicon resource and provides feedback in design time. To perform the simulation, meanwhile, a chip load model that represents the chip behavior from the point of view of load current is necessary. The chip load model that consists of the on-chip

Figure 1.11: Voltage-current-timing interdependency.

PDN model and full transistor-level switching circuit model can replay the on-chip behavior with high accuracy. However, even a very short period run takes days or even months to finish. Extensive PDN design exploration is infeasible. To reduce the computational cost for the chip load model, the switching circuit is often modeled by a current source [92, 93] or equivalent RC circuit models [30, 94, 95]. Cui prepares multiple current profiles and manually switches the profile for different operation modes [92]. However, the current source model is usually described with a current profile in a piecewise linear format. Once a current profile is obtained under a given supply voltage, these piecewise linear current values are irrelevant to supply voltage variation. Hence, a large simulation error is introduced when the actual supply voltage has a significant dynamic supply noise. The current source can be also modeled by voltage-controlled current source (VCCS) [96, 97] to take into account the dependence of current on voltage. However, VCCS relies on instant voltage-current scaling, which is not suitable for replaying temporal behavior. On the other hand, RC circuit model can roughly model the voltage-current interdependency. This modeling method uses variant resistors, typically implemented by VCCS, to mimic the equivalent resistance of on- and off-state transistor. Then parasitic capacitors are characterized to mimic cell transition delay. However, even with careful characterizing effort on RC parameters, the over-simplified RC model is difficult to replay a detailed current profile for large-scale circuit operation.

Figure 1.12: Existing challenges for supply noise mitigation and PDN design.

Figure 1.13: Proposed solutions for proactive noise mitigation and PDN design methodology.

## 1.3 Objective and Organization

The overall objective of this dissertation is to robustly provide the low-noise supply voltage through a VLSI power distribution system. To achieve the objective, this dissertation proposes a proactive noise mitigation system, and improves the PDN design methodology.

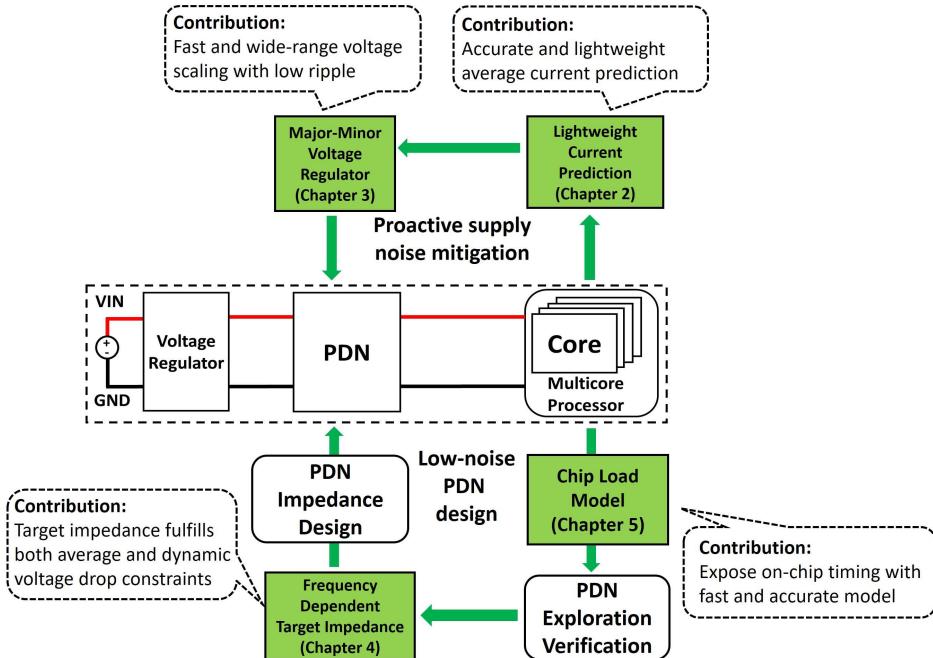

There are two main challenges and four problems in existing noise mitigation system and PDN design methodology. They are discussed in the previous Section 1.2 and summarized as Fig. 1.12, where the negative loop challenge is shown in the upper part, the design gap challenge is shown in the lower part. The main problems for each challenge are marked in the orange box. The contributions, proposed methods, and overall organization of this dissertation are diagrammed in Fig. 1.13, and each solution is marked in the green box. The proposed methods in Chapter 2 and Chapter 3 are used to construct the proactive noise mitigation system. The proposed methods in Chapter 4 and Chapter 5 aim to improve PDN design methodology.

The first contribution in Chapter 2 is to provide a lightweight current prediction solution, which is to solve the noise prediction bottleneck. The main difficulty here is to predict the near future noise with high accuracy and reasonable hardware overhead. The key idea to achieve this objective is to construct a lightweight short-term average current predictor using decision tree regressor. The decision tree regressor uses the instruction history of the processor as the input feature and averaged current as the prediction label. Based on the training result in the experiment, a six-layer decision tree predictor is implemented, and it achieves 50-cycle prediction length and over 0.99 correlation.

The second contribution in Chapter 3 is to provide a major-minor voltage regulator (MMVR) structure, which is to provide the fast and wide-range voltage scaling capability to solve the voltage scaling bottleneck. The main difficulty here is that traditional SCVR is not suitable to continuously scale the voltage because of the fixed conversion ratio. The key idea to overcome the difficulty is to propose a new major-minor voltage regulator (MMVR) structure, which consists of two SCVRs whose flying capacitance is much different. Major voltage regulator uses large flying capacitance to provide stable low ripple supply voltage. On the other hand, the minor voltage regulator is designed as a re-configurable SCVR structure, which can provide two different load voltage levels with small flying capacitance. This special structure enables minor voltage regulator to continuously scale supply voltage using simple switching frequency modulation. Meanwhile, a small flying capacitance means the capacitors in the minor voltage regulator can be integrated into a chip package to speed up voltage scaling. According to the experiment, MMVR achieved over 3X voltage scaling range compared with traditional SCVR while the ripple is within 16 mV, which is 1.6% of load voltage.

The third contribution in Chapter 4 is to provide a frequency-dependent target impedance methodology, which is to fill the gap between PDN voltage drop constraints and frequency domain impedance guidance. The main difficulty here is to bridge the

time domain voltage drop constraints and current profile with the frequency domain impedance curve. The key idea is to design the target impedance by introducing a new conception of magnitude equivalent frequency (MEF). That is, instead of analyzing the detailed time-domain current waveform, a sine waveform current can be used to reproduce the same magnitude of the voltage noise. The frequency of this sine waveform is defined as MEF. The conception of MEF can bridge the design gap and hence simplify the frequency-dependent target impedance design. The experiment confirmed that the synthesized target impedance satisfied the constraints with less than 0.1% error in the actual processor load case.

The fourth objective in Chapter 5 is to propose a chip load model that can provide the on-chip timing information, which is to fill the gap between off-chip PDN design and on-chip timing information. The main difficulty here is to construct a fast and accurate load model that can consider the voltage-current-timing interdependency and operation mode transitions. The key idea is to use the time-voltage-variant resistor to reproduce voltage-dependent load current taking into account voltage-dependent switching delay for a given operation mode. Then, multiple time-voltage-variant resistors are enabled or disabled by control logic interface so that mode transition is triggered. Critical paths are represented by the critical path replica module to replay critical path timing delay. Also, parasitic and intrinsic decoupling capacitances are modeled using small-signal analysis. Hence, the global and local clock latency, skew, and path delays can be computed with simulation. The experiment confirmed that the proposed chip load model achieves better correlation compared with the traditional current source based model and RC based model, while over 300X runtime reduction is achieved compared with full SPICE netlist simulation. The off-chip PDN modification experiments show the proposed model can guide off-chip PDN designers with on-chip timing information.

The rest of this dissertation is organized as follows. Chapter 2 presents the proactive noise mitigation system consisting of lightweight near-future current prediction and noise mitigation controller. The prediction is achieved by applying machine learning technology. Chapter 3 proposes a major-minor SCVR structure to achieve fast and wide-range voltage scaling. Chapter 4 proposes a frequency-dependent target impedance methodology to guide PDN design. The methodology considers both dynamic voltage drop and average voltage drop constraints. Chapter 5 presents chip load model which can expose the on-chip information for PDN verification. This capability is achieved by considering voltage-current-timing interdependency and operation mode transitions of chip load. Lastly, concluding remarks are given in Chapter 6.

# Chapter 2

## Lightweight Short-Term Current Prediction

To break the negative noise mitigation loop challenge discussed in Section 1.2.1, this chapter proposes a near-future current prediction method, which can accurately and quickly predict the near-future averaged current of chip load. The proposed method satisfies the prediction length requirement for the proposed proactive noise mitigation system.

### 2.1 Introduction

With the scaling down of the technology node, both power consumption and supply noise are continuously increasing, which causes timing degradation or even malfunctions in modern VLSI chips. Traditional reactive noise mitigation often fails to compensate for emergent supply noise due to the long latency of voltage boosting through the power delivery network (PDN). To conceal such latency, power/current prediction is studied toward proactive noise mitigation [127–129]. Proactive noise mitigation relies on accurate predictions with low hardware and computational cost. However, existing long-term prediction requires high computation cost and consequently longer computation latency, which makes further longer-term prediction requirements. This negative loop makes proactive noise mitigation less effective. To address this negative loop challenge, this chapter proposes a lightweight short-term average current predictor that achieves 50-cycle prediction length and over 0.99 correlation with a six-layer decision tree (DT) regressor.

The rest of this chapter is organized as follows. Section 2.2 explains the overall structure of the proposed proactive noise mitigation. Section 2.3 discusses the construction of lightweight near-future current predictor. Section 2.4 presents the controller and sensor structure of proactive mitigation system. Section 2.5 shows experimental results using RISC-V design. The conclusion of this chapter is given in Section 2.7.

Figure 2.1: Proposed structure for proactive supply noise mitigation. Red lines are power wires, black lines are ground wires, and blue lines are control signal wires.

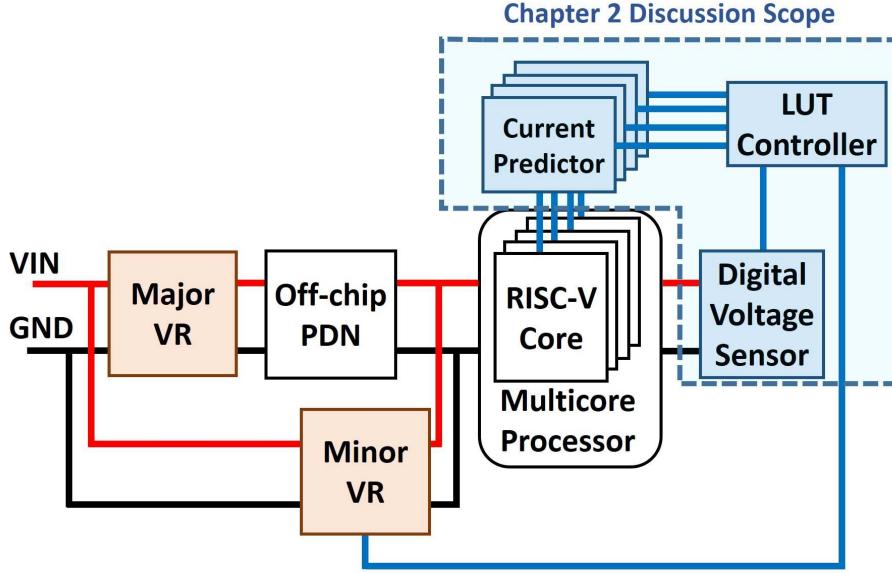

## 2.2 Overall Structure of Proposed Proactive Noise Mitigation

This section describes the overall structure of the proposed proactive noise mitigation. Fig. 2.1 shows the overall PDN structure with the proactive supply noise mitigation, where off-chip PDN and multicore processor are included in the original design. In this chapter, RISC-V Rocket core [161], which is an in-order single-issue core, is used in the processor module as an example. Here, it is noteworthy that the proposed method is basically independent of the processor core while minor ISA-dependent adaptation is necessary.

The first key component is the major-minor voltage regulator (MMVR), which is shown as orange boxes in Fig. 2.1. The major VR is placed outside the chip and serves as the main power supplier. The minor VR is placed close to the cores, possibly on the chip, and serves as a voltage regulator to mitigate noise. The second key component is the prediction and control units, which are shown as blue boxes in Fig. 2.1. For each RISC-V core, the dedicated current predictor obtains instruction information from I/O ports and then predicts future average current. The controller sums up the prediction results and decides noise mitigation action using a lookup table (LUT). A digital voltage sensor is equipped to override the mitigation action if the voltage is too high or too low for fail-safe purpose. Finally, the action signal is sent to minor VR for noise mitigation.

The remaining of this chapter details the current predictor and controller compo-

nents, which are surrounded by dotted blue lines in Fig. 2.1. Chapter 3 will present the details of MMVR.

## 2.3 Lightweight Short-Term Current Predictor

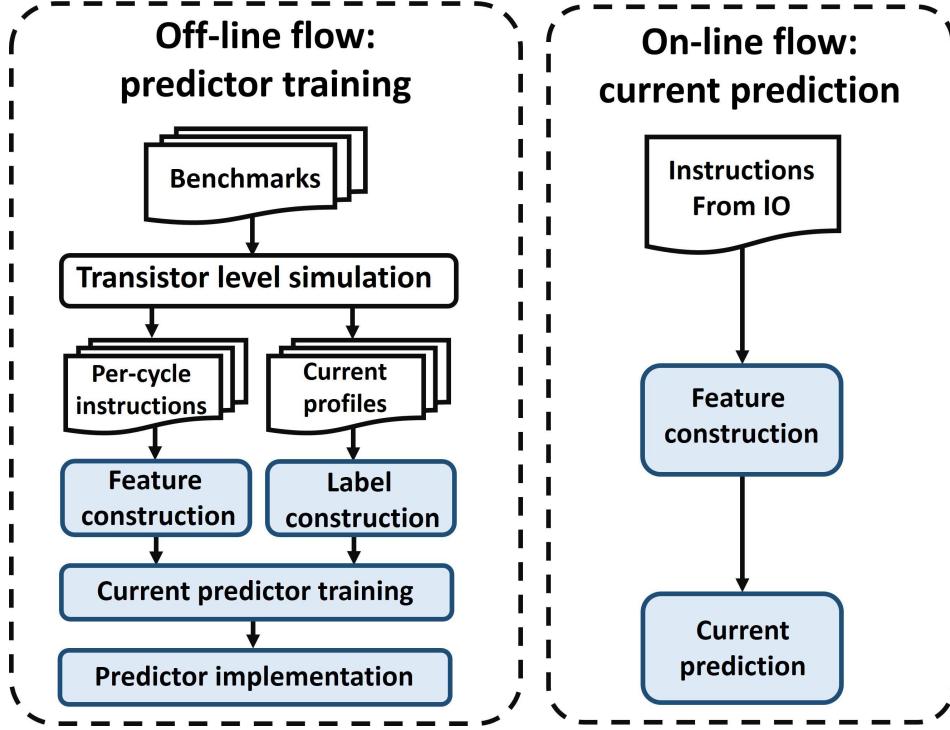

This section details the short-term current predictor. Fig. 2.2 shows the training and prediction flows of the predictor, where the left side illustrates the off-line training stage and the right side shows the on-line current prediction flow. The key training and prediction procedures are represented in blue blocks.

In the off-line training stage, firstly the training data is prepared from benchmark programs. Simulation is performed to generate current profiles and obtain the instruction at I/O ports for every cycle with logic/circuit simulator or power estimation tools. Then, a set of training label and features are constructed from the instructions and raw current profiles. After that, a decision tree-based predictor is trained. The predictor hardware is implemented accordingly using the training result. In the on-line current prediction stage, firstly the instructions are obtained from I/O ports. Next, the features are constructed and given to the predictor. The prediction results are collected to the controller for MMVR. The label and feature construction, and hardware implementation are discussed in the following.

### 2.3.1 Prediction Label Construction