| Title        | Sneak Path Free Reconfiguration and Fault<br>Diagnosis for Via-Switch Crossbar Based FPGA |

|--------------|-------------------------------------------------------------------------------------------|

| Author(s)    | 土井, 龍太郎                                                                                   |

| Citation     | 大阪大学, 2020, 博士論文                                                                          |

| Version Type | VoR                                                                                       |

| URL          | https://doi.org/10.18910/76647                                                            |

| rights       |                                                                                           |

| Note         |                                                                                           |

## Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

# Sneak Path Free Reconfiguration and Fault Diagnosis for Via-Switch Crossbar Based FPGA

# Submitted to Graduate School of Information Science and Technology Osaka University

January 2020

Ryutaro DOI

## **Publications**

### **Academic Journal**

- [AJ1] R. Doi, J. Yu, and M. Hashimoto, "Sneak Path Free Reconfiguration with Minimized Programming Steps for Via-switch Crossbar Based FPGA," *IEEE Transactions on Computer-Aided Design of Integrated Circuits and Systems*, (accepted).

- [AJ2] H. Ochi, K. Yamaguchi, T. Fujimoto, J. Hotate, T. Kishimoto, T. Higashi, T. Imagawa, R. Doi, M. Tada, T. Sugibayashi, W. Takahashi, K. Wakabayashi, H. Onodera, Y. Mitsuyama, J. Yu, and M. Hashimoto, "Via-Switch FPGA: Highly Dense Mixed-Grained Reconfigurable Architecture With Overlay Via-Switch Crossbars," *IEEE Transactions on Very Large Scale Integration (VLSI) Systems*, vol. 26, no. 12, pp. 2723–2736, Dec 2018.

- [AJ3] R. Doi, M. Hashimoto, and T. Onoye, "An Analytic Evaluation on Soft Error Immunity Enhancement due to Temporal Triplication," *International Journal of Embedded Systems*, vol. 10, no. 1, pp. 22–31, January 2018.

### **International Conference**

- [IC1] R. Doi, X. Bai, T. Sakamoto, and M. Hashimoto, "Fault Diagnosis of Via-Switch Crossbar in Non-volatile FPGA," in *Design, Automation, and Test in Europe Conference and Exhibition (DATE)*, (accepted).

- [IC2] M. Hashimoto, X. Bai, N. Banno, M. Tada, T. Sakamoto, J. Yu, R. Doi, Y. Araki, H. Onodera, T. Imagawa, H. Ochi, K. Wakabayashi, Y. Mitsuyama, and T. Sugibayashi, "Via-switch FPGA: First Implementation in 65-nm CMOS and Architecture Extension for AI Applications," in IEEE International Solid-State Circuits Conference (ISSCC), (accepted).

- [IC3] **R. Doi**, J. Yu, and M. Hashimoto, "Sneak Path Free Reconfiguration of Viaswitch Crossbars Based FPGA," in *IEEE/ACM International Conference on*

- Computer-Aided Design (ICCAD), Nov 2018, pp. 1–8.

- [IC4] R. Doi and M. Hashimoto, "SAT Encoding-Based Verification of Sneak Path Problem in Via-Switch FPGA," in *IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, July 2018, pp. 429–434.

- [IC5] M. Hashimoto, Y. Nakazawa, R. Doi, and J. Yu, "Interconnect Delay Analysis for RRAM Crossbar Based FPGA (invited)," in *IEEE Computer Society Annual Symposium on VLSI (ISVLSI)*, July 2018, pp. 522–527.

- [IC6] J. Hotate, T. Kishimoto, T. Higashi, H. Ochi, R. Doi, M. Tada, T. Sugibayashi, K. Wakabayashi, H. Onodera, Y. Mitsuyama, and M. Hashimoto, "A Highly-dense Mixed Grained Reconfigurable Architecture with Overlay Crossbar Interconnect using Via-switch," in *International Conference on Field Programmable Logic and Applications (FPL)*, Aug 2016, pp. 1–4.

- [IC7] R. Doi, J. Hotate, T. Kishimoto, T. Higashi, H. Ochi, M. Tada, T. Sugibayashi, K. Wakabayashi, H. Onodera, Y. Mitsuyama, and M. Hashimoto, "Highly-dense Mixed Grained Reconfigurable Architecture with Viaswitch," in *ACM International Workshop on Timing Issues in the Specification and Synthesis of Digital Systems (TAU)*, March 2016.

- [IC8] **R. Doi**, M. Hashimoto, and T. Onoye, "An Analytic Evaluation on Soft Error Immunity Enhancement due to Temporal Triplication," in *IEEE Pacific Rim International Symposium on Dependable Computing (PRDC)*, November 2015.

## **Domestic Conference**

- [DC1] 土井 龍太郎, 劉 載勲, 橋本 昌宜, "ビアスイッチ FPGA の部分的再構成 における書き換えスイッチ数の最小化," 情報処理学会 *DA* シンポジウム, August 2019.

- [DC2] Y. Sun, <u>R. Doi</u>, and M. Hashimoto, "RC Extraction-free Wiring Delay Analysis Focusing on Number of On-state Switches for Via-switch FPGA," in *IPSJ DA Symposium*, August 2019.

- [DC3] 土井 龍太郎, 劉 載勲, 橋本 昌宜, "ビアスイッチ FPGA 再構成時のスニー クパス問題を回避するプログラミング順決定手法," 情報処理学会 *DA* シ ンポジウム, August 2018.

- [DC4] 中澤 祐希, 土井 龍太郎, 劉 載勲, 橋本 昌宜, "ビアスイッチ FPGA 向け 配線遅延解析手法の検討," 電子情報通信学会 *VLSI* 設計技術研究会, no. VLD2017-120, March 2018.

- [DC5] <u>土井 龍太郎</u>, 橋本 昌宜, "ビアスイッチ FPGA におけるスニークパス問題の SAT 符号化を用いた検証," 情報処理学会 *DA* シンポジウム, August 2017.

- [DC6] 土井 龍太郎, 橋本 昌宜, 尾上 孝雄, "時間的三重化によるソフトエラー耐性向上の解析的評価," 電子情報通信学会 ディペンダブルコンピューティング研究会, November 2014.

## Workshop

[WS1] J. Hotate, T. Kishimoto, T. Higashi, H. Ochi, **R. Doi**, M. Tada, T. Sugibayashi, K. Wakabayashi, H. Onodera, Y. Mitsuyama, and M. Hashimoto, "Highly-dense Mixed Grained Reconfigurable Architecture with Viaswitch," in *Work in Progress Session, Design Automation Conference* (DAC), June 2016.

## **Summary**

Reconfigurable computing hardware, such as field-programmable gate arrays (FPGAs), is gaining its popularity since the design and manufacturing cost of application-specific integrated circuits (ASICs) is elevating according to the device miniaturization and larger-scale integration. However, the performance and energy efficiency of conventional FPGAs are much lower than those of ASICs. These drawbacks originate from low area efficiency due to static random access memory (SRAM)-based programmable switches that consist of transistors and have a large area, resistance and capacitance.

To overcome the conventional FPGA drawbacks, FPGAs that exploit viaswitches, which are a kind of Resistive RAM (RRAM), instead of SRAM-based switches are actively studied. The via-switch is a non-volatile switch with a small footprint and parasitic load, and it can be implemented and programmed without using transistors. Thanks to its characteristics, the via-switch is expected to boost the performance and energy efficiency of FPGA.

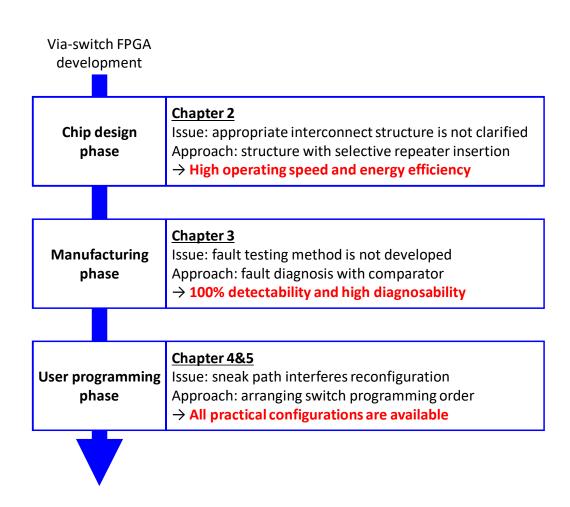

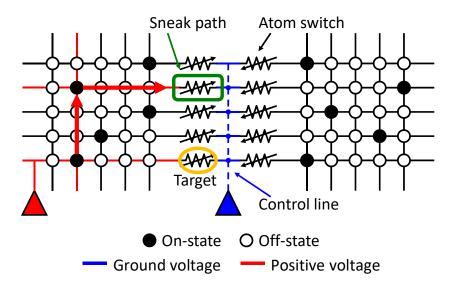

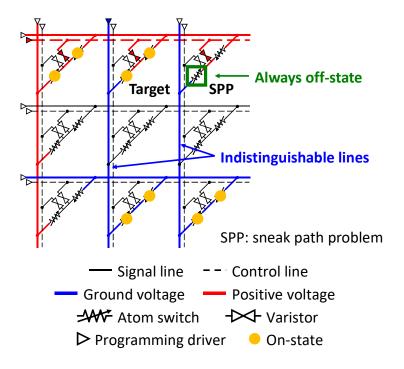

On the other hand, the via-switch FPGA is in an early stage of development and hence facing design, test, and programming challenges for practical application. First, in the design phase, there is no sufficient discussion on the interconnect structure that fully exploits the via-switch advantages. Previous studies on atom switch based FPGAs, where the atom switch is one of the component devices of the via-switch, presented a fundamental structure based on crossbars for higher integration density. Here, the crossbar is a circuit that has a switch device at every intersection of vertical and horizontal interconnections for signal routing. However, the appropriate interconnect structure with the via-switch crossbar is not discussed enough, and the performance improvement effect thanks to via-switches is not quantitatively evaluated. Next, the manufacturing phase requires the via-switch FPGA manufacturer to verify the crossbar functionality before the shipment for ensuring arbitrary routings at the FPGA user side. Therefore, fault testing is indispensable to check whether all the via-switches can be normally turned on/off. However, fault testing methodology for the via-switch crossbar has not been established so far. Meanwhile, in the user programming phase after the shipment, there is a possibility that the sneak path problem occurs due

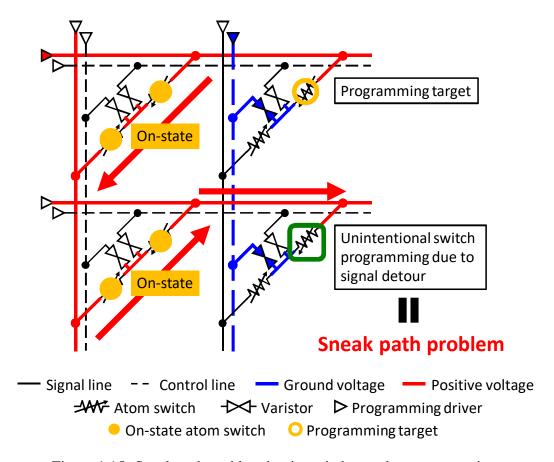

to the crossbar programming structure depending on configuration patterns of via-switches in the crossbar. The sneak path problem changes on/off state of non-target via-switches unintentionally due to programming signal detouring, and interferes the reconfiguration of FPGA. Therefore, it is crucially important to identify the occurrence conditions and develop countermeasures for this problem.

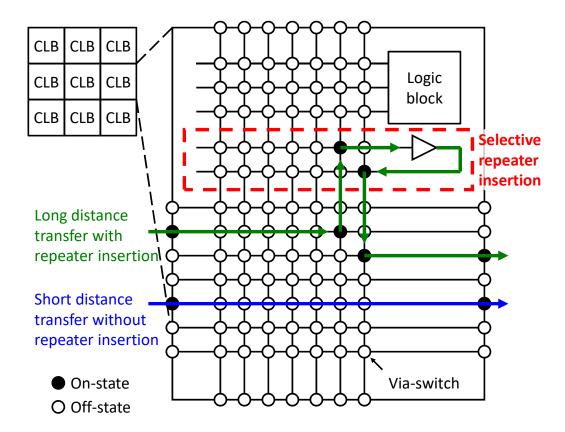

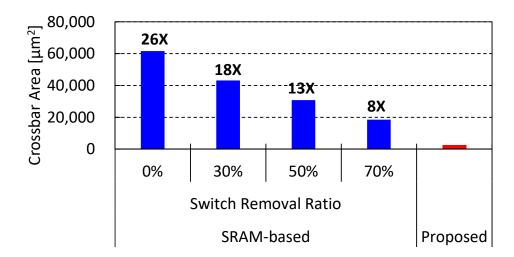

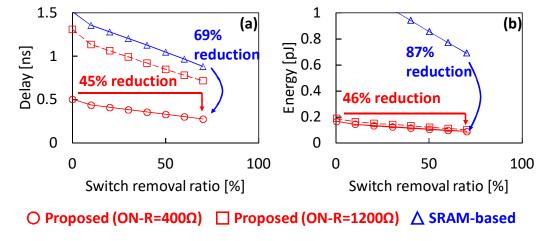

Solving the challenge at the design phase, this dissertation proposes an interconnect structure that can selectively insert repeaters to signal paths and achieve small interconnect delay and high energy efficiency. This work also clarifies the requirement of the programming structure for the connection switch between crossbars focusing on the sneak path problem. Transistor-level SPICE-based evaluation demonstrates that the proposed interconnect structure achieves a significant performance improvement compared with conventional SRAM-based FPGA. The proposed structure reaches 26X higher crossbar integration density and reduces interconnect delay and energy by 90% and 94% at 0.5 V operation.

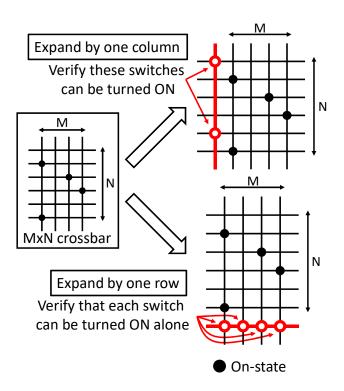

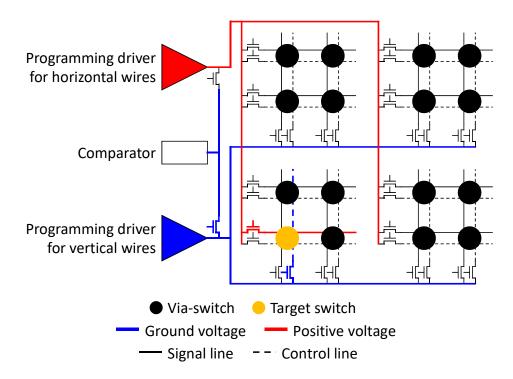

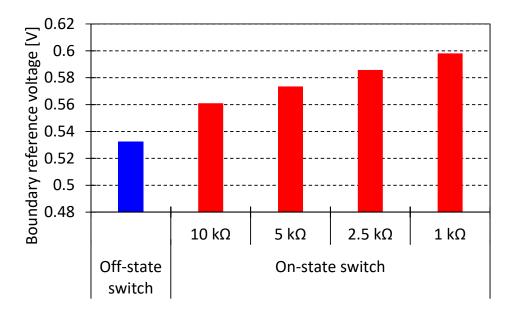

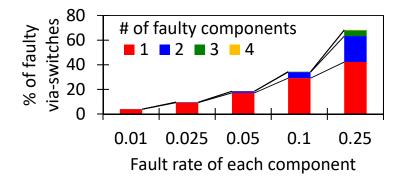

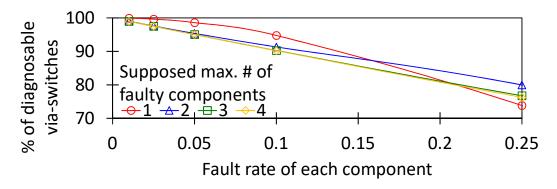

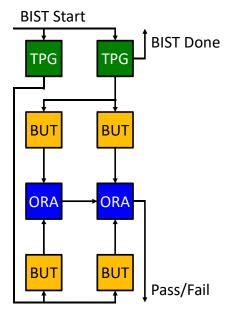

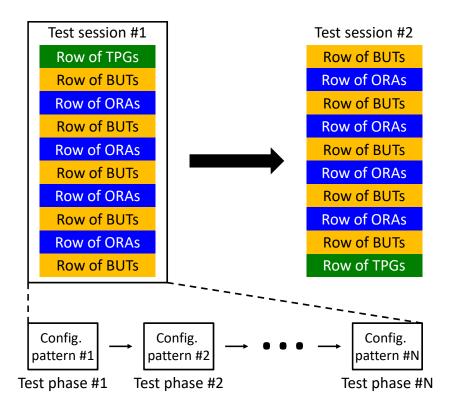

For the challenge at the manufacturing phase, this dissertation proposes a fault testing methodology to verify the via-switch crossbar functionality for ensuring arbitrary routings. This work confirms that a general differential pair comparator successfully discriminates on/off-states of via-switches, where the comparator can be implemented with a small area at the peripheral part of the via-switch FPGA chip. This work also identifies fault modes of a via-switch using SPICE simulation that injects stuck-on/off faults to atom switch and varistor, which are components of via-switches. Then, this dissertation proposes a fault diagnosis method that identifies faulty via-switches in the crossbar according to the comparator response difference between normal and faulty cases. The proposed method attains 100% fault detection. As for the diagnosability, the successful ratios of the fault diagnosis are 100% and 79% in cases that the number of faulty components in a via-switch is up to one and up to two, respectively.

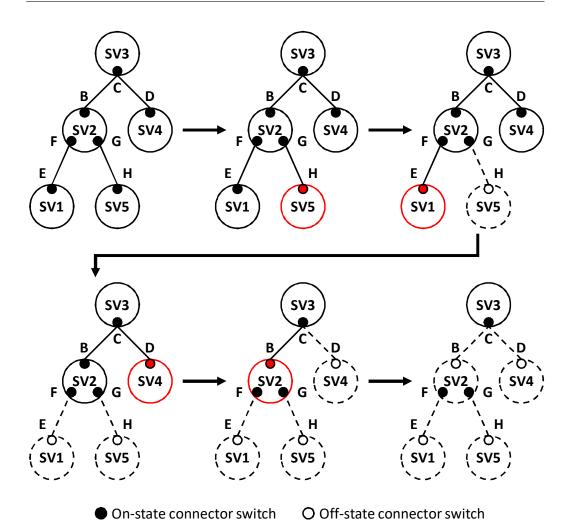

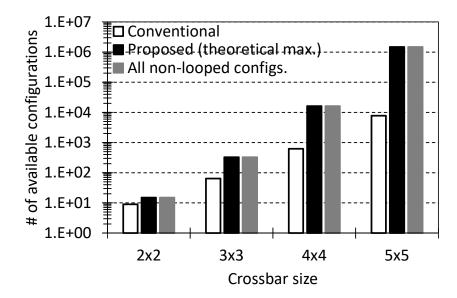

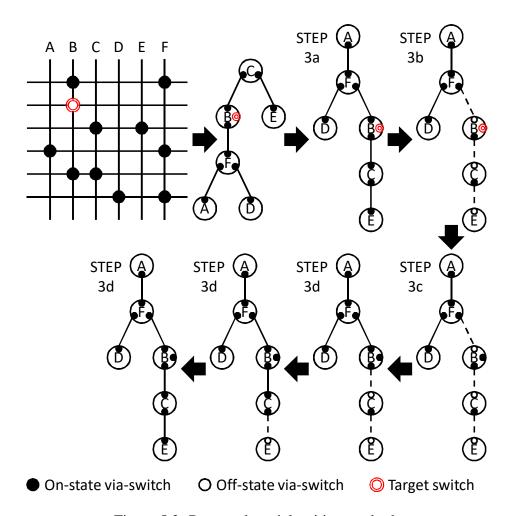

Aiming at overcoming the challenge at the user programming phase, this dissertation establishes a sneak path free reconfiguration methodology of viaswitch crossbar. This work investigates the occurrence conditions of the sneak path problem and identifies the crossbar programming status that causes the sneak path. Based on the occurrence conditions, this dissertation proposes a sneak path free programming method that arranges the programming sequence of via-switches in a crossbar. This work devises an algorithm that effectively derives a sneak path free programming order by constructing the connection status of signal lines in a crossbar as a tree structure, which is called the connection tree. This dissertation also gives a proof that a sneak path free programming order necessarily exists for arbitrary on-off patterns in a crossbar as long as no loops exist. The simulation-based evaluation demonstrates that the proposed method significantly improves the routing flexibility of the via-switch crossbar. In a practically-sized 100x100 crossbar, the number of available configurations

increases by over four orders of magnitude. The proposed method successfully solves the sneak path problem in any practical configurations of via-switch FPGA.

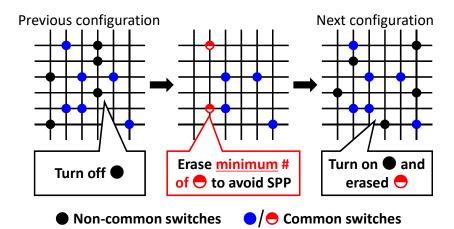

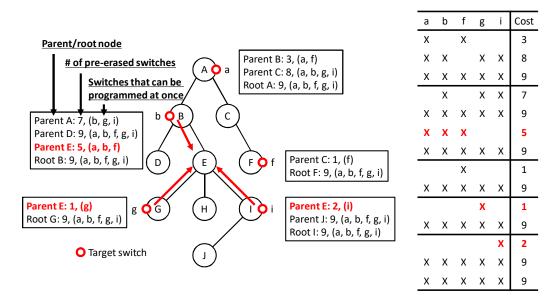

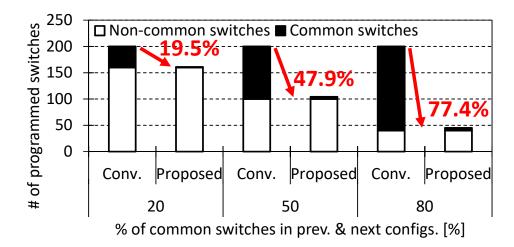

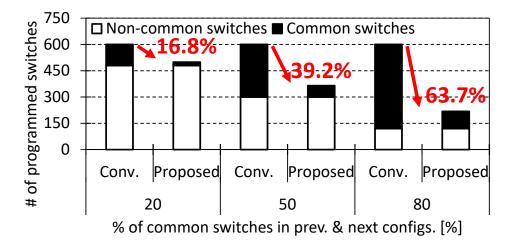

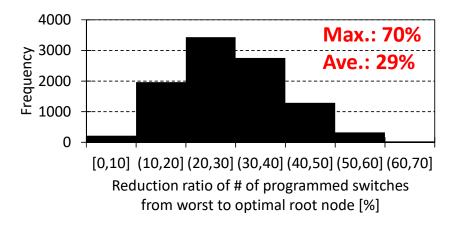

Furthermore, this dissertation extends the above programming method for partial reconfiguration that partially turns on and off via-switches in the already programmed crossbar. This work proposes a partial reconfiguration method that minimizes programming steps while avoiding the sneak path problem. The proposed method minimizes the number of programmed switches by arranging the root node of the connection tree. This work models the optimal root node selection as a set cover problem with cost minimization, and also proposes a low computational complexity method that obtains the same solution of the set cover problem without solving it. In a test case of simulation-based evaluation, the proposed method reduces the number of programmed switches by 77.4% compared to the conventional approach, which enables 4.4X more reconfigurations of the via-switch FPGA in its device lifetime and reduces reconfiguration time by 77.4%.

This dissertation covers challenges at all phases of via-switch FPGA development, i.e., design phase, manufacturing phase, and user programming phase. The proposed interconnect structure contributes to boosting the operating speed and energy efficiency. The proposed fault diagnosis method helps the manufacturer to inspect manufactured products and to prevent the shipment of defective products. The proposed sneak path solution enables to implement all the practical configuration patterns to the via-switch FPGA. The proposed partial reconfiguration method contributes to extending the lifetime of via-switches and speeding up the reconfiguration of the via-switch FPGA for both user programming and manufacturing test. At last, thanks to these contributions, FPGA users can enjoy implementing any systems on high-performance and defect-free via-switch FPGA.

## Acknowledgments

First of all, I would like to express my deepest gratitude to Professor Masanori Hashimoto in Osaka University for providing an excellent research environment and a precious opportunity to have various experiences for seven years of bachelor's, master's, and doctoral courses. He comprehensively supported my research, and his advanced perspective and thoughtful advice led me to successful achievements. I have learned a lot from him and realized the growth of my skills and mind.

I would like to deeply express my appreciation to Associate Professor Jaehoon Yu in Tokyo Institute of Technology for valuable discussions and accurate advice. His thoughtful supports improved my research achievements.

I am grateful to Professor Tatsuhiro Tsuchiya, Associate Professor Ittetsu Taniguchi, and Associate Professor Hiromitsu Awano in Osaka University for detailed reviews and valuable suggestions.

I would like to express great gratitude to Professor Hidetoshi Onodera in Kyoto University, Professor Hiroyuki Ochi in Ritsumeikan University, Associate Professor Yukio Mitsuyama in Kochi University of Technology, Assistant Professor Takashi Imagawa in Ritsumeikan University, Dr. Kazutoshi Wakabayashi, Mr. Tadahiko Sugibayashi, Dr. Toshitsugu Sakamoto, and Dr. Munehiro Tada in NEC Corporation for precious discussions, insightful suggestions, and teaching me the fun of collaborative research.

I would like to express my appreciation to Professor Takao Onoye in Osaka University, Professor Yoshinori Takeuchi in Kindai University, Associate Professor Yuichi Itoh, and Assistant Professor Masahide Hatanaka in Osaka University for their advice and supports.

I would like to thank Assistant Professor Yutaka Masuda in Nagoya University, Assistant Professor Wang Liao in Kochi University of Technology, Dr. Koichi Mitsunari, Mr. Jun Chen, and Mr. Ryo Shirai for daily discussions and their supports. My sincere appreciation goes to Ms. Asako Murakami and Ms. Yuki Yoshida for their various supports throughout my student life. I also would like to thank all members of Integrated System Design Laboratory and Information Systems Synthesis Laboratory in Osaka University for having interesting and

good time in the laboratory.

My heartfelt thanks go to my family for supporting my life and giving a delightful and relaxing time.

This work was supported by JSPS KAKENHI Grant Number JP17J10008 and JST CREST Grant Number JPMJCR1432, Japan.

## **Contents**

| 1 | Intr | oductio                                                | o <b>n</b>                                              | 1                                |

|---|------|--------------------------------------------------------|---------------------------------------------------------|----------------------------------|

|   | 1.1  | Backg                                                  | ground                                                  | 1                                |

|   | 1.2  |                                                        | entional FPGA and Drawbacks                             | 3                                |

|   |      | 1.2.1                                                  | SRAM-Based FPGA                                         | 3                                |

|   |      | 1.2.2                                                  | Drawbacks of SRAM-Based FPGA                            | 4                                |

|   | 1.3  | Emerg                                                  | ging FPGAs with Non-volatile Memories                   | 6                                |

|   |      | 1.3.1                                                  | Programmability and Energy Efficiency Trade-off in Con- |                                  |

|   |      |                                                        | ventional Hardware                                      | 7                                |

|   |      | 1.3.2                                                  | Traditional Non-volatile FPGAs                          | 8                                |

|   |      | 1.3.3                                                  | Emerging Non-volatile Memories                          | 9                                |

|   |      | 1.3.4                                                  | Emerging NVM-Based FPGAs                                | 12                               |

|   | 1.4  | Via-S                                                  | witch FPGA and Issues                                   | 13                               |

|   |      | 1.4.1                                                  | Via-Switch                                              | 13                               |

|   |      | 1.4.2                                                  | Via-Switch FPGA                                         | 16                               |

|   |      | 1.4.3                                                  | Issues of Via-Switch FPGA                               | 17                               |

|   | 1.5  | Object                                                 | tives of This Dissertation                              | 20                               |

| 2 | Inte | rconne                                                 | ct Structure Design and Evaluation in Via-Switch FPGA   | 25                               |

|   | 2.1  | Introd                                                 | uction                                                  | 25                               |

|   |      | muou                                                   | uction                                                  | 25                               |

|   | 2.2  |                                                        | onnect Structures of Via-Switch FPGA                    | 25<br>26                         |

|   | 2.2  |                                                        |                                                         |                                  |

|   | 2.2  | Interco                                                | onnect Structures of Via-Switch FPGA                    | 26                               |

|   | 2.2  | Interce 2.2.1                                          | onnect Structures of Via-Switch FPGA                    | 26<br>26                         |

|   | 2.2  | Interce 2.2.1 2.2.2                                    | Onnect Structures of Via-Switch FPGA                    | 26<br>26                         |

|   | 2.2  | Interce 2.2.1 2.2.2                                    | Onnect Structures of Via-Switch FPGA                    | 26<br>26<br>27                   |

|   | 2.2  | Interce 2.2.1 2.2.2 2.2.3 2.2.4                        | Proposed Interconnect Structure                         | 26<br>26<br>27<br>28             |

|   |      | Interce 2.2.1 2.2.2 2.2.3 2.2.4                        | Proposed Interconnect Structure                         | 26<br>26<br>27<br>28<br>31       |

|   |      | Interce<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Interce | Proposed Interconnect Structure                         | 26<br>26<br>27<br>28<br>31       |

|   |      | Interce<br>2.2.1<br>2.2.2<br>2.2.3<br>2.2.4<br>Interce | Proposed Interconnect Structure                         | 26<br>26<br>27<br>28<br>31<br>32 |

|   |      | Interce 2.2.1 2.2.2 2.2.3 2.2.4 Interce 2.3.1          | Proposed Interconnect Structure                         | 26<br>26<br>27<br>28<br>31<br>32 |

xii CONTENTS

| 3 | Faul | lt Diagnosis of Via-Switch Crossbar                           | 41 |

|---|------|---------------------------------------------------------------|----|

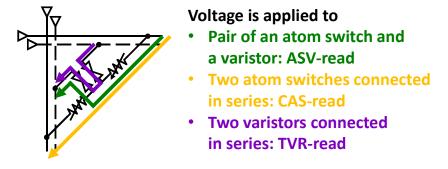

|   | 3.1  | Fault Mode Analysis of Via-Switch                             | 41 |

|   |      | 3.1.1 Discriminating Via-Switch On/Off-States with Comparator | 42 |

|   |      | 3.1.2 Via-Switch Fault Modes                                  | 45 |

|   | 3.2  | Proposed Fault Diagnosis Method                               | 47 |

|   |      | 3.2.1 Prerequisites                                           | 47 |

|   |      | 3.2.2 Fault Diagnosis                                         | 47 |

|   | 3.3  | Discussion                                                    | 51 |

|   | 3.4  | Conclusion                                                    | 53 |

| 4 | Snea | ak Path Free Initial Programming in Via-Switch FPGA           | 55 |

|   | 4.1  | Introduction                                                  | 55 |

|   | 4.2  | Occurrence Conditions of Sneak Path Problem                   | 57 |

|   | 4.3  | Proposed Sneak Path Free Initial Programming                  | 59 |

|   |      | 4.3.1 Overview of Proposed Method                             | 60 |

|   |      | 4.3.2 Programming Order Determination with Connection Tree    | 61 |

|   | 4.4  | Proof of Existence of Sneak Path Free Programming Order       | 66 |

|   | 4.5  | Pseudo Code and Execution Example                             | 68 |

|   | 4.6  | Evaluation Results                                            | 70 |

|   | 4.7  | Conclusion                                                    | 72 |

| 5 | Min  | imization of Programming Steps in Partial Reconfiguration of  |    |

|   | Via- | Switch FPGA                                                   | 73 |

|   | 5.1  | Proposed Partial Reprogramming Method                         | 73 |

|   |      | 5.1.1 Partial Erasing                                         | 74 |

|   |      | 5.1.2 Partial Writing                                         | 76 |

|   | 5.2  | Proof of Sneak Path Avoidance in Partial Reconfiguration      | 78 |

|   | 5.3  | Proposed Minimization Method of Programming Steps             | 80 |

|   |      | 5.3.1 Minimizing Number of Switches Programed in Partial      |    |

|   |      | Reconfiguration                                               | 80 |

|   |      | 5.3.2 Root Node Selection with Lower Computational Com-       |    |

|   |      | plexity                                                       | 84 |

|   | 5.4  | Pseudo Code of Partial Reprogramming                          | 85 |

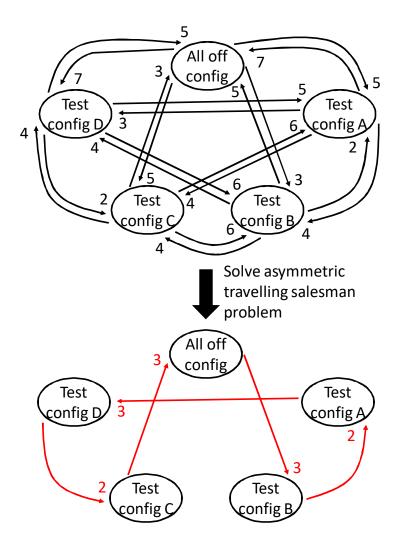

|   | 5.5  | Evaluation Results                                            | 86 |

|   | 5.6  | Discussion                                                    | 89 |

|   | 5.7  | Conclusion                                                    | 91 |

| 6 | Con  | clusion                                                       | 95 |

| A | Ano  | ther proof for Equation (5.6)                                 | 99 |

# **List of Figures**

| 1.1  | Isrand-style FPGA structure                                                                                                                                                                     | 4  |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.2  | SRAM-based logic block structure                                                                                                                                                                | 5  |

| 1.3  | SRAM-based connection block structure                                                                                                                                                           | 6  |

| 1.4  | SRAM-based switch block structure                                                                                                                                                               | 6  |

| 1.5  | Trade-off between programmability and energy efficiency of conventional computing devices, and goal of next-generation FPGAs                                                                    | 7  |

| 1.6  | with non-volatile memories.                                                                                                                                                                     | 7  |

| 1.6  | Structure and operation of STT-MRAM cell                                                                                                                                                        | 11 |

| 1.7  | Structure and operation of PCRAM cell                                                                                                                                                           | 11 |

| 1.8  | Structure and operation of RRAM cell                                                                                                                                                            | 12 |

| 1.9  | Structure and operation of atom switch                                                                                                                                                          | 14 |

| 1.10 | CAS structure                                                                                                                                                                                   | 15 |

| 1.11 | Via-switch structure                                                                                                                                                                            | 16 |

| 1.12 | Concept of via-switch FPGA                                                                                                                                                                      | 17 |

| 1.13 | Structure of via-switch FPGA                                                                                                                                                                    | 18 |

| 1.14 | Via-switch based crossbar structure and switch programming steps.                                                                                                                               | 19 |

| 1.15 | Sneak path problem in via-switch crossbar programming                                                                                                                                           | 20 |

| 1.16 | Contributions and organization of this dissertation                                                                                                                                             | 23 |

| 2.1  | Proposed interconnect structure of via-switch FPGA                                                                                                                                              | 27 |

| 2.2  | Sneak path problem in connection switch between CLBs                                                                                                                                            | 28 |

| 2.3  | Crossbar expansion supposed in induction-based proof                                                                                                                                            | 30 |

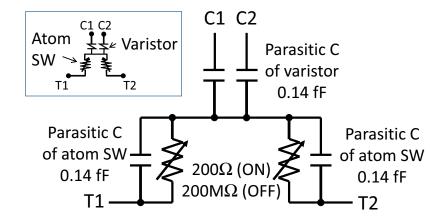

| 2.4  | An equivalent circuit model of via-switch in normal operation                                                                                                                                   | 33 |

| 2.5  | Signal transmission path in performance evaluation                                                                                                                                              | 33 |

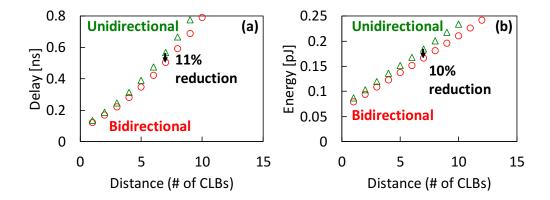

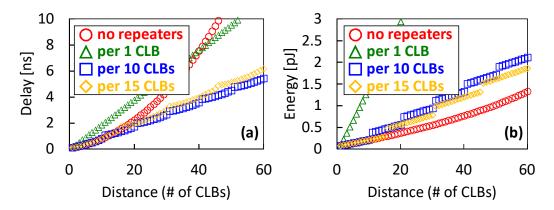

| 2.6  | (a) interconnect delay and (b) energy per signal transmission in the proposed interconnect structure. Two crossbar sizes of 86x153 and 96x163 are evaluated. Repeaters are not inserted. Supply |    |

|      | voltage is 1.0 V                                                                                                                                                                                | 34 |

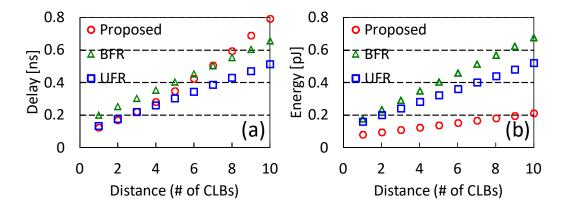

| 2.7  | (a) interconnect delay and (b) energy per signal transmission in the proposed, BFR, and UFR structures. The proposed and BFR structures are 86x153 crossbar and UFR structure is 96x163 crossbar. Supply voltage is 1.0 V | 34 |

|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

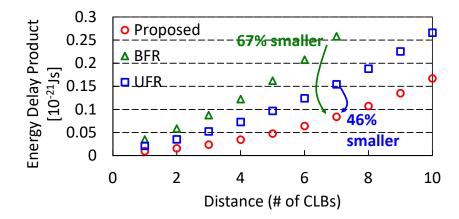

| 2.8  | Energy-delay product per signal transmission in the proposed, BFR, and UFR structures. The proposed and BFR structures are 86x153 crossbar and UFR structure is 96x163 crossbar. Supply voltage is 1.0 V                  | 35 |

| 2.9  | (a) interconnect delay and (b) energy per signal transmission in the proposed interconnect structure. Crossbar size is 86x153. Supply voltage is 1.0 V                                                                    | 35 |

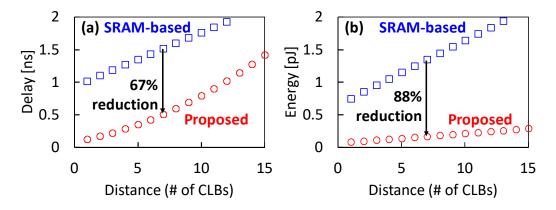

| 2.10 | Comparison between the proposed and SRAM-based architectures. Repeaters are not inserted. Crossbar size is 86x153. Supply voltage is 1.0 V                                                                                | 37 |

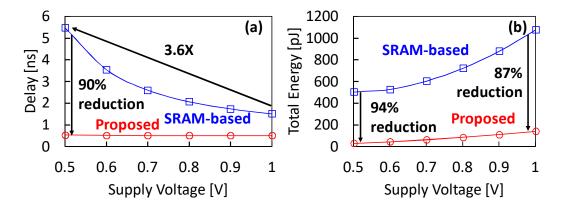

| 2.11 | (a) Interconnect delay and (b) total energy in the proposed and SRAM-based architectures when supply voltage is varied. Repeaters are not inserted. Crossbar size is 86x153                                               | 37 |

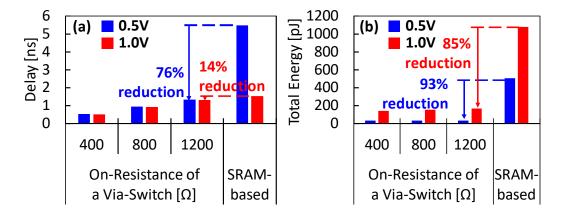

| 2.12 | (a) Interconnect delay and (b) total energy in the proposed and SRAM-based architectures when the ON-resistance of via-switch is varied. Repeaters are not inserted. Crossbar size is 86x153                              | 38 |

| 2.13 | Crossbar area variation in terms of switch removal                                                                                                                                                                        | 39 |

| 2.14 | (a) Interconnect delay and (b) energy in the proposed and SRAM-based architectures when the thinning ratio of intersection switches is varied. Repeaters are not inserted. Crossbar size is 86x153                        | 39 |

|      |                                                                                                                                                                                                                           |    |

| 3.1  | Connection between comparator, programming drivers, and crossbar array.                                                                                                                                                   | 43 |

| 3.2  | Boundary reference voltage of comparator when via-switch on-<br>resistance is varied                                                                                                                                      | 45 |

| 3.3  | Path to apply read voltage in ASV-, CAS-, and TVR-read                                                                                                                                                                    | 45 |

| 3.4  | Percentage of faulty via-switches in 100x100 crossbar when fault                                                                                                                                                          |    |

|      | rate of each component in a via-switch varies                                                                                                                                                                             | 52 |

| 3.5  | Percentage of diagnosable via-switches in 100x100 crossbar when the fault rate of each component in a via-switch and the supposed maximum number of faulty components are varied                                          | 52 |

|      |                                                                                                                                                                                                                           | 32 |

| 4.1  | Routing patterns that are prohibited in conventional countermeasure. These patterns are often used in practical applications                                                                                              | 57 |

| 4.2  | Two occurrence conditions of sneak path problem                                                                                                                                                                           | 58 |

| 4.3             | Example of non-looped configuration and definition of connector/non-connector switches                                | 52       |  |  |  |

|-----------------|-----------------------------------------------------------------------------------------------------------------------|----------|--|--|--|

| 4.4             | ,                                                                                                                     |          |  |  |  |

|                 | Example of connection tree for connector switches in Figure 4.3. 63                                                   |          |  |  |  |

| 4.5             | Programming of connector switch in leaf/non-leaf node at the last                                                     | - 1      |  |  |  |

| 4.6             | Recursively searching switch which can be programmed lastly for                                                       | 54<br>56 |  |  |  |

| 4.7             |                                                                                                                       | JU       |  |  |  |

| 4.7             | Number of available configurations with conventional counter-                                                         | 7 1      |  |  |  |

|                 | measure and proposed method in small crossbars                                                                        | 71       |  |  |  |

| 5.1             | Concept of partial reprogramming                                                                                      | 74       |  |  |  |

| 5.2             |                                                                                                                       | 76       |  |  |  |

| 5.3             |                                                                                                                       | 78       |  |  |  |

| 5.4             | Changes in the structure of connection tree and the number of                                                         | O        |  |  |  |

| J. <del>4</del> |                                                                                                                       | 32       |  |  |  |

| 5.5             |                                                                                                                       | 32<br>33 |  |  |  |

| 5.6             | Number of programmed switches in reconfiguration with con-                                                            | 53       |  |  |  |

|                 | ventional and proposed methods when 0.5% of via-switches are                                                          |          |  |  |  |

|                 |                                                                                                                       | 37       |  |  |  |

| 5.7             | Number of programmed switches in reconfiguration with conventional and proposed methods when 1.5% of via-switches are |          |  |  |  |

|                 | on-state in 100x100 crossbar                                                                                          | 38       |  |  |  |

| 5.8             | Histogram of reduction ratio in number of programmed switches                                                         |          |  |  |  |

|                 |                                                                                                                       | 39       |  |  |  |

| 5.9             | <u> •</u>                                                                                                             | 90       |  |  |  |

| 5.10            |                                                                                                                       | 91       |  |  |  |

| 5.11            | Complete directed graph that represents entire BIST sequence                                                          |          |  |  |  |

|                 | and optimal test order derivation by solving asymmetric travelling salesman problem                                   | 92       |  |  |  |

| A.1             | All combinations of two representative switches                                                                       | )()      |  |  |  |

## **List of Tables**

| 1.1 | tions                                                                                                      | 2  |

|-----|------------------------------------------------------------------------------------------------------------|----|

| 1.2 | Comparison of SRAM-based FPGA and traditional NVM-based                                                    |    |

|     | FPGAs                                                                                                      | 8  |

| 1.3 | Device Characteristic Comparison of SRAM and Emerging NVM Technologies                                     | 10 |

| 2.1 | Comparison of supposed interconnect structures                                                             | 31 |

| 3.1 | Comparator output when reference voltage is varied in read operation of atom switch                        | 44 |

| 3.2 | Boundary reference voltage in ASV-, CAS-, and TVR-read                                                     | 44 |

| 3.3 | Boundary reference voltage in ASV- and CAS-read with faulty varistor                                       | 46 |

| 3.4 | Boundary reference voltage in TVR-read with normal and faulty                                              | 10 |

|     | varistors                                                                                                  | 47 |

| 3.5 | Comparator response difference and diagnosability in case of up                                            |    |

|     | to two faulty components in a via-switch                                                                   | 49 |

| 3.6 | Diagonosable faults ratio                                                                                  | 51 |

| 4.1 | Summary of proposed initial programming method                                                             | 61 |

| 4.2 | Number of usable configurations among 10,000 random configurations in a practically-sized 100x100 crossbar | 71 |

| 5.1 | Summary of proposed partial reconfiguration method                                                         | 75 |

## Chapter 1

## Introduction

This dissertation addresses design, test, and programming issues of non-volatile via-switch FPGA that is an emerging FPGA with high energy efficiency. First, this chapter explains the background and objectives of this dissertation. Section 1.1 describes the research background. Then, Section 1.2 briefly explains the conventional FPGA and its drawbacks. As a solution to overcome conventional FPGA drawbacks, emerging non-volatile memory-based FPGAs are introduced in Section 1.3. After that, Section 1.4 explains via-switch FPGA that is mainly focused on in this dissertation, and also discusses issues to be solved. Finally, Section 1.5 states the research objectives of this dissertation.

## 1.1 Background

In 1965, Gordon Moore found that the number of transistors in an integrated circuit chip doubles every 18 months. This observation is called Moore's Law and has become a self-fulfilling prophecy [1]. Moore's Law has been maintained for recent decades by the effort of manufacturers. For example, the transistor count in Intel microprocessors has doubled every 26 months since the development of the 4004 microprocessor that had only 2,300 transistors in 1971 [2]. On the other hand, in 2019, Apple A13 Bionic microprocessor that contains 8.5 billion transistors was launched [3]. The continuation of Moore's Law over such a long term is mainly thanks to the scaling down of transistor size. The 4004 microprocessor was fabricated at a process node of 10  $\mu$ m, while the Apple A13 Bionic used a process node of 7 nm. Manufacturers adopt a new process node every a few years with a 30% smaller transistor size to pack twice as many transistors in the same area [1,4].

The successive scaling down of process node is beneficial to transistor performance, i.e., shrinking the transistor size brings faster operating speed and

|                           | ASICs     | FPGAs                    |

|---------------------------|-----------|--------------------------|

| Programmability           | No        | Yes                      |

| Layout/Mask/Manufacturing | Necessary | Unnecessary              |

| NRE Cost                  | Very High | Low                      |

| Time to Market            | Long      | Short                    |

| Design Change             | Difficult | Easy                     |

| Design Flow               | Comlex    | Simple                   |

| Performance               | High      | Medium (Higher than CPU) |

Table 1.1: Comparison between ASICs and FPGAs for system implementations.

lower power consumption. On the other hand, especially in application-specific integrated circuits (ASICs), the development cost is increasing exponentially as the transistor size scales down [5]. This is because non-recurring engineering (NRE) costs, which include costs of mask-sets and engineering design efforts of layout and verification, are very expensive in smaller process nodes. For example, in 14 nm process, the total development cost of an ASIC reaches 270 million dollars [6]. Such expensive development costs of ASICs are unacceptable in many fields except for some fields that will sell in huge quantities or that have cutting-edge performance requirements, e.g., smartphone market, gaming hardware market, etc. In addition to high development costs, the long time to market due to complicated design and verification processes is another concern of ASIC implementations. It also takes a long time and high cost for design modifications or bug fixes.

In recent years, field-programmable gate arrays (FPGAs) are becoming popular since ASIC development cost is elevating and development time becomes longer due to process node scaling. Table 1.1 summarizes the advantages and disadvantages of ASICs and FPGAs for system implementations. FPGAs are computing devices that can reprogram the circuit functionality after manufacturing. We utilize a hardware description language (HDL) such as Verilog HDL and VHDL, which are similar to programming languages, to design the circuit with already manufactured FPGA, and hence layout, mask, manufacturing steps are unnecessary in FPGA implementations. Eliminating these steps significantly reduces NRE costs and shortens the development time. When we need to modify the circuit design or fix design errors, the modification can be achieved by just changing the description of HDL and reprogramming the FPGA. The design flow of FPGA implementations is also simpler than that of ASIC implementations.

Thanks to the above advantages, FPGAs are widely adopted not only for prototyping but also practical use in various fields despite lower performance compared to ASICs. For example, Microsoft, Amazon Web Services, and IBM introduced FPGAs to their data centers of cloud computing services [7–10]. FPGAs often offer much higher performance than central processing units (CPUs), and this higher performance contributes to both speed up and energy reduction of the system. Besides, field-programmability, low NRE cost, and a short time to market of FPGAs are suitable for edge computing devices in the Internet of Things (IoT) era. Even in the fields of large variety and small quantity production, the adoption of FPGAs can improve profitability. Furthermore, hardware acceleration with FPGAs is drawing attention especially for artificial intelligence (AI) in recent years. For instance, Intel, Xilinx, and Microsoft corporations accelerate deep neural network (DNN) inference by using FPGAs [11–13]. In this way, FPGAs have a wide range of applications, and the FPGA market is expected to expand further in the future.

#### 1.2 Conventional FPGA and Drawbacks

Section 1.2.1 briefly reviews the structure and operating principle of conventional FPGAs. Then, Section 1.2.2 takes a look at the drawbacks of conventional FPGAs.

#### 1.2.1 SRAM-Based FPGA

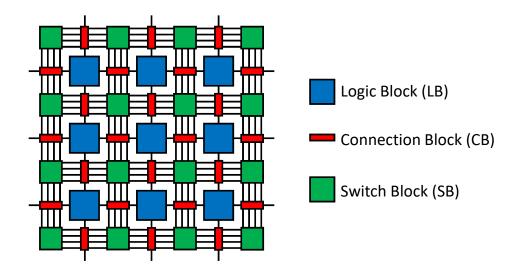

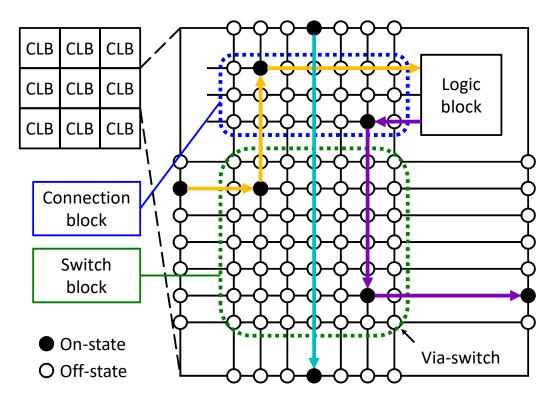

Static random access memory (SRAM)-based FPGAs are the most popular FPGAs in many fields. These FPGAs typically have an island-style structure illustrated in Figure 1.1. The island-style structure consists of programmable logic elements and interconnects arranged in an array, where programmable logic elements are called logic blocks (LBs) and programmable interconnect wires are called connection blocks (CBs) and switch blocks (SBs). We can implement any circuit functionality by constructing arbitrary combinational or sequential circuits in LBs and routing arbitrary signal paths between LBs in CBs and SBs [14–16].

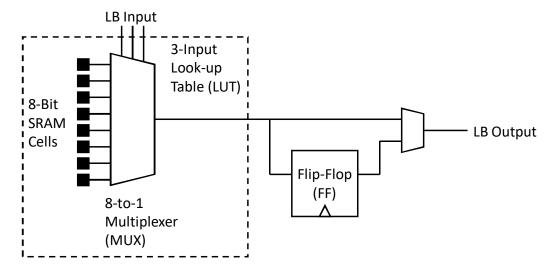

Figure 1.2 shows the most basic structure of an LB. A k-input look-up table (LUT) circuit has  $2^k$ -bit SRAM cells and a  $2^k$ -to-1 multiplexer (MUX) with k select terminals. To construct arbitrary combinational logic, we store a truth table of the desired function in k-input and 1-output, and give the input signals of LB to the select terminals of MUX. Thanks to the  $2^k$ -bit SRAM cells, we can define the output values for all the combinations of k input signals. The LB also contains flip-flops (FFs) to implement a sequential circuit.

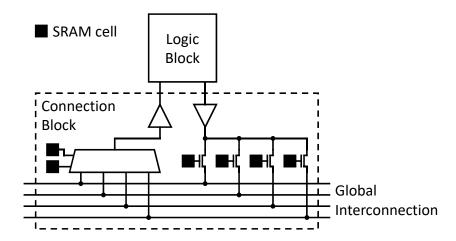

CB and SB have the structures depicted in Figure 1.3 and 1.4, respectively. CB is responsible for inputting to and outputting from the LB. MUX or pass transistors are used for controlling the connection between the LB and global interconnections. Here, the global interconnections are wiring resources that are

Figure 1.1: Isrand-style FPGA structure.

aligned outside LBs, while the local interconnections are arranged inside LBs. An SRAM cell is connected to the select terminal of MUX or gate terminal of the pass transistor. On the other hand, SB connects or disconnects the vertical interconnection and horizontal interconnection by pass transistors with SRAM cells. In both CB and SB, we program stored values in SRAM cells to construct the desired connection between LBs.

#### 1.2.2 Drawbacks of SRAM-Based FPGA

Conventional SRAM-based FPGAs are inferior to ASICs regarding operating speed, power consumption, and implementation area [17]. For example, when we implement the same circuit function, Kuon et al. report that FPGA implementation has four times slower operating speed, fourteen times more dynamic power, 87 times more static power, and 35 times larger circuit area than ASIC implementation [18]. These drawbacks originate from a tremendous amount of programmable switches that are equipped in SRAM-based FPGAs to acquire reconfigurability as mentioned in the previous subsection. Lin et al. say that 80% of the circuit delay comes from programmable interconnections with SRAM-based switches [19].

Typical SRAM-based programmable switch is composed of a switch gate, such as transmission gate or MUX, and an SRAM cell to hold the on/off states of switch gate. The switch gate consists of transistors, and hence it has high resistance and large capacitance, which degrade the circuit speed and increase power dissipation. The SRAM cell using six transistors consumes a large area. This increases not only circuit area but also wiring length, and the consequent

Figure 1.2: SRAM-based logic block structure.

long wire imposes a bad impact on the speed and power. Besides, the volatility of SRAM cells is also a concern. We need to keep supplying power to SRAM cells even during standby, and the leakage current in a large amount of SRAM cells causes enormous static power consumption. Furthermore, conventional FPGA structure where programming resources and logic circuits share the same layer, i.e., the transistor layer, is also undesirable. This is because SRAM cells dominate the FPGA chip area due to the large area and amount of them, and consequently logic circuits can only use a small area. This makes it difficult to put computing units that have high computing performance, e.g., arithmetic unit and multiply-accumulator, on the chip. Ref. [19] reports that programmable routing resources including SRAM-based switches occupy 78% of the chip area, whereas computing logic circuits account for only 14%.

From the above reasons, SRAM-based programmable switches lead to the degradation of interconnect performance and area efficiency of the FPGA. Therefore, miniaturizing the programmable switch, which is the performance bottleneck of conventional FPGAs, directly contributes to an area reduction of the entire FPGA. According to the area reduction, wiring length becomes shorter, and it reduces signal transmission delay and power consumption. Also, exploiting low resistance and small capacitance of programmable switches contributes to boosting the FPGA performance. In recent years, various FPGAs using non-volatile memories (NVM) are widely developed to overcome the drawbacks of conventional SRAM-based FPGAs. The details of such FPGAs are discussed in the following sections.

Figure 1.3: SRAM-based connection block structure.

Figure 1.4: SRAM-based switch block structure.

## 1.3 Emerging FPGAs with Non-volatile Memories

This section firstly compares conventional computing hardware in terms of programmability and energy efficiency. Then, Section 1.3.1 introduces non-volatile memory (NVM)-based FPGAs that are developed for improving the energy efficiency of conventional FPGAs. There are traditional NVM-based FPGAs and emerging NVM-based FPGAs. Section 1.3.2 discusses the advantages and disadvantages of traditional NVM-based FPGAs. Emerging NVM technologies are actively developed in recent years, and they are becoming the most promising candidates to replace SRAM memories in conventional FPGAs. Section 1.3.3 explains three emerging NVM technologies, their structure and operating principle, followed by the reviews of related works of emerging NVM-based FPGAs in Section 1.3.4.

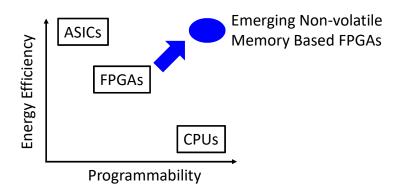

Figure 1.5: Trade-off between programmability and energy efficiency of conventional computing devices, and goal of next-generation FPGAs with non-volatile memories.

# 1.3.1 Programmability and Energy Efficiency Trade-off in Conventional Hardware

Conventional computing hardware has a trade-off relation between programmability and energy efficiency as shown in Figure 1.5. The programmability of CPUs is the highest since we can easily program them with high-level programming languages such as Python, C++, and so on. However, CPUs suffer from Von Neumann bottleneck due to their slow access speed between the processor and memory, and hence their energy efficiency becomes quite low [20, 21]. On the other hand, ASICs are designed to achieve the highest performance for a specific function, and therefore the energy efficiency is very high. Instead of this, ASICs cannot be programmed after manufacturing except the programs of embedded processors and hardly cope with design changes or bug fixes. Conventional FPGAs stand between CPUs and ASICs. FPGAs can be programmed like software by HDL, which is slightly difficult to use compared to high-level software programming languages. They often offer much better performance than CPUs since arbitrary circuit functionality can be implemented as dedicated hardware with parallelization.

In recent years, many researchers have studied how to boost up the programmability and performance of FPGAs. In terms of programmability, we have to describe cycle-by-cycle circuit behavior at a low level of abstraction with HDL, and this requires advanced hardware expertise. To improve the programmability, high-level synthesis techniques are well developed [22–27]. These techniques automatically generate an HDL description from a given algorithm written by high-level language, e.g., C and Java. The synthesis process can be optimized taking into account the performance, power, and area. Thanks to high-level synthesis, designers without hardware expertise can easily utilize FPGAs, and

| O/As.                 |            |             |                |

|-----------------------|------------|-------------|----------------|

|                       | SRAM-Based | Flash-Based | Antifuse-Based |

| Non-volatility        | No         | Yes         | Yes            |

| Switch Area           | Large      | Medium      | Small          |

| On-Resistance         | High       | High        | Low            |

| Capacitance           | Large      | Large       | Small          |

| Reconfigurability     | Yes        | Yes         | No             |

| Manufacturing Process | Simple     | Complex     | Simple         |

Table 1.2: Comparison of SRAM-based FPGA and traditional NVM-based FPGAs.

we can also shorten the development time.

For improving the energy efficiency of FPGAs, on the other hand, various FPGAs that exploit other programmable switches instead of SRAM-based one are studied. As described in the previous section, SRAM-based programmable switches are performance bottleneck in conventional FPGAs. Requirements of desirable programmable switches are as follows.

- Small circuit area.

- Low on-resistance and high off-resistance.

- Small parasitic capacitance.

- Simple manufacturing process and high yield rate.

- Non-volatility.

According to the above requirements, many FPGA architectures using non-volatile memories (NVMs) are widely developed. There are traditional NVM-based FPGAs and emerging NVM-based FPGAs. The following subsections explain the characteristics of each FPGA.

#### 1.3.2 Traditional Non-volatile FPGAs

There are two types of traditional non-volatile FPGAs, namely, flash memory-based FPGA [28–32] and antifuse FPGA [33–37]. Table 1.2 summarizes the characteristics of these traditional NVM-based FPGAs with the SRAM-based one.

Flash-based FPGAs replace SRAM cells by flash memories. The flash memory is a kind of floating-gate metal-oxide-semiconductor field-effect transistors (MOSFETs), and we program it by injecting an electrical charge to the floating-gate. Compared to SRAM-based switches, the area per switch can be reduced, but flash-based switches still have high on-resistance and large parasitic

capacitance. Besides, combining flash and complementary MOS (CMOS) technologies requires a complicated and costly manufacturing process.

When we program antifuse FPGAs, we apply a high voltage to the antifuse switch. Initially, the antifuse switch is insulated. The applied high voltage makes a small hole in the insulation layer, and the switch turns on. Antifuse switch has advantages of a small area, low on-resistance, and small capacitance. However, once a hole is formed in the insulation layer, we cannot fill up the hole. Therefore, an antifuse FPGA allows only one-time programming, and there is no reconfigurability after programming once.

#### 1.3.3 Emerging Non-volatile Memories

The previous subsection explains that traditional NVM-based FPGAs have many disadvantages despite their non-volatility. Recently, novel FPGA architectures using emerging non-volatile memories are widely proposed for boosting energy efficiency compared to conventional FPGAs [38, 39]. Firstly, this subsection summarizes the structure and operation of emerging NVM technologies, and then reviews emerging NVM-based FPGAs in the next subsection.

Emerging NVMs are two-terminal devices, and we change their resistance by imposing an electrical stimulus, i.e., voltage or current pulse. A high resistance state (HRS) is regarded as off-state and a low resistance state (LRS) corresponds to on-state. The switching between off-state and on-state is repeatable. NVMs have a non-volatility, namely, each on/off-state is maintained after power off. Emerging NVMs can be categorized into three types according to switching physics: spin-transfer-torque magnetic random access memory (STT-MRAM), phase-change random access memory (PCRAM), and resistive random access memory (RRAM) [40–42].

Table 1.3 compares the device characteristics of SRAM and emerging NVM technologies [41]. Thanks to very high cell density and low leakage power of emerging NVMs, replacing SRAM cells or whole SRAM-based switches including switch gate with these NVMs can improve the area efficiency and energy efficiency of FPGA. Especially, PCRAM and RRAM have a large on-off ratio, which represents the ratio of off-resistance to on-resistance. The large on-off ratio is beneficial to FPGA performance since low resistance in on-state enables high-speed signal transmission and high resistance in off-state cuts off the leakage current. PCRAM and RRAM also have good process compatibility with mainstream CMOS technology. Therefore, these NVM technologies can be easily combined with general CMOS logic circuits at a lower cost. On the other hand, cycling endurance of emerging NVMs, which means the maximum number of on-off switching, is lower than the SRAM cell. Thanks to the above features of emerging NVMs, they are becoming the most promising candidate

| cimologics.               |                       |                      |                      |                    |  |  |  |

|---------------------------|-----------------------|----------------------|----------------------|--------------------|--|--|--|

|                           | SRAM                  | STT-MRAM             | PCRAM                | RRAM               |  |  |  |

| Non-volatility            | No                    | Yes                  | Yes                  | Yes                |  |  |  |

| Cell Area                 | $> 100  \mathrm{F}^2$ | $6-50  \mathrm{F}^2$ | $4-30  \mathrm{F}^2$ | $4-12 \text{ F}^2$ |  |  |  |

| Leakage Power             | High                  | Low                  | Low                  | Low                |  |  |  |

| On-Off Ratio              | N/A                   | < 2X                 | $10^2 - 10^3 X$      | $10^{1}-10^{6}$ X  |  |  |  |

| <b>CMOS Compatibility</b> | Yes                   | Poor                 | Yes                  | Yes                |  |  |  |

| Cycling Endurance         | $> 10^{16}$           | $> 10^{15}$          | $10^6 - 10^9$        | $10^4 - 10^{12}$   |  |  |  |

Table 1.3: Device Characteristic Comparison of SRAM and Emerging NVM Technologies.

F: minimum feature size.

to replace SRAM-based programmable switches in conventional FPGAs. The following paragraphs explain the structure and operating mechanism of each emerging NVM.

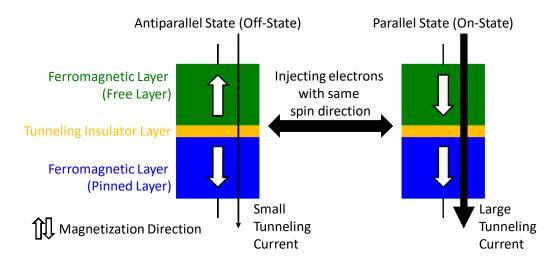

The STT-MRAM cell is based on a magnetic tunnel junction (MTJ) structure [43-49]. MTJ structure consists of two ferromagnetic layers separated by a thin tunneling insulator layer, and one ferromagnetic layer is called a free layer and the other is a pinned layer as shown in Figure 1.6. We can change the magnetization direction in the free layer by injecting a large amount of electrons with the same spin direction, while the magnetization direction in the pinned layer is fixed. When both free and pinned layers have the same magnetization direction, which is called a parallel state, the resistance of STT-MRAM is low and a large tunneling current flows in the cell. On the other hand, in an antiparallel state where magnetization directions of free and pinned layers are opposite, the resistance becomes high and the current becomes small. This resistance change phenomenon that depends on the magnetization direction is known as tunneling magnetoresistance (TMR) effect. The on-off ratio of STT-MRAM is typically small, specifically less than 2X. The fabrication of STT-MRAM becomes complicated and has relatively poor compatibility to CMOS process technology since ten or more layers of ferromagnetic materials are stacked in MTJ structure.

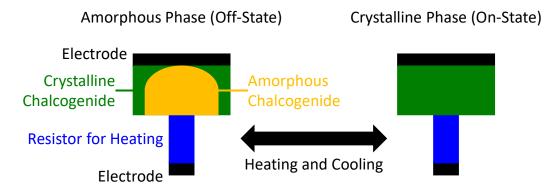

The PCRAM cell is composed of chalcogenide materials that have two phases of the amorphous phase and crystalline phase as illustrated in Figure 1.7 [50–55]. The amorphous phase corresponds to off-state and has high resistance, whereas the crystalline phase which has low resistance corresponds to on-state. When we turn on a PCRAM cell, we heat the cell at a relatively low temperature and then cool down slowly. In the turning off operation, on the other hand, we use a high temperature for heating and then rapidly cool the cell. The on-off resistance ratio of PCRAM is much larger in the range from 100X to 1,000X. Due to the slow cooling down process in the turning on operation, switching speed of PCRAM cell

Figure 1.6: Structure and operation of STT-MRAM cell.

Figure 1.7: Structure and operation of PCRAM cell.

is limited, specifically slower than 50 ns which is ten times longer than RRAM cell. PCRAM has a long endurance of  $10^6$ – $10^9$  cycles. In general, PCRAM has good process compatibility with CMOS technology.

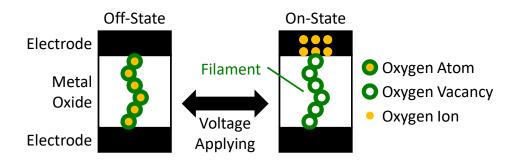

The RRAM cell consists of metal oxide or solid electrolyte sandwiched between two electrodes, where metal oxide-based RRAM and solid electrolyte-based RRAM are called oxide random access memory (OxRAM) [56–60] and conductive bridge random access memory (CBRAM) [61–65], respectively. In an RRAM cell, low resistance conductive filaments are formed (on-state) and ruptured (off-state) between two electrodes by applying a voltage as depicted in Figure 1.8. Here, this figure shows an OxRAM cell and its filaments consist of oxygen vacancies, while filaments of CBRAM consist of metal atoms. OxRAM has a small on-off resistance ratio of 10–100X and better cycling endurance up to  $10^{12}$  cycles. On the other hand, the on-off ratio of CBRAM is very large in the

Figure 1.8: Structure and operation of RRAM cell.

range from  $10^3$ X to  $10^6$ X and endurance is limited to  $10^4$  cycles. RRAMs have excellent process compatibility with CMOS technology.

#### 1.3.4 Emerging NVM-Based FPGAs

In recent years, FPGA architectures that utilize emerging NVMs are widely studied. There are three categories of emerging NVM-based FPGAs. The first category is FPGAs based on non-volatile SRAM (NV-SRAM) cells and non-volatile logic (NV-logic) circuits [66, 67]. The second category replaces SRAM cells with NVM cells [68, 69], while the third category exploits NVMs instead of whole SRAM-based switches including not only SRAM cells but also transistor switches whose gates are connected to the SRAM cells [39, 70]. The following paragraphs review FPGAs in each category and their contributions.

The first category adds NVMs to SRAMs and flip-flops for building the NV-SRAMs and NV-logic cells. The NVMs record the cell states before power off and restore after power on. The goal of this category is to completely cut off leakage power at standby and be immediately ready for computing on demand. Xue et al. proposed a low-power variation-tolerant non-volatile LUT, and demonstrated 38% reduction in power and 22% reduction in delay [66]. Huang et al. presented a low active leakage and high reliability PCRAM-based NV-SRAM [67]. The proposed NV-SRAM based LUT achieves 174 times reduction in active leakage power compared to the state-of-the-art. However, NV-SRAM and NV-logic based FPGAs remain having SRAM-based switches, which are the performance bottleneck in conventional FPGAs, and consequently the improvement on processing speed and area efficiency is limited.

In the second category, SRAM cells that control switch gates are replaced by NVM cells. Typically, NVM-based memory cell consists of two NVM cells in series where one end is connected to power rail and the other is connected to the ground rail. By letting only one NVM cell on-state, i.e., the other is off-state, a value of 0 or 1 can be read from the signal line between two NVM

cells. Thanks to the elimination of SRAM cells, FPGAs in the second category reduce the area and energy consumption. Ju et al. proposed an STT-MRAM memory block based FPGA that reduced the critical path delay by 8.55% and the power by 54.34% [68]. Yuan et al. proposed an overall FPGA architecture with RRAM-based memory cells, and stated that they reduced the energy consumption by 39.5% compared with the state-of-the-art techniques [69]. However, these FPGAs still use transistor switches with high resistance in signal paths, which increases the signal delay.

The third category replaces both a transistor switch and its corresponding SRAM cell with an NVM cell since NVMs naturally have both switching and memory functionalities. Thanks to low resistance NVMs being placed in signal paths instead of high resistance transistor switch, the critical path delays can be reduced. Gaillardon et al. proposed NVM-based SB and LUT structures, and demonstrated an area and delay reduction of up to 28% and 34% compared to conventional FPGA [39]. They also claimed that PCRAM leads to the lowest leakage power, whereas RRAM gives the best area and delay improvements. Khaleghi et al. presented an RRAM-based FPGA architecture including SB, LUT, and also programming circuitry [70]. Their architecture reduces the area and delay by 59.4% and 20.1% compared to SRAM-based FPGA, and also improves the area and power by 49.7% and 33.8% compared to recent RRAM-based architecture. Miyamura et al. fabricated an FPGA based on atom switches [71], where the atom switch is one of the via-switch component and is detailed in the next section. They also demonstrated that their FPGA performed 60% active power saving and three times faster operation compared with a conventional FPGA. However, these NVMs need a few transistors per each cell for programming and those transistors prevent the further improvement of area efficiency.

#### 1.4 Via-Switch FPGA and Issues

This section introduces via-switch FPGA that is mainly focused on in this dissertation. The via-switch FPGA is a novel non-volatile FPGA under active development for the practical application. First, Section 1.4.1 describes via-switch structure and characteristics. Then, Section 1.4.2 explains a fundamental structure and switch programming steps. Finally, Section 1.4.3 discusses challenges to be solved for the practical application of the via-switch FPGA.

#### 1.4.1 Via-Switch

To overcome the drawbacks of conventional SRAM-based FPGAs, various FPGAs that exploit emerging NVMs as programmable switches instead of

Figure 1.9: Structure and operation of atom switch.

SRAM-based ones are widely studied as explained in the previous section. In these emerging NVM-based FPGAs, however, one or two access transistors per a programmable switch are required for switch programming. The access transistor is relatively large despite the small footprint of an NVM-based switch, and hence it prevents further area reduction. To eliminate access transistors, non-volatile via-switch is actively developed [72–74]. The via-switch is a non-volatile, rewritable, and compact switch that is developed to implement a crossbar switch by Banno et al. [72]. This switch consists of atom switches, which are a kind of CBRAMs in RRAMs family, and varistors in place of access transistors. This subsection explains the device structure, functionality, and characteristics of the via-switch.

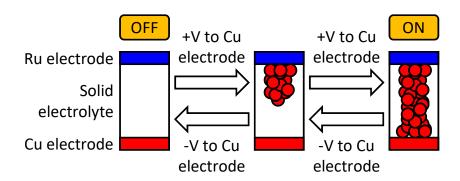

The atom switch consists of a solid electrolyte sandwiched between copper (Cu) and ruthenium (Ru) electrodes as shown in Figure 1.9. By applying a positive voltage to the Cu electrode, a Cu bridge is formed in the solid electrolyte, and the switch turns on. On the other hand, when a negative voltage is applied, Cu atoms in the bridge are reverted to the Cu electrode, and then the switch turns off. The switching between on-state and off-state is repeatable, and each state is non-volatile [75-79]. In an atom switch, both electrodes are connected by Cu metal ions, and therefore the on-resistance becomes low and capacitance becomes small. The on-resistance depends on the programming current through the atom switch when we form the Cu bridge, and it can be down to 200  $\Omega$  that is one order of magnitude lower compared with a MOS transistor switch. Off-resistance of an atom switch is 200 M $\Omega$ . Capacitance per atom switch is 0.14 fF [72, 80]. The atom switch can be reprogrammed about 1,000 times [71]. Furthermore, the atom switch can be integrated in the back-end-of-line (BEoL) layers with a small area, where BEoL layers correspond to wiring layers, while the front-end-of-line (FEoL) layer corresponds to transistor layer [81–84]. Since atom switches do not use transistors, we can fully utilize the FEoL layer to implement the logic, memory, or arithmetic computing unit.

Figure 1.10: CAS structure.

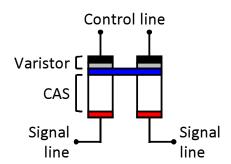

On the other hand, when we use a single atom switch as a programmable switch, a device reliability issue arises. The turning on/off operation applies a relatively high voltage (programming voltage) to the atom switch, whereas we use lower voltage than programming voltage during normal operation. However, even when a lower voltage is applied to the atom switch, a small amount of Cu ions move, and hence it may lead to the transition of on/off states. To prevent the above reliability issue, the complementary atom switch (CAS) is devised, where it consists of two atom switches connected in series with opposite direction as shown in Figure 1.10 [85-89]. By regarding two atom switches as a programmable switch, the voltage applied to each atom switch is divided and it alleviates Cu ions transfer. Besides, when a positive voltage is given to either atom switch, a negative voltage is applied to the other atom switch thanks to the anti-series structure of a CAS, and this improves the device reliability. In the programming of CAS, a pair of the signal line and control line supply a programming voltage to each atom switch, and two atom switches are programmed sequentially. During normal operation, on the other hand, only signal lines are used for routing [71].

To accurately provide the programming voltage only to the target atom switch in a switch array, the varistor, which is a kind of bidirectional diode, is introduced into the via-switch [72–74]. Figure 1.11 shows the structure of via-switch, where the varistor is connected to the control terminal of CAS. When a voltage higher than a threshold value (programming voltage) is applied between the signal and

Figure 1.11: Via-switch structure.

control lines, the varistor supplies programming current to an atom switch. On the other hand, the varistor isolates the control lines from the signal lines during normal operation, and we can regard a via-switch as a two-terminal device with two signal lines. Both CAS and varistor can be implemented in the BEoL layer, and therefore the via-switch is a fully transistor free programmable switch. The minimum footprint per via-switch is 18 F<sup>2</sup> [72, 80].

#### 1.4.2 Via-Switch FPGA

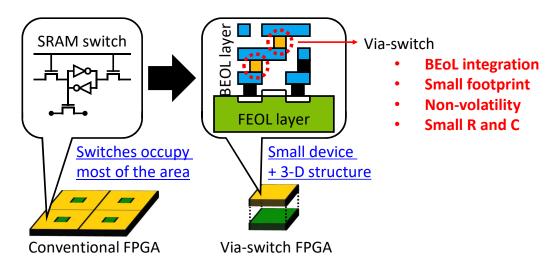

Figure 1.12 illustrates the concept of via-switch FPGA. By using non-volatile via-switches with a small footprint, resistance and capacitance instead of SRAM-based switches, the area and energy efficiency can be expected to improve. Furthermore, the BEoL layer integration of via-switches without transistors enables us to exploit the whole FEoL layer for computing logic. This promotes to implement rich computing units, e.g., arithmetic and logic units (ALUs), multiply-accumulators, accelerators for AI applications, etc. The following paragraphs explain the via-switch FPGA structure and switch programming steps.

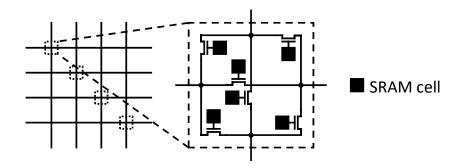

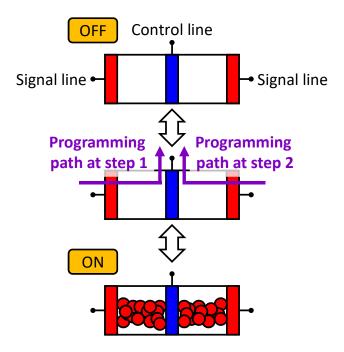

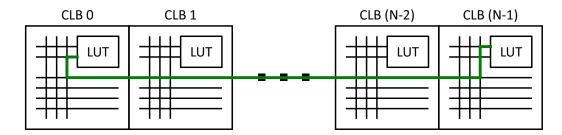

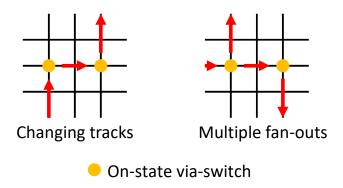

The structure of via-switch FPGA is an array of configurable logic blocks (CLBs), and each CLB is composed of a logic block and a crossbar where a via-switch is placed at each intersection of signal lines as shown in Figure 1.13 [80]. The via-switch in the crossbar is responsible for connection and disconnection between the horizontal and vertical signal lines by changing the switch on/off states. Besides, the top half of the crossbar serves as input and output multiplexers to the logic block and corresponds to the connection block in conventional FPGAs. On the other hand, the bottom half of the crossbar, which corresponds to the switch block, routes global interconnections. The logic block organizes combinational and sequential circuits. In via-switch FPGA, we reconfigure each CLB separately. To acquire this, via-switches are also placed at the boundary between adjacent CLBs as depicted in Figure 1.13.

Next, the following describes how to program the via-switch in the crossbar

Figure 1.12: Concept of via-switch FPGA.

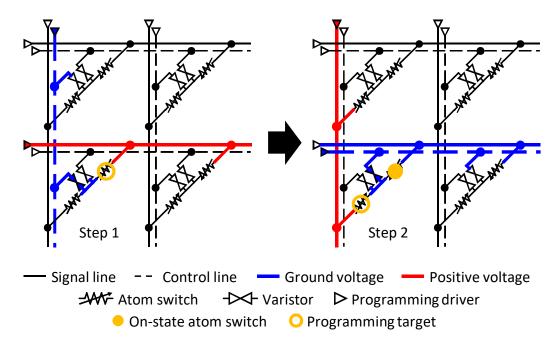

structure. Figure 1.14 illustrates the via-switch based crossbar structure. Both signal and control lines are aligned horizontally and vertically. This figure exemplifies programming steps in a 2x2 crossbar where an atom switch is turned on at each step. A pair of the perpendicular signal and control lines crossing at the via-switch of interest are used for switch programming. As mentioned in the previous subsection, when a high programming voltage is given between the signal and control lines, the varistor turns on and supplies programming current to the switch. Therefore, two programming drivers are activated at each step, and a positive voltage is given to one of the signal lines, and a ground voltage is given to one of the control lines. Other lines are floated. As shown in the figure, steps 1 and 2 successfully turn on the via-switch at the bottom left.

### 1.4.3 Issues of Via-Switch FPGA

Thanks to the advantages of via-switches as mentioned, via-switch FPGA is expected to significantly boost the energy efficiency compared to conventional FPGAs. On the other hand, the via-switch FPGA is facing some challenges for the practical application. First of all, it is primarily important to establish the fabrication and integration technologies of via-switches. For utilizing via-switches as programmable switches, they need to have a large on-off resistance ratio. Also, novel nano-sized devices such as via-switches face a challenge in terms of device yield, and hence highly-reliable manufacturing process is demanded. To tackle these issues, Refs. [74, 79, 90–92] have been actively developing the integration technology of via-switches and improving device characteristics. Besides, developing computer-aided design (CAD) tools for the via-switch FPGA

Figure 1.13: Structure of via-switch FPGA.

is also challenging. Based on the features and constraints of the via-switch FPGA architecture, it is essential to build appropriate CAD tools that are responsible for the logic synthesis, technology mapping, place and route. For this challenge, the mapping algorithm dedicated for the via-switch FPGA is devised [93, 94]. However, some critical challenges still remain for the practical application of the via-switch FPGA. This subsection explains these challenges along each phase of via-switch FPGA development, i.e., the chip design phase, manufacturing phase, and reprogramming phase at the user side.

First, as the challenge at the chip design phase, the interconnect structure that fully utilizes the advantages of via-switches is not sufficiently studied. The crossbar structure is considered to be suitable to efficiently accommodate many switches in a small area and to improve the performance in previous studies on FPGAs with atom switches. However, quantitative evaluations on the performance improvement effect in the case that the via-switch FPGA exploits crossbar structure are not enough. Besides, an appropriate connection structure between CLBs has not been considered so far. Furthermore, the repeater insertion technique for improving the interconnect performance, which is a common strategy in conventional circuit design, is not discussed. For example in

Figure 1.14: Via-switch based crossbar structure and switch programming steps.

conventional FPGAs, signal slope tends to become gentle due to the large circuit area and the large parasitic load of switch circuits. To prevent the signal distortion and improve the performance, conventional FPGAs frequently insert repeaters to the signal paths, where the repeater is a driving circuit to restore the distorted signals and is typically implemented by a buffer or inverter. From the above, the interconnect structure that maximizes the performance improvement effect thanks to via-switches needs to be clarified.

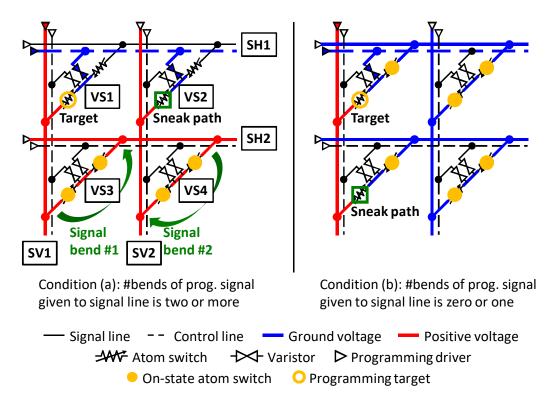

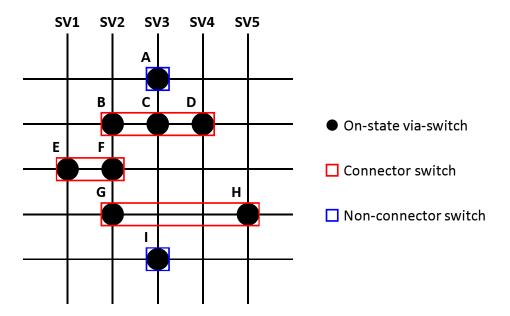

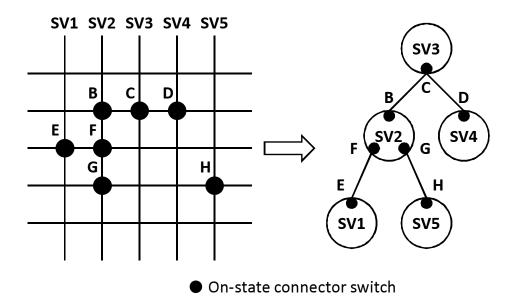

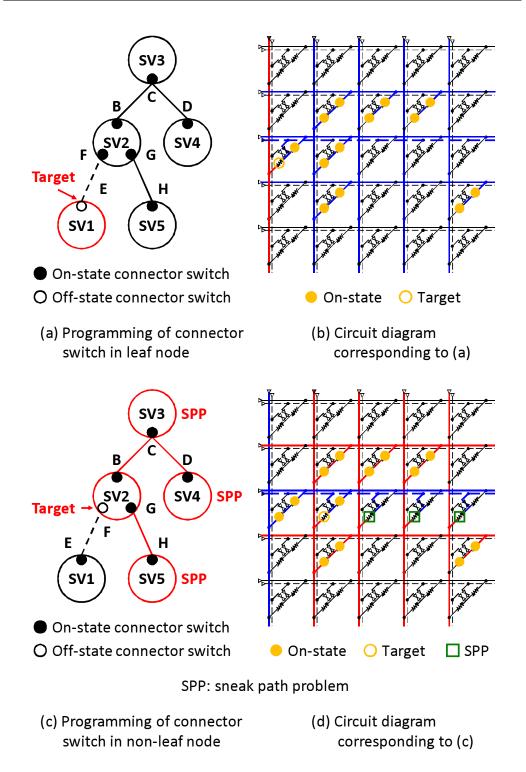

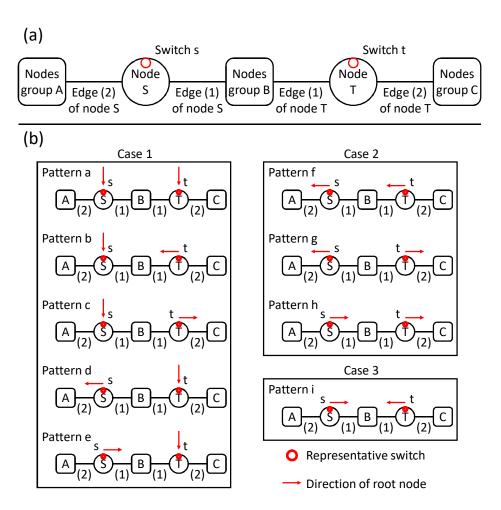

Next, in the manufacturing phase, via-switch FPGA manufacturer needs to inspect the via-switch based crossbar functionality before the shipment for ensuring that FPGA users can implement arbitrary routings. For this purpose, fault testing that investigates whether all the via-switches can be normally turned on and off is essential. However, fault testing methodology for via-switch based crossbar has not been developed. As mentioned, the via-switch has an upper limit on the number of reprogramming. Therefore, the fault testing method with a small number of reprogramming is desirable for maximizing the number of reprogramming at the FPGA user side after the shipment.