| Title        | A Study on Reducing the Amount of Out-of-Core<br>Data Access for GPU-Accelerated Applications |  |

|--------------|-----------------------------------------------------------------------------------------------|--|

| Author(s)    | 陸, 悦超                                                                                         |  |

| Citation     | 大阪大学, 2020, 博士論文                                                                              |  |

| Version Type | VoR                                                                                           |  |

| URL          | https://doi.org/10.18910/77462                                                                |  |

| rights       |                                                                                               |  |

| Note         |                                                                                               |  |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

A Study on Reducing the Amount of Out-of-Core Data Access for GPU-Accelerated Applications

Submitted to Graduate School of Information Science and Technology Osaka University

April 2020

Yuechao Lu

# **Published Papers**

## **Journal Papers**

- Yuechao Lu, Fumihiko Ino, and Kenichi Haighara, "Cache-Aware GPU Optimization for Out-of-Core Cone Beam CT Reconstruction of High-Resolution Volume," *IE-ICE Transactions on Information and Systems*, Vol.E99-D, No.12, pp.3060–3071, Dec. 2016.

- 2. Yuechao Lu, Ichitaro Yamazaki, Fumihiko Ino, Yasuyuki Matsushita, Stanimire Tomov, and Jack Dongarra, "Reducing Out-of-Core Data Access for GPU-accelerated Randomized SVD," *Concurrency and Computation: Practice and Experience*, accepted.

- 3. Yuechao Lu, Yasuyuki Matsushita, and Fumihiko Ino, "Block Randomized SVD on GPUs," *IEICE Transactions on Information and System*, accepted.

### **International Conference Papers**

Yuechao Lu, Boqi Gao, and Fumihiko Ino, "GPU-Accelerated Randomized Newton Method for Fast Training Malicious Web Site Classifier," Proceedings of the 18th International Conference on Security and Management (SAM), pp.95–99, Aug. 2019.

## **Oral Presentations**

1. Yuechao Lu, Fumihiko Ino, Yasuyuki Matsushita, and Kenichi Hagihara, "RLAGPU: High-performance Out-of-core Randomized Singular Value Decomposition on GPU," *Poster in the 8th GPU Technology Conference (GTC)*, May 2017.

## Abstract

The computing architectures are shifting quickly as we move forward to exascale computing. Heterogeneous computing architectures employing accelerators like graphics processing unit (GPU) have become the mainstream approach for high-performance computing (HPC) systems from supercomputers to mobile devices. However, the increased layers of the memory hierarchy in heterogeneous architectures have hindered the users to extract the full potential and maximum scalability of the hardware. Communication cost for transferring data between memory hierarchy dominates the overall processing time for most applications and the floating-point operations per second (flop/s) has become comparatively irrelevant.

In this work, we look into two applications to address the problems in accelerating applications with GPUs. The first application is the cone beam computed tomography (CT) reconstruction, which is an widely used by medical imaging devices. The second application is a matrix decomposition algorithm called randomized singular value decomposition (RSVD). We show that the CPU-GPU data transfer is the main bottleneck for processing large scale data on GPU-enabled systems. We first propose methods to accelerate RSVD by reducing the data transfer between the CPU and GPU. We then propose algorithms which modify the original RSVD to fit into the heterogeneous computing architecture. The proposed methods successfully move the performance bottleneck from CPU-GPU bandwidth bound to compute bound, so that the computation ability of the GPUs can be fully utilized for acceleration.

This thesis is divided into three parts. In the first part of this work, we propose a cacheaware optimization method to accelerate the out-of-core cone beam CT reconstruction on a GPU. Out-of-core data here are data that are too large to fit into the GPU memory at once. Utilizing the GPU in reconstructing CT images has gained its popularity for its high performance and low cost implementation compared to other methods. The proposed method extends a GPU-based previous method by increasing the cache hit rate to speed up the reconstruction of high-resolution volumes that exceed the capacity of GPU memory. More specifically, our approach accelerates the well-known Feldkamp, Davis, and Kress (FDK) algorithm by utilizing the following three strategies: (1) a loop organization strategy that identifies the best trade-off point between the cache hit rate and the number of off-chip memory accesses; (2) a data structure that exploits high locality within a layered texture; and (3) a fully pipelined strategy for hiding file input/output (I/O) time of GPU execution and data transfer time. We implement our proposed method on NVIDIA's Maxwell architecture and provide a tuning guideline for adjusting the execution parameters, which include the granularity and shape of thread blocks as well as the granularity of I/O data to be streamed through the pipeline, which maximizes reconstruction performance. Our experimental results show that it took less than three minutes to reconstruct a 2048<sup>3</sup>-voxel volume from 1200 2048<sup>2</sup>-pixel projection images on a single GPU; this translates to a speedup of approximately 1.47 as compared to a previous method. We also make clear a trade-off between the texture cache hit rate and the number of memory accesses. Concerning GPU optimization, we found that it is not necessarily efficient to compact as many tasks as possible into kernel execution to decrease total execution time. Instead, proper tuning is required to identify the optimum number of tasks that will minimize the overall time. With the aid of texture interpolation and cache-aware strategies, our presented GPU implementation achieves performance advantages over other computing platforms.

In the second part, we propose two acceleration methods, namely Fused and Gram, for reducing the out-of-core data access when performing RSVD on GPUs. Both methods accelerate GPU-enabled RSVD using the following three schemes: (1) a highly tuned general matrix-matrix multiplication (GEMM) scheme for processing out-of-core data on GPUs; (2) a data-access reduction scheme based on one-dimensional (1D) data partition; and (3) a first-in, first-out (FIFO) scheme that reduces CPU-GPU data transfer using a reverse iteration. The Fused method further reduces the amount of out-of-core data access by merging two GEMM operations into a single operation. In contrast, the Gram method reduces both incore (*i.e.*, all the working data can be held on the GPU memory) and out-of-core data access by explicitly forming the Gram matrix. According to our experimental results, the Fused and Gram methods improved the RSVD performance by up to  $1.9 \times$  and  $5.2 \times$ , respectively, compared with a straightforward method that deploys schemes (1) and (2) on the GPU. In addition, we present a case study of deploying the Gram method for accelerating robust principal component analysis (RPCA), a convex optimization problem in machine learning.

In the third part, we propose a two-pass RSVD, named block randomized SVD (BRSVD), designed for matrices with a slow-decay singular spectrum that is often observed in image data. BRSVD fully utilizes the power of modern computing system architectures and efficiently processes large-scale data in a parallel and batched fashion. Our experiments show that BRSVD effectively moves the performance bottleneck from data transfer to computation, so that outperforms existing RSVD methods in terms of speed with retaining similar accuracy. We also show an application of randomized SVD to convex RPCA on a GPU, which shows significant speedup in computer vision applications.

Our work demonstrates that communication cost is an important factor to influence the overall performance. The first application demonstrates that cache-aware optimization improves overall performance effectively. The second application shows that reducing the communication cost at the expense of increased computational cost is a viable approach in a computing environment where communication cost exceeds the computational cost. Furthermore, our work shows that redesigning algorithms to fit for the heterogeneous computing architecture is a feasible approach in dealing with bandwidth bound problems.

## Acknowledgements

I would like to express my deep and sincere gratitude to my supervisor, Professor Fumihiko Ino, for his many valuable and insightful advices and for his continuous encouragement during my years.

I would like to sincerely thank Professor Yasuyuki Matsushita, who has guided this work with many constructive suggestions and detailed help on my thesis.

I would like to thank the member of my thesis committee: Professor Toshimitsu Masuzawa, Professor Yasuyuki Matsushita, and Professor Fumihiko Ino for their insightful comments and encouragement.

I am deeply grateful to Honorary Professor Kenichi Hagihara and Associate Professor Masao Okita for discussions, for their many valuable and thoughtful comments, and for their encouragement.

I would like to thank my collaborators: Professor Jack Dongarra, Dr. Ichitaro Yamazaki, and Professor Stanimire Tomov (affiliated with the innovative computing laboratory, University of Tennessee). They gave me a lot of motivating research ideas and guided me through the difficulties during the research.

I acknowledge the financial support from Humanware Innovation Program at Osaka University in the last five years.

Finally, I am indebted to members of Ino laboratory, for their daily support and useful comments.

# Contents

| 1 | Intr | oduction                                                         | 1         |

|---|------|------------------------------------------------------------------|-----------|

|   | 1.1  | Overview of High-Performance Computing                           | 1         |

|   | 1.2  | Overview of Graphics Processing Unit (GPU)                       | 2         |

|   |      | 1.2.1 Architectural Difference between CPU and GPU               | 2         |

|   |      | 1.2.2 GPU Computing Model                                        | 2         |

|   | 1.3  | Challenges in Heterogeneous Computing Architectures              | 4         |

|   | 1.4  | Contributions of This Thesis                                     | 5         |

| _ | ~    |                                                                  |           |

| 2 |      | he-Aware GPU Optimization for Out-of-Core Cone Beam CT Recon-    | -         |

|   |      | action of High-Resolution Volumes                                | 7         |

|   | 2.1  |                                                                  | 7         |

|   | 2.2  | Related Work                                                     | 9         |

|   | 2.3  | Preliminaries                                                    | 10        |

|   |      | 2.3.1 FDK Reconstruction Algorithm                               | 11        |

|   | 2.4  | 2.3.2 GPU Implementation of the FDK Algorithm                    | 12        |

|   | 2.4  | Proposed Method                                                  | 14        |

|   |      | 2.4.1 Cache-aware Loop Organization                              | 15        |

|   |      | 2.4.2 Cache-aware Data Structure with Layered Texture            | 16        |

|   | ~ ~  | 2.4.3 Pipelined Strategy that Includes I/O Interface             | 17        |

|   | 2.5  | Experimental Results                                             | 18        |

|   |      | 2.5.1 Parameter Configuration                                    | 19        |

|   |      | 2.5.2 Breakdown Analysis                                         | 22        |

|   |      | 2.5.3 Efficiency Analysis                                        | 23        |

|   |      | 2.5.4 Estimated Performance on the Future Architecture           | 25        |

|   | 2.6  | Conclusions                                                      | 26        |

| 3 | Red  | lucing the Amount of Out-of-Core Data Access for GPU-Accelerated |           |

|   |      | ndomized SVD                                                     | <b>27</b> |

|   | 3.1  | Introduction                                                     | 27        |

|   | 3.2  | Related Work                                                     | 29        |

|   |      | 3.2.1 Deterministic SVD Algorithms                               | 29        |

|   |      | 3.2.2 Randomized Algorithms                                      | 29        |

|   |      | 3.2.3 GPU-Accelerated Randomized Algorithms                      | 30        |

|   | 3.3  | RSVD Algorithm                                                   | 31        |

|   | 3.4  | GPU-Accelerated Out-of-Core GEMM                                 | 32        |

|   |      |                                                                  |           |

|   |              | 3.4.1 Performance Model                                            | 33       |

|---|--------------|--------------------------------------------------------------------|----------|

|   |              | 3.4.2 Row-wise 1D Partition Scheme for Out-of-Core GEMM            | 35       |

|   |              | 3.4.3 Performance Tuning and Comparison of Out-of-Core GEMM        | 37       |

|   | 3.5          | Proposed Out-of-Core RSVD Methods                                  | 39       |

|   |              | 3.5.1 Basic and FIFO Schemes for Reducing Out-of-Core Data Access  | 41       |

|   |              | 3.5.2 Fused Method for Reducing Out-of-Core Data Access            | 42       |

|   |              | 3.5.3 Gram Method for Reducing In-Core and Out-of-Core Data Access | 43       |

|   |              | 3.5.4 Implementation details                                       | 44       |

|   | 3.6          | Experimental Results                                               | 45       |

|   |              | 3.6.1 Performance Evaluation                                       | 45       |

|   |              | 3.6.2 Performance Comparison                                       | 49       |

|   |              | 3.6.3 Numerical Study with Synthetic and Real Data                 | 50       |

|   | 3.7          | Case Study with RPCA                                               | 51       |

|   | 3.8          | Conclusions                                                        | 54       |

| 4 | Blo          | ck Randomized Singular Value Decomposition on GPUs                 | 57       |

| т | 4.1          | Introduction                                                       | 57       |

|   | 4.2          | Preliminaries                                                      | 58       |

|   | 4.3          | Proposed Method: Block Randomized SVD (BRSVD)                      | 59       |

|   | 1.0          | 4.3.1 Efficiency Analysis                                          | 61       |

|   |              | 4.3.2 Implementation Detail                                        | 63       |

|   | 4.4          | Experiments                                                        | 64       |

|   |              | 4.4.1 Performance Comparison                                       | 64       |

|   |              | 4.4.2 Experiment Environment and Setup                             | 64       |

|   |              | 4.4.3 Performance Comparison Results                               | 65       |

|   |              | 4.4.4 Accuracy Evaluation                                          | 66       |

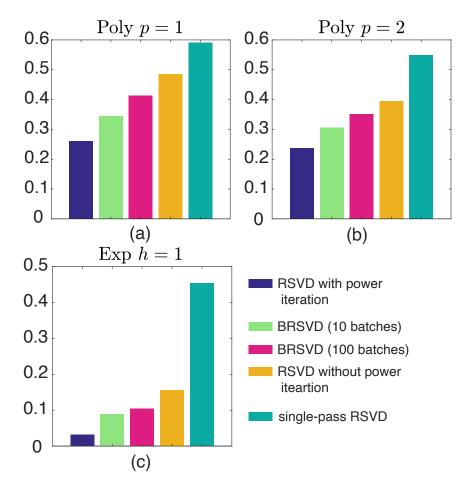

|   |              | 4.4.5 Algorithm Comparison                                         | 70       |

|   | 4.5          | Applications of BRSVD                                              | 72       |

|   |              | 4.5.1 Eigenfaces                                                   | 72       |

|   |              | 4.5.2 Computed Tomography                                          | 72       |

|   | 4.6          | Conclusions                                                        | 73       |

| 5 | Car          | clusions                                                           | 75       |

| J | 5.1          | Summary of This Thesis                                             | 75<br>75 |

|   | $5.1 \\ 5.2$ | Future Work   Future Work                                          | 75<br>76 |

|   | 0.2          |                                                                    | 10       |

# List of Figures

| $1.1 \\ 1.2$ | Maxwell GPU architecture [71]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 3        |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1.2          | ture with GPUs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5        |

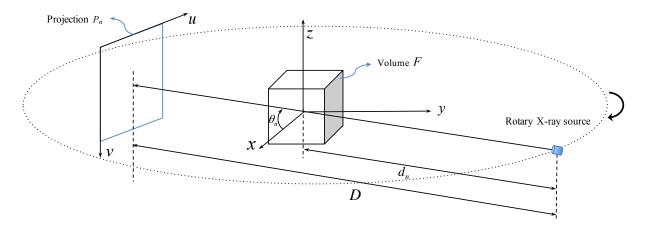

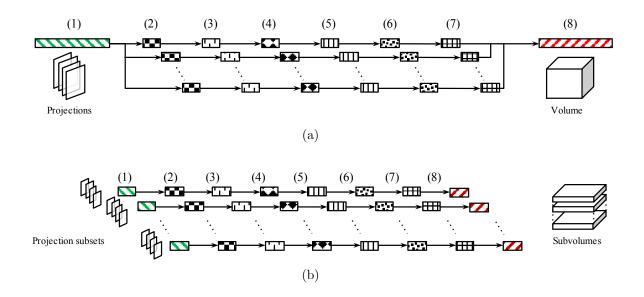

| 2.1<br>2.2   | Geometry for back-projection of the <i>n</i> -th filtered projection, where $0 \le n < N$ .<br>Reconstruction pipelines of (a) Okitsu's previous method [82] and (b) the<br>proposed method. Both pipelines consist of the following eight steps, with the<br>first and last steps not pipelined in the previous method: (1) raw projections<br>are loaded from a storage device into CPU memory, (2) projections in CPU<br>memory are then transferred to GPU memory; (3) ramp filtering is applied<br>to produce filtered projections, (4) filtered projections are transferred back to<br>CPU memory if necessary, (5) filtered projections are transferred from CPU<br>memory to GPU memory if necessary; (6) back-projection is performed to<br>produce a subvolume; (7) the subvolume is transferred to CPU memory, and | 11       |

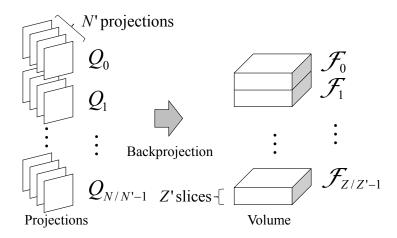

| 2.3          | (8) the subvolume in CPU memory is written to the storage device Data decomposition scheme in which the back-projection kernel is invoked for each pair $\langle Q_m, \mathcal{F}_k \rangle$ of subset $Q_m$ of projections and subvolume $\mathcal{F}_k$ , where                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 13       |

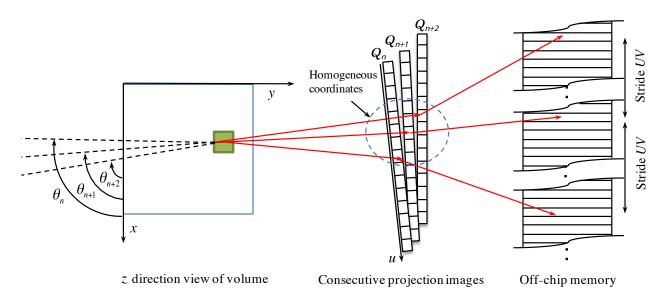

| 2.4          | $0 \leq m < N/N' - 1$ and $0 \leq k < Z/Z' - 1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 13       |

| 2.5          | V are the horizontal and vertical resolutions of projections, respectively<br>Micro-benchmarks for evaluating texture access performance. Here two access<br>patterns were examined with $U = V = 1024$ and $1 \le L \le 64$ ; the access<br>patterns are (a) intra-layer-first and (b) inter-layer-first patterns. A single<br>thread was used to fetch all texels. The innermost loop of both patterns was<br>unrolled for optimization                                                                                                                                                                                                                                                                                                                                                                                     | 16<br>17 |

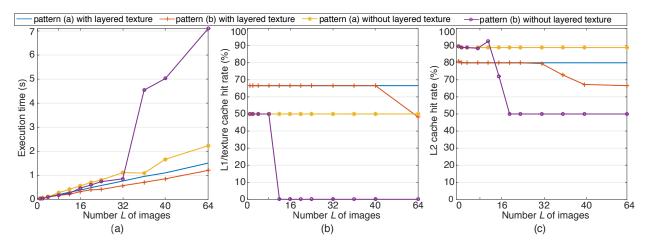

| 2.6          | Benchmark and profiling results for different loop organizations and data structures, showing (a) execution time, (b) L1/texture cache hit rate, and (c) L2 cache hit rate. Here, intra-layer-first and inter-layer-first patterns were investigated with a layered texture and non-layered ( <i>i.e.</i> , naive two-dimensional) textures.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 18       |

|              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 10       |

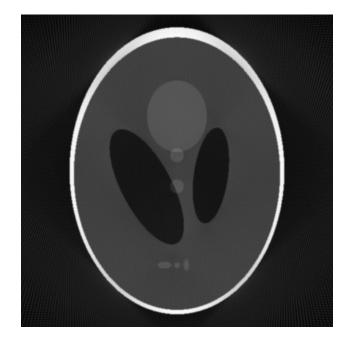

| 2.7  | Shepp-Logan phantom $[94]$ reconstructed by our experimental machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 20 |

|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

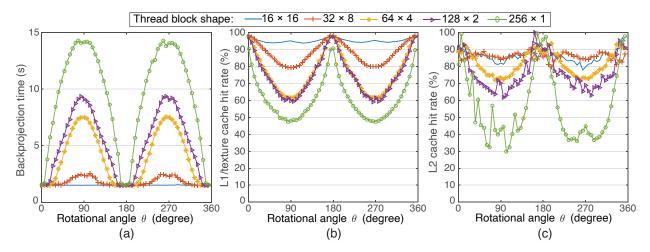

| 2.8  | Back-projection performance and profiling results with different shapes of thread blocks and rotational angles: (a) back-projection time, (b) L1/texture cache hit rate, and (c) L2 cache hit rate. These results were obtained with a thread block size of 256 for the medium dataset, with $N' = 20$ and $Z' = 512$ .                                                                                                                                                                                                                                                                                                                                                                                     | 21 |

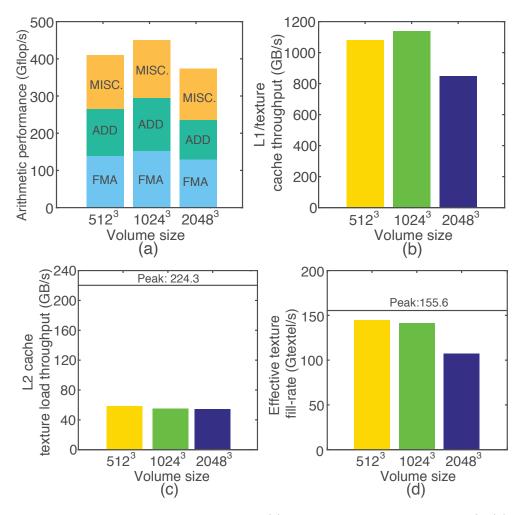

| 2.9  | Back-projection performance and profiling results with different projection<br>subset sizes $N'$ and thread block sizes: (a) back-projection times, (b) L1/texture<br>cache hit rates, and (c) number of global memory accesses. These results were<br>obtained with a medium dataset and $Z' = 512$                                                                                                                                                                                                                                                                                                                                                                                                        | 22 |

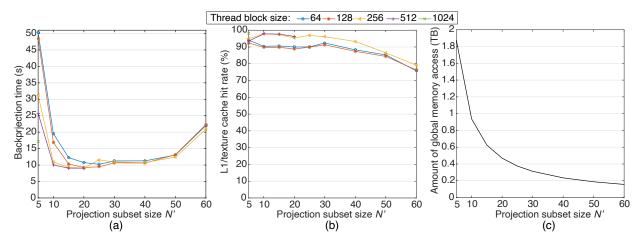

| 2.10 | Profiling results for different data sizes: (a) arithmetic performance in Gflop/s, (b) L1/texture cache throughput, (c) L2 cache texture load throughput, and (d) effective texture fill rate. FMA, ADD, and MISC in (a) refer to fused multiply-add [77], addition, and other instructions, respectively. The horizontal lines in (c) and (d) are peak memory bandwidth and peak texture fill rate, respectively, with the latter derived according to the boosted clock speed presented in Table 2.2.                                                                                                                                                                                                     | 24 |

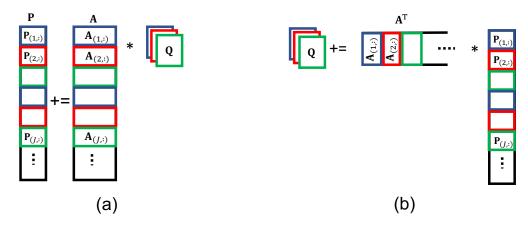

| 3.1  | Proposed row-wise 1D partition scheme for tall-skinny GEMM. (a) $\mathbf{P} = \mathbf{A}\mathbf{Q}$ (line 3 of Algorithm 3), where $\mathbf{A}$ is partitioned into blocks and $\mathbf{Q}$ is broadcasted among GPUs. (b) $\mathbf{Q} = \mathbf{A}^{\top}\mathbf{P}$ , where $\mathbf{Q}$ is accumulated by reduction. Blocks are assigned to CUDA streams [77] in a round-robin fashion ( <i>i.e.</i> , block-cyclic distribution as illustrated with different colors). Because $\mathbf{P}$ is computed in a block-wise manner, the GPU is allowed to store the part of $\mathbf{P}$ .                                                                                                                  | 35 |

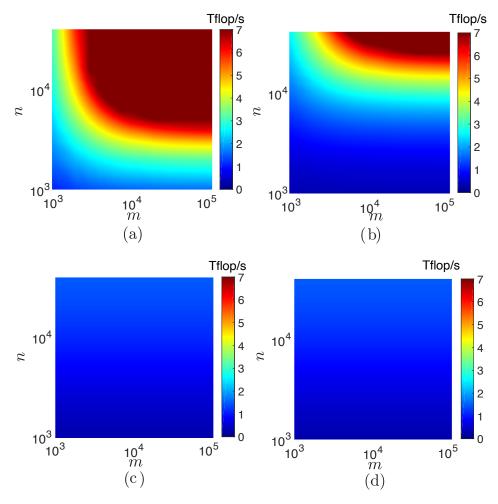

| 3.2  | Performance upper bound of GPU-accelerated out-of-core GEMM: $\mathbf{P} = \mathbf{AQ}$ ,<br>where $\mathbf{P} \in \mathbb{R}^{m \times \ell}$ , $\mathbf{A} \in \mathbb{R}^{m \times n}$ and $\mathbf{Q} \in \mathbb{R}^{n \times \ell}$ . Row-wise 1D partitioning results<br>for (a) square ( $\ell = n$ ) and (b) tall-skinny matrices $\mathbf{Q}$ ( $\ell = n/10$ ). 2D partition<br>results for (c) square ( $\ell = n$ ) and (d) tall-skinny matrices $\mathbf{Q}$ ( $\ell = n/10$ ).<br>Hardware specific parameters were set for the Tesla V100 GPU: $B = 13$ GB/s<br>and $C = 7$ Tflop/s. Both partition schemes used the block size b of 1024,<br>which was the default setup of cuBLAS-XT [76] | 36 |

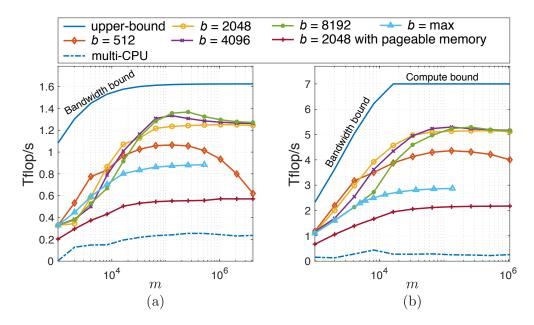

| 3.3  | Out-of-core GEMM performance with different block sizes $b$ on a single Tesla V100 GPU. Measured results for (a) small ( $\ell = n = 1000$ ) and (b) large square matrices ( $\ell = n = 5000$ ). The maximum block size ( $b = \max$ ) indicates the performance without data partition. A multithreaded CPU version was also evaluated on two 8-core CPUs. Note that the upper-bound line is curved because the horizontal axis of our extended model is the height of matrix <b>A</b> , which is different from that ( <i>i.e.</i> , the operational intensity) of the original roofline model.                                                                                                          | 38 |

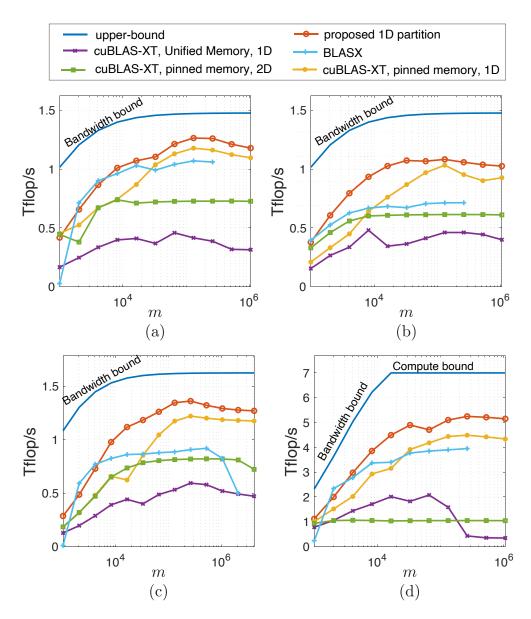

| 3.4  | Performance comparison of the out-of-core GEMM implementations on a sin-<br>gle Tesla V100 GPU. Results with different shapes for the matrix <b>Q</b> : (a)<br>tall-skinny ( $n = 5000, \ell = 500$ ), (b) short-wide ( $n = 500, \ell = 5000$ ), (c) small<br>square ( $\ell = n = 1000$ ) and (d) large square ( $\ell = n = 5000$ ). BLASX is<br>a high-level library that hides specific data partition and memory allocation<br>methods                                                                                                                                                                                                                                                                | 39 |

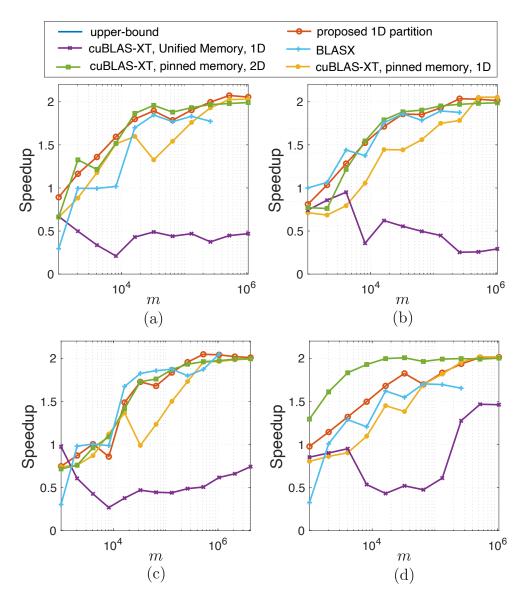

| 3.5  | Speedup of the out-of-core GEMM implementations on two Tesla V100 GPUs.<br>Results with different shapes for the matrix <b>Q</b> . (a) tall-skinny $(n = 5000, \ell = 500)$ , (b) short-wide $(n = 500, \ell = 5000)$ , (c) small square $(\ell = n = 1000)$ and (d) large square $(\ell = n = 5000)$ . For each implementation, we executed the same implementation on a single GPU to compute the speedup                                                                                                                                                                                                                                                          | 40 |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

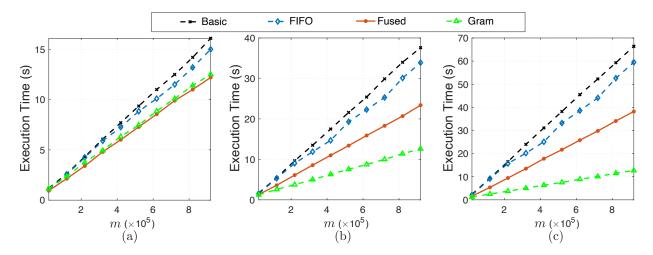

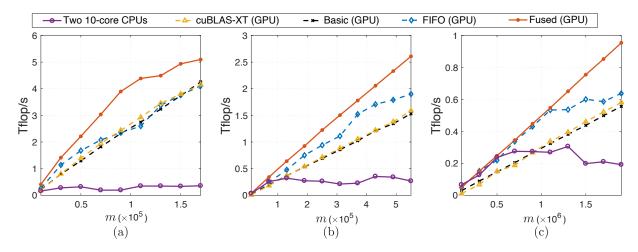

| 3.6  | RSVD execution time a single Tesla V100 GPU with different numbers of rows $m$ . Results for power iteration counts (a) $q = 1$ , (b) $q = 4$ , and (c) $q = 8$ . Matrix sizes were $n = 5000$ and $\ell = 500$ . The results are shown in execution time instead of flop/s because the flop counts of the Gram method are different from others. CPU-based results are omitted to focus on GPU-based results.                                                                                                                                                                                                                                                       | 47 |

| 3.7  | Speedup of one Tesla V100 GPU over two Xeon Silver 4114 CPUs with dif-<br>ferent numbers of rows $m$ . Results for power iteration counts (a) $q = 1$ , (b)<br>$q = 4$ , and (c) $q = 8$ . Matrix sizes were $n = 5000$ and $\ell = 500$ . For each<br>method, we executed a multithreaded version of Algorithm 3 on two CPUs to<br>compute the speedup                                                                                                                                                                                                                                                                                                              | 47 |

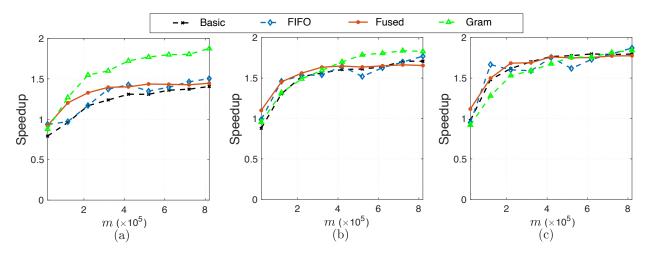

| 3.8  | Speedup of two Tesla V100 GPUs over one V100 GPU with different numbers of rows $m$ . Results for power iteration counts (a) $q = 1$ , (b) $q = 4$ , and (c) $q = 8$ . Matrix sizes were $n = 5000$ and $\ell = 500$ . For each method, we executed the same method on a single GPU to compute the speedup.                                                                                                                                                                                                                                                                                                                                                          | 48 |

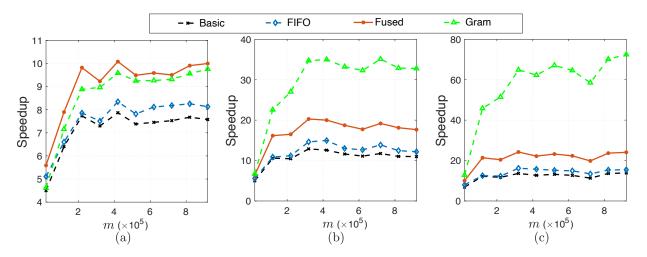

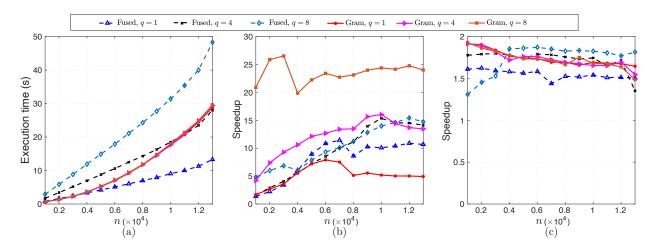

| 3.9  | RSVD performance comparison of Fused and Gram methods with different<br>numbers of columns $n$ and different power iteration count $q$ . (a) Execution<br>time on a single Tesla V100 GPU, (b) speedup of one GPU over two Xeon<br>Silver 4114 CPUs, and (c) speedup of two GPUs over one GPU. Matrix sizes<br>were $m = 4 \times 10^5$ and $\ell = n/10$ . We executed a multi-threaded version of<br>Algorithm 3 to compute the speedup over two CPUs in (b). For each method<br>in (c), the same method was executed to compute the speedup over a single<br>GPU                                                                                                  | 48 |

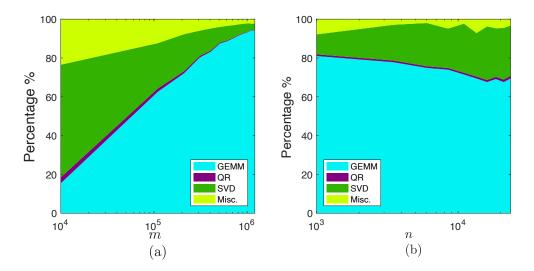

| 3.10 | Breakdown of execution time on a single Tesla V100 GPU with $\ell = n/10$ and $q = 4$ . Results of (a) growing height $m$ of $\mathbf{A}$ with fixed width $n = 5000$ and of (b) growing width $n$ of $\mathbf{A}$ with fixed height $m = 1 \times 10^5$ . GEMM includes the time of CPU-GPU data transfer and GEMM operations. SVD denotes the deterministic SVD of matrix $\mathbf{B}$ . Misc. is composed of initialization and random matrix generation.                                                                                                                                                                                                         | 49 |

| 3.11 | Comparison of CPU-based method, cuBLAS-XT [76], and the proposed Fused<br>method with different matrix shapes. (a) rectangular with $m : n : \ell = 100 :$<br>$10 : 1$ , (b) tall-skinny with $m : n : \ell = 1000 : 10 : 1$ , and (c) extremely<br>tall-skinny with $m : n : \ell = 10000 : 10 : 1$ . Results obtained on a single Tesla<br>V100 GPU are presented in flop/s. Power iteration count was $q = 4$ . The<br>CPU-based method was multi-threaded using two Xeon Silver 4114 CPUs.<br>Note that the horizontal scale is different in three setups because we set the<br>maximum input matrix size to the maximum memory size that our system<br>can hold | 51 |

|      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |    |

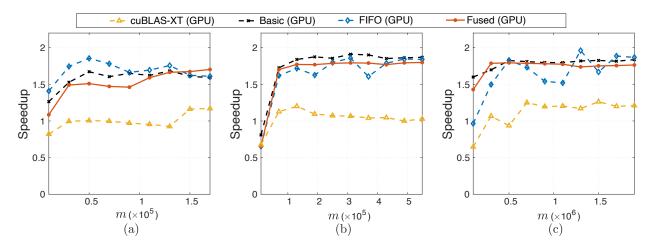

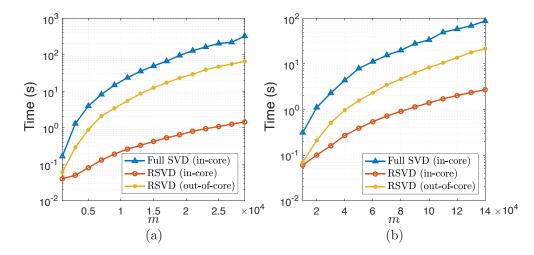

| <ul> <li>3.12 Speedup of two Tesla V100 GPUs over one V100 GPU with different matrix shapes: Results for (a) rectangular matrices with m : n : ℓ = 100 : 10 : 1, (b) tall-skinny matrices with m : n : ℓ = 1000 : 10 : 1, and (c) extremely tall-skinny matrices with m : n : ℓ = 10000 : 10 : 1. Power iteration count was q = 4. For each method, the same method was executed to compute the speedup.</li> <li>3.13 Comparison of out-of-core and in-core performance. (a) Execution time with square matrices (m = n). (b) Execution time with tall-skinny matrices (n = m/10). Note that for in-core implementation of full SVD and RSVD, the</li> </ul> | 52       |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| CPU-GPU data transfer time is not included                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 53<br>53 |

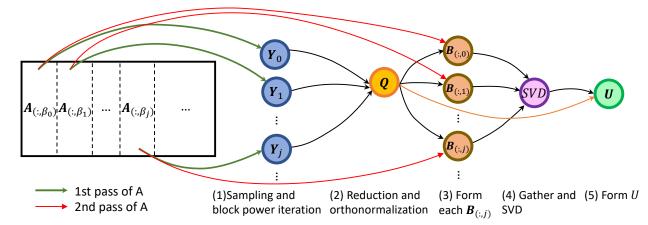

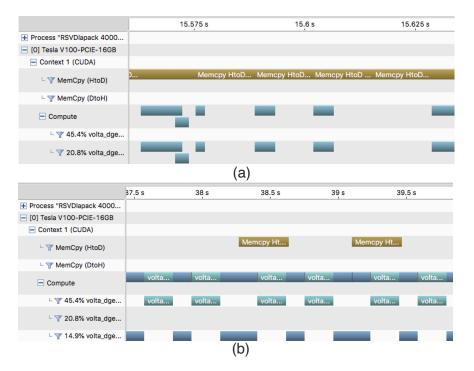

| <ul> <li>4.1 Diagram of proposed BRSVD method. Column blocks A<sub>(:,βj)</sub> in local memory are reused in the RSVD computation pipeline</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 62       |

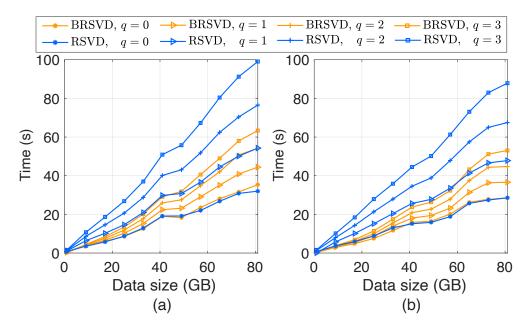

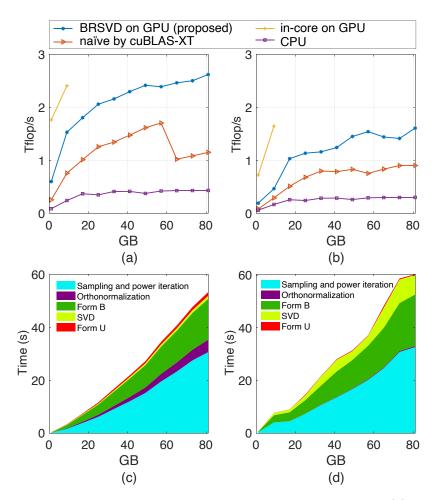

| <ul> <li>number q. (a) and (b) show the execution time of tall-skinny matrices (m : n : k = 1024 : 32 : 1) and square (m : n : k = 256 : 256 : 1) ones with different q. The partition number for BRSVD was set to s = 10. The sampling parameters were set as: o = k for all setups.</li> <li>4.3 Performance comparison for different data sizes in double precision. (a) and (b) show overall performance of tall-skinny matrices (m : n : k = 1024 : 32 : 1) and square (m : n : k = 256 : 256 : 1) ones in Tflop/s. Tflop/s is calculated as #flops (Table 4.1) divided by the measured running time. (c) and (d) show</li> </ul>                        | 66       |

| the measured time breakdown of BRSVD for tall-skinny and square matrices.<br>The parameters were set as: $o = k$ and $q = 2$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 67       |

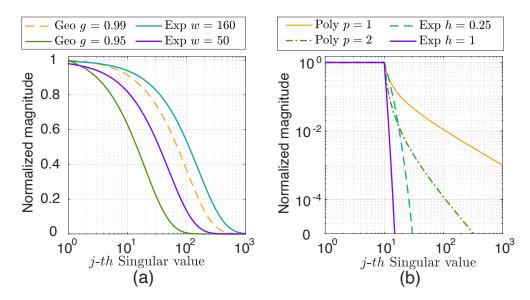

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 68       |

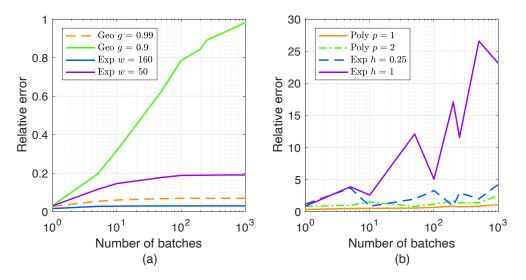

| 4.6 Result of relative error w.r.t. the varying number of batches. (a) Geometric                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 69       |

| 4.7 Actual error with different singular spectrum decay patterns which are (a)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 70       |

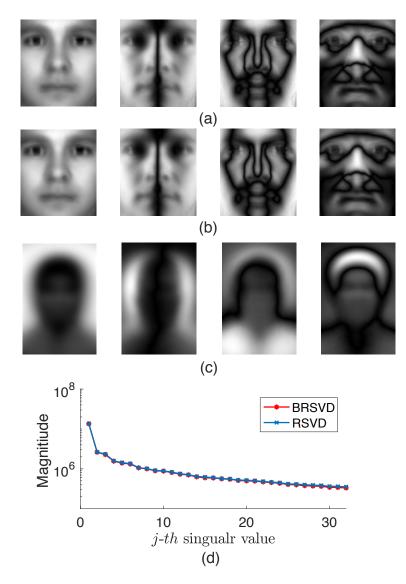

| 4.8 Comparison of BRSVD and deterministic rank- $k$ SVD. (a) and (b) shows<br>the eigenfaces from the Extended Yale Face dataset [32] approximated by<br>BRSVD and deterministic rank- $k$ SVD, respectively. (c) shows the eigenfaces<br>computed from the FERET dataset [87] approximated by BRSVD. (d) shows                                                                                                                                                                                                                                                                                                                                               | 71       |

| the singular values calculated by BRSVD and RSVD for the FERET dataset.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 73       |

# List of Tables

| 2.1 | Comparison of the performance of our work with relevant recent works. Note that back-projection throughput $\rho$ which is measured in GUPS, is given by $\rho = NXYZ/T$ , where N is the number of projections, $X \times Y \times Z$ is the volume size in voxels, and T is the back-projection time, which includes data transfer times between CPU and GPU. Further, U and V are the horizontal and vertical sizes of a projection, respectively. Note that efficient cache utilization achieves an efficiency of more than 100%. | 10 |

|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 2.2 | Specifications of our experimental machine                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 19 |

| 2.3 | Comparing the performance of our proposed method and previous method<br>using different data sizes. The baseline corresponds to Okitsu's method [82]<br>with the best parameters tuned for the Maxwell architecture. Further, "Both<br>strategies" corresponds to our proposed method                                                                                                                                                                                                                                                 | 23 |

| 2.4 | Breakdown analysis of execution times for the large dataset. Here, "No pipeline" means that all steps were processed sequentially with synchronous APIs, whereas the "Previous pipeline" and "Proposed pipeline" were processed asynchronously. These results were obtained with the large dataset, with $N' = 16$ and $Z' = 256$ .                                                                                                                                                                                                   | 23 |

| 2.5 | GPU architecture comparsion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 26 |

| 3.1 | Comparison of the proposed methods in terms of computational cost, the number of data passes, and CPU-GPU data transfer cost. The number of data passes and CPU-GPU data transfer cost correspond to in-core access cost and out-of-core access cost, respectively. We consider matrix <b>A</b> to evaluate the number of data passes. Both the Fused and Gram methods adopt the FIFO scheme to reduce the CPU-GPU data transfer cost                                                                                                 | 41 |

| 3.2 | Comparison of approximation error $\ \mathbf{A} - \hat{\mathbf{A}}\ _F / \ \mathbf{A}\ _F$ with different SVD methods and different power iteration count $q$                                                                                                                                                                                                                                                                                                                                                                         | 51 |

| 3.3 | Execution time of RPCA based on two Xeon Silver 4114 CPUs and two Tesla V100 GPUs. Both implementations converged with the same number (28) of iterations.                                                                                                                                                                                                                                                                                                                                                                            | 54 |

|     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |    |

- 4.1 Computational and communication costs comparison. #flops refers to the arithmetic computational cost in floating point operations. #word indicates communication cost between CPU and GPU. Line # indicates the corresponding operation blocks in Algorithm 10. The non-dominant terms of #flops for random number generation in (1), QR in (4) and SVD in (6) are dropped. (For a detailed #flops count, please refer to Matrix Computations [34] and LAPACK working note [12].) We show the commucation cost for out-of-core GEMM in item (2), (3) and (5). b denotes the partition size in out-of-core GEMM. The value of b varies in different implementations (e.g. LAPACK or cuBLAS) and hardware architectures. Note that if  $b \ge l$ , #words (RSVD) are mn, 2qmn and mn for item (2), (3) and (5), respectively. . . . . . . . . . 63

- 4.4 Accuracy comparison for the leading four left singular vectors. The sampling parameters were set as: k = o = 32 for Yale Face and k = o = 128 for FERET, respectively. Other parameters were set as: q = 2 and s = 10 for both datasets. 74

# Chapter 1 Introduction

In this chapter, we first brief the history of high-performance computing (HPC). We then describe the recent heterogeneous computing architecture with GPU and the bottleneck for accelerating applications on this architecture. After that, We introduce the two topics of this work. Finally, we summarize the contributions of this thesis.

## 1.1 Overview of High-Performance Computing

In recent years, HPC has gradually entered almost all aspects of science and engineering. HPC enables scientists and engineers to construct and validate large simulation models like molecular simulation and plasma fusion simulation. Supercomputers now are regarded as an essential tool in driving new exploration and discovery. In 1997, the first supercomputer reached Tflop/s was called ASCI Red and was built by Sandia National Lab [21]. In 2008, a supercomputer called RoadRunner at Los Alamos National Lab first reached Pflop/s [8].

As we move forward to exascale computing [19], the supercomputing architectures are rapidly shifting. The traditional customized CPUs, networking, and storage systems for supercomputers are diminishing. Three architectures are emerging: the first is that the trend of building supercomputers with commodity CPUs like Intel Xeon. Those machines have dominated the Top 500 list<sup>1</sup>. The second is that systems with accelerators are increasing. Over one hundred systems out of Top 500 adopt accelerators like GPUs or field-programmable gate array (FPGA). This kind of heterogeneous architectures is expected to become mainstream soon. The third is that lightweight CPUs like advanced RISC machine (ARM) have entered the realm of supercomputing. Lightweight CPUs have much lower power consumption and heat dissipation than traditional CPUs. This kind of supercomputer fits needs like building supercomputers with a limited power supply.

Regarding the benchmark software for supercomputers, LINPACK [20] has been the de facto tool for more than 30 years. Solving a dense system of linear equation  $\mathbf{A}\mathbf{x} = \mathbf{b}$  is used as the benchmark in LINPACK. The idea is that making matrix  $\mathbf{A}$  as large as possible, then solving the equation using Gaussian elimination with partial pivoting. By measuring the performance with a maximum size of  $\mathbf{A}$ , an actual performance peak will be obtained.

<sup>&</sup>lt;sup>1</sup>top500.org

Combined with the theoretical peak performance, those numbers are the benchmark values for supercomputers on the Top 500 list.

## 1.2 Overview of Graphics Processing Unit (GPU)

NVIDIA, AMD, and ARM are three major vendors for commodity GPUs. The former two provide their GPUs mainly for desktops and workstations, while ARM only provides GPUs for mobile devices with low power consumption. All of their products support the programming framework OpenCL [66]. In this work, we focus on NVIDIA GPUs and their programming framework called CUDA [77]. The reason is that NVIDIA GPUs yield the best performance per unit and dominate the accelerator market in HPC. The methods proposed in the work are general and can be extended to GPUs provided by other vendors.

#### 1.2.1 Architectural Difference between CPU and GPU

The major difference between CPU and GPU is that CPU is latency-focused or serialfocused, while GPU is throughput-focused or parallel-focused. Modern CPUs have powerful arithmetic logic units (ALUs), which include complex circuits for functions like instruction reordering, branch prediction, out-of-order execution, paging, and caching. Almost all those functions aim at reducing the latency of program execution.

On the other hand, GPUs use the opposite strategy. The ALUs on GPUs have much fewer functions than those on CPUs. Those simple ALUs are called CUDA cores by NVIDIA. A typical GPU is compacted with thousands of CUDA cores. GPU hides the latency behind high throughput provided by CUDA cores and complex memory systems. CUDA cores are grouped into an array of streaming multiprocessors (SMs). To compensate for the CUDA cores, each SM is also equipped with ALUs like special function units (SFUs), double precision units, and warp schedulers. CUDA cores are in charge of processing 32-bit integer and floating-point operations. SFUs are in charge of special arithmetic operations like reciprocation. Double-precision units are in charge of double-precision operations. The number of double-precision units in a single SM varies according to the target market of a certain GPU. In the CUDA framework so far, 32 threads are packed into a single unit called *warp* for managing and scheduling execution. A hardware mechanism called warp scheduler manages the dispatch of warps to CUDA cores.

In general, using implementations based on CUDA offloads the performance bottleneck of a CPU-based sequential code. Such offloaded workloads can be implemented as *kernel functions*, which can be parallelized via millions of GPU threads for acceleration.

#### 1.2.2 GPU Computing Model

Single instruction multiple data (SIMD) is the most widely adopted parallel computing model. SIMD generally means that all processors execute the same instruction while the data can be different on each processor. The constraint is that SIMD uses vector instructions (*e.g.* AVX for Intel CPU). Vector instructions perform the same operation on multiple data elements. However, data must be loaded and stored contiguously in vector instructions.

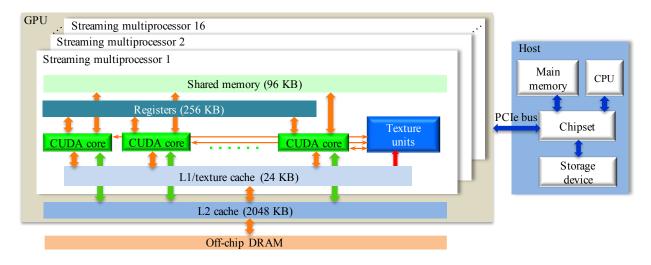

Figure 1.1: Maxwell GPU architecture [71].

NVIDIA improved the SIMD computing model and proposed single instruction multiple threads (SIMT) model for its GPU computing. SIMT relaxes the constraint of SIMD. SIMT allows threads to take different execution paths in the unit of warp.

We use the Maxwell GPU [71] (Fig. 1.1) for the explanation of the GPU computing model. Similar to other CUDA-compatible GPUs, this architecture has an array of SMs to process millions of tasks in parallel. Regarding the memory hierarchy inside the SM, there are registers, a shared memory, and L1 cache. Registers provide the shortest access latency, analogous to CPU registers, but different in number; here there are 64K 32-bit registers. The shared memory is a software-managed cache that allows CUDA cores to more efficiently share data inside an SM so that they do not need to share through the slow off-chip memory. Finally, the L1 cache acts as a read-only cache and coalescing buffer for off-chip memory access [72]. L1 cache can be accessed by all threads assigned to the current SM. Outside the SM, there are L2 cache, memory controller, texture caches, and translation lookaside buffers. L2 cache and memory controller together controls memory request so that threads that access the same piece of memory do not need to access slow off-chip memory.

Outside of the SMs, there is an off-chip memory called GPU memory. Although GPU memory provides a large storage of up to 32 GB, its latency of several hundreds of clock cycles is much longer than that of the on-chip memory. GPU memory can be used as both texture and global memory. Here, texture memory stores read-only data that can be accessed using hardware interpolation, while global memory stores readable/writable data for CUDA cores. As shown in the figure, the L2 cache is an on-chip cache located between the SMs and global memory.

During kernel execution, threads are cyclically assigned to SMs in the unit of a thread block [77], *i.e.*, a group of threads organized by CUDA programmers. Different thread blocks must be independent of each other with respect to data dependencies; otherwise parallelization cannot be correctly achieved. Resident thread blocks that have been assigned consume SM resources, including registers and shared memory, such that there are limitations on the maximum number of resident threads and that of thread blocks. This assignment process is repeated until all thread blocks finish execution.

Threads in a warp, which share the same instruction at each clock cycle, are processed on an SM in parallel. While threads in the same warp access global memory, memory access coalescence is critical for maximizing effective memory bandwidth [77]. In most cases, assigning multiple thread blocks to an SM is an effective approach for overlapping memory accesses with computation, because the SM has more data-independent resident warps to switch while waiting for data to be fetched from off-chip memory. Thus, if we maximize the occupancy, or ratio of the number of resident thread blocks to the maximum number of resident thread blocks, we can hide memory access latencies with computation. In other words, fewer resident thread blocks expose memory latency.

Each thread can also independently access memory in the SIMT model, which means the data can be loaded and stored non-contiguously. Although each thread is free to branch and execute independently, the threads can be stalled for reasons like data fetching latency. As we previously mentioned, the memory access has a tremendous impact on program performance. If the memory access requests from a warp have stride larger than the memory segment limit (*e.g.* 128 bytes in recent GPU memory system), those requests need to be severed by several memory transactions which degrade the performance. The best case is that the memory access stride is small enough to be severed with only one transaction, which is called memory coalescing. Despite memory coalescing, a lot of other factors like cache hit rate and shared memory bank conflicts also influence the performance significantly.

## 1.3 Challenges in Heterogeneous Computing Architectures

There are a few major challenges that hinder applications to fully benefit from emerging new computing architectures. First, more layers of the memory hierarchy in new architecture complicate programming, migration, and optimization. Heterogeneous architectures make the situation even worse. Tuning the granularity of tasks, the locality of data, coordination, and synchronization for those system imposes a tremendous burden on researchers.

Second, communication across distinct memory hierarchies or networks often constitutes a performance bottleneck [18, 37] due to the increasing gap between arithmetic and communication performance [15]. Supercomputers now have more than millions of computing cores. The spent time for communication between those cores usually dominates the overall processing time for large scale data. The methodology for algorithm design has shifted from reducing the computational cost to reducing the communication cost [15, 30, 113].

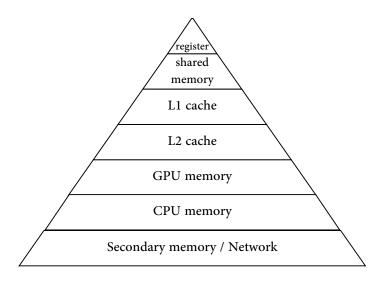

Figure 1.2 illustrates the memory hierarchy in a heterogeneous computing architecture with GPUs. The capacity of each layer in Fig. 1.2 is normally more than  $10 \times$  larger than its upper layer. However, the access speed will also decrease to less than 1/10 for accessing the lower layer with a larger capacity.

In this work, the GPU is regarded as the computing core, and the data is stored outof GPU memory and brought into GPU memory to be processed. Out-of-core data access here involves CPU-GPU data transfer in our target CPU-GPU system, where by contrast, in-core data can be rapidly accessed without additional CPU-GPU data transfer. Currently,

Figure 1.2: Illustration of the memory hierarchy in a heterogeneous computing architecture with GPUs.

the in-core data access speed for GPU has reached 900 GB/s (V100 GPU). Comparatively, the PCIe 3.0 interface for CPU-GPU data transfer has a theoretical maximum bandwidth of 15.75 GB/s. This large performance gap renders the out-of-core data transfer to be the bottleneck of accelerating applications with a large data set.

#### 1.4 Contributions of This Thesis

The contributions of this thesis are divided into three parts:

In the first part, we look into an application called cone beam CT reconstruction. We analyze the bottleneck of accelerating cone beam CT reconstruction on the GPU. We propose a cache-aware optimization method to maximize the usage of the cache mechanism on GPUs.

In the second part, we investigate a randomized matrix decomposition algorithm called randomized singular value decomposition (RSVD). We focus on accelerating RSVD on GPUs. We use a roofline model [111] to show that the theoretical peak performance is bounded by CPU-GPU data transfer. We then propose out-of-core methods that reduce data transfer especially for tall-skinny matrices. Our methods do not modify the original algorithm.

In the third part, we propose an algorithm which is called Block Randomized Singular Value Decomposition (BRSVD). BRSVD is based on the original RSVD algorithm and is modified to fit for the heterogeneous computing environment with GPUs. The out-of-core methods proposed in the second part loose the constraint of CPU-GPU bandwidth, but the bandwidth remains the performance bottleneck. BRSVD successfully moves the performance bottleneck from CPU-GPU bandwidth bound to performance bound at the expense of slightly reducing the accuracy of the original algorithm.

## Chapter 2

# Cache-Aware GPU Optimization for Out-of-Core Cone Beam CT Reconstruction of High-Resolution Volumes

### 2.1 Introduction

CT reconstruction is a radiology imaging technology that converts two-dimensional X-ray projection images generated by a rotary CT scanner into a three-dimensional (3D) volume, such that CT data can be viewed using 3D visualization software. The FDK algorithm [26] is the de facto standard for cone beam CT reconstruction and is widely adopted in medical and industrial applications [24, 53, 62]. Because reconstruction time is critical, especially for real-time medical applications such as image-guided surgery [90, 108], research activities on accelerating the FDK algorithm have been ongoing ever since its advent in 1984.

With the development of parallel computing and computer graphics technologies, efforts to parallelize the FDK algorithm have included various computing devices, including a GPU [112, 117], a cell broadband engine (CBE) [52], a field-programmable gate array (FPGA) [29] and a Xeon Phi coprocessor [43]. CBE has eight synergistic processing elements (SPEs) allow for a theoretical performance of 192 Gflop/s. Data mining techniques and double buffering of input data were extensively used to optimally utilize both the memory bandwidth and the available local store of each SPE. The pixel-driven back-projection code uses floating point arithmetic and either inear interpolation or nearest neighbor interpolation between neighboring detector channels. For FPGA implementation, Gac *et al.* proposed a prediction algorithm to prefetch the data needed into cache so as to increase the spatial and temporal localities [29].

In particular, utilizing CUDA, compatible with GPUs [77], to parallelize FDK computation has gained popularity due to its high performance and low-cost implementation as compared to other devices [24, 46, 91]. Given this parallelization technique, the performance bottleneck of the FDK algorithm lies in its back-projection of projection images in which interpolated pixel values are accumulated back to form voxel values, which then compose the 3D volume. Therefore, typical implementations store projection images in *textures* to take advantage of hardware-accelerated interpolation available on the GPU.

In addition to this fundamental implementation scheme, Okitsu *et al.* [82] presented a multiplication method that back-projects multiple projections with a single kernel invocation. This multiplication method accelerates the back-projection procedure by reducing the number of off-chip memory accesses. In [82], Okitsu et al. concluded that GPU memory bandwidth (*i.e.*, the memory bandwidth between SMs [77] and off-chip memory) determines reconstruction throughput on a GeForce 8800 GTX GPU. The FDK has long been proved to be a memory-bound application on parallel computers. A performance model [45] is normally used to indicate the implementation efficiency on a specific hardware. The model is given  $E = 4\rho/B$ , where B is the total memory bandwidth of the deployed machine,  $\rho$  is the backprojection throughput. Okitsu et al. emphasized memory coalescing to improve the overall performance, because the GPU memory bandwith was the bottleneck on the deployed G80 architecture [69] and the cache capacity was too small to impact on the overall performance. Therefore, in this chapter, we propose a cache-aware optimization method [61] to accelerate the FDK algorithm for handling out-of-core data on a GPU. To our knowledge, no work has been done in modeling the GPU cache performance. The reason is that the cache hit rate varies greatly with different applications. Also, the cache is transparent to the programmer, which means that the programmer has no direct control over the data movement. Regarding the general purpose modeling of the GPU memory, latency, and bandwidth, several works has been done. Those works do not take the cache into their models. For example, Nakano has proposed asynchronous memory machine model for GPU computing [67]. They applied the model in analyzing several applications like interval sum and prefix-summing. However, the proposed model is not cache-aware.

In this chapter, we extends Okitsu's method [82] by increasing the cache hit rate, thereby improving out-of-core cone beam CT reconstruction. The proposed method consists of the following three key strategies: (1) a loop organization strategy which identifies the best trade-off point between the cache hit rate and the number of off-chip memory accesses; (2) a data structure that exploits high locality within a layered texture; and (3) a fully pipelined strategy for hiding file I/O times with GPU execution and data transfer times. We analyze the underlying mechanism of these strategies and provide tuning guidelines for adjusting the execution parameters, which include the granularity and shape of thread blocks [77] and the granularity of I/O data to be streamed through the pipeline, the latter maximizing reconstruction performance on NVIDIA's latest Maxwell architecture [71].

The rest of this chapter is organized as follows. In Section 2.2 we introduce related studies regarding the acceleration of cone beam CT reconstruction. In Section 2.3 we summarize the FDK algorithm and its previous GPU-based implementation [82]. In Section 2.4, we describe our proposed method, and then present our experimental results in Section 2.5 along with discussion on tuning for the Maxwell architecture. Finally, in Section 2.6, we conclude our chapter and suggest avenues for future work.

#### 2.2 Related Work

Table 2.1 shows a comparison of our present work with recent studies, showing the advantages of our proposed method. In the table, the back-projection throughput  $\rho$  is presented in giga voxel updates per second (GUPS), where giga denotes 10<sup>9</sup>. In summary, our present work employs a single-GPU machine to achieve high back-projection throughput for large amounts of data that exceed not only GPU memory but also CPU memory. Further, we incorporate optimization method based on NVIDIA's Maxwell architecture [71].

To our knowledge, Scherl *et al.* [91] first proposed the use of a CUDA-based GPU to accelerate the FDK algorithm, claiming that reducing register file usage raised GPU occupancy [77] so as to accelerate reconstruction. They demonstrated that a GeForce 8800 GTX GPU achieved two times higher reconstruction performance as compared to a CBE. A similar CUDA-based approach with similar results was presented by Noël *et al.* [68].

As for kernel optimization, Okitsu *et al.* [82] extended Xu's method [112], who first proposed back-projecting multiple projections in a single kernel invocation. These multiplication schemes reduced the number of off-chip memory accesses and that of kernel invocations. They concluded that GPU memory bandwidth determines reconstruction performance; thus, the back-projection kernel should process more projections at a time. A similar scheme was presented by Papenhausen *et al.* [85], who processed 64 projections with a single kernel execution. In contrast to the above studies, we show that excessive projections result in a lower texture cache hit rate on the latest Maxwell architecture [71]. Consequently, it is important to find the best trade-off point between texture cache hit rate and the number of off-chip memory accesses.

Based on Okitsu's multiplication method [82], Zinßer *et al.* [123] swapped the nested loop structure proposed in [82] such that threads that share the same instruction can simultaneously access a single projection. Zinßer *et al.* claimed that their loop organization not only increased the texture cache hit rate but also reduced the number of off-chip memory accesses by processing 32 projections with a single kernel invocation. A key drawback of their loop organization is that it consumes more registers than the original organization. Consequently, only four xy-slices of the volume were produced by a kernel invocation, whereas the original organization produced 512 xy-slices at a time. This consumption issue must be resolved for large amounts of data, which we focus on in the present study, because 128 times more kernel invocations are required to produce the entire volume. In our work, we present a data structure capable of achieving an L1/texture cache hit rate of more than 95%, even with the original loop organization.

In contrast to the input-related optimization mentioned above, Zheng *et al.* [122] presented a cache-aware method capable of maximizing write throughput for the output volume. Their method rearranges volume data according to the back-projection angle such that a series of memory transactions can be coalesced into a single transaction. Since this data rearrangement incurs overhead, they allocated another copy of the volume to avoid rearrangement overhead; however, such duplicated data must be eliminated to handle large amounts of data on limited GPU memory. Our method realizes memory access coalescence by adopting a workload distribution scheme in which threads are responsible for angle-independent regions of the volume.

With respect to out-of-core reconstruction in which I/O data flow exceed GPU memory,

**Table 2.1:** Comparison of the performance of our work with relevant recent works. Note that backprojection throughput  $\rho$  which is measured in GUPS, is given by  $\rho = NXYZ/T$ , where N is the number of projections,  $X \times Y \times Z$  is the volume size in voxels, and T is the back-projection time, which includes data transfer times between CPU and GPU. Further, U and V are the horizontal and vertical sizes of a projection, respectively. Note that efficient cache utilization achieves an efficiency of more than 100%.

| Work                    | Platform                      | Memory spe         | cification      | Data specification                                | 1                       | Throughput    | Efficiency |

|-------------------------|-------------------------------|--------------------|-----------------|---------------------------------------------------|-------------------------|---------------|------------|

|                         |                               | Bandwidth $(GB/s)$ | Capacity (GB)   | $NUV \rightarrow XYZ$                             | Size (GB)               | $\rho$ (GUPS) | E(%)       |

| Scherl (2007) [91]      | 8800 GTX                      | 86.4               | 0.8             | $414 \times 1024 \times 1024 \rightarrow 512^3$   | $1.6 \rightarrow 0.5$   | 6.2           | 29         |

| Okitsu (2010) [82]      | $2 \times \text{Tesla C870}$  | $2 \times 76.8$    | $2 \times 1.5$  | $1024\times 1024\times 1024 \rightarrow 1024^3$   | $4.0 \rightarrow 4.0$   | 48.9          | 127        |

| Ino (2010) [45]         | $4 \times \text{Tesla S1070}$ | $4 \times 102.0$   | $4 \times 4.0$  | $2048\times 2048\times 2048\to 2048^3$            | $32.0 \rightarrow 32.0$ | 105.7         | 104        |

| Noël (2010) [68]        | GTX 280                       | 141.7              | 1.0             | $106 \times 1024 \times 1024 \rightarrow 512^3$   | $0.4 \rightarrow 0.5$   | 2.3           | 6          |

| Zheng (2010) [122]      | GTX 480                       | 177.4              | 1.5             | $364 \times 1024 \times 768 \rightarrow 512^3$    | $1.1 \rightarrow 0.5$   | 12.0          | 27         |

| Zhang (2012) [120]      | $2 \times \text{GTS} 450$     | $2 \times 57.7$    | $2 \times 1.0$  | $360 \times 1024 \times 1024 \rightarrow 512^3$   | $1.4 \rightarrow 0.5$   | 11.1          | 38         |

| Treibig (2013) [100]    | $4 \times Xeon E7-4870$       | $4 \times 34.2$    | N/A             | $496 \times 1248 \times 960 \rightarrow 1024^3$   | $2.2 \rightarrow 4.0$   | 12.0          | 35         |

| Papenhausen (2013) [85] | GTX 680                       | 192.3              | 2.0             | $496 \times 1248 \times 960 \rightarrow 512^3$    | $2.2 \rightarrow 0.5$   | 72.3          | 150        |

| Zinßer (2013) [123]     | GTX 680                       | 192.3              | 2.0             | $496 \times 1248 \times 960 \rightarrow 1024^3$   | $2.2 \rightarrow 4.0$   | 88.2          | 183        |

| Blas (2014) [9]         | $2 \times GTX 680$            | $2 \times 192.3$   | $2 \times 2.0$  | $720\times 1024\times 1024 \rightarrow 1024^3$    | $2.8 \rightarrow 4.0$   | 117.5         | 122        |

| Serrano (2014) [92]     | 2×GTX 680                     | $2 \times 192.3$   | $2 \times 2.0$  | $360 \times 512 \times 512 \rightarrow 512^3$     | $0.4 \rightarrow 0.5$   | 27.1          | 28         |

|                         | $2 \times Xeon$ Phi 7120P     | $2 \times 352.0$   | $2 \times 16.0$ | $360 \times 512 \times 512 \rightarrow 512^3$     | $0.4 \rightarrow 0.5$   | 26.7          | 15         |

| This work (2016)        | GTX 980                       | 224.0              | 4.0             | $1200 \times 512 \times 512 \rightarrow 512^3$    | $1.2 \rightarrow 0.5$   | 116.7         | 208        |

|                         |                               |                    |                 | $1200\times 1024\times 1024 \rightarrow 1024^3$   | $4.7 \rightarrow 4.0$   | 128.5         | 229        |

|                         |                               |                    |                 | $1200 \times 2048 \times 2048 \rightarrow 2048^3$ | $18.8 \rightarrow 32.0$ | 92.9          | 166        |

several studies have explored a multi-GPU machine to achieve further acceleration [9, 45, 120]. Existing multi-GPU implementations adopt a pipelined approach to overlap kernel execution with data transfer between CPU and GPU; however, except for Blas *et al.* [9], file I/O overhead has not been considered in detail. Blas *et al.* [9] did indeed consider file I/O overhead, thus realizing on-the-fly reconstruction, which produces the volume immediately after image acquisition; however, cache optimization issues were not addressed. Our out-of-core pipelined strategy yields a fully pipelined cache-aware solution for processing large amounts of data on a single-GPU system. Further, although we evaluated the advantages of our method on a single-GPU machine, our method can be expanded to support a multi-GPU environment in a straightforward manner.

On the other hand, Serrano *et al.* [92] proposed using a directive-based programming approach [83] to parallelize the FDK algorithm on GPUs and Intel Xeon Phi coprocessors. Compared with CUDA, this directive-based approach provides an easy programming scheme in which parallelization is achieved by adding compiler directives to sequential code; however, using such a high-level programming style degrades the performance. Due to the same performance related reason, we prefer CUDA rather than OpenCL [56].

Finally, Treibig *et al.* [100] explored optimizing the AVX instruction set [47]. They indicated that GPU-based solutions degrade reconstruction throughput for large amounts of data, because limited GPU memory requires data transfers between CPU and GPU. Our pipelined solution overlaps these required data transfers with GPU computation, thereby achieving higher out-of-core reconstruction performance as compared to CPU-based approaches (Table 2.1).

#### 2.3 Preliminaries