| Title        | Studies on Thermal Design Evaluation Method of<br>SiC Power Module |

|--------------|--------------------------------------------------------------------|

| Author(s)    | 福永, 崇平                                                             |

| Citation     | 大阪大学, 2020, 博士論文                                                   |

| Version Type | VoR                                                                |

| URL          | https://doi.org/10.18910/77495                                     |

| rights       |                                                                    |

| Note         |                                                                    |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

## Doctoral Dissertation

### Studies on Thermal Design Evaluation Method of SiC Power Module

SiCパワーモジュールの熱設計評価法に関する 研究

## Shuhei Fukunaga

June 2020

Division of Electrical, Electronic and Information Engineering Graduate School of Engineering

Osaka University

## Abstract

Fast switching operation of SiC unipolar power devices enables to make more efficient and to miniaturize power conversion systems, which achieves a high power density power conversion system. High di/dt in fast switching operation, however, induces a switching surge voltage associated with the parasitic inductance in the circuit wiring, then it is required to minimize the parasitic inductance with maintaining the circuit topology. Thermal design is another key factor for the safety and reliable operation of high power density circuits. Then, thermal characteristics of power module packages should be evaluated for thermal management of power conversion systems.

The objective of this research is the development of thermal design evaluation methods for power module packages to realize a high power density SiC power conversion system. This thesis develops an algorithm to accurately identify the transient thermal network model of power module packages. And this thesis proposes a modified static test method to evaluate transient thermal characteristics of power module packages with SiC MOSFETs. The significant parameters to improve heat spreading performance of SiC power modules are revealed using the developed transient thermal network model identification method in order to design transient thermal characteristics of SiC power modules.

This thesis consists of the following six chapters. Chapter 1 is the introduction. The background and objective of this research are introduced. The problems to achieve a high power density power conversion system with SiC power devices are also explained in this chapter.

Chapter 2 treats fundamentals of SiC power devices and power modules. Electrical characteristics and its temperature dependency of SiC SBD and SiC MOSFET are derived in section 2.2. Recent and next generation structure and technology of power

module package are described in section 2.3. Section 2.3 also shows the developed multi-layered ceramic substrate in this study and evaluates the parasitic inductance of the developed SiC power module using the multi-layered ceramic substrate.

Chapter 3 develops a signal processing algorithm to identify the accurate transient thermal network model for power module packages. The conventional algorithm for identifying the transient thermal network model has difficulty in eliminating noise on the measured result. The modified algorithm for identifying the transient thermal network model is explained and performs some numerical validations for a known numerical model in the frequency domain. Moreover, the developed algorithm is experimentally validated for a discrete power device and power module with an active metal bonding (AMB) substrate.

Chapter 4 proposes a junction temperature  $(T_J)$  estimation method for SiC MOS-FETs in the transient thermal characterization. SiC MOSFET has still concern about the dynamic gate threshold voltage shift due to the trap in the oxide/semiconductor interface, which violates the estimated time response of  $T_J$ . The proposed method, which advances the conventional static test method, is performed and validated using the embedded temperature sense diode on SiC MOSFET. The time response of  $T_J$  is also evaluated for the developed SiC MOSFET with built-in Schottky barrier diode (SBD) named as SWITCH-MOS.

Chapter 5 evaluates the thermal design of SiC power module substrates for various types of module constitutions using the transient thermal network model. Finite volume method (FVM) simulation is performed to evaluate the validity of obtained transient thermal characteristics. Section 5.3 and 5.4 reveal the significant parameters for improving transient thermal characteristics of power module packages based on an AMB substrate.

Conclusions, industrial impacts and suggestions of future work are provided in Chapter 6.

## Acknowledgement

First of all, I would like to express my most sincere gratitude to Professor Tsuyoshi Funaki at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University. He has provided me the great opportunity to accomplish this work, insightful suggestions, and ceaseless encouragement through fruitful discussions.

I would like to acknowledge Professor Tomoo Ushio and Professor Shigemasa Takai at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University for their careful review on my thesis and valuable suggestions. I would also like to acknowledge Professor Masahide Hojo at Graduate School of Advanced Technology and Science, Tokushima University for his careful review on my thesis and valuable suggestions. And I would like to thank Professor Hiroyuki Shiraga at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University for his useful comments.

I sincerely thank Associate Professor Hideharu Sugihara and Assistant Professor Takaaki Ibuchi at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University for a great deal of their insightful comments and useful suggestions. I am thankful for kind advice of Specially Appointed Professor Takashi Nakamura and Guest Professor Shigekazu Sakabe at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University.

I would like to thank Mr. Tomoaki Hara at Siemens Japan for his kind instruction and invaluable advice. I am deeply grateful to Dr. Kunihiro Sakamoto, Dr. Hiroshi Sato and Dr. Fumiki Kato at National Institute of Advanced Industrial Science and Technology (AIST) for a great deal of their insightful comments and valuable discussion.

My deep acknowledgments also go to thank all members of Funaki Laboratory for kindness and support. I am deeply grateful to Mr. Hiroshi Kinemura for kind instruction, meaningful comments and valuable discussion. My special thanks to Ms. Fumie Imura, secretary in Funaki laboratory, for kindly supporting my daily work. And I wish to thank my colleagues Mr. Tomohiro Ozaki, Mr. Eisuke Masuda, Mr. Ken Inoue, and Mr. Hiroyuki Iwasa for my wonderful work.

This work was partially supported by Waseda University Graduate Program for Power Energy Professionals (PEP). And this work was partially supported by a Grantin-Aid for Japan Society for the Promotion of Science (JSPS) Fellows (DC2). This work has been partially implemented under a joint research project of Tsukuba Power Electronics Constellations (TPEC).

Finally, I deeply thank my parents, and all of my friends for their understanding, continuous support, and heartfelt encouragement.

Shuhei FUKUNAGA Osaka, June 2020

## Contents

| A        | Abstract         |                                                                        |    |  |  |  |  |  |  |  |

|----------|------------------|------------------------------------------------------------------------|----|--|--|--|--|--|--|--|

| A        | Acknowledgement  |                                                                        |    |  |  |  |  |  |  |  |

| Co       | onter            | nts                                                                    | v  |  |  |  |  |  |  |  |

| 1        | Intr             | roduction                                                              |    |  |  |  |  |  |  |  |

|          | 1.1              | Background                                                             | 1  |  |  |  |  |  |  |  |

|          | 1.2              | Problems in realizing high power density SiC power conversion system . | 4  |  |  |  |  |  |  |  |

|          | 1.3              | Purpose and outline of this thesis                                     | 5  |  |  |  |  |  |  |  |

| <b>2</b> | $\mathbf{SiC}$   | power device and its module packages                                   | 7  |  |  |  |  |  |  |  |

|          | 2.1              | Introduction                                                           | 7  |  |  |  |  |  |  |  |

|          | 2.2              | SiC power device                                                       | 7  |  |  |  |  |  |  |  |

|          |                  | 2.2.1 SiC SBD                                                          | 8  |  |  |  |  |  |  |  |

|          |                  | 2.2.2 SiC MOSFET                                                       | 11 |  |  |  |  |  |  |  |

|          |                  | 2.2.3 SWITCH-MOS                                                       | 16 |  |  |  |  |  |  |  |

|          |                  | 2.2.4 Temperature sensitive electrical parameter of SiC power device . | 18 |  |  |  |  |  |  |  |

|          | 2.3              | SiC power module                                                       | 20 |  |  |  |  |  |  |  |

|          |                  | 2.3.1 Typical power module constitution                                | 22 |  |  |  |  |  |  |  |

|          |                  | 2.3.2 Developed multi-layered ceramic substrate for power module       | 24 |  |  |  |  |  |  |  |

|          | 2.4              | Summary                                                                | 26 |  |  |  |  |  |  |  |

| 3        | Tra              | nsient thermal network model identification for power module           |    |  |  |  |  |  |  |  |

|          | pac              | kages                                                                  | 29 |  |  |  |  |  |  |  |

|          | 3.1 Introduction |                                                                        |    |  |  |  |  |  |  |  |

| 5 | 4.4<br><b>The</b><br>5.1 | ermal o | aryary                                                                                                | 59<br><b>61</b><br>61 |

|---|--------------------------|---------|-------------------------------------------------------------------------------------------------------|-----------------------|

|   | 4.4                      | Summ    | ary                                                                                                   | 59                    |

|   |                          | C       |                                                                                                       | -                     |

|   |                          |         | temperature $\ldots$ | 57                    |

|   |                          | 4.3.2   | Comparative evaluation of estimated time response of junction                                         |                       |

|   |                          | 4.3.1   | Studied SWITCH-MOS and measurement setup                                                              | 55                    |

|   | 4.3                      |         | on temperature estimation for SWITCH-MOS                                                              | 55                    |

|   |                          |         | with TSD                                                                                              | 52                    |

|   |                          | 4.2.3   | Evaluation of estimated time response of junction temperature                                         |                       |

|   |                          | 4.2.2   | Studied power module                                                                                  | 51                    |

|   |                          | 4.2.1   | Dynamic thermal characterization setup for MOSFET                                                     | 49                    |

|   |                          | MOSE    | ΈΤ                                                                                                    | 49                    |

|   | 4.2                      | Evalua  | ation of modified junction temperature estimation method for SiC                                      |                       |

|   | 4.1                      | Introd  | uction                                                                                                | 48                    |

| 4 | Dyr                      | namic j | junction temperature estimation method for SiC MOSFET                                                 | 48                    |

|   | 3.5                      | Summ    | ary                                                                                                   | 46                    |

|   | 0 5                      | C       | module package                                                                                        | 44                    |

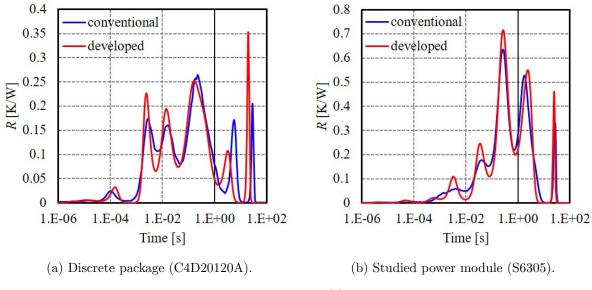

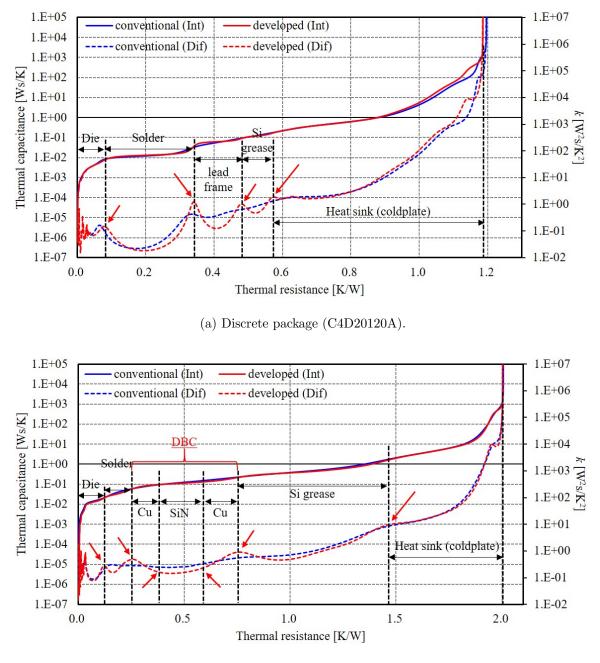

|   |                          | 3.4.3   | Experimental validation for discrete power device and power                                           |                       |

|   |                          |         | signal                                                                                                | 42                    |

|   |                          | 3.4.2   | Evaluation of robustness for the noise superimposed on the ideal                                      |                       |

|   |                          | 3.4.1   | Quantization error                                                                                    | 39                    |

|   |                          |         | using the developed algorithm                                                                         | 38                    |

|   | 3.4                      | Impro   | vement of accuracy for the identified transient thermal network                                       |                       |

|   |                          | 3.3.3   | Bayesian deconvolution                                                                                | 38                    |

|   |                          | 3.3.2   | Noise reduction using weighted discrete Fourier transformation .                                      | 36                    |

|   |                          | 3.3.1   | Transformation of time domain from linear to logarithmic $\ldots$                                     | 35                    |

|   | 3.3                      | Signal  | processing algorithm in logarithmic time domain $\ldots \ldots \ldots$                                | 34                    |

|   |                          | 3.2.2   | Foster thermal network model identification by deconvolution $% \mathcal{A}(\mathcal{A})$ .           | 32                    |

|   |                          | 3.2.1   | Structure function related to transient thermal networks $\ . \ . \ .$                                | 30                    |

|   | 3.2                      | Transı  | ent thermal network model of power module packages                                                    | 30                    |

|    | 5.2    | 2 Numerical modeling for transient thermal characterization of power mod- |                                                                       |      |  |  |  |

|----|--------|---------------------------------------------------------------------------|-----------------------------------------------------------------------|------|--|--|--|

|    |        | ule pa                                                                    | ckage                                                                 | 62   |  |  |  |

|    |        | 5.2.1                                                                     | Finite volume equation                                                | 63   |  |  |  |

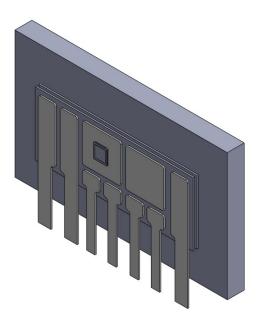

|    |        | 5.2.2                                                                     | Simulation model                                                      | 65   |  |  |  |

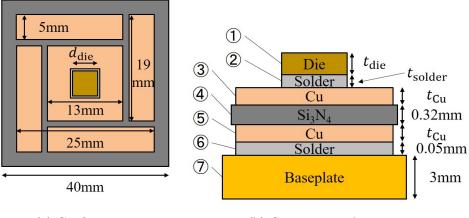

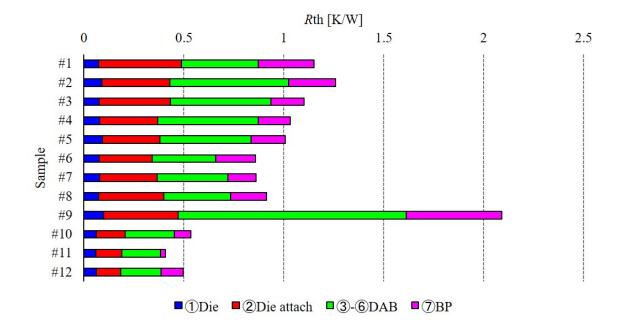

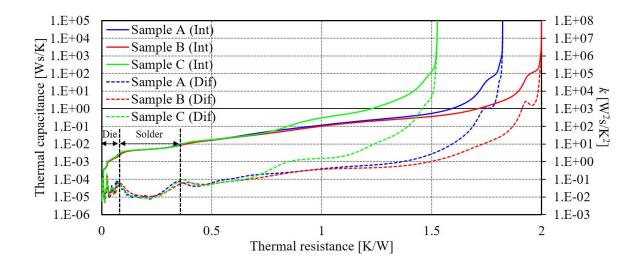

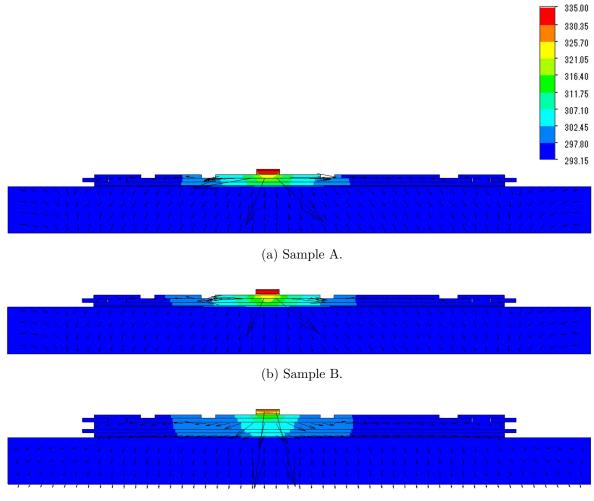

|    | 5.3    | Param                                                                     | etric study of transient thermal characteristics for SiC power module | e 65 |  |  |  |

|    |        | 5.3.1                                                                     | Studied power module constitution                                     | 65   |  |  |  |

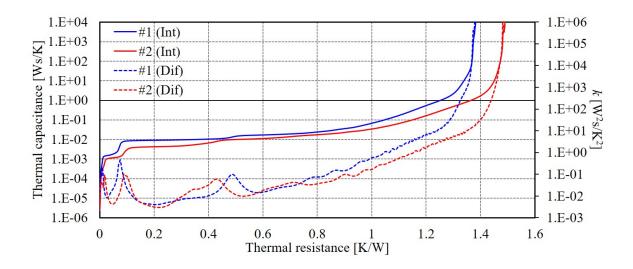

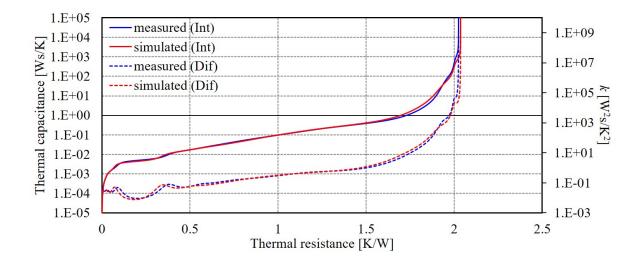

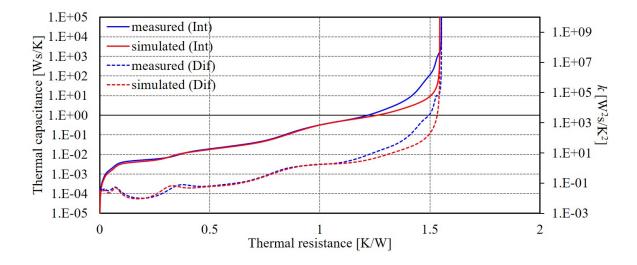

|    |        | 5.3.2                                                                     | Experimental evaluation of transient thermal network model            | 69   |  |  |  |

|    | 5.4    | Therm                                                                     | al design evaluation of the developed multi-layered ceramic sub-      |      |  |  |  |

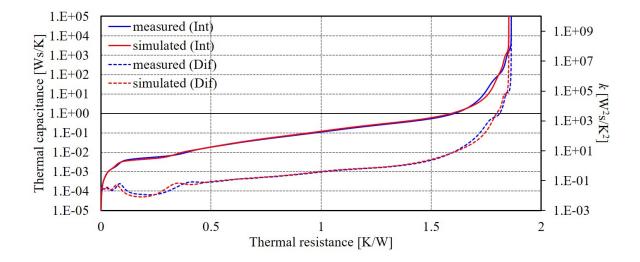

|    |        | strate                                                                    |                                                                       | 78   |  |  |  |

|    |        | 5.4.1                                                                     | Specification of studied power module constitution                    | 78   |  |  |  |

|    |        | 5.4.2                                                                     | Experimental results                                                  | 78   |  |  |  |

|    |        | 5.4.3                                                                     | Simulation results                                                    | 80   |  |  |  |

|    | 5.5    | Summ                                                                      | ary                                                                   | 80   |  |  |  |

| 6  | Con    | clusio                                                                    | 18                                                                    | 85   |  |  |  |

|    | 6.1    | Conclu                                                                    | isions                                                                | 85   |  |  |  |

|    | 6.2    | Indust                                                                    | rial impacts                                                          | 87   |  |  |  |

|    | 6.3    | Future                                                                    | e outlooks                                                            | 88   |  |  |  |

| Re | eferei | nces                                                                      |                                                                       | 90   |  |  |  |

| Pι | ıblica | blications 100                                                            |                                                                       |      |  |  |  |

## Chapter 1

## Introduction

### 1.1 Background

Electrical power is generated and consumed in a variety of voltage and current levels in modern society. Power electronics, which was defined by W. E. Newell in 1974 [1], is a key technology to efficiently use a electrical power by changing voltage and current amplitude and/or frequency using power conversion systems. Switching operation of power conversion systems is realized by using power semiconductor devices such as power diode, metal-oxide semiconductor field effect transistor (MOSFET), insulated gate bipolar transistor (IGBT), and gate turn off thyristor (GTO). Power conversion systems are widely adopted for industrial application (motor drive, factory automation, data center), renewable energy conversion system (solar, wind, geothermal heat), transportation (hybrid or electrical car, railway, aerospace), home appliance (air conditioner, robot cleaner), and so on.

As extending the adopted field of power conversion systems and increasing amount of consumed electrical power in the world, power conversion systems are required to be more efficient operation and reduce size, weight and cost. Fast switching operation of power conversion systems realizes low switching loss in operation and allows high frequency switching operation. This enables to miniaturize and accomplish a high power density power conversion system. While some breakthroughs have been occurred for developing device structure such as Si super junction (SJ) MOSFET [2], the conventional Si-based power semiconductor device is approaching to the theoretical limitation, which is derived from the physical property of Si and its device structures.

Wide bandgap (WBG) semiconductor materials such as silicon carbide (SiC) and gallium nitride (GaN) attract attention as next generation power semiconductor devices [3]-[10]. Table 1.1 lists the major physical properties of WBG and conventional semiconductor materials for power semiconductor devices. Here, Baliga figure of merit (BFOM) shows the performance index of conduction loss assuming the specific on-state resistance of power MOSFET at low switching frequency operation [11]. Reference [12] is adopted for high frequency operation of power conversion systems, which considers switching loss of each switching transient. As shown in Table 1.1, WBG semiconductor materials are superior to the conventional Si semiconductor in terms of wide bandgap, high critical breakdown, high electron mobility and thermal stability. These features accomplish the high breakdown voltage unipolar power device with low on resistance, fast switching and high temperature operation capability.

|                                                                 | Si   | GaAs | 4H-SiC | GaN  | Diamond |

|-----------------------------------------------------------------|------|------|--------|------|---------|

| Bandgap $E_{\rm G}$ [eV]                                        | 1.12 | 1.43 | 3.26   | 3.39 | 5.47    |

| Breakdown electric field $E_{\rm c}~[{\rm MV/cm}]$              | 0.3  | 0.4  | 3.0    | 3.3  | 10.0    |

| Electron mobility $\mu_{\rm e}  [{\rm cm}^2/{\rm Vs}]$          | 1400 | 8500 | 1000   | 900  | 2200    |

| Saturated electron mobility $v \text{ [cm/s]}$                  | 1.0  | 2.0  | 2.2    | 2.7  | 2.7     |

| Thermal conductivity $\lambda ~[W/cm/K]$                        | 1.5  | 0.5  | 4.9    | 2.0  | 20.0    |

| Relative dielectric constant $\varepsilon$                      | 11.8 | 12.8 | 9.7    | 9.0  | 5.5     |

| $\mathrm{BFOM}(=\varepsilon\mu_{\mathrm{e}}E_{\mathrm{G}}^{3})$ | 1    | 13.7 | 14.5   | 13.6 | 85.3    |

Table 1.1

Physical properties of WBG and conventional semiconductor materials

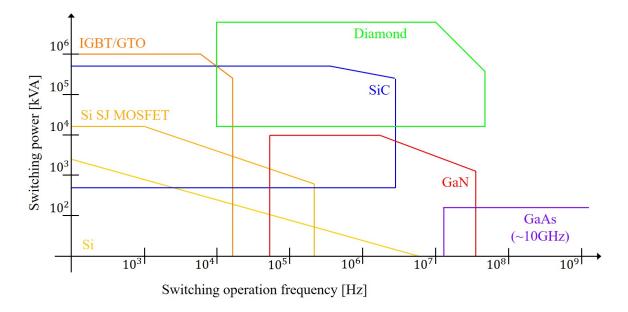

Fig. 1.1 shows the major territories of WBG and conventional power semiconductor devices for a variety of applications. GaN power semiconductor devices have the equal or better potential than SiC power semiconductor devices [13]. But it is difficult to fabricate insulation layer like Si, thus they are expected to adopt a small or middle power and high switching frequency operation application using the lateral structure such as high electron mobility transistor (HEMT) [14] [15]. Wireless power transfer (WPT) applications over MHz switching frequency using GaN power semiconductor devices were already reported [16]-[18]. Reference [19] developed high switching frequency gate driver using GaN HEMT to operate synchronous DC-DC converter at 10MHz. Diamond is the most promising material as power semiconductor devices, and some Schottky barrier diodes (SBD) and MOSFETs have been enthusiastically studied [20]-[23]. But since doping on pure diamond crystal is difficult due to its wide bandgap, a practical rated power device is still not realized. In regard to SiC power semiconductor devices, SiC crystal growth had break through by epitaxial growth method in Japan [24]. And the vertical SiC power devices like MOSFET and IGBT are easily fabricated using SiC single crystal because SiC can be thermally oxidized in the same manner as silicon and SiO<sub>2</sub> forms a native passivation layer on SiC crystal [25]. Moreover, SiC power semiconductor devices can operate over 300 °C due to its wide bandgap and high thermal conductivity [26] [27]. Thus SiC power semiconductor devices are expected to adopt for high power rated applications. Researchers have reported many application using SiC power semiconductor devices [28]-[31], and some are already commercialized.

Figure 1.1 Major territories of power semiconductor devices.

## 1.2 Problems in realizing high power density SiC power conversion system

Passive components such as inductor and capacitor dominate the size and weight of power conversion systems. High frequency switching operation using high speed switching with SiC unipolar power devices allows to use the less inductance and capacitance in power conversion systems. High di/dt and dv/dt in fast switching, however, induce large switching surge voltage and current with the parasitic components in the circuit. This leads to failure operation or high frequency electromagnetic interference (EMI) noise problem of power conversion systems. References [32] and [33] analyzed self turn-on phenomena induced by the high switching speed. Modeling and visualization of noise source and path have been conducted to achieve electromagnetic compatibility (EMC) design [34] [35]. Modularization of power semiconductor devices and miniaturization of power conversion systems are one way of reducing parasitic components. Designing power module structure is effective to reduce parasitic components [36]-[39]. Reference [40] reported the design method of the parasitic inductance and capacitance in laminated busbars, which connects power module to power conversion system. On the other hand, miniaturization increases heat dissipation per unit area/volume and thermal interference effect among components in the module and/or circuit. These problems make thermal management difficult and concern about long-term reliability in actual operation. Therefore, thermal design is a key factor for miniaturization of power conversion systems to maximize SiC power semiconductor device capability.

Thermal design of power module aims at spreading and transferring heat dissipated in the power semiconductor device. Heat spreading and transferring mainly depends on the structure and material property of power module constitutions. The conventional static thermal resistance model evaluates the temperature difference between junction to case of power modules in steady-state operation. However, a transient thermal network model represented by thermal resistance and thermal capacitance is needed to estimate the time response of junction temperature  $(T_J)$  in over or fault current condition [41]-[53]. References [46] and [47] assessed the dynamic thermal coupling effect for multi-chip power module packages. References [48]-[52] identified a transient thermal network model in the frequency domain using Fourier series expansion. Frequency domain modeling is also conducted for several thermal circuit models in reference [53]. Static test method [54] is the standard method for identifying the transient thermal network model of power module packages. This method estimates  $T_{\rm J}$  by the temperature dependency in I - V characteristics of power semiconductor devices in power modules.

Reference [54] performs some numerical calculations such as deconvolution calculation to identify the transient thermal network model from the time response of  $T_{\rm J}$ in cooling operation from thermal equilibrium in self heated condition. The precise numerical calculation procedure to identify the transient thermal network model is not clearly addressed in [54]. And the conventional model identification algorithm has difficulty in eliminating the influence of noise in the measured signal. An additional filtering or another signal processing algorithm is necessary in order to achieve higher noise reduction capability for identifying the accurate transient thermal network model from the estimated time response of  $T_{\rm J}$ .

Other problem is that SiC MOSFET has difficulty of the gate threshold voltage shift due to the carrier traps in the level of gate oxide or interface [55]. The static gate threshold voltage shift has been improved, but the dynamic gate threshold voltage shift, for example negative bias temperature instability (NBTI) problem [56] [57], still remains great concern. The latter causes an error in  $T_J$  estimation of SiC MOSFETs using its temperature dependency of I - V characteristics [58]. This error makes it difficult to identify the transient thermal network model of power module packages with SiC MOSFETs. Thus new evaluation method for SiC power semiconductor device is necessary.

### **1.3** Purpose and outline of this thesis

This thesis is concerned with developing thermal design evaluation methods of SiC power modules to realize a high power density SiC power conversion system. This research focuses on an algorithm to accurately identify the transient thermal network model of power module packages, and a thermal characterization method for SiC MOS-

FETs without the influence of the dynamic gate threshold voltage shift. This research also evaluates the thermal design of power module substrates for SiC power modules using the developed transient thermal network model identification method.

Chapter 2 treats the structure and property of SiC power semiconductor devices and power modules. The electrical characteristics and its temperature dependency of SiC SBD and SiC MOSFET are derived from solid state physics. Constitutions and its function of power module packages are also explained in this chapter. And the developed SiC power module with a multi-layered ceramic substrate in this study is shown.

Chapter 3 develops an algorithm for identifying the transient thermal network model of SiC power modules using weighted discrete Fourier transformation and noise filtering in frequency domain. The influence of quantization error and noise in the measured signal is evaluated for the simulated time response of  $T_{\rm J}$  with a given transient thermal network model. The accuracy of the identified transient thermal network model for a discrete power device and a power module package is experimentally evaluated.

Chapter 4 proposes an accurate  $T_{\rm J}$  estimation procedure for SiC MOSFETs without the dynamic gate threshold voltage shift, which advances the conventional static test method. The estimated time response of  $T_{\rm J}$  using the proposed procedure is validated with temperature sense diode embedded in SiC MOSFET. And this chapter also evaluates the estimated time response of  $T_{\rm J}$  for the developed SiC MOSFET with built-in SBD, whose  $I_{\rm d} - V_{\rm sd}$  characteristic does not depend on  $V_{\rm gs}$ .

Chapter 5 evaluates the thermal design of SiC power module substrates for varieties of power module constitutions using the developed transient thermal network model. This chapter performs the parametric study of transient thermal characteristics for power module constitution with a single chip module, and obtains the significant parameters to improve transient thermal characteristics of power module. The obtained measured results are validated using the numerical simulation based on finite volume method (FVM).

And chapter 6 summarizes this thesis and suggests industrial impacts and topics for future research work.

## Chapter 2

# SiC power device and its module packages

### 2.1 Introduction

A power module consists of packaged plural power devices. Thus, electrical characteristics and its temperature dependency of power device are very important for analyzing electrical and thermal behavior of power conversion systems. Moreover, power module structure and packaging technology critically affect parasitic components and thermal characteristics of SiC power modules. Section 2.2 explains the structure of some typical SiC power devices and derives its electrical characteristics including temperature dependency from device structure. Section 2.3 explains typical structures and materials of the conventional and next generation power modules. And section 2.3 introduces the developed multi-layered ceramic substrate, and evaluates its electrical characteristics.

### 2.2 SiC power device

SiC is a IV-IV compounded material with unique physical properties. The strong chemical bonding between Si and C atoms gives thermal, chemical and mechanical stability. SiC is the best known example as polytypism such as 3C-, 4H- and 6H-SiC crystal structure and their physical properties are different. In the field of power electronics, 4H-SiC is the most popular material. This is because a high quality 4H-SiC

Figure 2.1 Major territories of Si and SiC power semiconductor devices.

crystal had been obtained by epitaxial growth [24]. Moreover, 4H-SiC has the most high electron mobility compared to other polytypes.

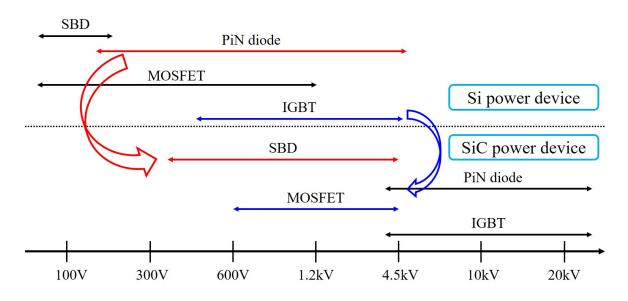

Fig. 2.1 shows the major territories of Si and SiC power devices. In the conventional Si power device, bipolar power device such as PiN diode or insulated gate bipolar transistor (IGBT) is often used in several hundreds to thousands voltage application. Bipolar power device achieves high breakdown voltage and low on-state resistance by conductivity modulation effect. On the other hand, it is difficult to obtain high switching speed because the time to sweep minority carrier needs in the turn-off transient. The critical breakdown voltage of SiC is about ten times higher than that of Si, thus it enables to achieve high breakdown voltage of power device by unipolar power device such as Schottky barrier diode (SBD) and metal-oxide semiconductor field effect transistor (MOSFET). This section explains the structure and electrical characteristics of SBD and MOSFET in detail.

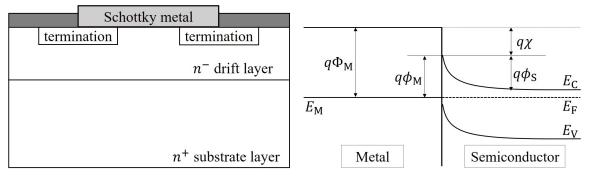

### 2.2.1 SiC SBD

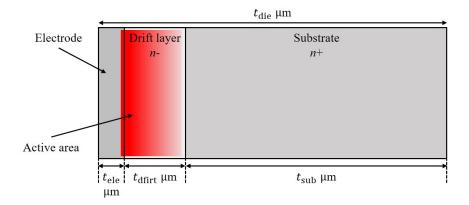

Fig. 2.2(a) is the typical cross-sectional structure of SBD. SBD is a rectifier device that utilizes Schottky junction by contacting semiconductor and metal such as titanium and nickel [59]. Barrier height of Schottky junction is designed by the different junction

(a) Cross-sectional structure. (b) Energy band diagram.

Figure 2.2 Typical cross-sectional structure and energy band diagram of SBD.

metal and surface processing. Lightly-doped  $(n^-)$  drift layer on heavily-doped  $(n^+)$ substrate layer plays an important role in blocking the reverse voltage as power device, which is derived from Poisson equation. Fig. 2.2(b) illustrates the energy band diagram of SBD. Here,  $\Phi$  is the work function and "M" and "S" denote metal and semiconductor, respectively. The work function is the energy obtained by subtracting the vacuum level from Fermi level. The electron affinity  $\chi$  is the energy obtained by subtracting the vacuum level from the conductor level.  $\Phi$  and  $\chi$  are the potential, thus it is necessary to multiply the elementary charge q.

When the forward bias voltage applies to Schottky junction, the electron density at the junction  $n_{\rm e}$  is obtained by the following equation:

$$n_{\rm e} = N_{\rm c} \exp\left(-\frac{E_{\rm c} - E_{\rm F}}{k_{\rm B}T}\right) = N_{\rm c} \exp\left[-\frac{q\phi_{\rm M} - qV}{k_{\rm B}T}\right],\tag{2.1}$$

where  $N_{\rm c}$  is the number of electron per unit area at the conduction band,  $k_{\rm B}$  is the Boltzmann constant, and T is the absolute temperature. V is the voltage applied to the device and defined as the forward voltage from metal to semiconductor.

The electron current density from semiconductor to metal  $J_{\rm S}$  is assumed to be proportional to the electron density, and the following equation is given by

$$J_{\rm S} = \alpha \exp\left[-\frac{q\phi_{\rm M} - qV}{k_{\rm B}T}\right] \left(=\alpha \exp\left(-\frac{q\phi_{\rm M}}{k_{\rm B}T}\right) \exp\left(\frac{qV}{k_{\rm B}T}\right)\right).$$

(2.2)

Here,  $\alpha$  is a function of temperature as  $\alpha = AT^2$ , and A is the effective Richardson constant. Eq. (2.2) reveals that  $J_{\rm S}$  increases as the forward bias voltage increases.

The electron current density from metal to semiconductor  $J_{\rm M}$  is balanced to  $J_{\rm S}$ when a voltage is not applied. Then substituting V = 0 into Eq. (2.2), we obtain the

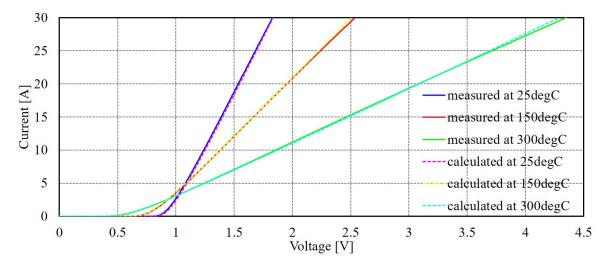

Figure 2.3 Temperature dependency of I - V characteristic for C4D20120A.

following equation:

$$J_{\rm M} = \alpha \exp\left(-\frac{q\phi_{\rm M}}{k_{\rm B}T}\right). \tag{2.3}$$

Therefore, the net electron current density J is given as follow:

$$J = J_{\rm S} - J_{\rm M} = \alpha \exp\left(-\frac{q\phi_{\rm M}}{k_{\rm B}T}\right) \left[\exp\left(\frac{qV}{k_{\rm B}T}\right) - 1\right].$$

(2.4)

We assume that the actual voltage decreases by the voltage drop  $V_0$  of the onstate resistance  $R_{\text{Td}}$  in Eq (2.4). The forward current of diode I, which is derived by multiplying the current density J and the cross-sectional area of current flow path S, is obtained by the following equations:

$$I = I_0 \left[ \exp\left(\frac{qV_0}{nk_{\rm B}T}\right) - 1 \right], \qquad (2.5)$$

$$I_0 = AT^2 \exp\left(-\frac{q\phi_{\rm M}}{k_{\rm B}T}\right), \qquad (2.6)$$

$$V_0 = V - R_{\rm Td}I.$$

(2.7)

Here,  $I_0$  is the saturation current, and n is the ideal factor. Generally, n is 1 for SBD which dominates the drift current, and n is 2 for PiN diode which dominates recombination current.

Fig. 2.3 is the temperature dependency of I-V characteristic for SiC SBD C4D20120A (1200 V/20 A, CREE). Here, "measured" is the measured I-V characteristic at each temperature, and "calculated" is calculated using Eq. (2.5) and Table 2.1 extracted

| $T \ [^{\circ}C]$ | n     | $I_0$ [A]               | $R_{\rm Td} \ [{\rm m}\Omega]$ |

|-------------------|-------|-------------------------|--------------------------------|

| 25                | 1.042 | $2.313 \times 10^{-15}$ | 27.75                          |

| 50                | 1.025 | $4.786 \times 10^{-14}$ | 31.23                          |

| 75                | 1.020 | $9.167 \times 10^{-13}$ | 35.66                          |

| 100               | 1.016 | $1.240 \times 10^{-11}$ | 40.89                          |

| 125               | 1.018 | $1.316 \times 10^{-10}$ | 46.92                          |

| 150               | 1.004 | $8.980 \times 10^{-10}$ | 54.26                          |

| 175               | 1.006 | $5.969 \times 10^{-9}$  | 62.25                          |

| 200               | 1.013 | $3.492 \times 10^{-8}$  | 71.31                          |

| 225               | 0.997 | $1.447 \times 10^{-7}$  | 81.88                          |

| 250               | 1.004 | $6.260 \times 10^{-7}$  | 92.96                          |

| 275               | 0.971 | $1.962 \times 10^{-6}$  | 105.51                         |

| 300               | 0.974 | $6.510 \times 10^{-6}$  | 118.14                         |

Table 2.1

Obtained each parameter of studied SiC SBD

by the measured data. Fig. 2.3 shows that the knee voltage of SiC SBD decreases as the junction temperature increases. This is the feature of semiconductor that carrier excites as the junction temperature increases. In the high current region, the gradient of I - V characteristic becomes small. This is because lattice vibration at Schottky metal becomes active as the junction temperature increases, and this leads to increase the on-state resistance of SiC SBD. The calculated I - V characteristic of studied SiC SBD coincides with the measured result. The obtained Richardson constant A is 9.25  $\times 10^{-2}$  and the work function  $\phi_{\rm M}$  is 1.10. From Table 2.1, ideal factor n is almost 1.

### 2.2.2 SiC MOSFET

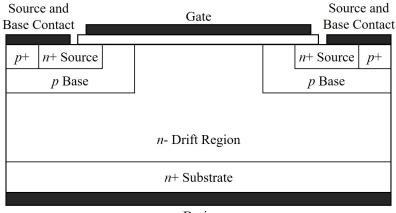

MOSFET is a semiconductor device which is widely used for switching and amplifying electric signals. MOSFET can switch on/off operation, and this enables to change voltage/current amplitude and/or frequency in power electronics. Generally, "power MOSFET" indicates the vertical structure whose drain current flows vertically in the structure. By contrast, the lateral structure, whose drain current flows horizontally thorough the inversion layer under the gate oxide, is often used for integrated circuit

Drain

(a) Planer gate structure.

(b) Trench gate structure.

Figure 2.4 Cross-sectional structure of typical *n*-type power MOSFET.

(IC) or large scale integration (LSI).

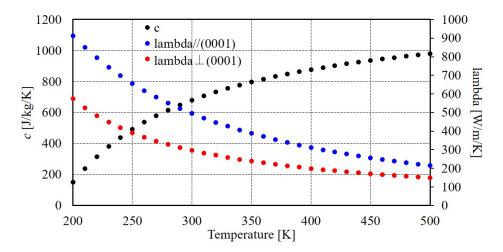

Fig. 2.4 is the cross-sectional structure of a typical *n*-type vertical power MOSFET. Fig. 2.4(a) is a planer gate double implanted MOSFET (DiMOSFET), which is derived from the similar structure of Si power device. Fig. 2.4(b) is a trench gate U-shaped MOSFET (UMOSFET). In general,  $n^-$  drift region of vertical power MOSFET is formed on a thick, richly-doped  $n^+$  substrate, and current flows vertically through the drift region. Trench gate SiC MOSFET is attractive for reducing the specific onresistance resulting from a small cell pitch and high channel mobility on the trench sidewall [60]. Another reason is that the electron mobility on the vertical and lateral direction is different in the c-axis of 4H-SiC crystal<sup>\*1</sup>. Gate terminal of MOSFET is formed by thermally oxidized polysilicon insulation layer and metal electrode.

This section briefly shows some important equations to understand electrical characteristics of MOSFET. They are covered in many semiconductor textbooks in detail, thus the reader refers to the literature for the detailed derivations.

The voltage across gate oxide  $V_{\text{OX}}$  has the relationship to the total charge par unit area at the oxide/semiconductor interface  $Q_{\text{S}}$ .

$$V_{\rm OX} = E_{\rm OX} t_{\rm OX} = \frac{Q_{\rm S}}{\varepsilon_{\rm OX}} t_{\rm OX} = \frac{Q_{\rm S}}{C_{\rm OX}},$$

(2.8)

where  $t_{\text{OX}}$ ,  $\varepsilon_{\text{OX}}$  and  $C_{\text{OX}}$  are the thickness, relative dielectric constant and capacitance par unit area of the gate oxide, respectively. When the inversion layer occurs at the oxide/semiconductor interface, its surface potential  $\psi_{\text{S}}$  is two times higher than the bulk potential  $\psi_{\text{B}}$ .

$$\psi_{\rm S} = 2\psi_{\rm B}.\tag{2.9}$$

The bulk potential  $\psi_{\rm B}$  is the potential of the depletion layer, and  $\psi_{\rm B}$  has a function of the impurity concentration in semiconductor.

$$\psi_{\rm B} = \left(\frac{E_{\rm i} - E_{\rm FS}}{q}\right) = \frac{k_{\rm B}T}{q} \ln\left(\frac{p_0}{n_{\rm i}}\right) = \frac{k_{\rm B}T}{q} \ln\left(\frac{N_{\rm A}}{n_{\rm i}}\right).$$

(2.10)

Here,  $E_{\rm i}$  is the intrinsic Fermi energy,  $E_{\rm FS}$  is the flatband energy, and  $n_{\rm i}$  is the intrinsic carrier concentration.  $p_0$  is the hole concentration, and this is equal to impurity concentration  $N_{\rm A}$  in silicon. Thus, the threshold voltage of MOSFET  $V_{\rm TH}$  is given as the following equation:

$$V_{\rm TH} = \frac{Q_{\rm S}}{C_{\rm OX}} + \psi_{\rm S} = \frac{Q_{\rm S}}{C_{\rm OX}} + 2\psi_{\rm B}.$$

(2.11)

The total charge par unit area at the oxide/semiconductor interface in weak inversion is given as follow:

$$Q_{\rm S} = \sqrt{2\varepsilon_{\rm S}qp_{\rm p0}\psi_{\rm S}} = \sqrt{4\varepsilon_{\rm S}qN_{\rm A}\psi_{\rm B}}.$$

(2.12)

$<sup>^{*1}</sup>$ Vertical:1020cm<sup>2</sup>/V/s, lateral:1200cm<sup>2</sup>/V/s [25]

Here,  $\varepsilon_{\rm S}$  is the relative dielectric constant of semiconductor, and  $n_{\rm p0}$  is the electron concentration in the depletion region of semiconductor at the chemical equilibrium condition. Eq. (2.11) is rewritten as follow using Eq. (2.12):

$$V_{\rm TH} = \frac{\sqrt{4\varepsilon_{\rm S}qN_{\rm A}\psi_{\rm B}}}{C_{\rm OX}} + 2\psi_{\rm B}.$$

(2.13)

And Eq. (2.13) can be rewritten as follow using Eq. (2.10):

$$V_{\rm TH} = \frac{\sqrt{4\varepsilon_{\rm S}k_{\rm B}TN_{\rm A}\ln(N_{\rm A}/n_{\rm i})}}{C_{\rm OX}} + \frac{2k_{\rm B}T}{q}\ln\left(\frac{N_{\rm A}}{n_{\rm i}}\right).$$

(2.14)

The first term of Eq. (2.14) dominates the threshold voltage of MOSFET.  $V_{\rm TH}$  is also expressed as the following equation by rewriting the capacitance at the gate oxide and neglecting the second term in Eq. (2.14).

$$V_{\rm TH} = \frac{t_{\rm OX}}{\varepsilon_{\rm OX}} \sqrt{4\varepsilon_{\rm S} q N_{\rm A} \psi_{\rm B}}$$

(2.15)

$$= \frac{t_{\rm OX}}{\varepsilon_{\rm OX}} \sqrt{4\varepsilon_{\rm S} k_{\rm B} T N_{\rm A} \ln\left(\frac{N_{\rm A}}{n_{\rm i}}\right)}.$$

(2.16)

Eq. (2.16) shows that the threshold voltage of MOSFET is proportional to the square of the gate oxide thickness and doping concentration.

Differentiating Eq. (2.13) by T and we obtain the following equation:

$$\frac{dV_{\rm TH}}{dT} = \frac{d\psi_{\rm B}}{dT} \left[ \frac{1}{C_{\rm OX}} \sqrt{\frac{\varepsilon_{\rm S} q N_{\rm A}}{\psi_{\rm B}}} + 2 \right].$$

(2.17)

Here,  $d\psi_{\rm B}/dT$  is approximated as follow [61]:

$$\frac{d\psi_{\rm B}}{dT} \approx \frac{1}{T} \left[ \frac{E_{\rm g}(T=0)}{2q} - |\psi_{\rm B}(T)| \right]. \tag{2.18}$$

Eqs. (2.17) and (2.18) show that the threshold voltage of MOSFET decreases as the junction temperature increases if  $|\psi_{\rm B}(T)| > E_{\rm g}(T=0)/2q$ .

Next, we consider current-voltage relationship of MOSFET. The channel current  $I_{\rm D}$  is given as follow:

$$I_{\rm D} = \left(\frac{W}{L}\right) C_{\rm OX} \mu_{\rm n} \left[ \left(V_{\rm G} - V_{\rm FB} - 2\psi_{\rm B} - \frac{V_{\rm D}}{2}\right) V_{\rm D} - \left(\frac{2}{3}\right) \frac{\sqrt{2\varepsilon_{\rm S}qN_{\rm A}}[(V_{\rm D} + 2\psi_{\rm B})^{3/2} - (2\psi_{\rm B})^{3/2}]}{C_{\rm OX}} \right].$$

(2.19)

Eq. (2.19) shows that channel current increases as the increase of drain and gate voltage. This region is called as the linear operating region of MOSFET, and channel current is also called as drift current. Eq. (2.19) is simply rewritten as follow with assuming  $N_{\rm A}$  is small:

$$I_{\rm D} = \left(\frac{W}{L}\right) C_{\rm OX} \mu_{\rm n} \left(V_{\rm G} - V_{\rm TH} - \frac{V_{\rm D}}{2}\right) V_{\rm D}.$$

(2.20)

In actual MOSFET, the drain current is limited by a saturated carrier velocity over the saturated drain voltage  $V_{\text{Dsat}}$ . We consider the condition of  $dI_{\text{D}}/dV_{\text{D}} = 0$ .

(i)  $V_{\rm D} \ll 2\psi_{\rm B}$

$$V_{\rm D} = V_{\rm Dsat} = V_{\rm G} - V_{\rm TH},$$

(2.21)

(ii)  $V_{\rm D} \gg 2\psi_{\rm B}$

$$V_{\rm D} = V_{\rm Dsat}$$

$$= V_{\rm G} - V_{\rm FB} - 2\psi_{\rm B} + \frac{K^2}{2} - \left(\frac{K}{2}\right)\sqrt{K^2 + 4(V_{\rm G} - V_{\rm FB} - 2\psi_{\rm B})}.$$

(2.22)

Here,  $K = \frac{\sqrt{2\varepsilon_{\rm S}qN_{\rm A}}}{C_{\rm OX}}$ . Thus,  $I_{\rm Dsat}$  is obtained as the following equation under  $V_{\rm D} > V_{\rm Dsat}$ :

(i)  $V_{\rm D} \ll 2\psi_{\rm B}$

$$I_{\rm D} = \left(\frac{W}{2L}\right) C_{\rm OX} \mu_{\rm n} (V_{\rm G} - V_{\rm TH})^2, \qquad (2.23)$$

(ii)  $V_{\rm D} \gg 2\psi_{\rm B}$

$$I_{\rm D} = \left(\frac{W}{L}\right) C_{\rm OX} \mu_{\rm n} \left[V_{\rm G} - V_{\rm FB} - 2\psi_{\rm B} - \left(\frac{2}{3}\right) \frac{\sqrt{2\varepsilon_{\rm S}qN_{\rm A}}}{C_{\rm OX}} - \frac{V_{\rm Dsat}}{2}\right] V_{\rm Dsat}.$$

(2.24)

After the drain current saturated, the inversion layer narrows near the drain, and eventually pinches off. When this occurs, Eq. (2.19) is no longer valid. The drain voltage that causes the pinch-off can be found by setting the charge in the inversion layer at the drain to zero. This region is called as the saturated region. In practical, I - V characteristics of MOSFET at the linear and saturated region are given as the following equations:

$$I_{\rm D} = \alpha \left( V_{\rm G} - V_{\rm TH} - \frac{V_1}{2} \right) V_1 \text{ for } V_{\rm D} < V_{\rm G} - V_{\rm TH}, \qquad (2.25)$$

$$I_{\rm D} = \frac{\alpha}{2} (V_{\rm G} - V_{\rm TH})^2 (1 + \lambda_{\rm c} V_{\rm D}) \text{ for } V_{\rm D} > V_{\rm G} - V_{\rm TH}, \qquad (2.26)$$

$$V_1 = V_{\rm D} - R_{\rm Tm} I_{\rm D}, \qquad (2.27)$$

$$\alpha = \left(\frac{W}{L}\right) C_{\rm OX} \mu_{\rm n}. \tag{2.28}$$

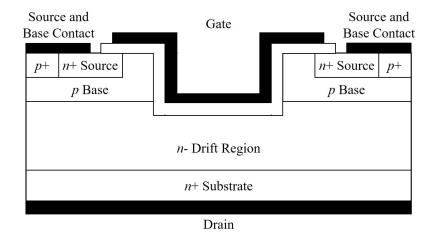

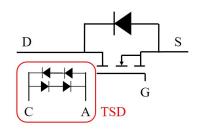

Fig. 2.5 is the temperature dependency of I - V characteristics for SiC MOSFET CMF20120D (1200 V/40 A, CREE). Figs. 2.5(a) and 2.5(b) are  $I_d - V_{ds}$  characteristics at room temperature and  $T = 300^{\circ}$ C, respectively. For a relatively large gate voltage, the gradient of I - V carves becomes small as the junction temperature increases. This is because the on-state resistance becomes large as shown in Fig. 2.5(c). And for a relatively small gate voltage over the gate threshold voltage, the saturation current becomes larger for the same gate voltage. This is because the gate threshold voltage becomes lower as the junction temperature increases. Fig. 2.5(c) shows that the gate threshold voltage becomes low as the junction temperature increases, which coincides with Eqs. (2.17) and (2.18).

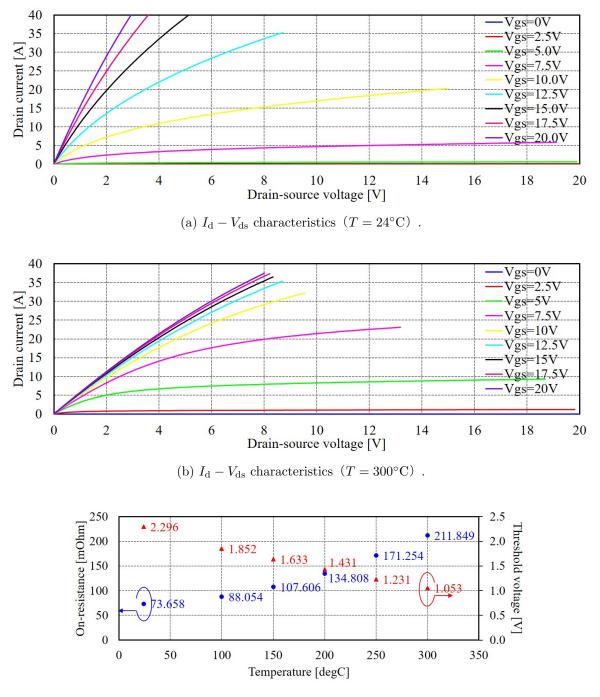

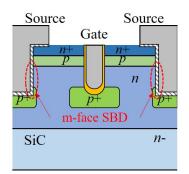

### 2.2.3 SWITCH-MOS

Knee voltage of body diode in SiC MOSFETs is relatively large due to its wide bandgap, which results in the large conduction losses in reverse conduction through body diode. In addition, the current conduction in body diode induces the bipolar degradation due to the recombination of injected minority carriers [62]. This causes the increase of the on-state resistance of SiC MOSFET.

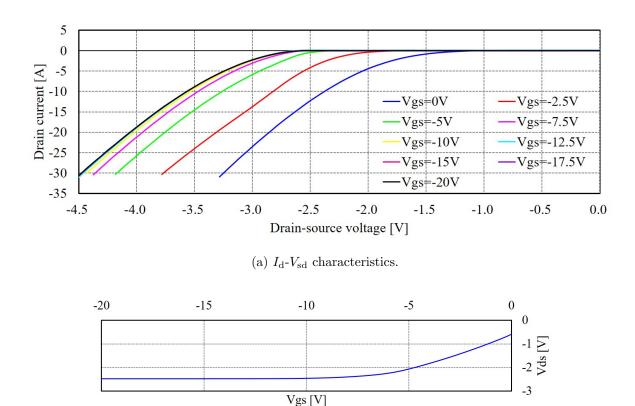

Fig. 2.6 shows the typical device structure of the developed SiC MOSFET with built-in SBD [63] [64]. This is named as <u>SBD-Wall-Integrated TrenCH MOS</u>FET (SWITCH-MOS). While the planer gate SiC MOSFET with built-in SBD was reported in the same time [65], SWITCH-MOS is designed based on the trench gate SiC UMOSFET [66]. SWITCH-MOS is designed to have the reverse current flow through built-in SBD rather than through pn body diode by controlling the electric field around

(c) Temperature dependency of  $V_{\rm TH}$  and  $R_{\rm on}$ .

Figure 2.5 Temperature dependency of I - V characteristics for SiC MOSFET.

Figure 2.6 Cross-sectional structure of SWITCH-MOS.

the  $p^+$  layer of bottom gate trench. This results in suppressing conduction losses and the bipolar degradation, and reducing the area in the package for the external free wheeling diode.

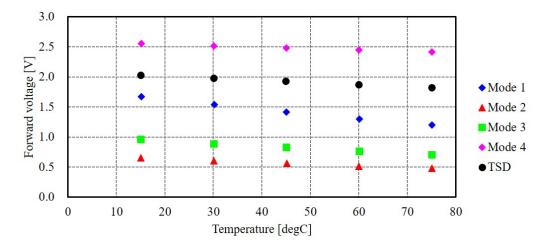

## 2.2.4 Temperature sensitive electrical parameter of SiC power device

Thermal management with monitoring the junction temperature of power device  $(T_J)$  is one of the most important interest in the safety and reliable operation of power conversion systems. There are some methods to the estimate  $T_J$  of power modules.

1. Thermocouple

This method applies Seebeck effect, which is the thermoelectric force caused by different temperature between 2 different metal wire. Thermocouple has fast response time for the temperature change, but it needs to attach directly on measuring objects. And this also has the large error in the estimated temperature about  $\pm 2^{\circ}$ C.

2. Thermometer or Thermal image viewer

This method measures the temperature based on the black body radiation. Thermal image viewer also can show the temperature distribution on the measuring object by color variation. Though this method does not need to directly attach on measuring objects, the response time is not good.

#### 3. Electrical Test Method (ETM) [67]

This method utilizes the temperature dependency in I-V characteristics of power device itself. Temperature dependency of the knee voltage for power diodes and the gate threshold voltage for IGBTs or MOSFETs are used for estimating  $T_J$ . This method enables to use power devices as not only the heat source but also the temperature sensor. While this method enables to obtain the fast time response of  $T_J$ , it is necessary to be care about the electrical noise of measuring system.

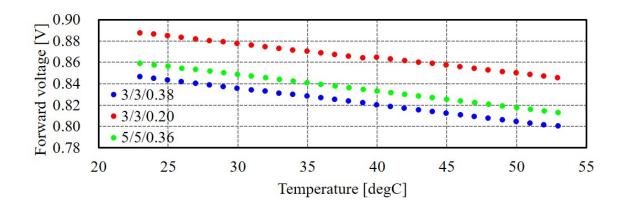

This study focuses on ETM method to utilizes the fast time response for estimating  $T_{\rm J}$  of SiC power device. For a fixed measurement current  $I_{\rm M}$ , the terminal voltage is almost linearly proportional to  $T_{\rm J}$ . This is called as temperature sensitive electrical parameter (TSEP) or K factor. Here,  $I_{\rm M}$  is small enough to neglect the self heating effect on power device.

First of all, we derive K factor of power diode, especially of SBD. Eq. (2.5) can be rewritten as the following equation for  $I_{\rm M}$ , which is very small to neglect the on-state resistance.

$$I_{\rm M} = I_0 \left[ \exp\left(\frac{qV_{\rm J}(T)}{nk_{\rm B}T}\right) - 1 \right], \qquad (2.29)$$

where  $V_{\rm J}(T)$  is the junction voltage of power device and as a function of temperature T. Assuming that the temperature dependency of  $I_0$  can be neglect, Eq. (2.29) is rewritten as follow:

$$\log\left(\frac{I_{\rm M}}{I_0} - 1\right) = \frac{qV_{\rm J}(T)}{nk_{\rm B}T},$$

$$\Leftrightarrow V_{\rm J}(T) = \frac{nk_{\rm B}T}{q} \left(\frac{I_{\rm M}}{I_0} - 1\right).$$

(2.30)

Differentiating Eq. (2.30) by T, we can obtain K factor for diode.

$$\frac{1}{K_{\rm diode}} = \frac{dV_{\rm J}(T)}{dT} = \frac{nk_{\rm B}}{q} \left(\frac{I_{\rm M}}{I_0} - 1\right).$$

(2.31)

We can also derive K factor of MOSFET as the following procedure. Assuming the GD short condition ( $V_{\rm ds} = V_{\rm gs}$ ), I and  $V_{\rm ds} = V_{\rm gs}$  are replaced by  $I_{\rm M}$  and  $V_{\rm ds} = V_{\rm gs} = V_{\rm J}(T)$  as a function of T, respectively. And then,

$$V_{\rm J}(T)^2 - 2V_{\rm TH}V_{\rm J}(T) - \frac{2LI_{\rm M}}{W\varepsilon_{\rm S}C_{\rm OX}} = 0.$$

(2.32)

Solving Eq. (2.32) and we obtain the following equation:

$$V_{\rm J}(T) = V_{\rm TH} \pm \sqrt{V_{\rm TH}^2 + \frac{2LI_{\rm M}}{W\varepsilon_{\rm S}C_{\rm OX}}}.$$

(2.33)

For a forward bias condition,  $V_{\rm J}(T)$  is larger than 0. Thus,

$$V_{\rm J}(T) = V_{\rm TH} + \sqrt{V_{\rm TH}^2 + \frac{2LI_{\rm M}}{W\varepsilon_{\rm S}C_{\rm OX}}}.$$

(2.34)

Differentiating Eq. (2.34) by T with Eq. (2.15) and we obtain the following equation.

$$\frac{dV_{\rm J}(T)}{dT} = \frac{dV_{\rm TH}}{dT} + \frac{V_{\rm TH}\frac{dV_{\rm TH}}{dT}}{\sqrt{V_{\rm TH}^2 + \frac{2LI_{\rm M}}{W\varepsilon_{\rm S}C_{\rm OX}}}}$$

$$= \frac{dV_{\rm TH}}{dT} \left( 1 + \frac{V_{\rm TH}}{\sqrt{V_{\rm TH}^2 + \frac{2LI_{\rm M}}{W\varepsilon_{\rm S}C_{\rm OX}}}} \right).$$

(2.35)

77 7

Eq. (2.35) can be rewritten as follow using Eq. (2.32):

$$\frac{dV_{\rm J}(T)}{dT} = \frac{dV_{\rm TH}}{dT} \left( 1 + \frac{V_{\rm TH}}{\sqrt{V_{\rm TH}^2 - 2V_{\rm TH} + V_{\rm J}(T)^2}} \right)

= \frac{dV_{\rm TH}}{dT} \left( 1 + \frac{V_{\rm TH}}{|V_{\rm TH} - V_{\rm J}(T)|} \right)

= \frac{dV_{\rm TH}}{dT} \left( 1 + \frac{1}{\left|\frac{V_{\rm J}(T)}{V_{\rm TH}} - 1\right|} \right).$$

(2.36)

And then,

$$\frac{1}{K_{\text{MOSFET}}} = \frac{dV_{\text{J}}(T)}{dT} = \frac{1}{T} \left[ \frac{E_{\text{g}}(T=0)}{2q} - |\psi_{\text{B}}(T)| \right] \left( 1 + \frac{1}{\left| \frac{V_{\text{J}}(T)}{V_{\text{TH}}} - 1 \right|} \right). \quad (2.37)$$

Eq. (2.37) shows that it is possible to estimate  $T_{\rm J}$  of MOSFET using K factor.

### 2.3 SiC power module

A power module packages plural switching devices such as MOSFET or IGBT and/or free wheeling diode (FWD). Modularization enables to obtain the high breakdown and

Figure 2.7 Typical structures of power module.

large current capacity by connecting power devices in series and parallel. Actually, most power module connects two or more power devices in parallel on the module in order to realize high current capacity, although the rated voltage is determined by least breakdown voltage among parallel connected devices, and series connection is rarely seen. Another advantage of modularization is to miniaturize power conversion systems. Integrating and implementing devices in the module package reduces the area to implement components in power conversion systems. Moreover this enables to reduce parasitic components in the circuit, which results in improving electrical behavior of power conversion systems such as switching surge voltage. This section summarizes typical structures and materials of recent power module packages.

### 2.3.1 Typical power module constitution

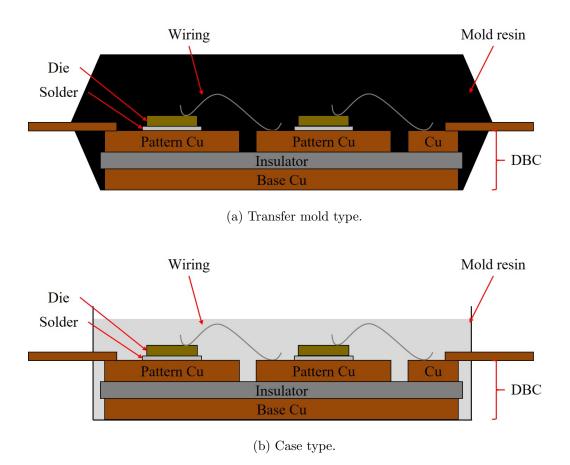

Fig. 2.7 illustrates typical structures of power module, which are almost same structure.Fig. 2.7(a) is a transfer mold encapsulated power module and molded by thermal resin.Fig. 2.7(b) is a case type power module and covered with protective resin such as Si gel.

Bare die of power device is attached on the module substrate using solder material and forms die attach. Die attach plays an important role in flowing both the large current and the heat generated in junction of power device. Due to RoHS, Pb free solder such as Sn/Ag/Cu (SAC) is generally used as die attach material. However, Pb free solder has difficulty in terms of reliability for high temperature application because its melting point is lower than the conventional Pb solder [68] [69]. This concerns about long-term reliability at the harsh environment using SiC power devices over 300°C. Sintered die attach using nano particle metal such as Ag or Cu attracts attention to achieve the low electrical and thermal resistance for high density power module. A variety of sintered die attach materials have been reported [70]-[72]. Reference [73] developed 3.3 kV/1000 A SiC power module with sintered Cu die attach.

Metal wire bonding forms a electrical connection between power device and module as shown in Fig. 2.8 by ball bonding or wedge bonding. Al or Cu wire, whose diameter is 50 to 500  $\mu$ m are often used to flow large current. Ribbon bonding technology attracts attention for using interconnections instead of multiple bonding wires. Ribbon bonding increases current capability of ribbons, and also carries the heat generated in junction of power device [74] [75].

Insulation layer plays an important role in making the electrical insulation between power device and heatsink and transferring heat from power device to heat sink. This is required to obtain the high insulation resistance and high thermal conductivity at the high temperature condition. Table 2.2 shows physical properties of typical ceramic material. Here,  $\lambda$  is the thermal conductivity, c is the specific heat,  $\rho$  is the density,  $\sigma_{\text{MAX}}$  is the 3-points bending strength, CTE is the coefficients of thermal expansion, and  $\varepsilon_{\rm r}$  is the relative dielectric constant. Aluminium oxide (Al<sub>2</sub>O<sub>3</sub>) is used for direct bonding copper (DBC) substrate as insulation layer for a long time. Active metal brazing (AMB) technology with active metal enables to joint copper and silicon nitride

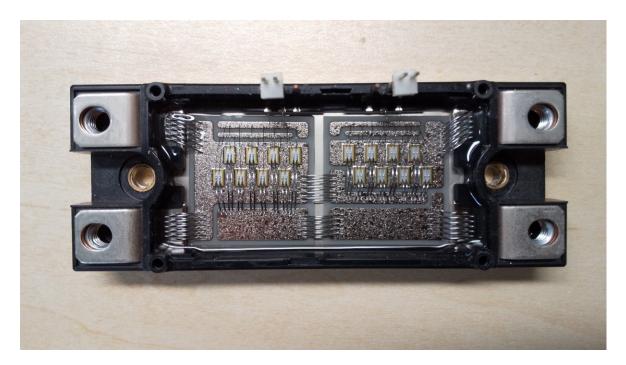

Figure 2.8 Example of case type power module and bonding wire (BSM180D12P2C101, ROHM).

| Table 2.2 Thysical properties of typical certaine material |                            |            |                       |                          |             |                      |  |

|------------------------------------------------------------|----------------------------|------------|-----------------------|--------------------------|-------------|----------------------|--|

| Material                                                   | $\lambda \; [{\rm W/m/K}]$ | c  [J/g/K] | $\rho~[{\rm g/cm^3}]$ | $\sigma_{\rm MAX}$ [MPa] | CTE [ppm/K] | $\varepsilon_{ m r}$ |  |

| $Al_2O_3$                                                  | 36                         | 0.779      | 3.9                   | 400                      | 7.2         | 9.9                  |  |

| $Si_3N_4(SN-490)$                                          | 85                         | 0.69       | 3.2                   | 820                      | 2.3         | 9.5                  |  |

| $\mathrm{Si}_3\mathrm{N}_4(\mathrm{SN}\text{-}460)$        | 58                         | 0.63       | 3.5                   | 790                      | 2.7         | 9.6                  |  |

| AlN                                                        | 150                        | 0.71       | 3.4                   | 310                      | 4.6         | 8.6                  |  |

Table 2.2

Physical properties of typical ceramic material

$(Si_3N_4).$

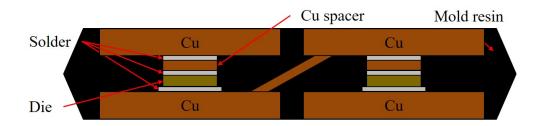

Fig. 2.9 shows a new power module structure for double sided cooling particularly developed for automotive applications [76] [77]. This structure solders both backside and top side of power device on the heat spreader without wire bonding. This structure enables to not only flow the large current but also transfer the heat dissipated in junction at both direction of power device and reduce the total thermal resistance, which differs from the conventional direct lead bonding (DLB) structure [78].

Figure 2.9 Power module with double sided cooling.

### 2.3.2 Developed multi-layered ceramic substrate for power module

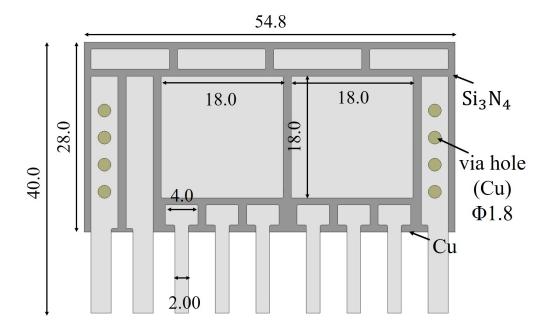

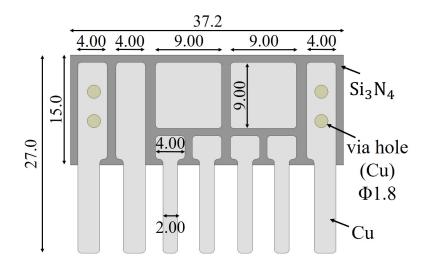

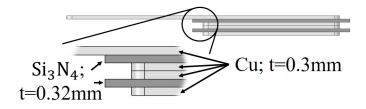

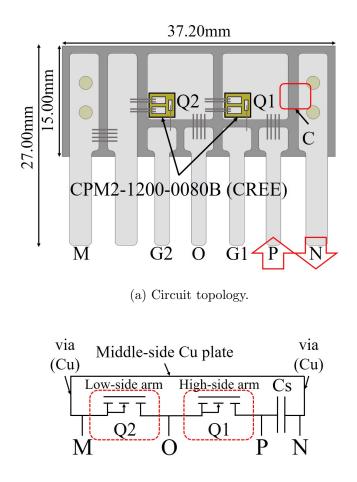

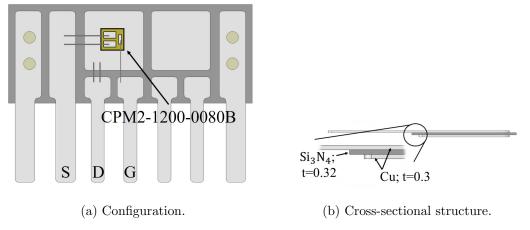

The developed multi-layered ceramic substrate for SiC power module in this study is illustrated in Fig. 2.10. The dimension of module substrate A and B are different to mount various types of chip size, parallelization and wiring connection layout. The insulation layer is composed of  $Si_3N_4$  with  $320\mu$ m. The Cu plate is brazed with active metal as the conduction layer on the both side of insulation layer. Two double side substrate is stacked to constitute multi-layered substrate. Pattern and middle layer conductor are electrically connected at terminal M and N through two  $\phi$ 1.8mm vias with Cu cores to flow the large current.

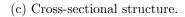

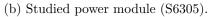

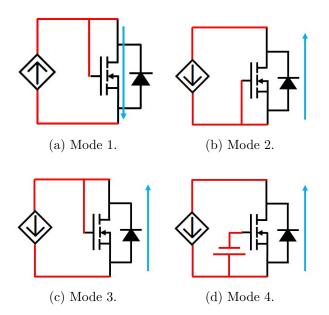

Fig. 2.11 shows the typical topology of buck converter. Here, the dashed line indicates power module. The parasitic inductance in power conversion system  $L_{PCB}$ and in power module  $L_{PM}$  induces switching surge voltage with high current switching transient (di/dt). Though C snubber near power module is often used for the switching surge voltage suppression, but this still remains the parasitic inductance of power module itself. The developed multi-layered ceramic substrate enables to directly attach the snubber capacitor on the substrate across DC bus for eliminating the parasitic inductance of wiring between half-bridge and smoothing DC capacitor. This results in suppressing switching surge voltage with high speed switching using unipolar SiC power device.

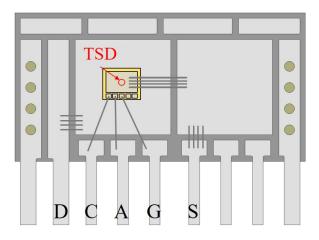

Fig. 2.12 is a example of SiC power module using the developed multi-layered ceramic substrate. SiC MOSFET CPM2-1200-0080B (1200 V/40 A, 3.1 mm/3.36 mm/180  $\mu$ m, CREE) is attached with 120  $\mu$ m Sn/Ag/Cu solder (SMIC) on pattern

(a) Module substrate A.

(b) Module substrate B.

Figure 2.10 Developed multi-layered ceramic substrate.

Figure 2.11 Typical buck converter topology using power module.

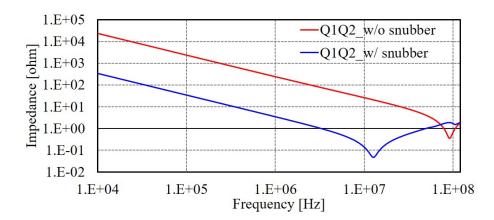

Cu for both arm. Multi-layered ceramic capacitor (MLCC) GRM43DR73A473KW01 (1 kV, 0.047  $\mu$ F, Murata) is attached directly on the module substrate across DC bus between half-bridge and smoothing DC capacitor. Fig. 2.13 is the frequency characteristics of impedance for terminal P to N. Here, this is experimentally obtained by impedance analyzer 4294A (Agilent Technolgy). The parasitic inductance without and with MLCC of the developed SiC power module obtained from Fig. 2.13 is 4.51nH and 3.38nH, respectively.

#### 2.4 Summary

This chapter treated fundamentals of SiC power devices and power modules. Electrical characteristics and its temperature dependency of SBD and MOSFET were derived in section 2.2. The knee voltage of SBD and the gate threshold voltage of MOSFET became small as  $T_{\rm J}$  of power device increases, which would be used for  $T_{\rm J}$  estimation as K factor. Section 2.3 described typical power module constitutions. Recent and next generation structures and materials of power module were shown in section 2.3.1. The developed multi-layered ceramic substrate in this study was shown in 2.3.2.

(b) Equivalent circuit of developed module.

Figure 2.12 Developed SiC power module using multi-layered ceramic substrate.

structure enables to reduce the parasitic inductance with snubber capacitor, which results in suppressing switching surge voltage of SiC power module with high speed switching.

Figure 2.13 Frequency characteristics of impedance for terminal P to N.

### Chapter 3

## Transient thermal network model identification for power module packages

#### 3.1 Introduction

Transient thermal characterization of power modules plays an important role in designing power conversion systems for miniaturization. The transient thermal network model of power module packages is identified by deconvolution calculation for the time response of junction temperature  $(T_J)$  in power semiconductor devices, which is obtained by static test method. This chapter develops a signal processing algorithm using weighted discrete Fourier transformation and noise filtering in frequency domain for nonuniform time step data in the converted logarithmic time domain to apply deconvolution calculation. The developed algorithm suppresses the influence of noise superimposed on the measured signal and enables the accurate identification of transient thermal network model.

## 3.2 Transient thermal network model of power module packages

This section summarizes the theory and the measurement setup of static test method. For more details on the method, the reader refers the standard text [54] and related references.

#### 3.2.1 Structure function related to transient thermal networks

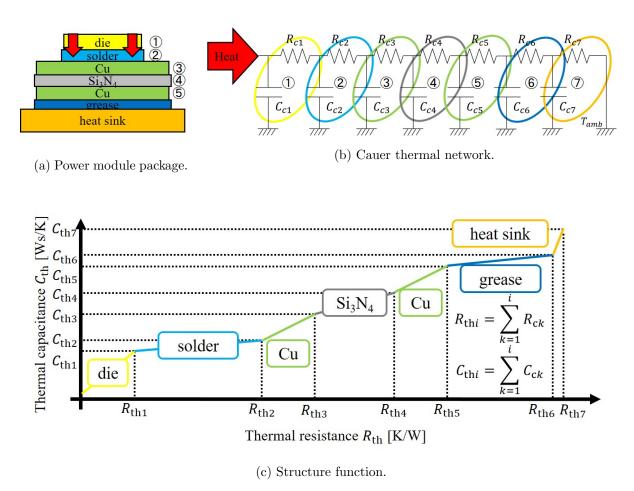

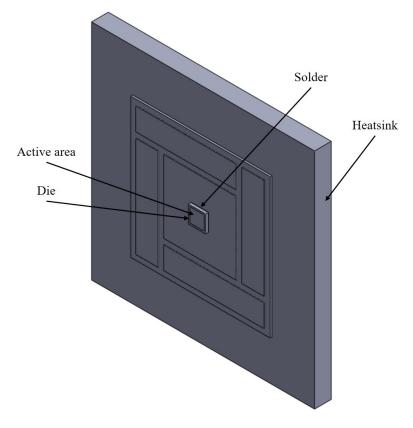

Figure 3.1 Structure function related to actual power module package.

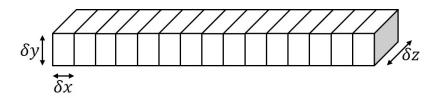

The typical structure of a power module package with active metal bonding (AMB) substrate is illustrated in Fig. 3.1(a). The heat dissipated in junction of power device approximately flows to heat sink through each layer of power module package in one direction. The thermal equivalent circuit is modeled by the cascade connected pairs

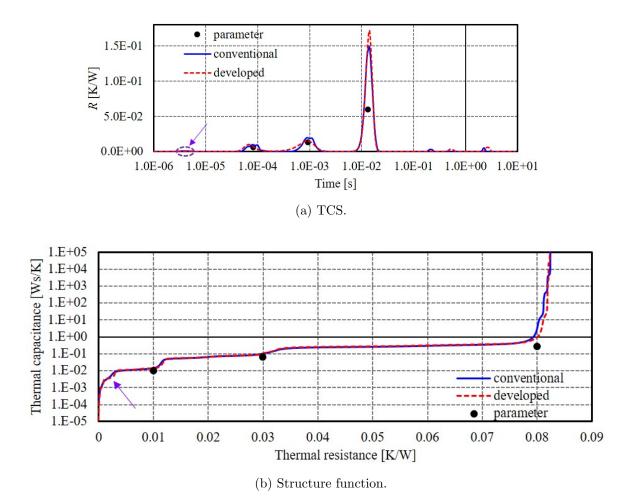

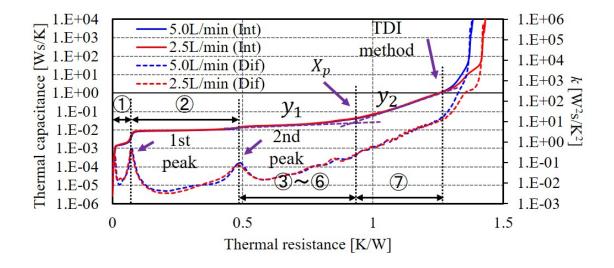

of thermal resistance and thermal capacitance as Cauer thermal network illustrated in Fig. 3.1(b), by assuming that each layer of the power module package is uniform and heat spreading in the horizontal axis is integrated. Here, the electrical potential and current in electrical circuit correspond to the junction temperature and heat flow in thermal circuit, respectively. The Protonotarious-Wing function [79], or structure function [80], represents the cumulative thermal capacitance as a function of the cumulative thermal resistance as illustrated in Fig. 3.1(c). In other words, structure function related to Cauer thermal network represents transient thermal behavior of respective components in the power module.

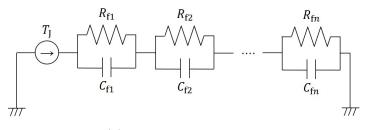

(a) Cauer thermal network.

(b) Foster thermal network.

Figure 3.2 Transient thermal network models.

Generally, the thermal impedance of an *n*th order Cauer thermal network  $Z_{\text{cauer}}(s)$ in Laplace (*s*-)domain is given by the following equation with the parameters in Fig. 3.2(a):

$$Z_{\text{cauer}}(s) = \frac{1}{sC_{c1} + \frac{1}{R_{c1} + \frac{1}{sC_{c2} + \frac{1}{R_{c2} + \frac{1}{\ddots + \frac{1}{sC_{cn} + \frac{1}{R_{cn}}}}}}.$$

(3.1)

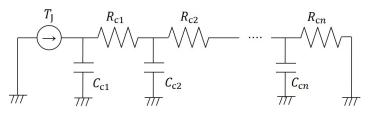

Although Cauer thermal network corresponds to the actual physical parameter and

structure of power module packages, but the parameter extraction directly from the measured time response of  $T_{\rm J}$  is difficult. We therefore consider the numerical equivalent transient thermal network model illustrated in Fig. 3.2(b). This network is known as Foster thermal network, and its parameters do not have physical correspondence to the model structure. The thermal impedance of an *n*th order Foster thermal network  $Z_{\rm foster}(s)$  in *s*-domain is given by the summation of fractional impedances with the parameters in Fig. 3.2(b):

$$Z_{\text{foster}}(s) = \frac{R_{\text{f1}}}{1 + sR_{\text{f1}}C_{\text{f1}}} + \frac{R_{\text{f2}}}{1 + sR_{\text{f2}}C_{\text{f2}}} + \dots + \frac{R_{\text{fn}}}{1 + sR_{\text{fn}}C_{\text{fn}}} = \sum_{i=1}^{n} \frac{R_{\text{fi}}}{1 + sR_{\text{fi}}C_{\text{fi}}}.$$

(3.2)

By converting Eq. (3.2) from s-domain to time domain, the time response of junction temperature  $T_{\rm J}(t)$  for  $\Delta P_{\rm H}$  power dissipation is calculated by the following equation:

$$T_{\rm J}(t) = \Delta P_{\rm H} \sum_{i=1}^{n} R_{\rm fi} [1 - \exp(-t/\tau_{\rm fi})], \qquad (3.3)$$

where  $\tau_{fi} = R_{fi}C_{fi}$  is the thermal time constant. This equation means that the time response of  $T_J$ , which is obtained experimentally from power devices in power modules, is represented by the summation of exponential functions. Moreover, the desired Cauer thermal network is obtained from Foster thermal network by numerical equivalent transformation.

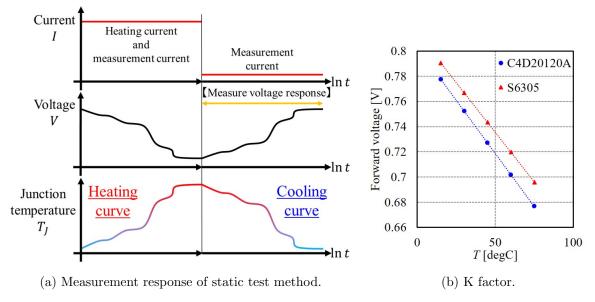

### 3.2.2 Foster thermal network model identification by deconvolution

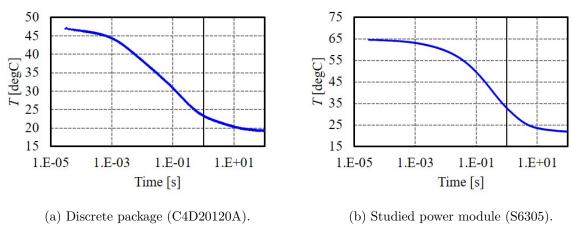

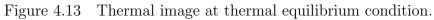

The time response of  $T_J$  is experimentally obtained using static test method. The measurement procedure is summarized as follows, and illustrated in Fig. 3.3(a). First, a device under test (DUT) is attached on the temperature-controlled coldplate. A large current, which is sufficient to achieve self-heating, is forced to flow through a DUT until it reaches thermal equilibrium condition. The heating current then shunts off and the time response of  $T_J$  in cooling operation is measured.  $T_J$  is obtained from the measured voltage drop to a small constant current, whose self-heating effect is negligible, and the temperature dependency in I - V characteristics of power semiconductor devices. The measured time response of junction voltage  $(V_J)$  is converted to the time response of

Figure 3.3 Static test method.

$T_{\rm J}$  using K factor. Fig. 3.3(b) shows the example of K factor for SiC Schottky barrier diode (SBD) C4D20120A (1200 V/20 A, CREE, TO-220 package) and S6305 (1200 V/50 A, ROHM, mounted on ceramic substrate).

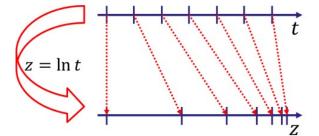

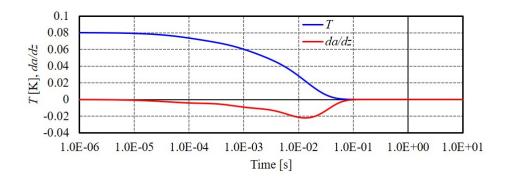

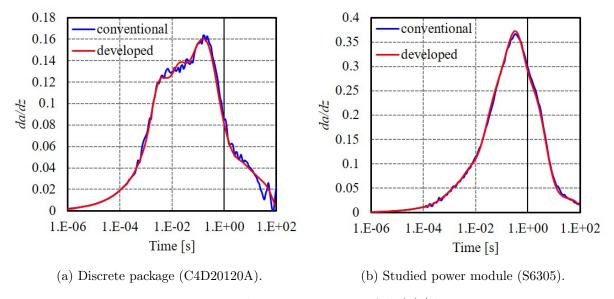

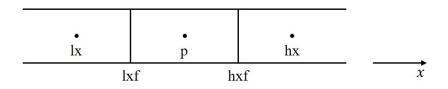

Cauer thermal network model is identified from the measured time response of  $T_{\rm J}$  using the procedure listed in Table 3.1. In this chapter, this procedure is referred as the conventional algorithm, which is implemented in the analysis software T3SterMaster (MentorGraphics). Eq. (3.3) is rewritten as the transfer function a(t) for the unit power step input:

$$a(t) = \frac{T_{\rm J}(t)}{\Delta P_{\rm H}} = \sum_{i=1}^{n} R_{\rm fi} [1 - \exp(-t/\tau_{\rm fi})], \qquad (3.4)$$

where a(t) is transformed to a(z) by introducing the logarithmic time scale  $z = \ln t$ , and  $\zeta = \ln \tau$ . Thermal time constant spectrum or TCS, R(z), is given as the following equation with the deconvolution integral  $\otimes^{-1}$ :

$$R(z) = \frac{d}{dz}a(z) \otimes^{-1} w(z), \qquad (3.5)$$

where  $w(z) = \exp(z - \exp(z))$  is the given weight function. The obtained Foster thermal network model from TCS by deconvolution can be transformed to Cauer thermal network model by Foster-Cauer transformation.

| table 3.1                                                                        |      | 1 ne con                                        | ventional algorithm for identifying transfent thermal network mod                                           |  |

|----------------------------------------------------------------------------------|------|-------------------------------------------------|-------------------------------------------------------------------------------------------------------------|--|

|                                                                                  | Step | Domain                                          | Procedure                                                                                                   |  |

| 1 Time $(t)$ Measure the time response of $V_{\rm J}$ in the coolin              |      | Time $(t)$                                      | Measure the time response of $V_{\rm J}$ in the cooling operation                                           |  |

| 2 Time (t) Convert $V_{\rm J}(t)$ to $T_{\rm J}(t)$ using K factor and divide in |      | Time $(t)$                                      | Convert $V_{\rm J}(t)$ to $T_{\rm J}(t)$ using K factor and divide it by the input power $\Delta P_{\rm H}$ |  |

| 3 Time (t) $T_{\rm J}(0)$ estimation by extrapolating [81]                       |      | $T_{\rm J}(0)$ estimation by extrapolating [81] |                                                                                                             |  |

| 4 Time (t) Convert $a(t)$ from the linear time domain to the                     |      | Time $(t)$                                      | Convert $a(t)$ from the linear time domain to the logarithmic time domain                                   |  |

|                                                                                  | 5    | Time $(t)$                                      | Remove the noise with moving average filter and resample                                                    |  |

|                                                                                  | 6    | Time $(z)$                                      | Differentiate $a(z)$ with z to obtain $da(z)/dz$                                                            |  |

|                                                                                  | 7    | Time $(z)$                                      | Calculate $w_{\rm z}(z)$                                                                                    |  |

|                                                                                  | 8    | Frequency                                       | FFT of $da(z)/dz$ and $w_z(z)$                                                                              |  |

|                                                                                  | 9    | Frequency                                       | Deconvolution calculation                                                                                   |  |

|                                                                                  | 10   | Time $(z)$                                      | Obtain TCS by IFFT using the filter function with Fermi-Dirac function [54]                                 |  |

|                                                                                  | 11   | Time $(z)$                                      | Determine Foster thermal network model from TCS                                                             |  |

|                                                                                  | 12   | Time $(z)$                                      | Determine Cauer thermal network model by Foster-Cauer transformation                                        |  |

|                                                                                  |      |                                                 |                                                                                                             |  |

Table 3.1

The conventional algorithm for identifying transient thermal network model

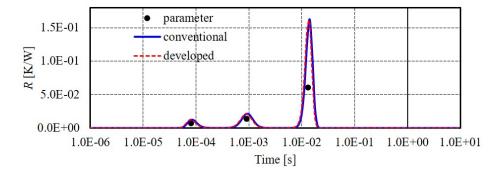

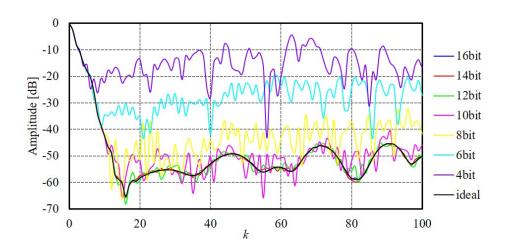

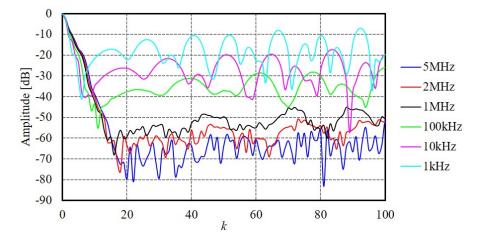

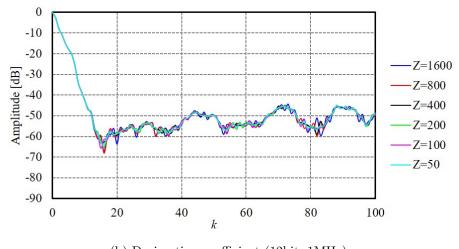

# 3.3 Signal processing algorithm in logarithmic time domain

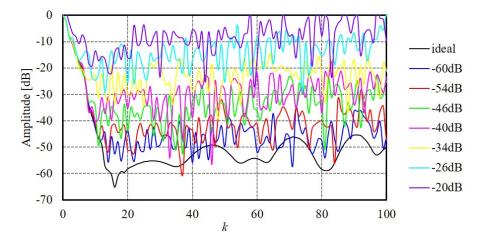

Table 3.2 shows the signal processing algorithm developed in this study to identify Cauer thermal network model, and the difference in procedure from Table 3.1 is specified by bold number. The conventional algorithm eliminates noise in the measured signal using a moving average filter in the linear time domain. However, the moving average filter cannot fully eliminate the measurement noise, and the residual noise is emphasized in numerical differentiation of a(z), which degrades the accuracy of the identified transient thermal network model. The developed algorithm adopts weighted discrete Fourier transformation and noise filtering in logarithmic frequency domain to suppress the influence of measurement noise. The details of each calculation is discussed in this chapter.

| able 3.2                                                     |    | I ne dev   | eloped algorithm for identifying transient thermal network mode                                             |

|--------------------------------------------------------------|----|------------|-------------------------------------------------------------------------------------------------------------|

| Step Domain Procedure                                        |    | Procedure  |                                                                                                             |

| 1     Time $(t)$ Measure the time response of $V_J$ in       |    | Time $(t)$ | Measure the time response of $V_{\rm J}$ in the cooling operation                                           |

|                                                              |    | Time $(t)$ | Convert $V_{\rm J}(t)$ to $T_{\rm J}(t)$ using K factor and divide it by the input power $\Delta P_{\rm H}$ |

|                                                              |    | Time $(t)$ | $T_{\rm J}(0)$ estimation by extrapolating [81]                                                             |

| 4 Time (t) Convert $a(t)$ from the linear time domain to the |    | Time $(t)$ | Convert $a(t)$ from the linear time domain to the logarithmic time domain                                   |

|                                                              | 5  | Time $(z)$ | Differentiate $a(z)$ with z to obtain $da(z)/dz$                                                            |

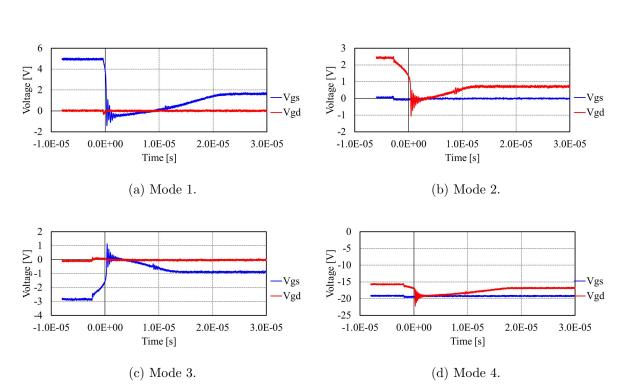

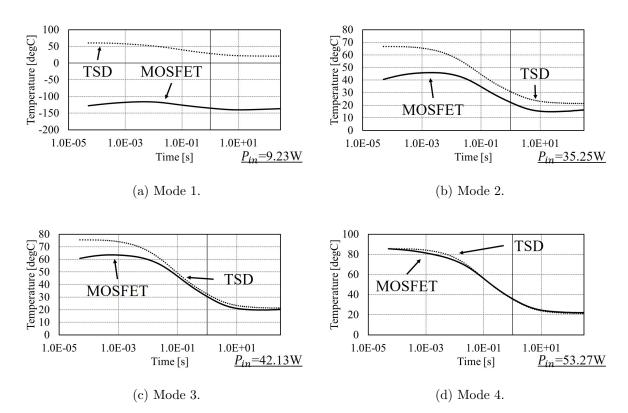

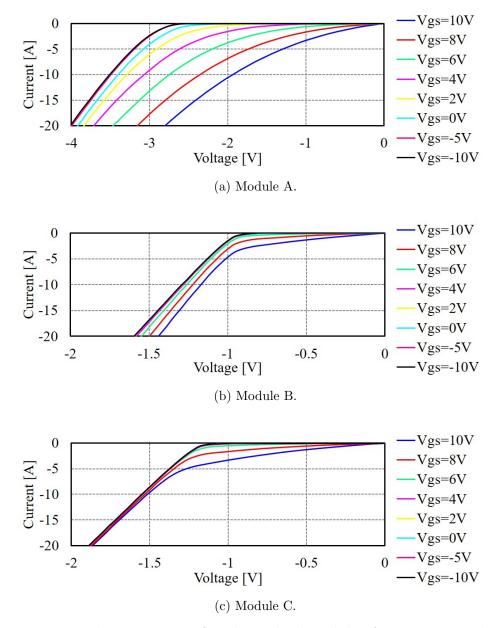

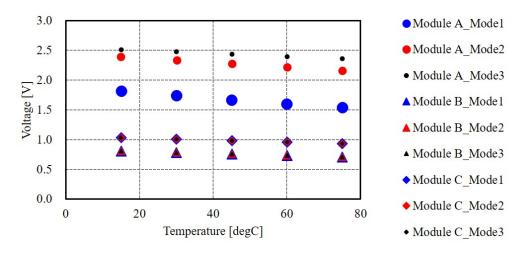

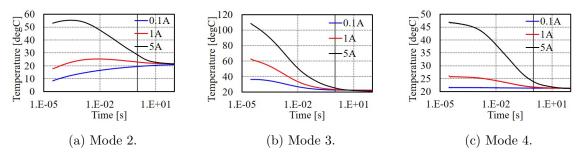

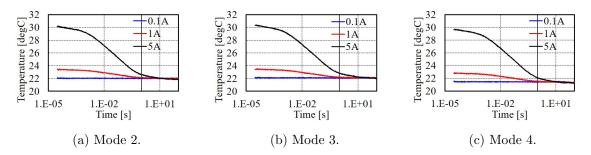

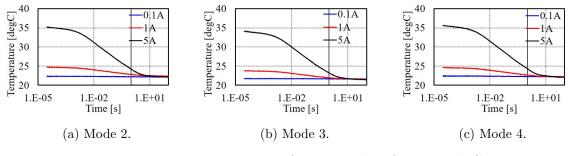

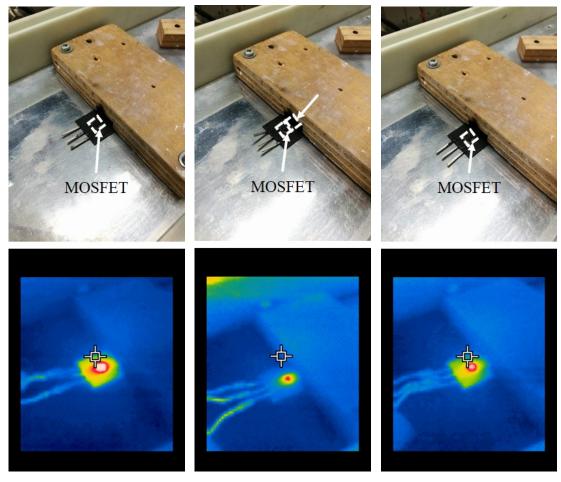

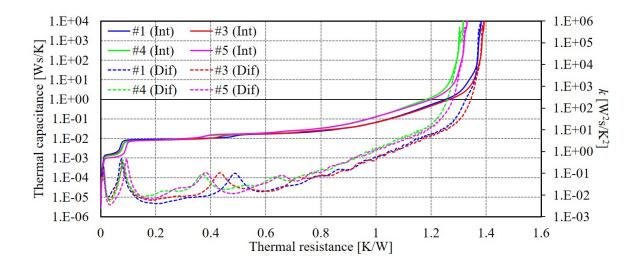

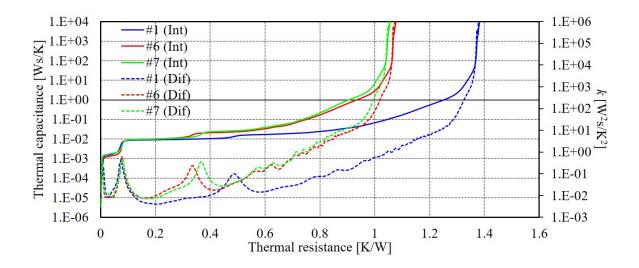

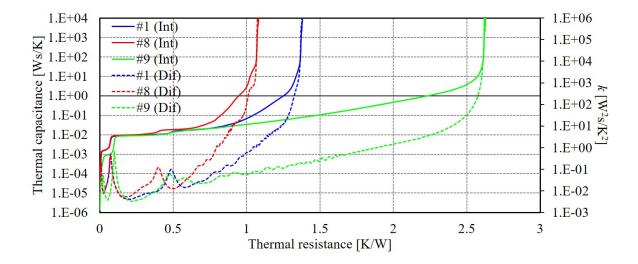

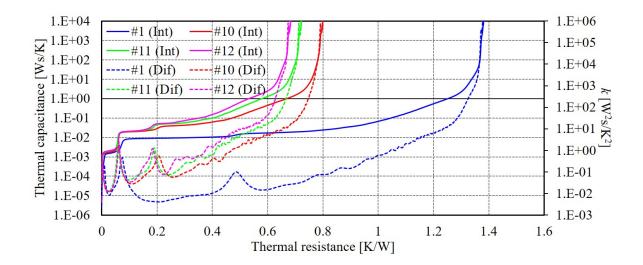

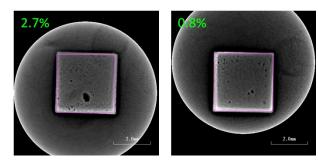

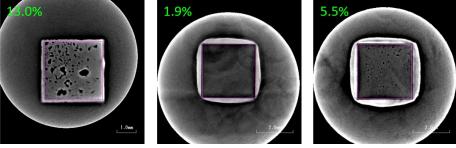

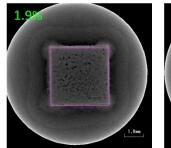

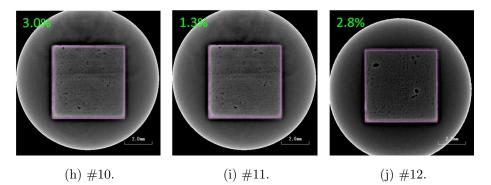

|                                                              |    | Frequency  | Weighted DFT of $da(z)/dz$                                                                                  |