|              |                                                                              |

|--------------|------------------------------------------------------------------------------|

| Title        | Energy-efficient DNN Training with Approximate Computing and Voltage Scaling |

| Author(s)    | 鄭, 泰禹                                                                        |

| Citation     | 大阪大学, 2021, 博士論文                                                             |

| Version Type | VoR                                                                          |

| URL          | <a href="https://doi.org/10.18910/82288">https://doi.org/10.18910/82288</a>  |

| rights       |                                                                              |

| Note         |                                                                              |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# Energy-efficient DNN Training with Approximate Computing and Voltage Scaling

Submitted to

Graduate School of Information Science and Technology

Osaka University

January 2021

TaiYu Cheng

# Publications

## Journal Article (Refereed)

[J1] T. Cheng, Y. Masuda, J. Chen, J. Yu, and M. Hashimoto, “Logarithm-approximate floating point multiplier is applicable to power-efficient neural network training,” *VLSI Integration*, vol. 74, pp. 19-31, 2020.

## International Conference Papers (Refereed)

[I1] T. Cheng, J. Yu, and M. Hashimoto, “Minimizing power for neural network training with logarithm-approximate floating-point multiplier,” in *2019 29th International Symposium on Power and Timing Modeling, Optimization and Simulation (PATMOS)*, Rhodes, Greece, 2019, pp. 91-96.

[I2] T. Cheng, Y. Masuda, J. Nagayama, Y. Momiyama, J. Chen, and M. Hashimoto, “Mode-wise voltage-scalable design with activation-aware slack assignment for energy minimization,” in *2021 25th Asia and South Pacific Design Automation Conference (ASP-DAC)*, accepted, 2021.

## International Conference Papers (Unrefereed)

[C1] Y. Masuda, J. Nagayama, T. Cheng, T. Ishihara, Y. Momiyama, and M. Hashimoto, “Critical path isolation and bit-width scaling are highly compatible for voltage over-scalable design,” in *2021 24th Design, Automation and Test in Europe Conference (DATE)*, accepted, 2021.

# Summary

The proliferation of Artificial Intelligence (AI) has a wide range of impact on the world-wide daily life such as medicine, finance, and even industry. In many AI applications such as image, video, and speech processing, deep neural network (DNN) has been recognized as a vital solution in terms of its high quality and generality. DNN attains astonishing accuracy for tackling non-trivial and complicated Big Data analysis, though, at the cost of high computation. Even inference with a pre-trained DNN model requires considerable computation, and what is more, training stage demands further overwhelming amount of computation.

When pursuing a high-quality and general solution through DNN, we often rely on a large size of data for training in addition to sophisticated, i.e., very deep, DNN models, elevating the amount of parameters and computation. To make matter worse, to stabilize and converge the model parameters, several iterations (epochs) in training phase are indispensable, which elevates the computing cost. Both inference and training algorithms primarily perform matrix multiplication, which consists of a series of MAC (multiply-accumulate) computations. When the size of DNN models and input data increases, the amount of MAC computations also increases. Modern DNN training widely applies GPU in servers or cloud systems. The parallel-computing property of GPU can provide higher bandwidth for large-scale matrix multiplications and contribute to DNN training acceleration. On the other hand, while DNN training accelerates with the aid of GPUs, GPU is substantially a compute-intensive system and also highly demands power. Therefore, solutions for achieving an efficient DNN training scheme could undoubtedly save the resource and cost for many AI applications and facilitate the AI marketing revenue. Meanwhile, since the training quality is the most essential factor for a competitive DNN model, it is challenging yet worth studying to enhance a DNN training efficiency while sustaining its quality.

Besides GPUs, the demands for accommodating training capability in edge terminal servers or mobile ASICs also raise. These platforms have the advantage to provide more local services with privacy preservation. On the other hand, regarding the limited size and tiny-volume battery, developing an efficient training hardware becomes an essential requirement from AI service providers.

Approximate computing (AC) is a set of techniques providing cost-effective tuning knobs that make the applications enhance their efficiency such as speed, power, and area,

at the sacrifice of minor quality loss. DNN is one of the applications highly compatible with AC according to its natural characteristics of error tolerance and resilience. Several AC techniques are already explored to achieve efficiency improvement of DNN but mainly for inference purpose, assuming an accurate pre-trained model is ready. On the other hand, the training result is thought to be more sensitive and susceptible to computation inaccuracy once the DNN structure gets more complex, and then there is always a concern for final training quality once applying too much approximation in training stage. Therefore, the applicability of AC to DNN training is insufficiently explored. Only bit-width scaling (BWS) is majorly studied since it is intuitive and the approximation degree can be controlled gradually.

Due to gradient computation in the back-propagation algorithm, training is performed with a wide dynamic range of values, and therefore, many mainstream systems exploit floating-point (FP) expression for training. To attain sufficient quality, training of modern DNN models conventionally relies on 32-bit FP (FP32). On the other hand, some literatures claim that training with FP32 is more than necessary. While FP16 is recognized with its advantage of high computation and memory efficiencies, it is still controversial whether FP16 can attain the same training quality as FP32 without cooperating with other crafted strategies or techniques. In most of the cases, training with FP16 still requires FP32 to assist some computing that FP16 cannot well cover. Experimental results reproduced in this work reveal that the precision of FP16 training has not been well certified if tackling new real-world datasets or applications. The results also indicate that when there are only two choices of FP32 and FP16, it is difficult to well balance the quality and efficiency.

Voltage scaling (VS) is a general means to reduce the power dissipation of integrated circuits in a quadratic manner, whereas AC is effective for applications possessing inherent error tolerance. However, the delay of logic gates would increase and the circuits become risky to occur timing error as the voltage decreases. In order to achieve aggressive voltage scaling while preventing the timing errors, activation-aware slack assignment (ASA) is proposed to reallocate the timing margin for timing critical paths that might be activated during the operation. The previous works of ASA introduce mean-time-to-failure (MTTF) analysis regarding the timing error as stochastic events. MTTF-aware ASA can aggressively scale down the voltage for power reduction at the cost of allowing less but not zero timing error. Though ASA is thought effective, the previous works did not provide a methodology to maximize its benefit with guaranteeing no timing errors, which restricts its generality and consequently application domains. Then, an interesting question is raised; how much can ASA benefit VS efficiency with ensuring no timing errors?

This dissertation aims at providing a design methodology to achieve energy minimization for DNN training with useful implementation techniques. First, to reduce the primary MAC computation in training with FP, this work proposes to use logarithm-approximate multiplier (LAM) for training. By approximating float-point multiplica-

---

tion to cheap fixed-point addition, the NN training engine is expected to be implemented with smaller delay, fewer gates, and lower power consumption. With a dedicated hardware for NN training engine and a 2-D classification dataset, this dissertation demonstrates that LAM-based training can achieve 10% speed-up, 2.3X power and area improvement, respectively, compared with traditional training with FP32 exact computation. In addition, LAM also reveals its high compatibility with conventional BWS. If LAM is applied to NN where BWS is already implemented, LAM and BWS can enjoy synergy effect and up to 4.9X power reduction is attained with sacrificing up to 1% accuracy loss. Also, the processor level design can exploit the advantage of LAM. An experimental GPGPU embedded with LAM executing a NN training workload presents 28% power reduction improvement and the improvement reaches 41% with LAM + BWS. Finally, LAM is qualified for deeper-layer NN training. Up to four hidden layers, LAM- based training yields the same level of accuracy as training with accurate multipliers, even with aggressive BWS.

Next, this dissertation addresses the disadvantage of non-zero timing error risk involved in conventional ASA methods and provide a design applying to mode-wise voltage-scaling (MWVS) design with enhancing ASA benefit on VS efficiency yet guaranteeing zero timing errors. First, the MWVS design is formulated as an optimization problem that minimizes the overall power consumption considering each mode duration, as well as the achievable voltage reduction, and accompanied circuit overhead. The proposed method explores the solution space with the downhill simplex algorithm (DSA). To attain a solution, i.e., a design, the feature of multi-corner multi-mode (MCMM) in a commercial tool is exploited to perform mode-wise ASA, where the ASA is realized by assigning with sets of false paths specialized for individual modes to obtain the maximum voltage scaling for each mode. Experimental results based on a popular RISC-V hardware design show that the proposed MWVS design can save 20% more energy compared with the conventional VS approach and acquire 15% more gain compared with single-mode ASA. In addition, the cycle-by-cycle fine-grained false paths identification is also proposed and it successfully reduced 42% leakage power.

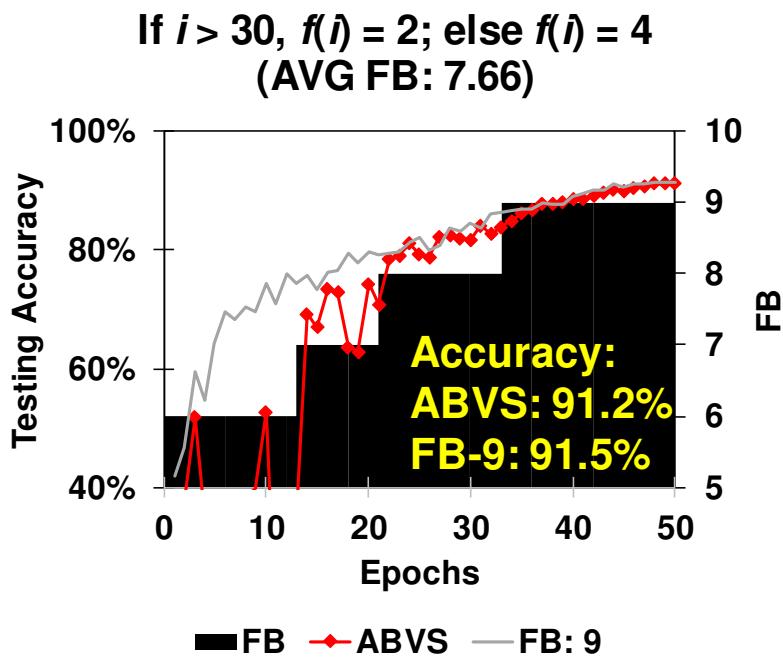

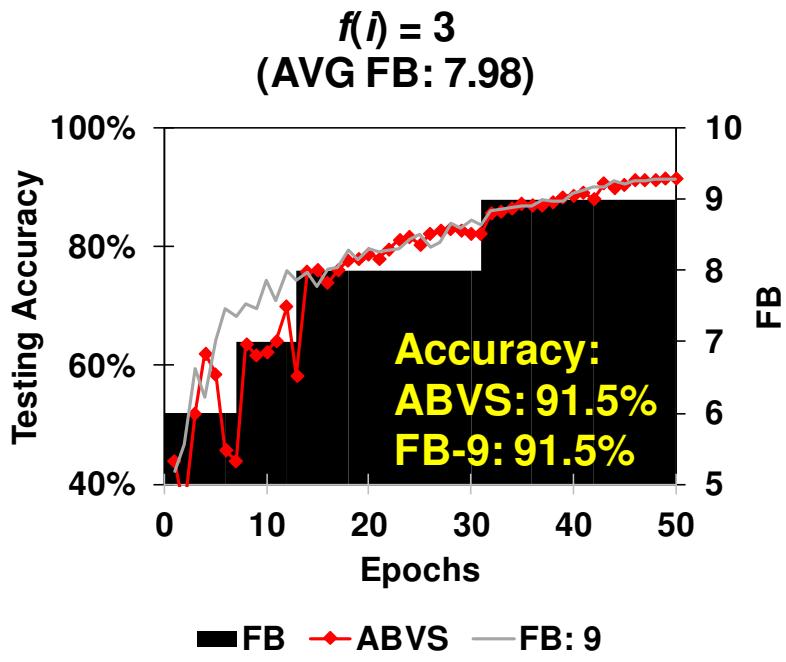

Finally, this dissertation provides an overall scheme for minimizing NN training energy as the main contribution of this work and gave it a name as adaptive bit-width and voltage scaling (ABVS) which can leverage the FP units with configurable bit-width. The key idea is that the NN training starts with smaller fraction bit-width (FB), and then FB is gradually increased depending on present training quality during the training phase. Since smaller FB possesses shorter latency, this training scheme can concurrently adapt the bit-width and voltage scaling and hence intensify energy reduction. Experimental results across a various scale of training datasets and DNN applications reveal that the proposed ABVS flow in training can achieve the comparable training quality as FP32, but up to 62% energy reduction, and at most 37% reduction even compared with the training under the least sufficient FB, with at most 0.5% quality loss. This work also gave an explanation of why ABVS works in modern DNN training. Furthermore,

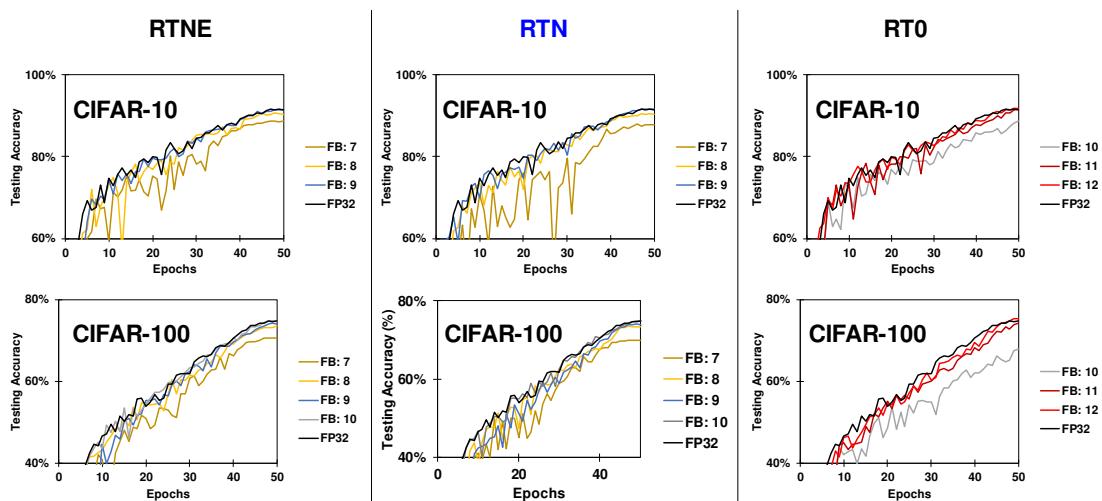

the investigation of different rounding schemes is conducted. Results show that conventional round-to-the-nearest (RTNE) provides better trade-off between training quality and energy efficiency than round-to-zero (RT0).

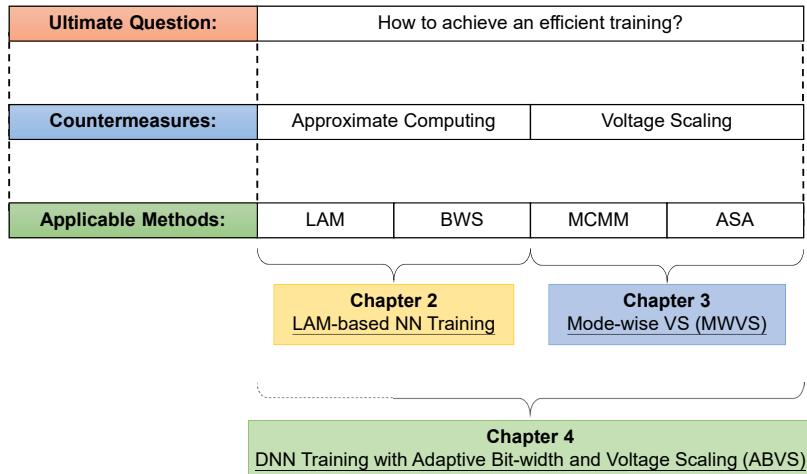

Overall, this dissertation seeks for achieving energy minimization with two main countermeasures, “approximate computing” and “voltage scaling.” LAM and BWS techniques are exploited in this work as the former, while MWVS belonging to the latter combines MCMM and ASA to achieve further voltage reduction. The ABVS flow can be recognized as an integrated solution for all the aforementioned strategies. In addition, all the methods apply to GPUs and the dedicated ASICs for achieving efficient DNN training.

# Acknowledgments

First of all, I would like to express my deepest gratitude to Professor Masanori Hashimoto in Osaka University for providing me a precious opportunity and an excellent environment to study as a doctoral student in his laboratory. All of my productive researches are credited to none other than him. His advanced perspective and thoughtful advise led me to the achievements.

I would like to appreciate Associate Professor Hiromitsu Awano in Kyoto University, Professor Katsuyoshi Miura and Associate Professor Ittetsu Taniguchi in Osaka University for detailed reviews and insightful suggested comments.

I would like to appreciate Associate Professor Jaehoon Yu in Tokyo Institute of Technology, Assistant Professor Yutaka Masuda in Nagoya University, Dr. Jun Chen for their precious suggestions and enormous help throughout my doctoral research.

My appreciation also goes to Mr. Yoichi Momiyama, Mr. Jun Nagayama in Sкционext Inc. for technical discussions and suggestions.

I would like to thank other colleagues who belong or belonged to the Integrated System Design Laboratory in Osaka University for daily discussions and their support: Dr. Wang Liao in Kochi University of Technology, Dr. Koichi Mitsunari, Dr. Ryutaro Doi, Mr. Ryo Shirai, Mr. Pei-Hao Chen, Miss Yangchao Zhang, Mr. Dehua Liang. I express my heartfelt thanks to all members of Integrated System Design Laboratory in Osaka University for having an interesting and comfortable time in the laboratory. I would like to thank Mrs. Asako Murakami and Mrs. Naoko Isozaki for her various support. I would like to thank Japan-Taiwan Exchange Association to provide me a big financial support so I can enjoy my time for the daily life in Japan. I also would like to thank all of my friends for having good times.

Finally, I give my thank to family (Father, Mother, younger brother) for supporting my livelihood, and sincerely thank to my dear girl friend, Miss Yu-Ting Lin to cheer me for studying abroad and support me for pursuing this degree.

# Contents

|          |                                                                       |           |

|----------|-----------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                   | <b>1</b>  |

| 1.1      | Background . . . . .                                                  | 1         |

| 1.2      | Basics of Neural Networks . . . . .                                   | 5         |

| 1.3      | Energy-efficient DNN Training . . . . .                               | 10        |

| 1.4      | Approximate Computing to NN . . . . .                                 | 11        |

| 1.4.1    | Software-level AC Techniques . . . . .                                | 13        |

| 1.4.2    | Architecture-level AC Techniques . . . . .                            | 13        |

| 1.4.3    | Hardware-level AC Techniques . . . . .                                | 13        |

| 1.5      | Low-power Design Methodology: Voltage Scaling . . . . .               | 15        |

| 1.6      | Challenge for Realizing Efficient Training Engine . . . . .           | 19        |

| 1.6.1    | AC to Achieve Computation Reduction . . . . .                         | 19        |

| 1.6.2    | DNN Training with FP16 . . . . .                                      | 19        |

| 1.6.3    | ASA to Increase Timing Margin . . . . .                               | 20        |

| 1.7      | Objective of this Dissertation . . . . .                              | 23        |

| <b>2</b> | <b>Logarithm-Approximate-Multiplier-based (LAM-based) NN Training</b> | <b>27</b> |

| 2.1      | Introduction . . . . .                                                | 27        |

| 2.2      | Previous work on Logarithm-based Multipliers . . . . .                | 28        |

| 2.3      | Introduction of Logarithm-approximate Multiplier (LAM) . . . . .      | 30        |

| 2.3.1    | Floating-point Multiplication . . . . .                               | 30        |

| 2.3.2    | Logarithm-approximate Multiplier . . . . .                            | 31        |

| 2.4      | Evaluation for Dedicated Hardware Design . . . . .                    | 37        |

| 2.4.1    | LAM Performance . . . . .                                             | 37        |

| 2.4.2    | Experimental Setup for NN Training . . . . .                          | 37        |

| 2.4.3    | Evaluation for FOURCLASS Dataset . . . . .                            | 39        |

| 2.4.4    | Evaluation for Higher Dimensional Datasets . . . . .                  | 41        |

| 2.5      | Evaluation in GPU Design . . . . .                                    | 45        |

| 2.5.1    | LAM-based GPU Implementation on FPGA . . . . .                        | 45        |

| 2.5.2    | Measurement Results . . . . .                                         | 47        |

| 2.6      | Evaluations for Deeper NN Models . . . . .                            | 50        |

| 2.7      | Conclusion . . . . .                                                  | 54        |

|                                                                                          |            |

|------------------------------------------------------------------------------------------|------------|

| <b>3 Mode-wise Voltage Scaling</b>                                                       | <b>55</b>  |

| 3.1 Introduction . . . . .                                                               | 55         |

| 3.2 Previous Work . . . . .                                                              | 57         |

| 3.2.1 Mode-wise ASA . . . . .                                                            | 57         |

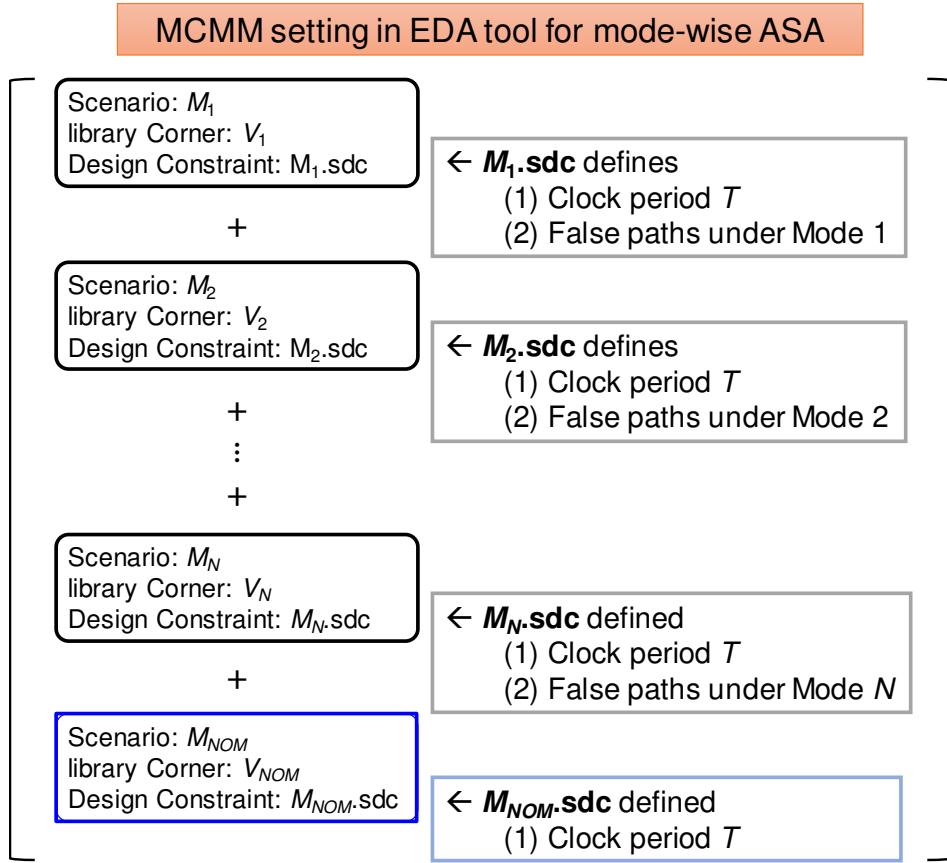

| 3.2.2 MCMM . . . . .                                                                     | 57         |

| 3.3 Problem Formulation for MWVS . . . . .                                               | 58         |

| 3.4 Proposed Design Methodology for MWVS . . . . .                                       | 61         |

| 3.4.1 Downhill Simplex Algorithm (DSA) . . . . .                                         | 61         |

| 3.4.2 Integrating Mode-wise ASA into MCMM Flow . . . . .                                 | 63         |

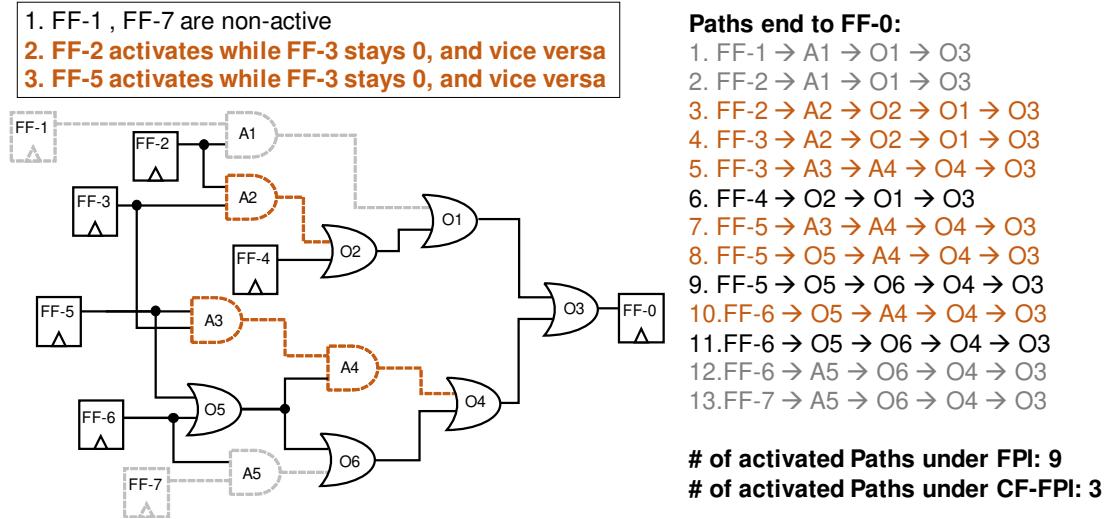

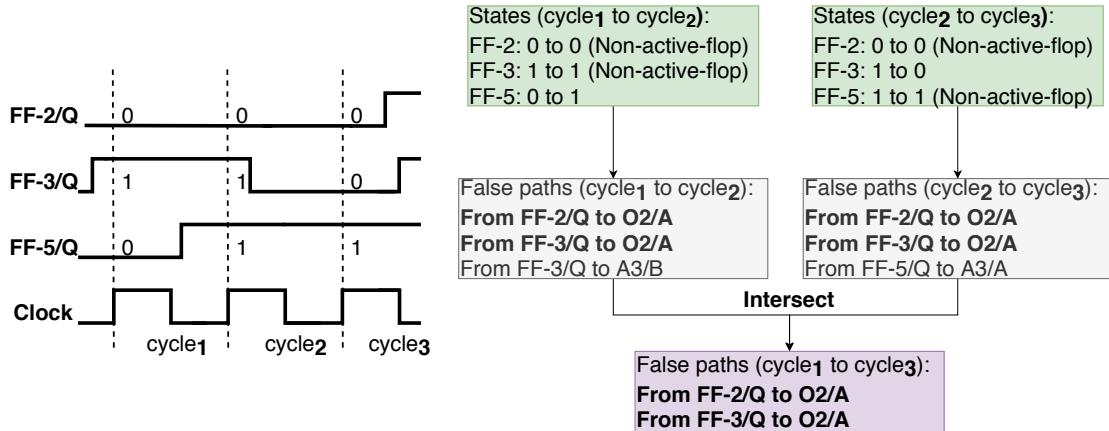

| 3.4.3 False Path Identification . . . . .                                                | 64         |

| 3.5 Experimental Results and Analysis . . . . .                                          | 70         |

| 3.5.1 Setup . . . . .                                                                    | 70         |

| 3.5.2 Results . . . . .                                                                  | 70         |

| 3.5.3 Proposed Methodology Investigation . . . . .                                       | 72         |

| 3.6 Conclusion . . . . .                                                                 | 76         |

| <b>4 DNN Training with Adaptive-Bit-width-and-Voltage-Scaling (ABVS)</b>                 | <b>77</b>  |

| 4.1 Introduction . . . . .                                                               | 77         |

| 4.2 Previous Work . . . . .                                                              | 79         |

| 4.3 Proposed ABVS Scheme for DNN Training . . . . .                                      | 80         |

| 4.4 Experimental Results . . . . .                                                       | 82         |

| 4.4.1 Evaluation Strategy and Experimental Setup . . . . .                               | 82         |

| 4.4.2 FB Reduction by ABVS . . . . .                                                     | 84         |

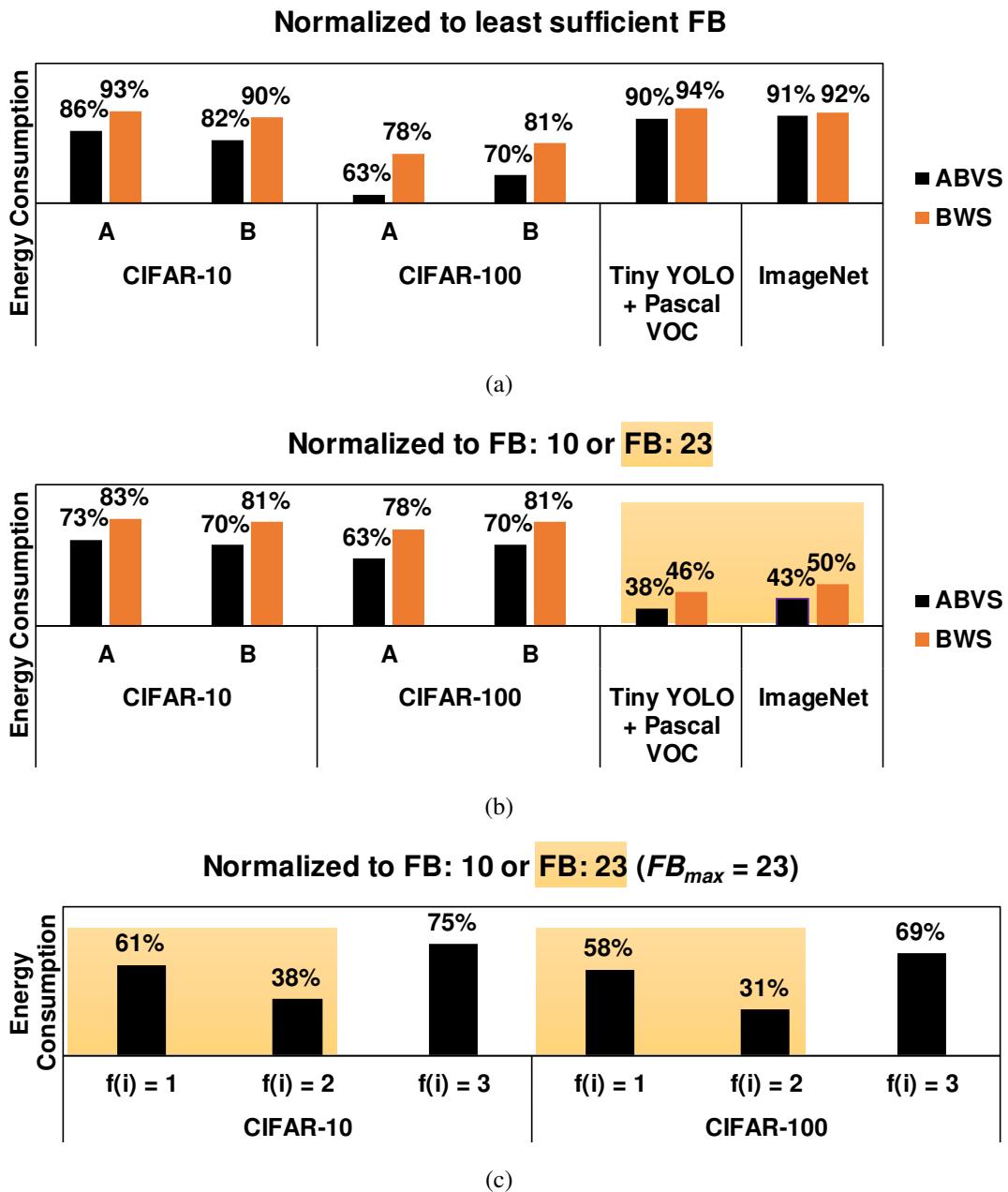

| 4.4.3 Energy Reduction by ABVS . . . . .                                                 | 86         |

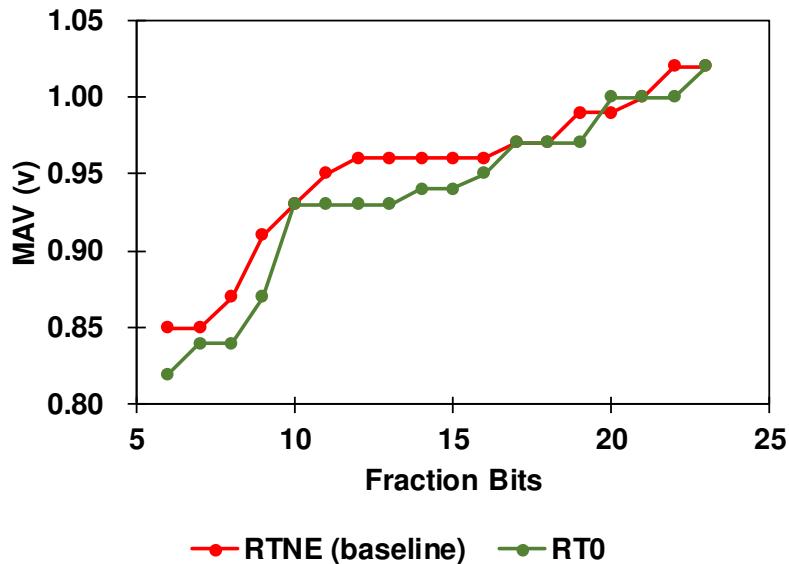

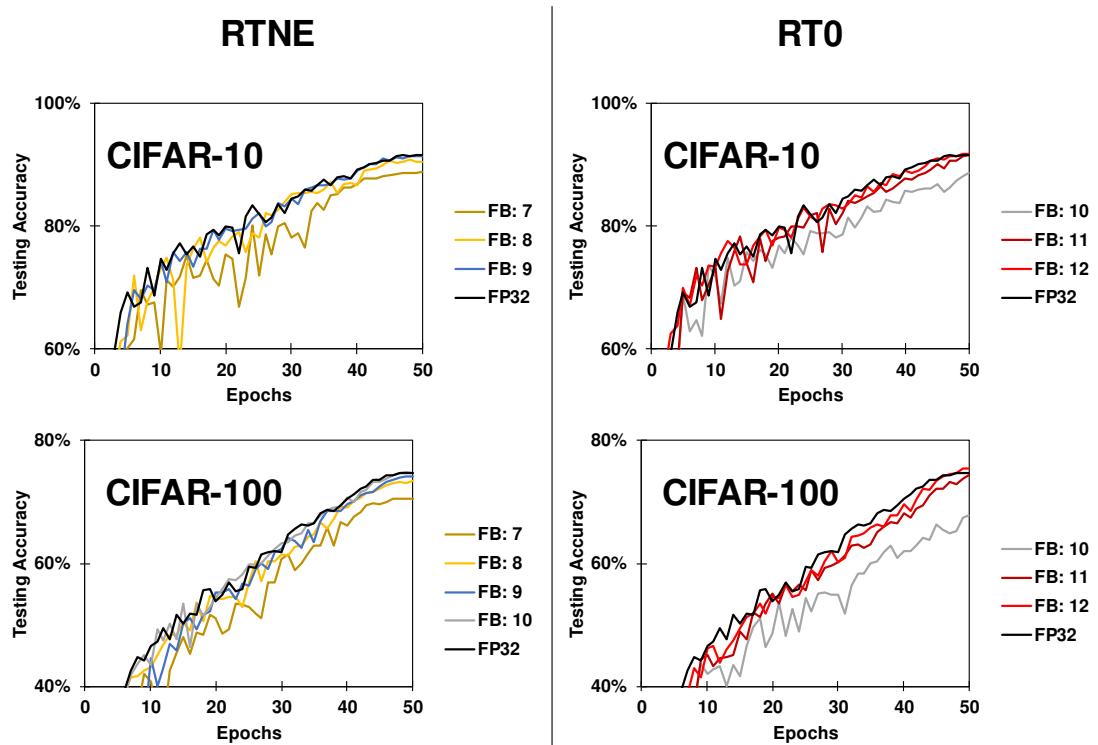

| 4.4.4 Rounding Methods . . . . .                                                         | 88         |

| 4.4.5 Potential Solution for More Area-efficient FB-configurable FP-MAC Design . . . . . | 88         |

| 4.5 Conclusion . . . . .                                                                 | 100        |

| <b>5 Conclusion</b>                                                                      | <b>101</b> |

# List of Figures

|      |                                                                                                                                                                                                                                              |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Market size/revenue comparison for artificial intelligence worldwide from 2015 to 2025. . . . .                                                                                                                                              | 2  |

| 1.2  | Accuracy vs. number of layers in DNN for ImageNet classification (#training dataset: 1.3 million). Empirically, models with more layers achieve higher accuracy. . . . .                                                                     | 3  |

| 1.3  | Annual size of real-time data in the global datasphere. The Global Datasphere quantifies and analyzes the amount of data created, captured, and replicated in any given year across the world. . . . .                                       | 4  |

| 1.4  | Prediction error and power consumption of hardware platform. . . . .                                                                                                                                                                         | 5  |

| 1.5  | Feed-forward neural network. (a) is a schematic of a feed-forward neural network with 1 hidden layer. (b) and (c) are the schematics for illustrating forward- and back-propagation at the $a$ -th neuron in $i$ -th layer. . . . .          | 8  |

| 1.6  | Distribution density of gradients observed when a NN is trained for MNIST dataset. $x$ -axis represents the gradients in log scale with base 2, and $y$ -axis is the normalized distribution density. . . . .                                | 9  |

| 1.7  | Different coverage of value for fixed-point and floating-point data format. . . . .                                                                                                                                                          | 9  |

| 1.8  | Categories of the area in energy-efficient training. . . . .                                                                                                                                                                                 | 11 |

| 1.9  | Framework of AC. . . . .                                                                                                                                                                                                                     | 12 |

| 1.10 | Schematic of the AVS techniques. . . . .                                                                                                                                                                                                     | 17 |

| 1.11 | Concept schematic for applying ASA (a) VS before ASA and (b) VS after ASA. . . . .                                                                                                                                                           | 18 |

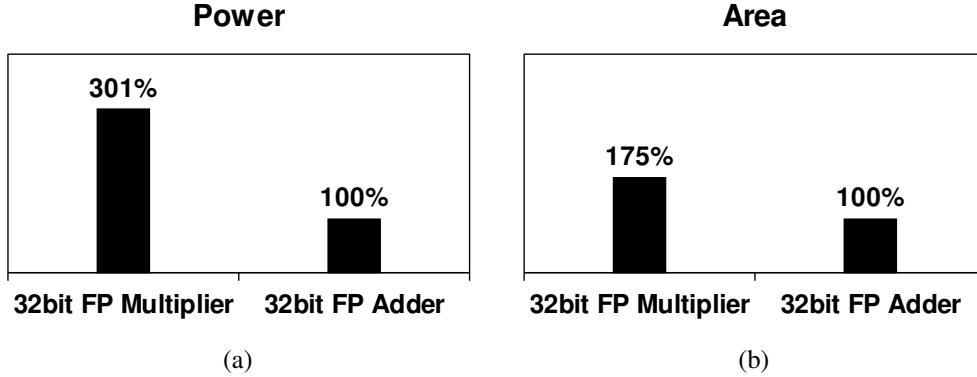

| 1.12 | Hardware benchmarking for 32-bit floating-point multiplier and adder synthesized with Nangate 45nm cell library for the same clock frequency. Both (a) power and (b) area values are normalized by those of the adder, respectively. . . . . | 20 |

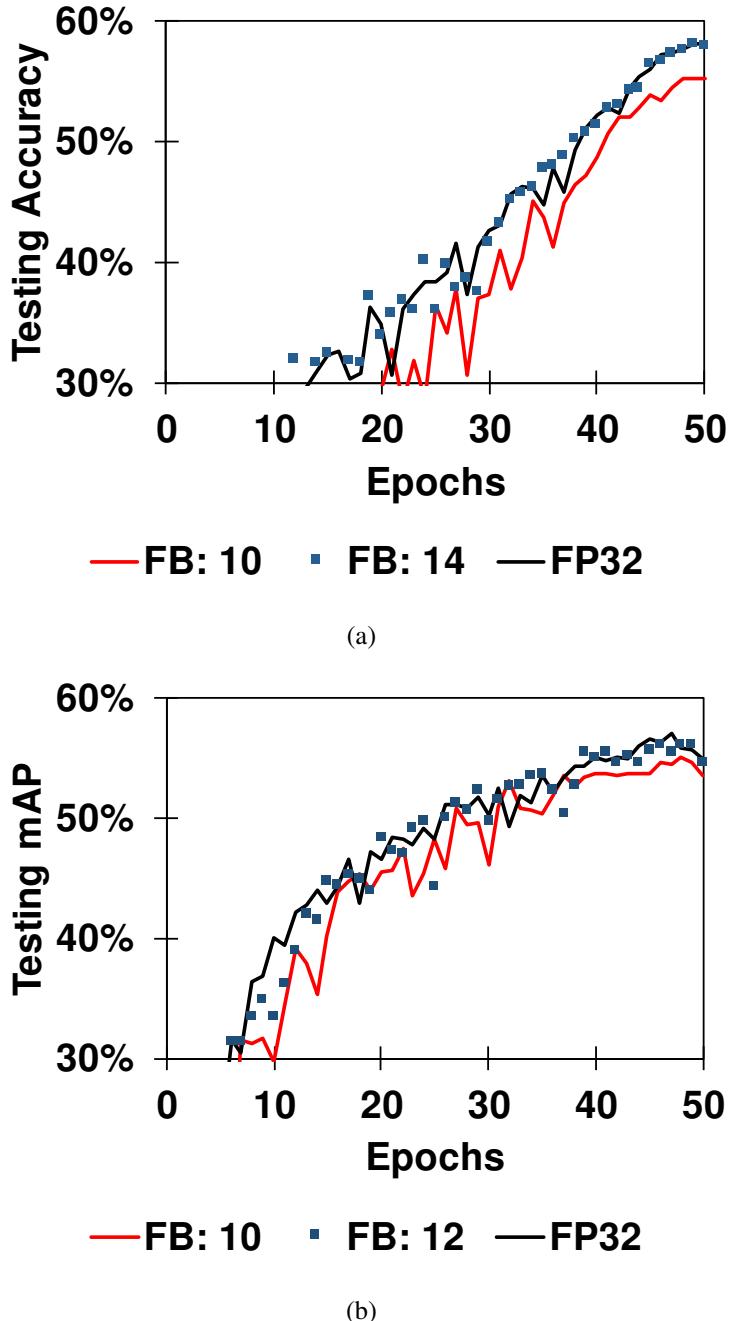

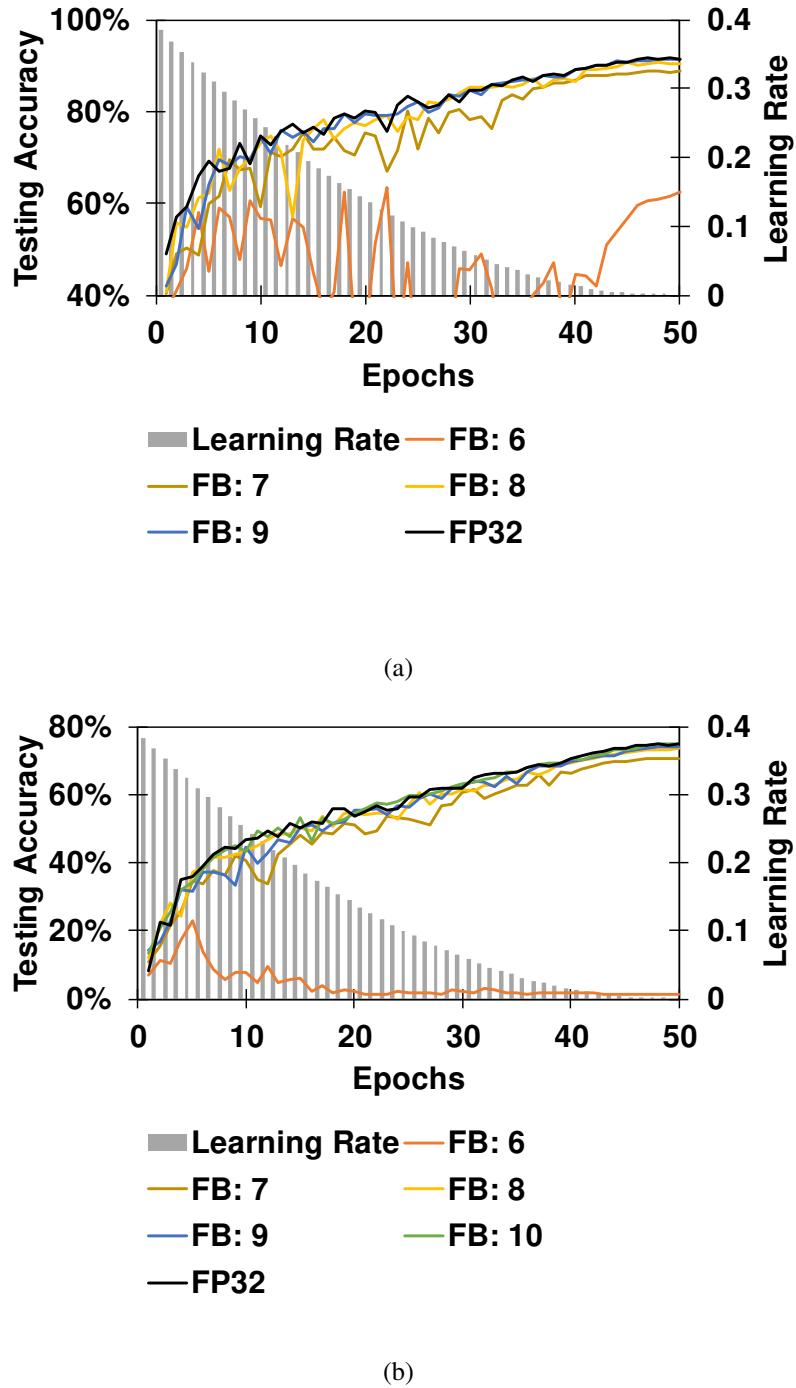

| 1.13 | FP16 precision (FB: 10) cannot guarantee its training quality to be comparable with FP32 one for (a) ImageNet (image classification) and (b) Pascal VOC (object detection). . . . .                                                          | 21 |

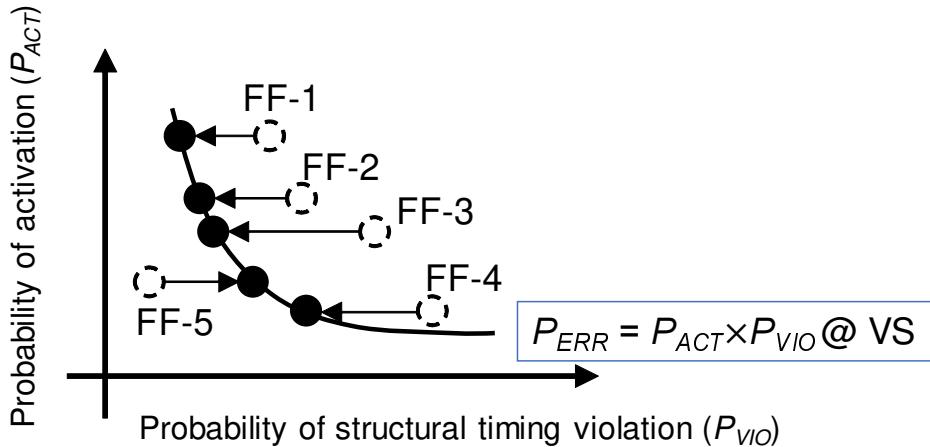

| 1.14 | Timing margin for each FF is determined such that $P_{ERR}$ is constraint while individual $P_{ACT}$ values are different. . . . .                                                                                                           | 23 |

|                                                                                                                                                                                                                                                                                                                                          |    |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

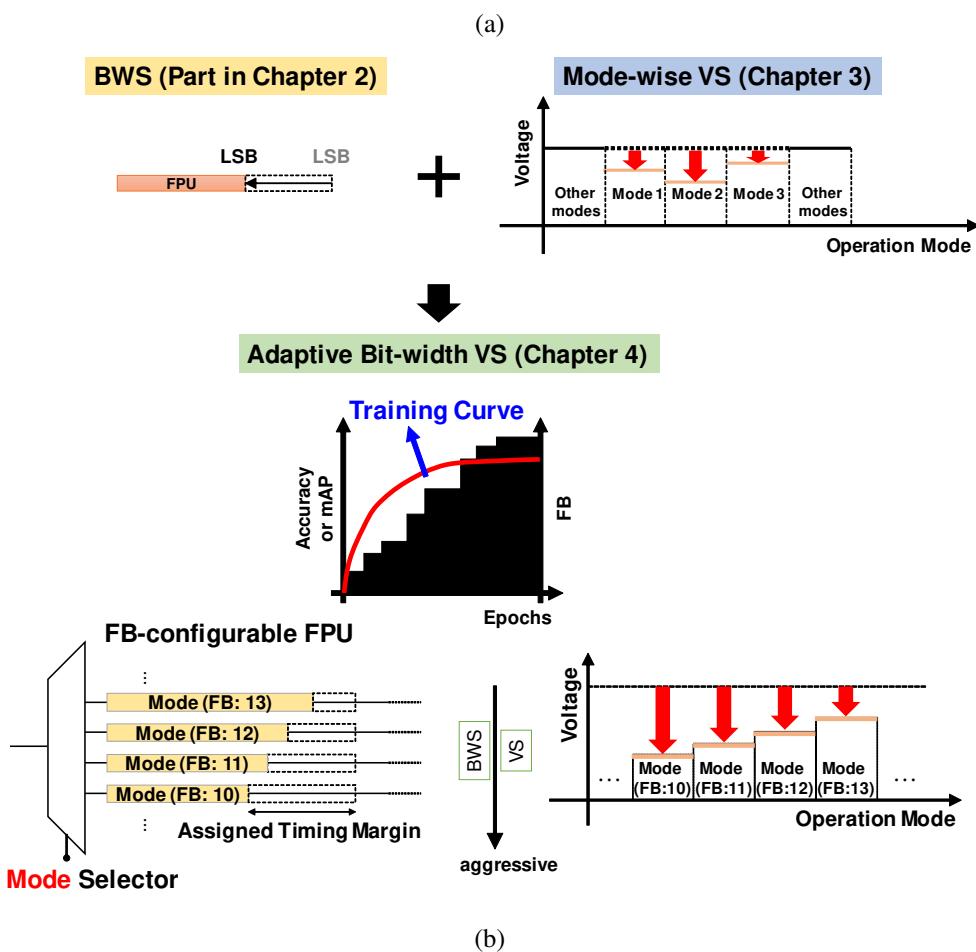

| 1.15 (a) Overall organization of this dissertation. (b) Connections of key ideas between the chapters. . . . .                                                                                                                                                                                                                           | 26 |

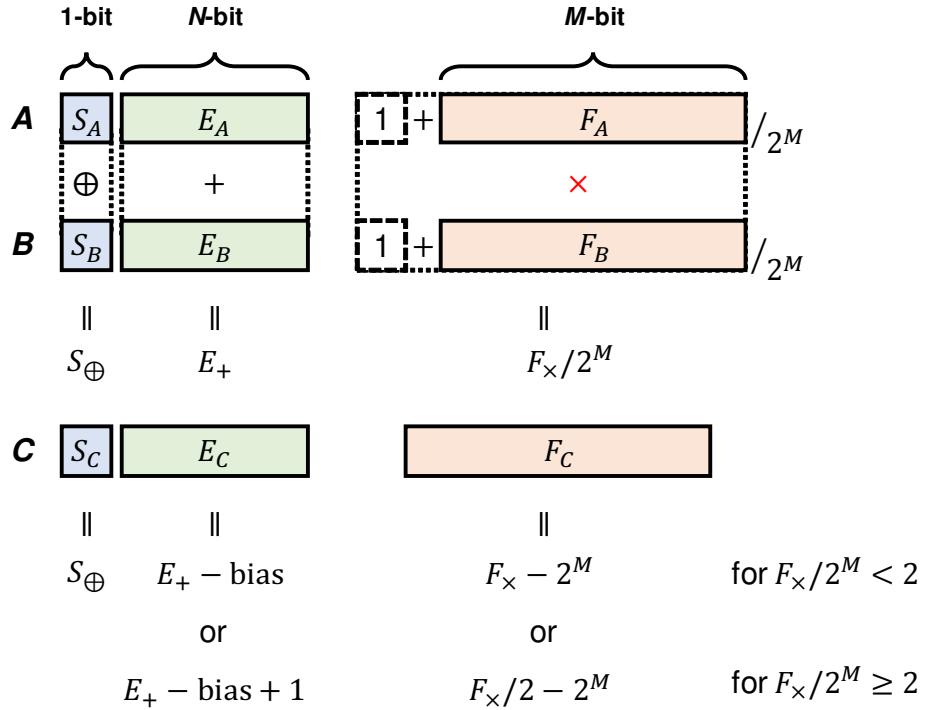

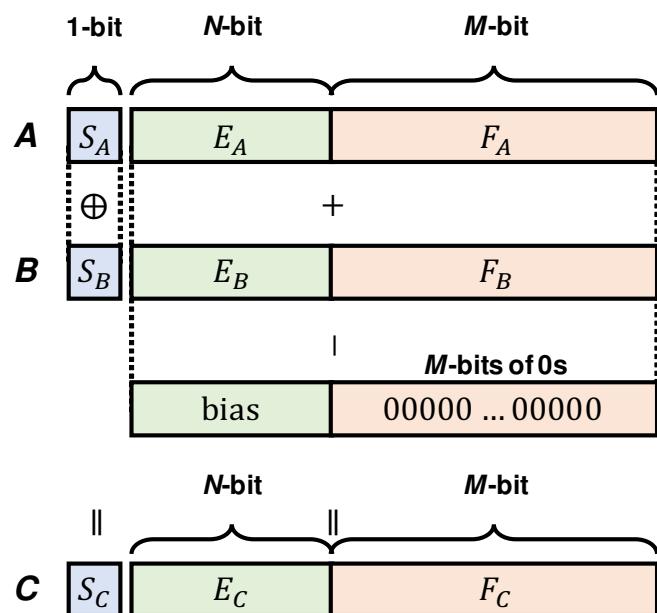

| 2.1 Operation of exact floating-point multiplier. ( $S_{\otimes}, E_+, F_{\times}$ ) are individually calculated by XOR, addition, and multiplication based on the sign, exponent, and fraction part of multiplicand and multiplier, respectively. Then, $E_C$ and $F_C$ are the conditional formula according to $F_{\times}$ . . . . . | 31 |

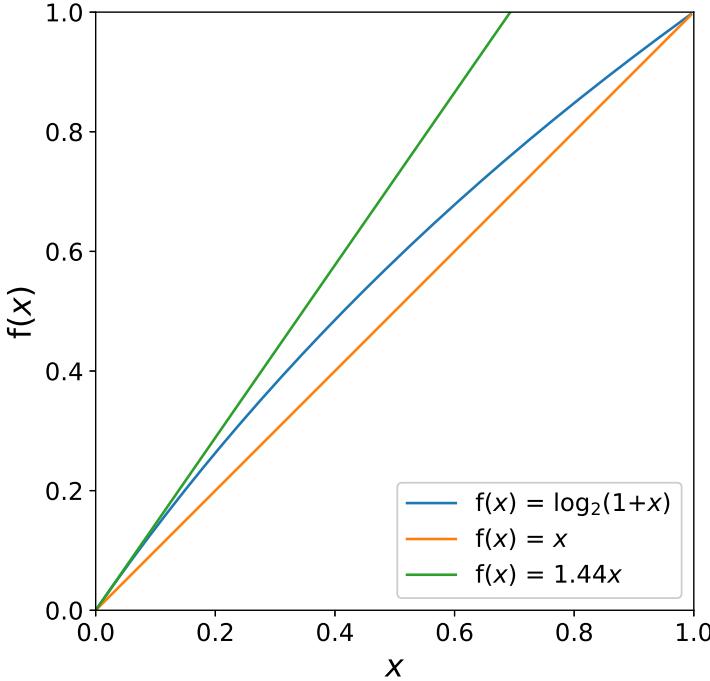

| 2.2 Curves of functions $\log_2(1 + x)$ , $1.0x$ , and $1.44x$ . Taking into the entire range of $0 \leq x \leq 1$ , $1.0x$ is a possible approximation of $\log_2(1+x)$ , while $1.44x$ is better at the point of $x = 0$ . . . . .                                                                                                     | 32 |

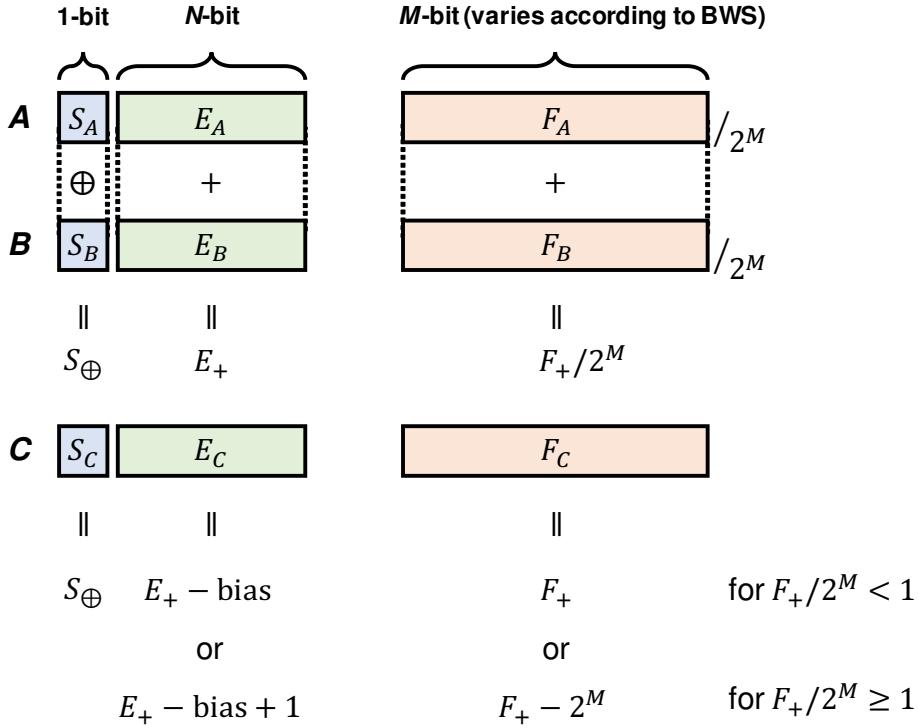

| 2.3 Operation of logarithm-approximate multiplier (LAM). $S_{\otimes}$ and $E_+$ are identical to those of the exact floating-point multiplier, but $F_+$ is directly computed by adding the fractions without making their mantissas. $E_C$ and $F_C$ are expressed by the conditional formula regarding $F_+$ . . . . .                | 34 |

| 2.4 Algorithm for implementing LAM in hardware. $E_A$ and $F_A$ are concatenated, and $E_B$ and $F_B$ as well. Then, directly sum up them and subtract the bias term that is followed by $M$ -bits of 0s to compute $E_C$ and $F_C$ . . . . .                                                                                            | 35 |

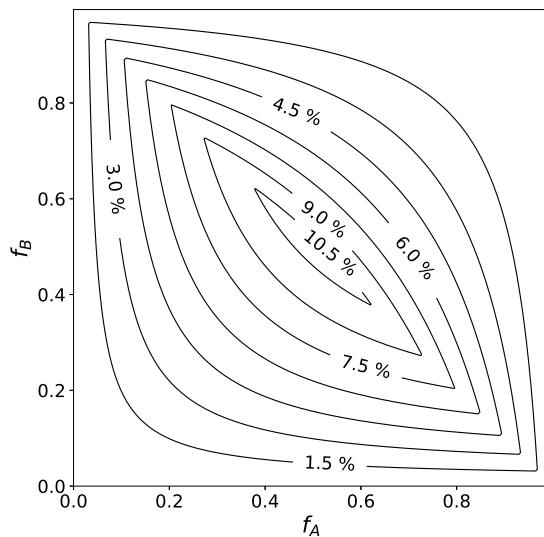

| 2.5 Contour plot of <i>ErrLAM</i> , which represents the relative approximation error between LAM and exact floating-point multiplier. The error depends on the fraction values ( $f_A, f_B$ ) of the multiplicand $A$ and multiplier $B$ under base-2 scientific notation, where $0 \leq f_A, f_B < 1$ . . . . .                        | 36 |

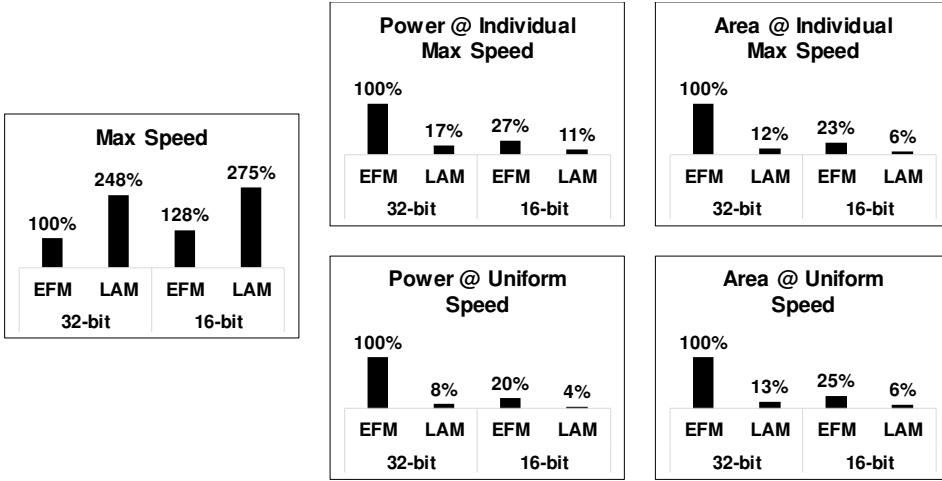

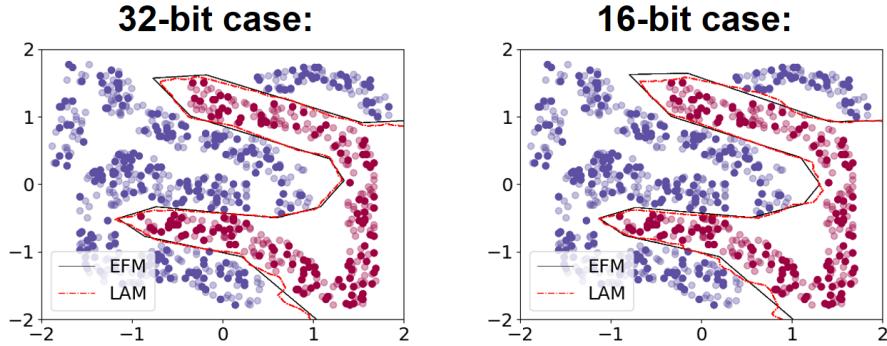

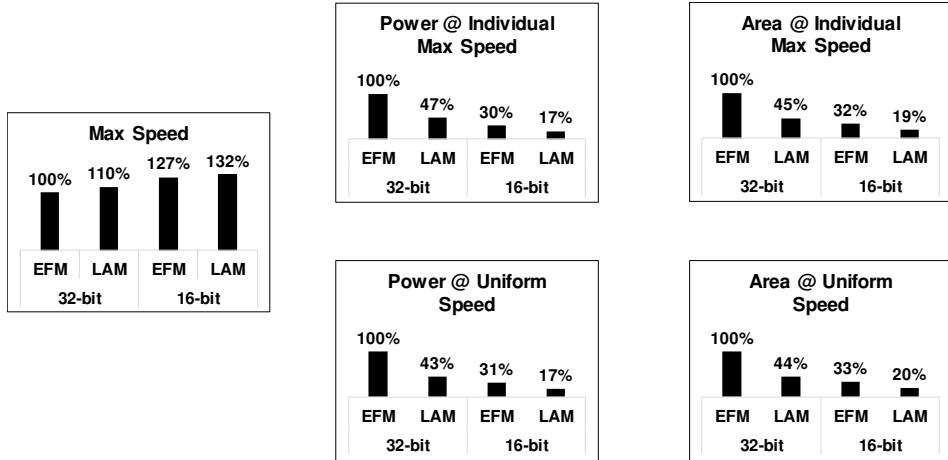

| 2.6 Speed, power, and area benchmarking for synthesized LAM and EFM. There is one speed comparison and two scenarios for power and area under the max speed circuit or the uniform speed circuit. All the values are normalized to EFM 32-bit case. . . . .                                                                              | 38 |

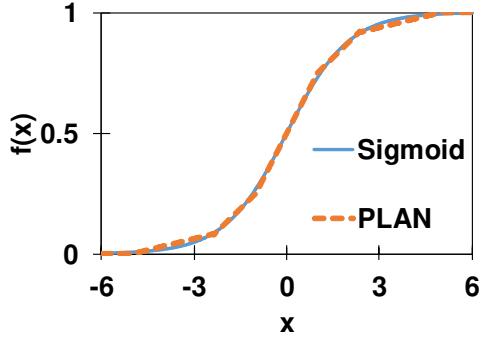

| 2.7 PLAN function, an approximate form of Sigmoid function. (a) Expression of PLAN and (b) Plot of original Sigmoid and PLAN functions. . . . .                                                                                                                                                                                          | 39 |

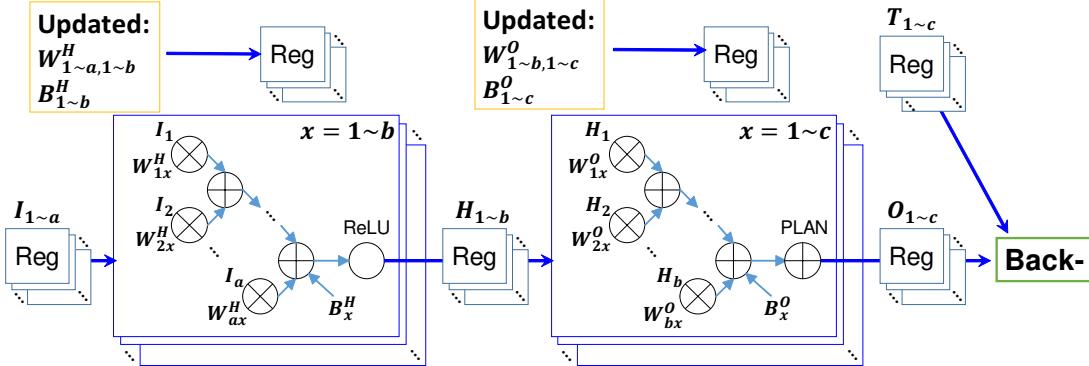

| 2.8 Diagram of the dedicated NN training hardware implemented in this work, including forward-, back-, and updating blocks. $\otimes$ and $\oplus$ denote multipliers and adders, respectively. All the $\otimes$ and $\oplus$ are spatially implemented at the same time. . . . .                                                       | 40 |

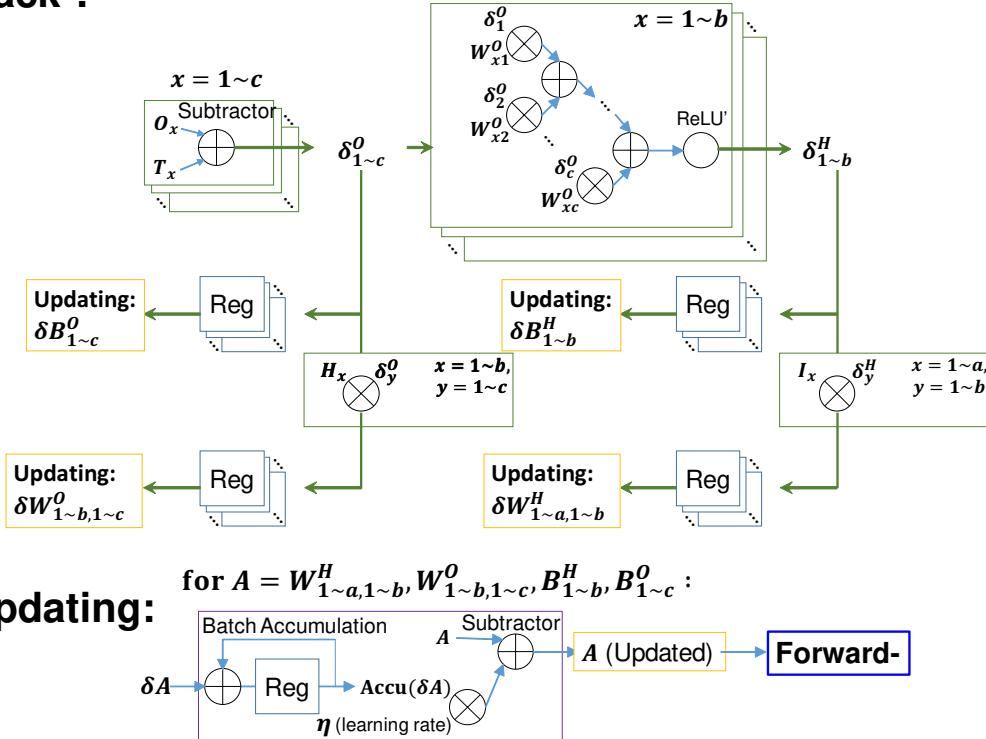

| 2.9 Boundaries trained for 2-D classification FOURCLASS. . . . .                                                                                                                                                                                                                                                                         | 41 |

| 2.10 Speed, power, and area comparisons between synthesized LAM-based and EFM-based training engines. The synthesis setup is identical to that of Fig. 2.6, and all the values are normalized by those of EFM 32-bit case. . . . .                                                                                                       | 41 |

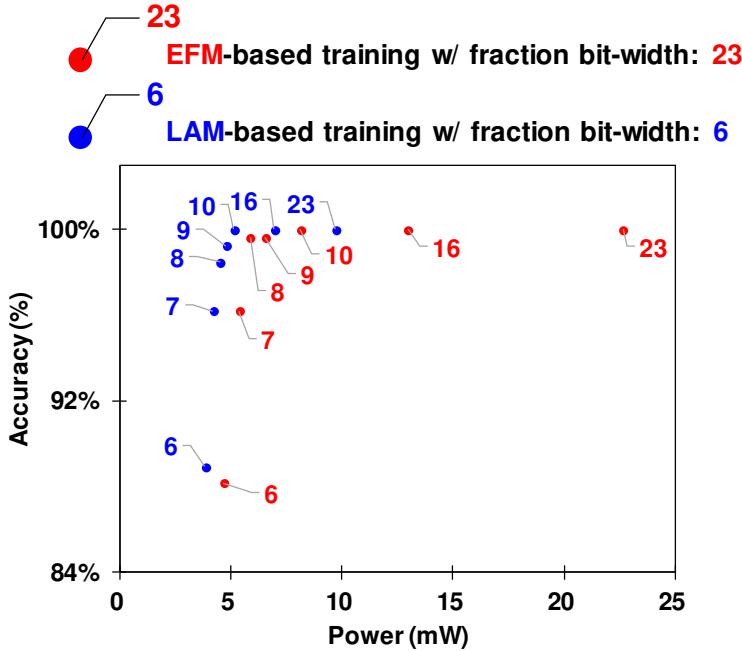

| 2.11 Accuracy vs power for synthesized LAM-based and EFM-based training engines, where the numbers marked on the points means the FBs. The synthesis setup is identical to that of Fig. 2.6. . . . .                                                                                                                                     | 42 |

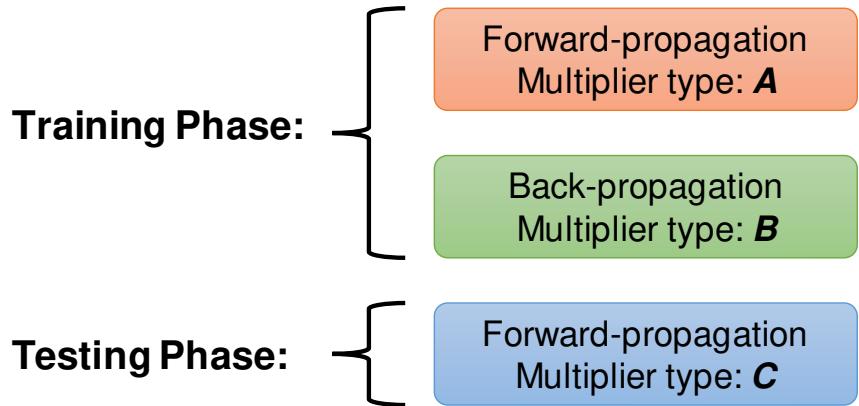

| 2.12 Different approximation strategies that use EFM and/or LAM in training and testing phases. . . . .                                                                                                                                                                                                                                  | 43 |

---

|      |                                                                                                                                                                                                                                    |    |

|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

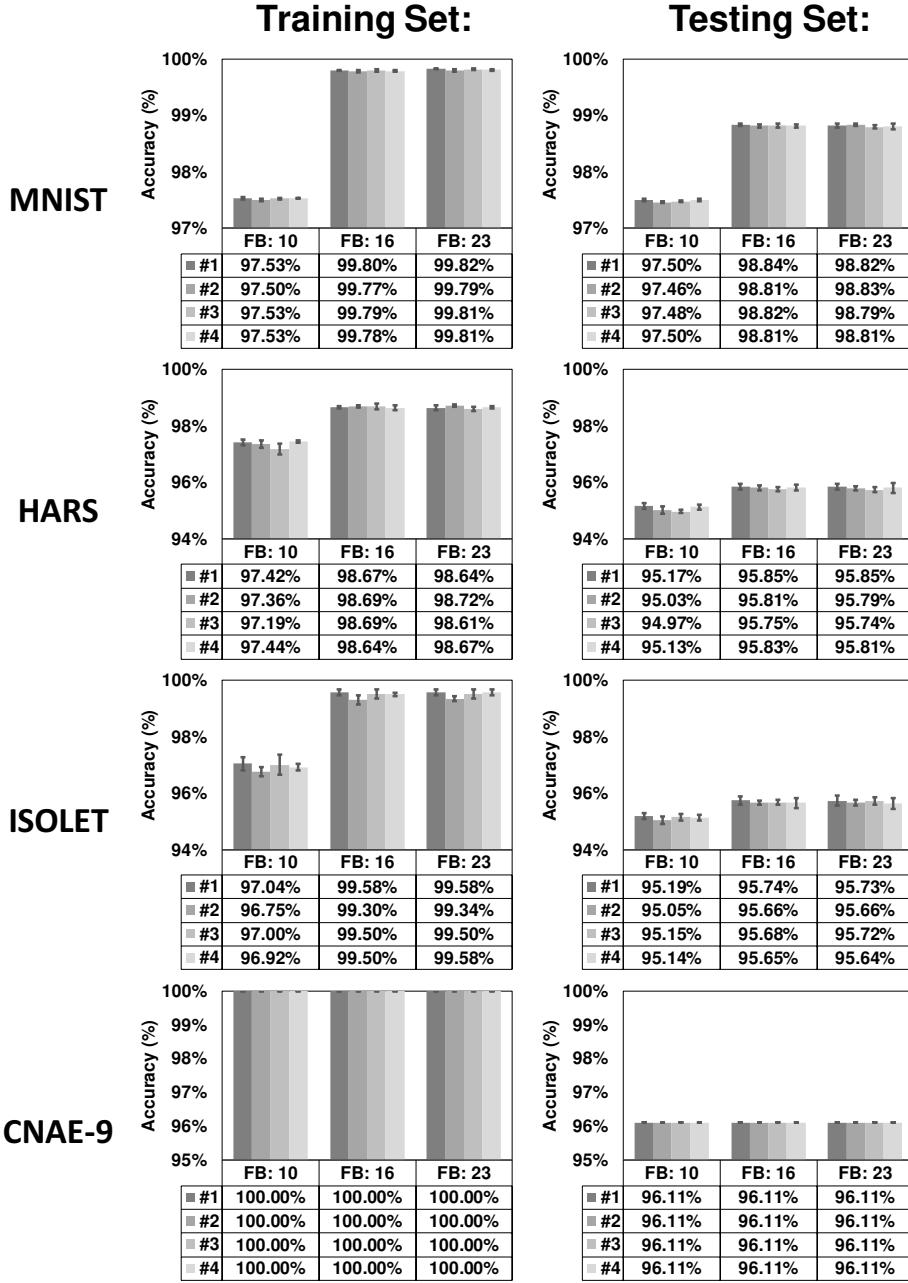

| 2.13 | Training results for MNIST, HARS, ISOLET, CNAE-9 under different approximation strategies illustrated in Fig. 2.12 for the FB = 10, 16, and 23, with plotting the average accuracies and the ranges of min-max difference. . . . . | 44 |

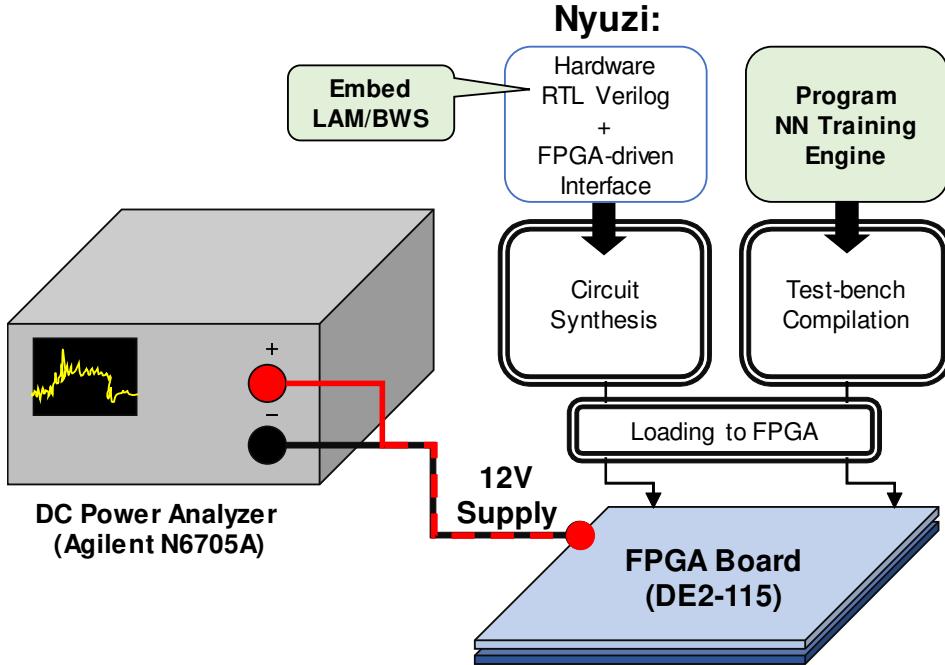

| 2.14 | Flow for measuring power of LAM (and LAM+BWS) based Nyuzi on FPGA. . . . .                                                                                                                                                         | 46 |

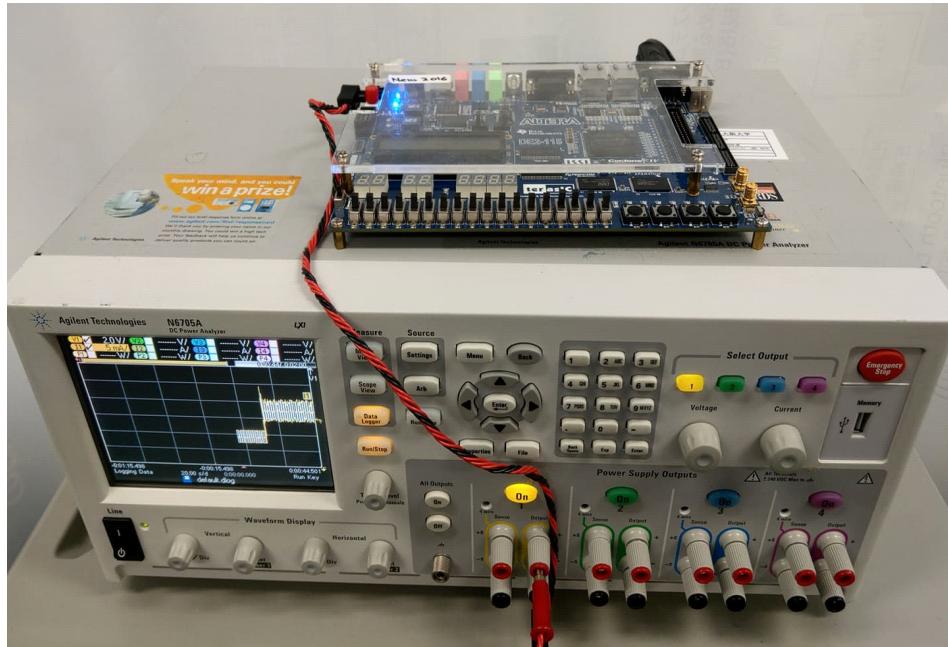

| 2.15 | Photo for power measurement setup of Nyuzi processor. The FPGA board is placed on the DC power analyzer. The power analyzer is used for voltage supply and power measurement. . . . .                                              | 47 |

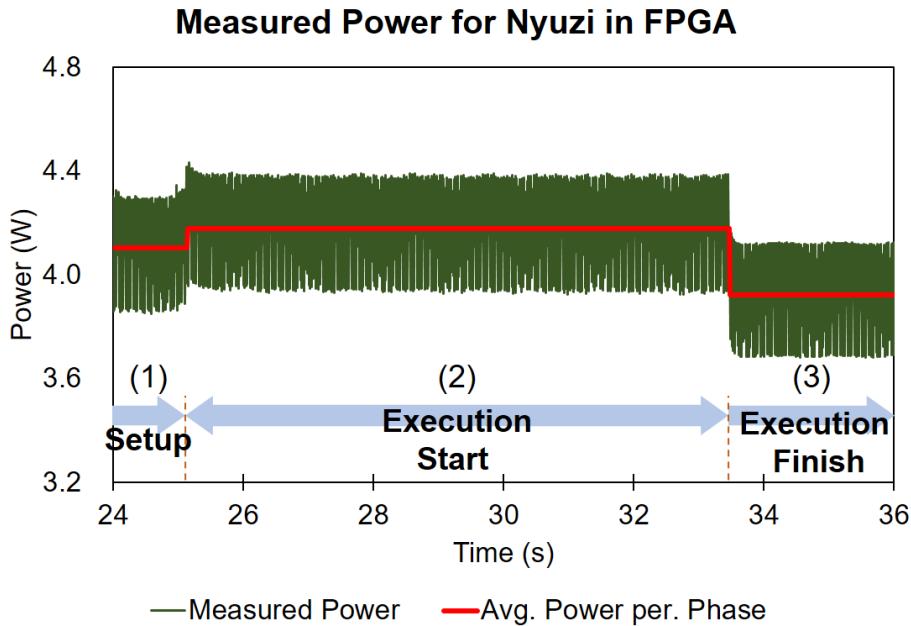

| 2.16 | Transient power response measured during Nyuzi operation. Phase (2) is the phase for executing NN training program. In Phase (3), the training process already finished. . . . .                                                   | 48 |

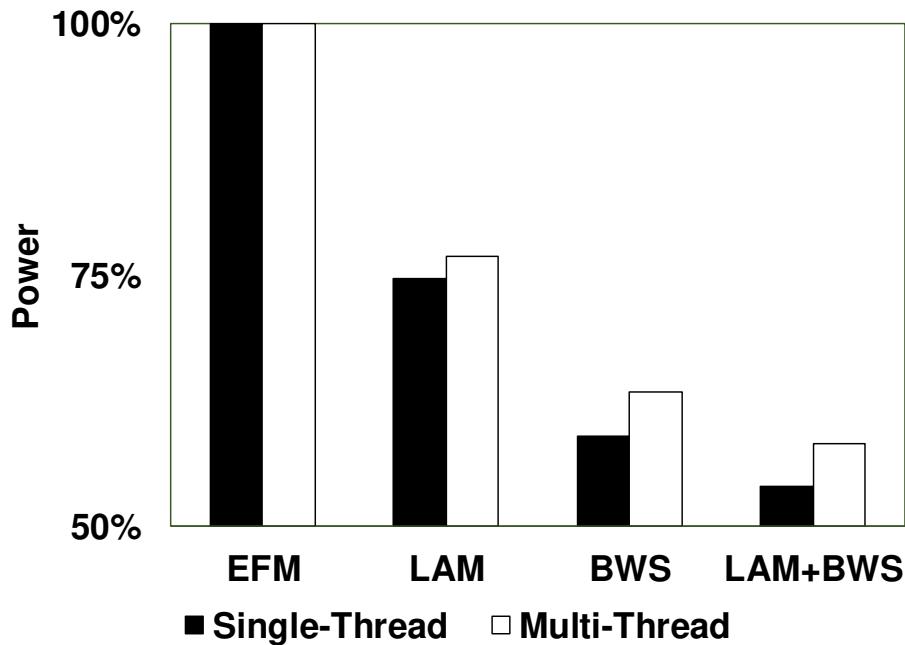

| 2.17 | Power measurement results for single-thread and multi-thread (FOUR-CLASS dataset). All the values are normalized to EFM case. . . . .                                                                                              | 48 |

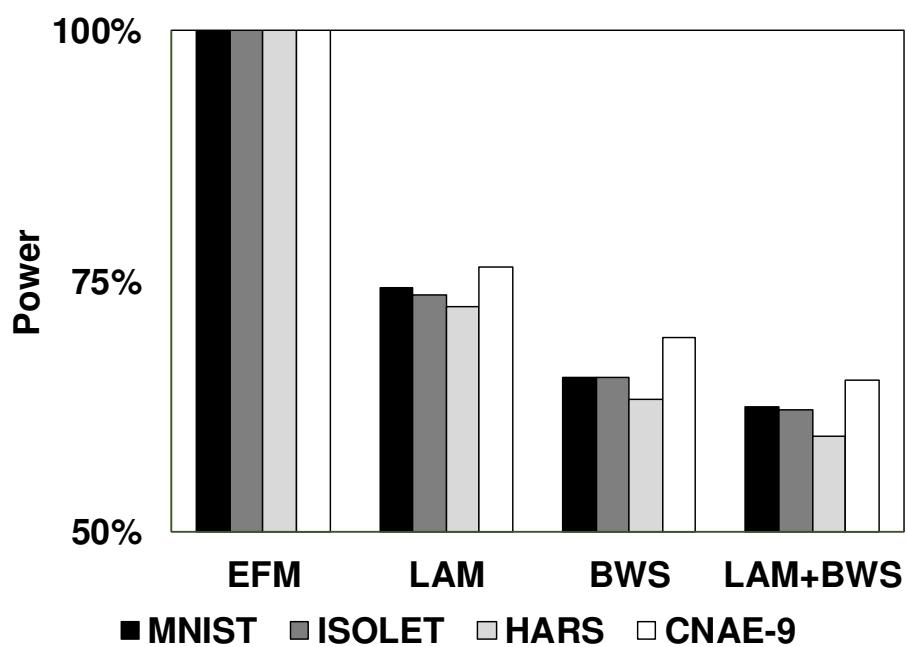

| 2.18 | Power measurement results for MNIST, HARS, ISOLET, CNAE-9 datasets. All the values are normalized to EFM case. . . . .                                                                                                             | 49 |

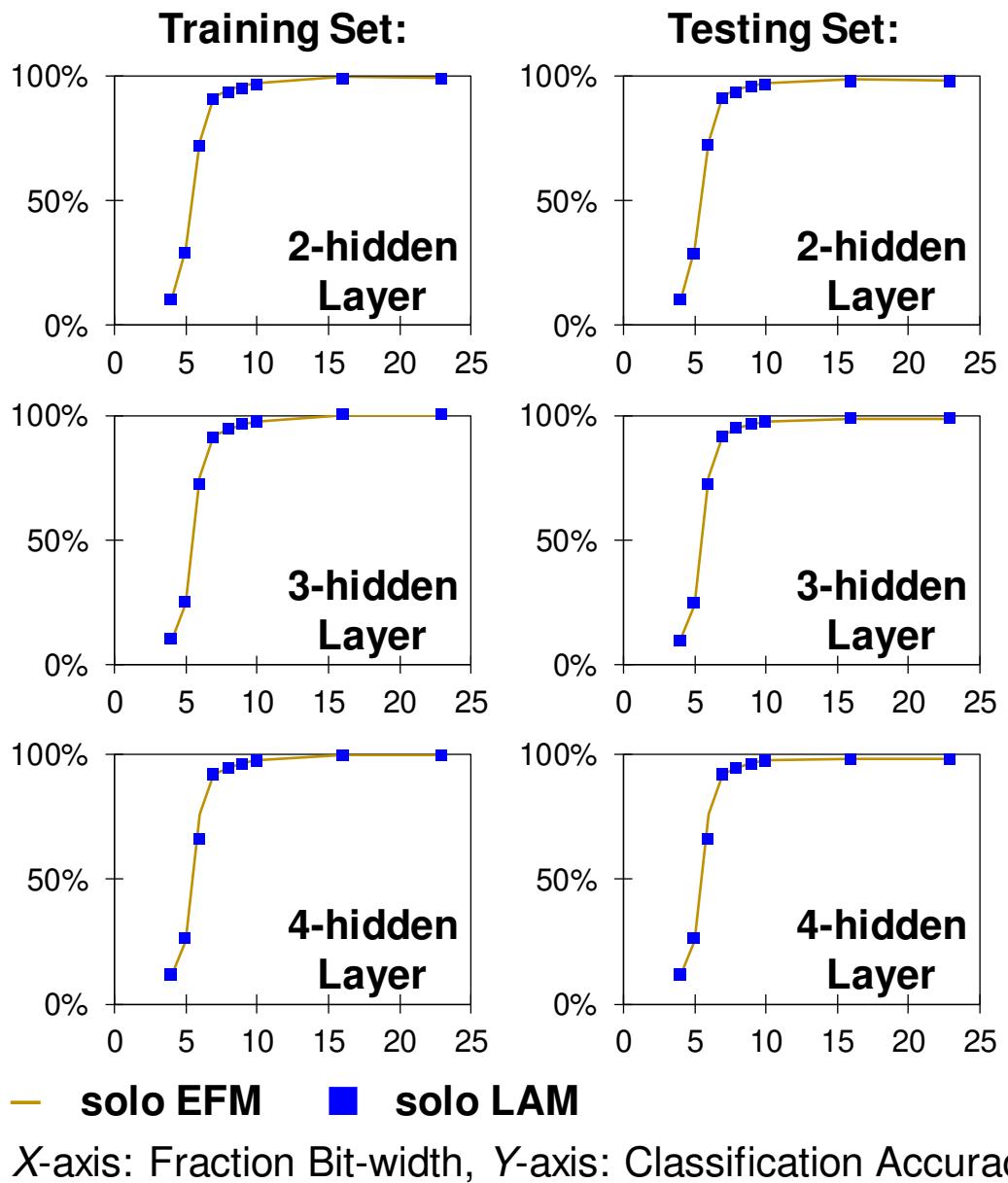

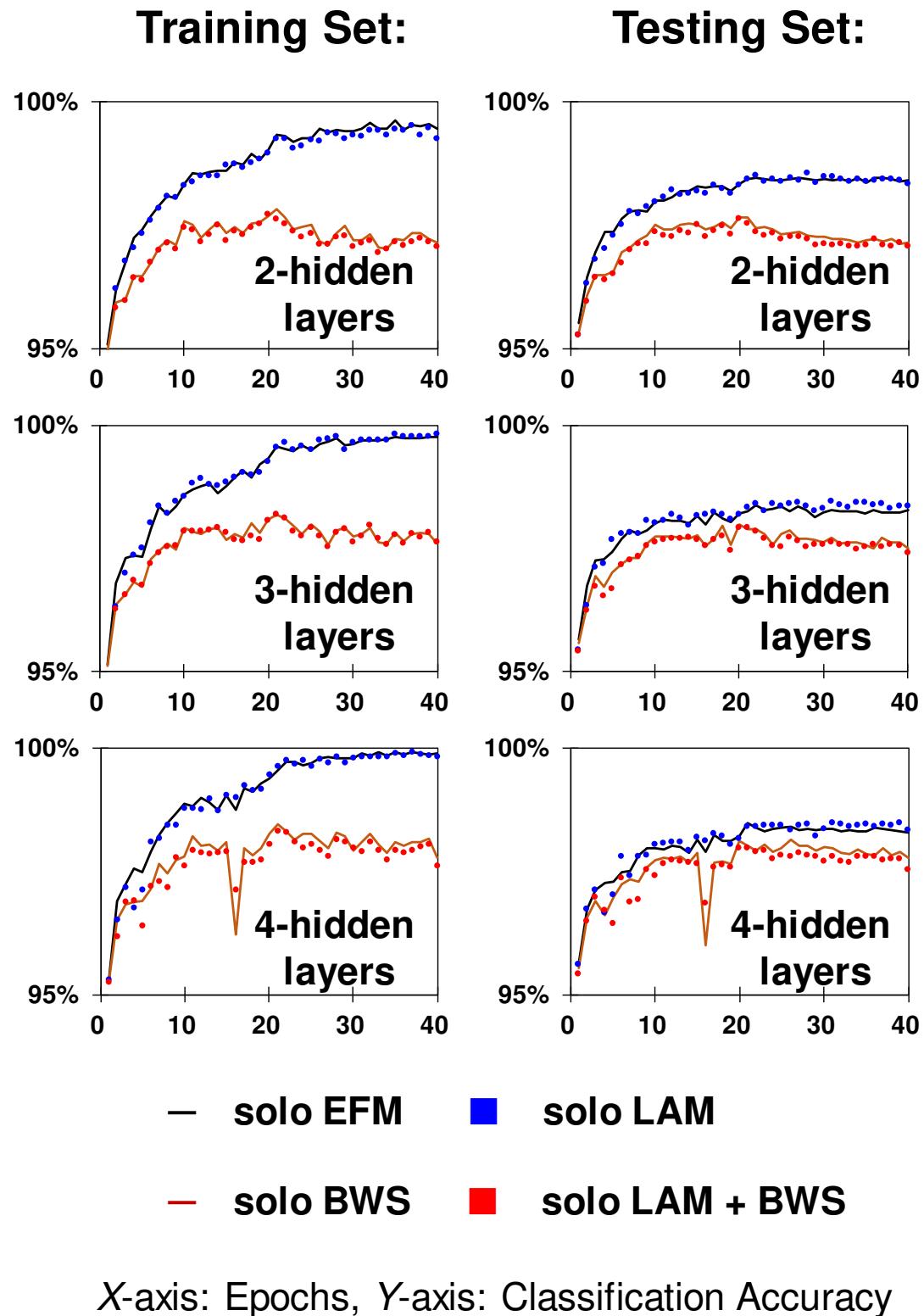

| 2.19 | MNIST training results for NNs having 2, 3, and 4 hidden layers and various fraction bits. The attained accuracies are almost identical. . . .                                                                                     | 51 |

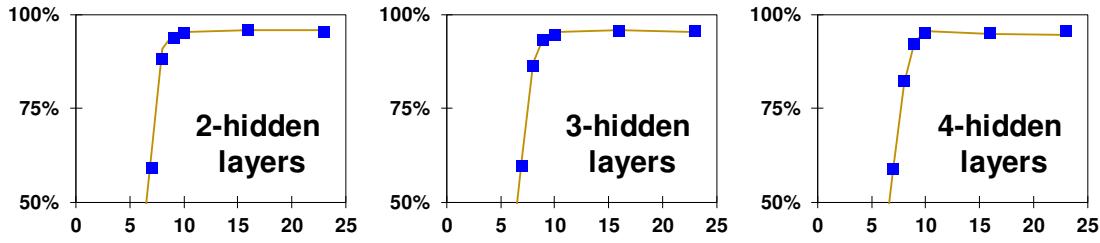

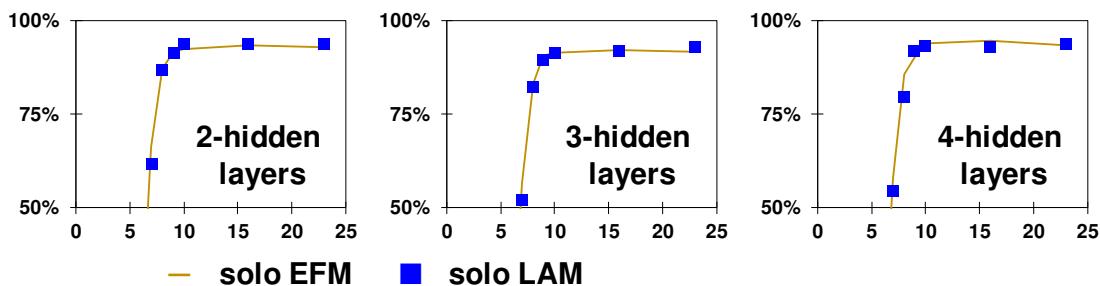

| 2.20 | Deeper NNs training results varying with fraction bits. The attained accuracies are almost identical (a) HARS (b) ISOLET (c) CNAE-9. . .                                                                                           | 52 |

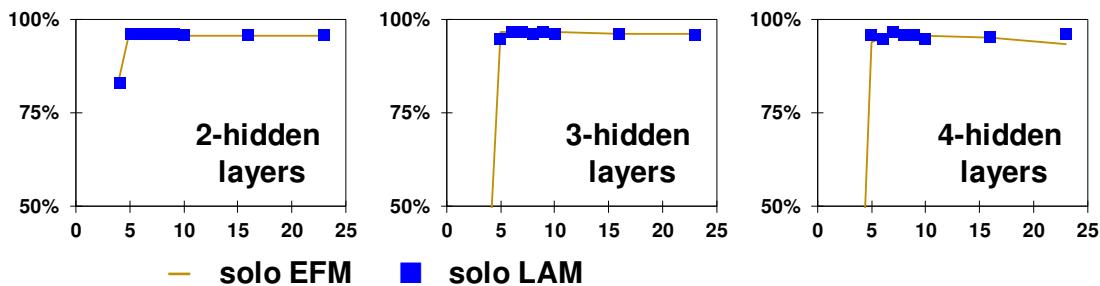

| 2.21 | Training curves for MNIST. The convergence speeds of solo-EFM and solo-LAM training are almost identical. . . . .                                                                                                                  | 53 |

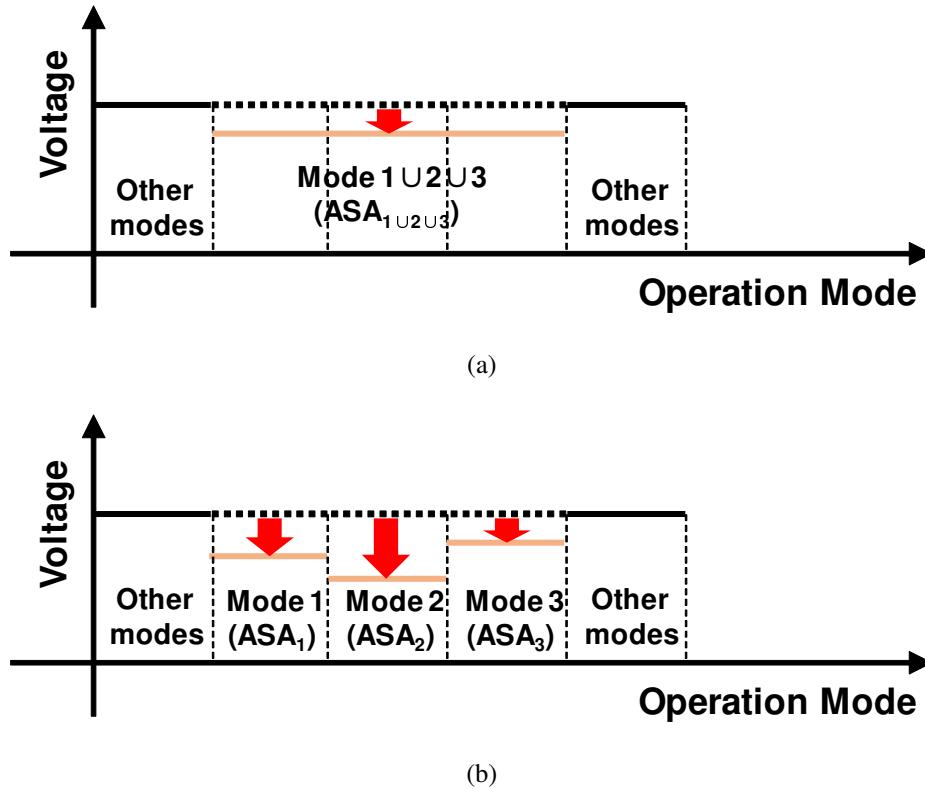

| 3.1  | Expected voltage scaling operations for (a) single-mode VS design and (b) multi-mode (mode-wise) VS design. . . . .                                                                                                                | 58 |

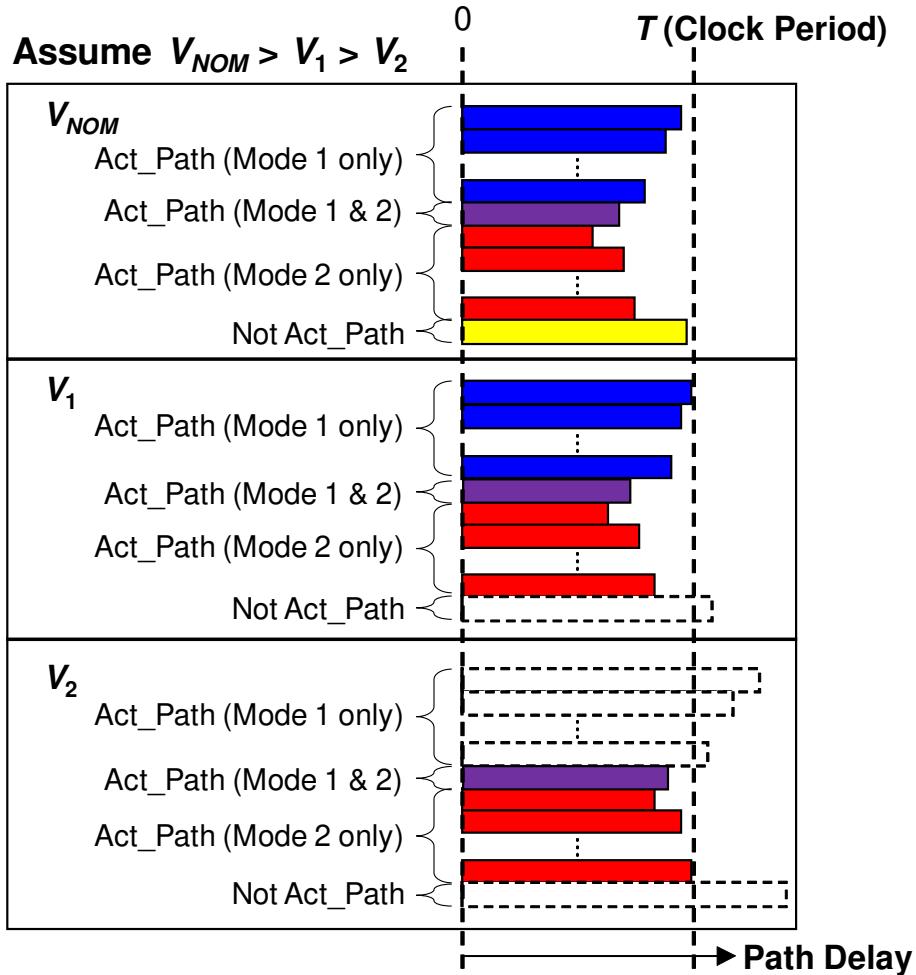

| 3.2  | Mode-wise timing constraints (two-mode case). . . . .                                                                                                                                                                              | 60 |

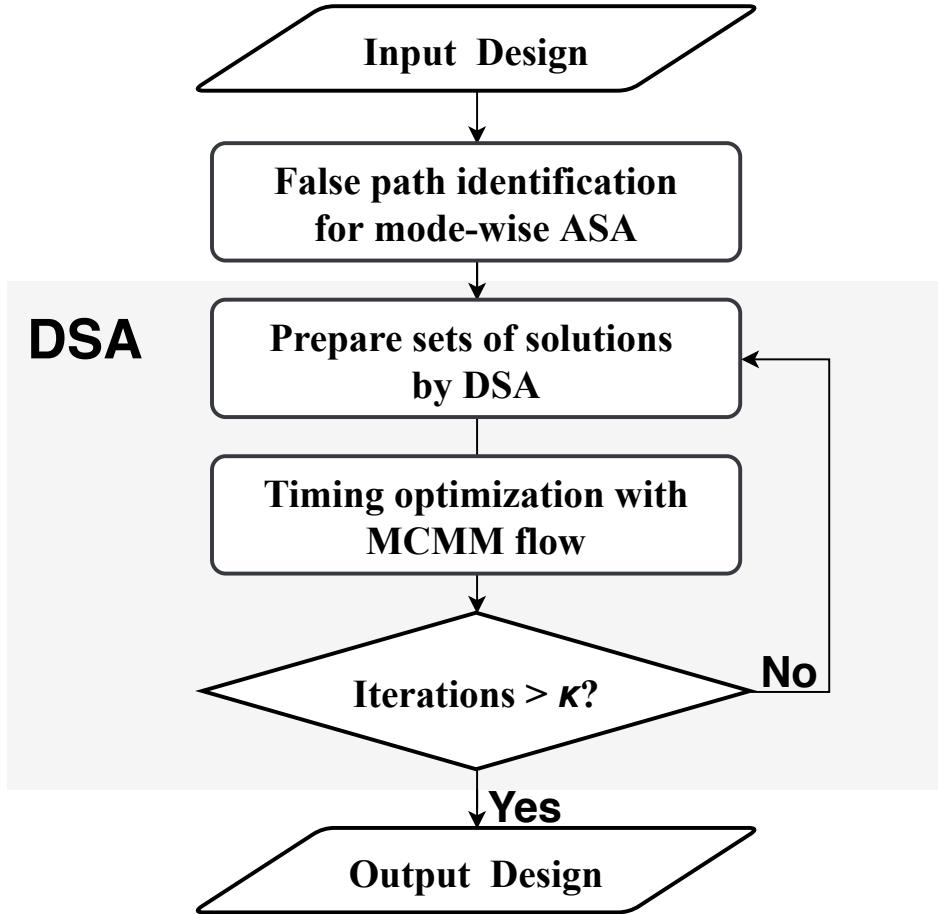

| 3.3  | Overall flow for solving MWVS problem. . . . .                                                                                                                                                                                     | 62 |

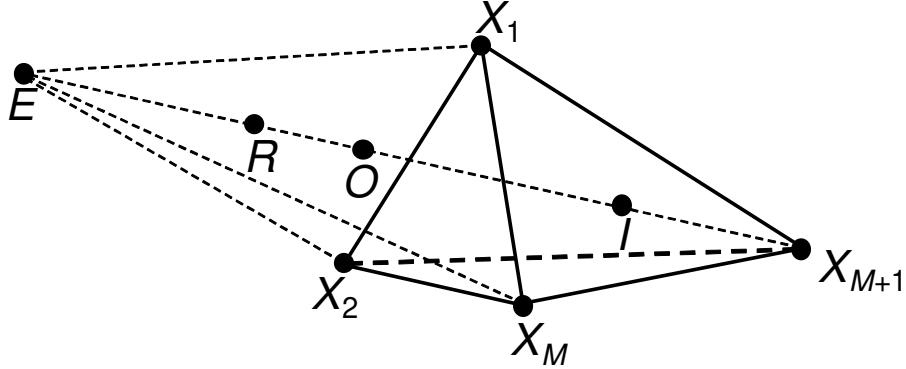

| 3.4  | Illustration of three-dimensional simplex in DSA. . . . .                                                                                                                                                                          | 63 |

| 3.5  | MCMM setting in EDA tool for MWVS design. . . . .                                                                                                                                                                                  | 64 |

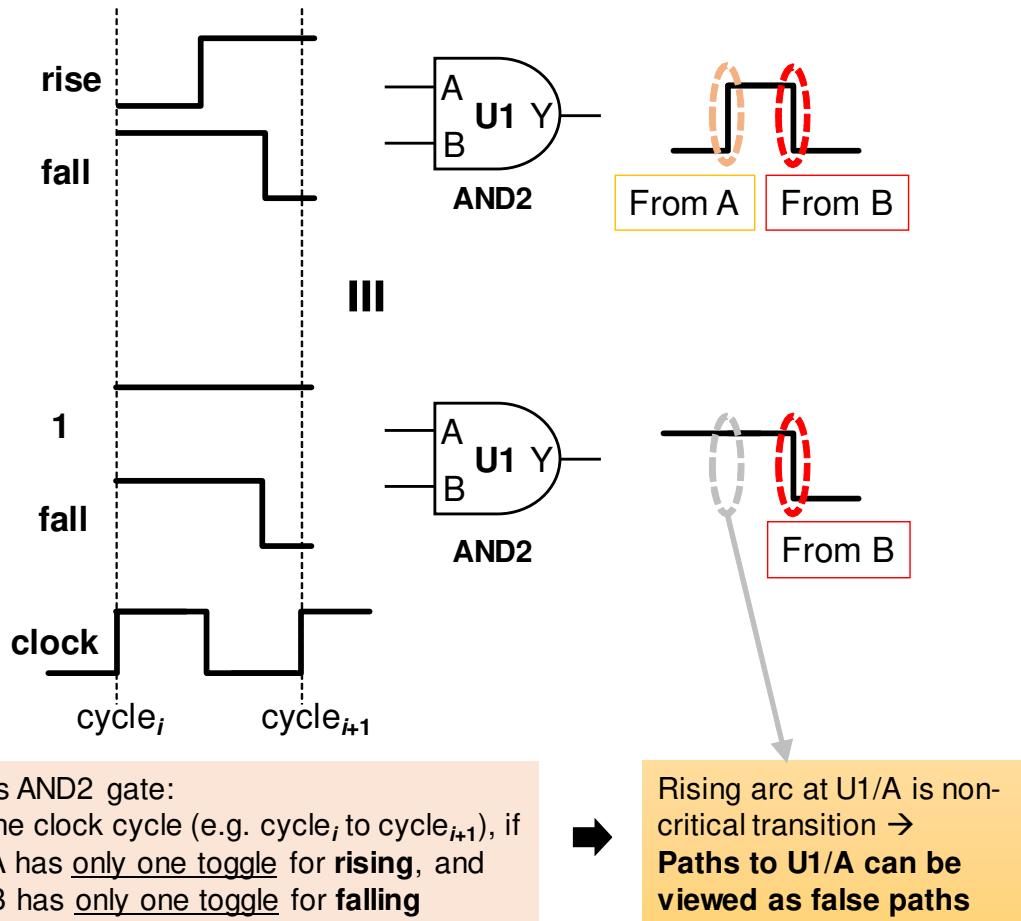

| 3.6  | Examples of false path identification including cycle-by-cycle analysis. .                                                                                                                                                         | 66 |

| 3.7  | Cycle-based false path analysis. . . . .                                                                                                                                                                                           | 67 |

| 3.8  | Cycle-based non-critical transition and false path analysis in AND2 gate. .                                                                                                                                                        | 68 |

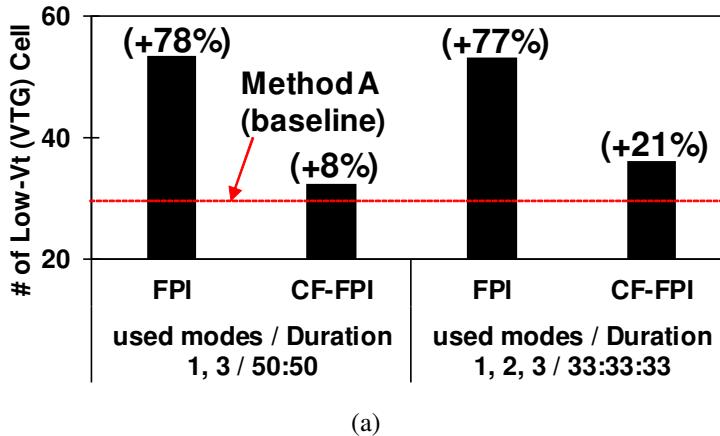

| 3.9  | Comparison between FPI and CF-FPI for (a) # of low-Vt (VTG) cells (b) leakage powers. . . . .                                                                                                                                      | 72 |

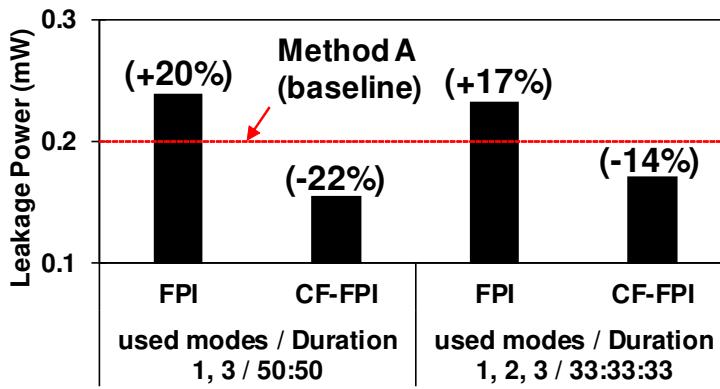

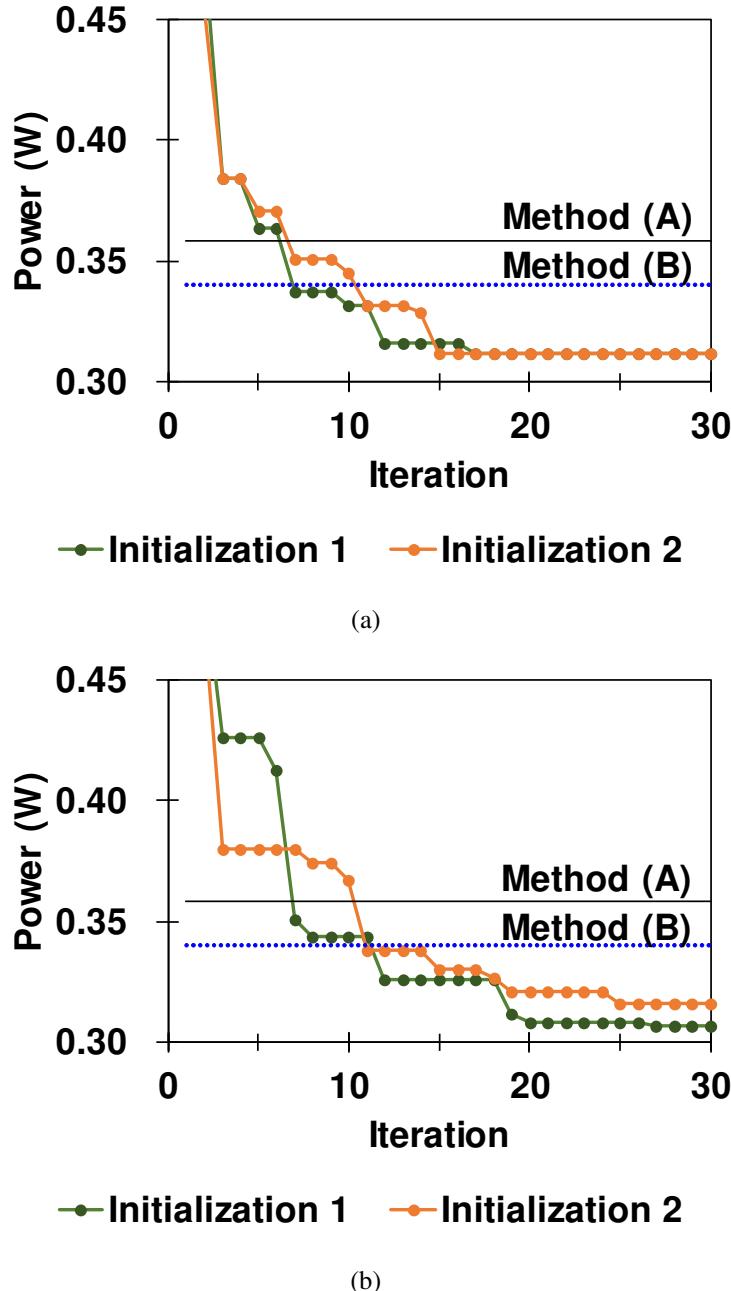

| 3.10 | Convergence plots of the optimization for (a) two-mode case (1, 3), and (b) three-mode case (1, 2, 3) starting from two different initial points. .                                                                                | 74 |

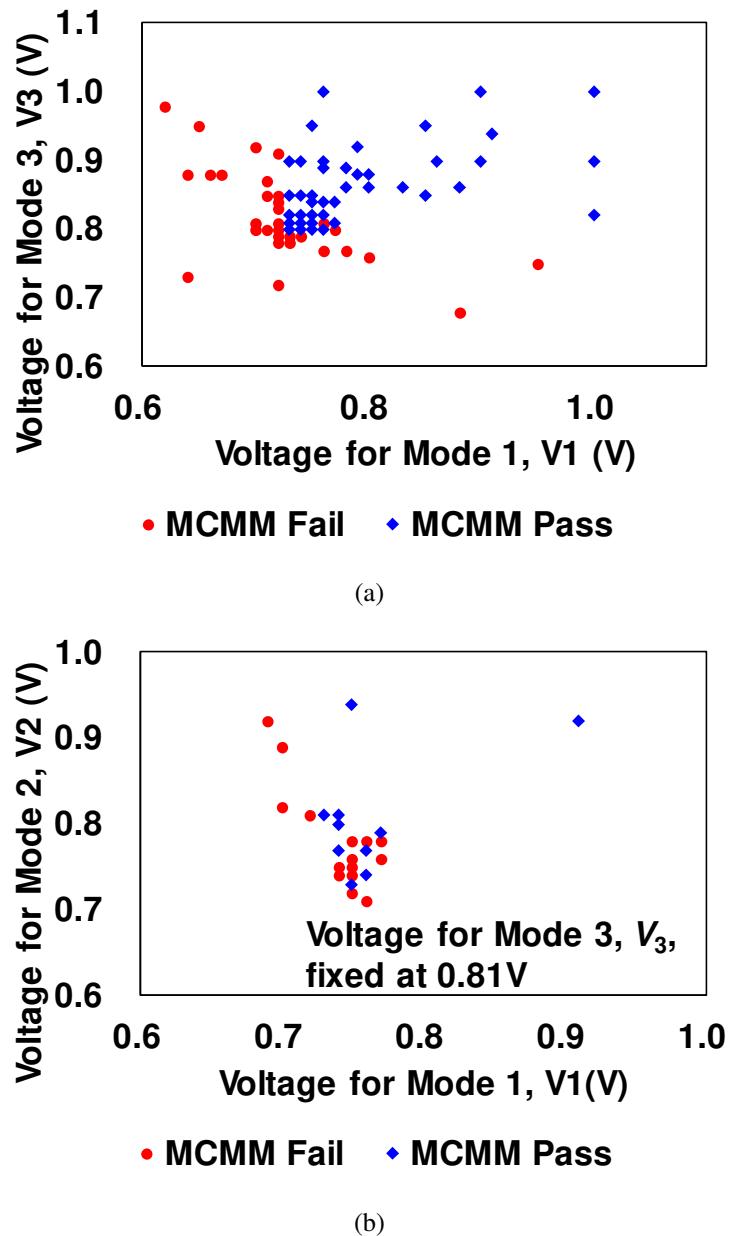

| 3.11 | Timing closure results at various sets of voltages for individual modes. (a) two-mode case (1, 3). and (b) three-mode case (1, 2, 3) where the voltage for Mode 3 is fixed at 0.81 V. . . . .                                      | 75 |

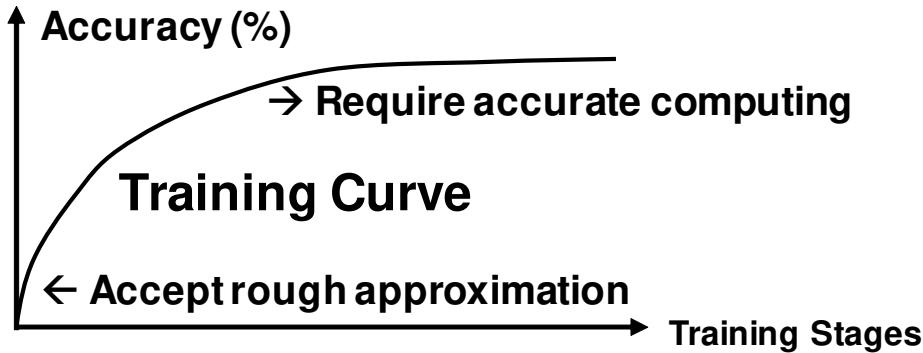

| 4.1  | Concept of gradual training approximation (GTA). . . . .                                                                                                                                                                           | 80 |

|      |                                                                                                                                                                                                                            |    |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

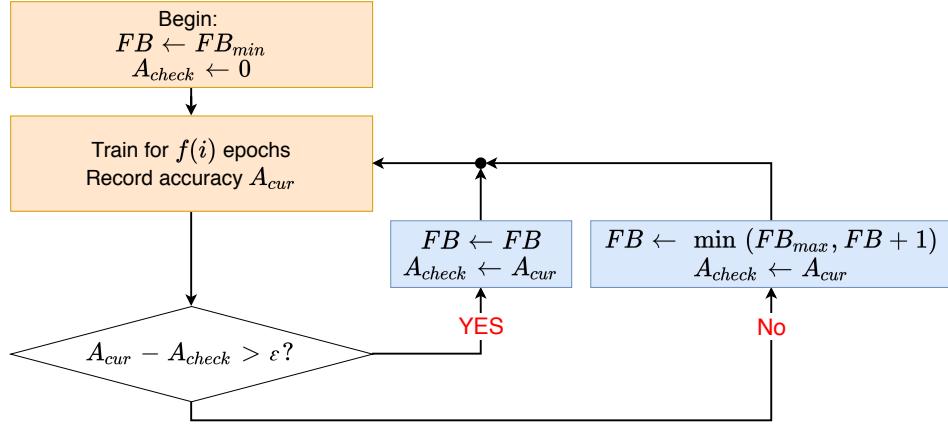

| 4.2  | ABVS flow chart. Training finishes when $i$ reaches $T$ , but this process is omitted in the figure. . . . .                                                                                                               | 81 |

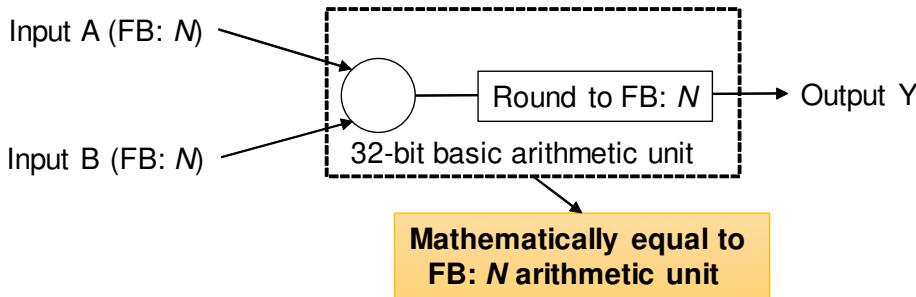

| 4.3  | Concept of BWS implementation in QPyTorch. . . . .                                                                                                                                                                         | 82 |

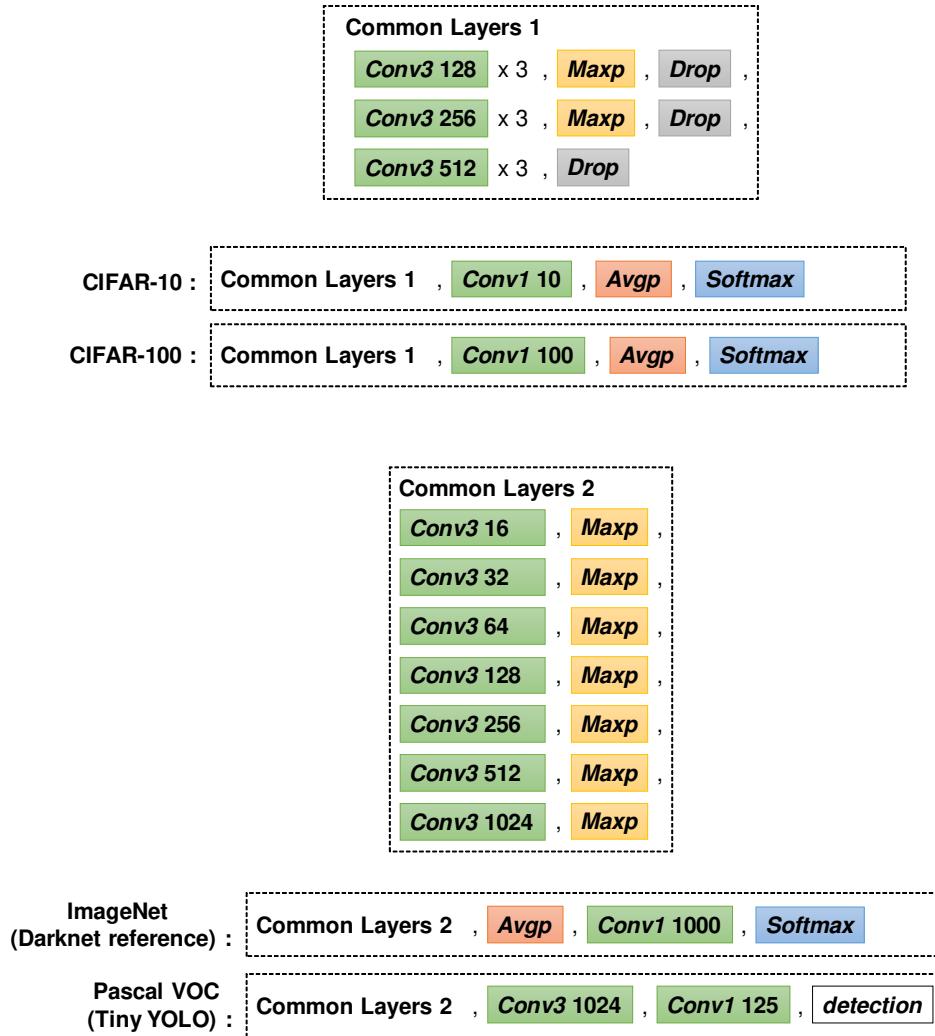

| 4.4  | DNN structures used in the experiments. . . . .                                                                                                                                                                            | 83 |

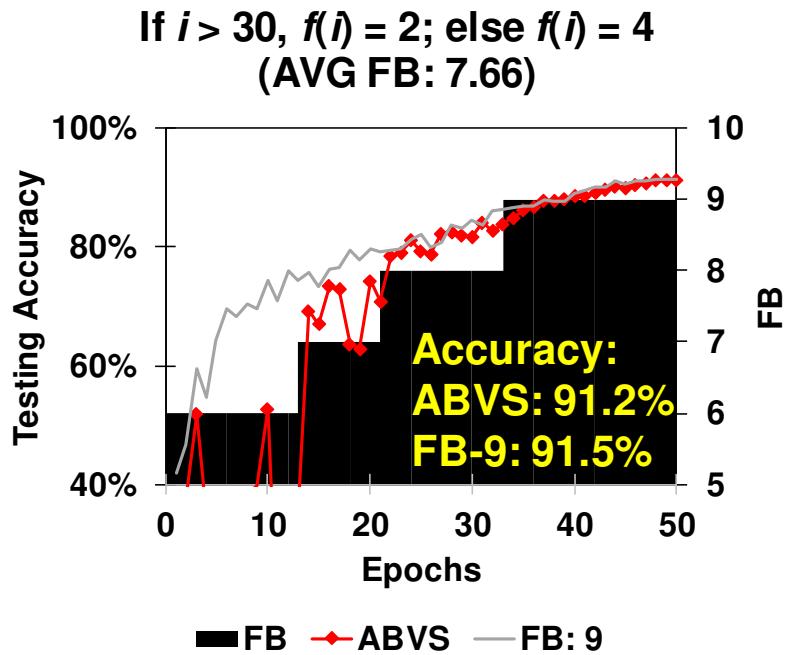

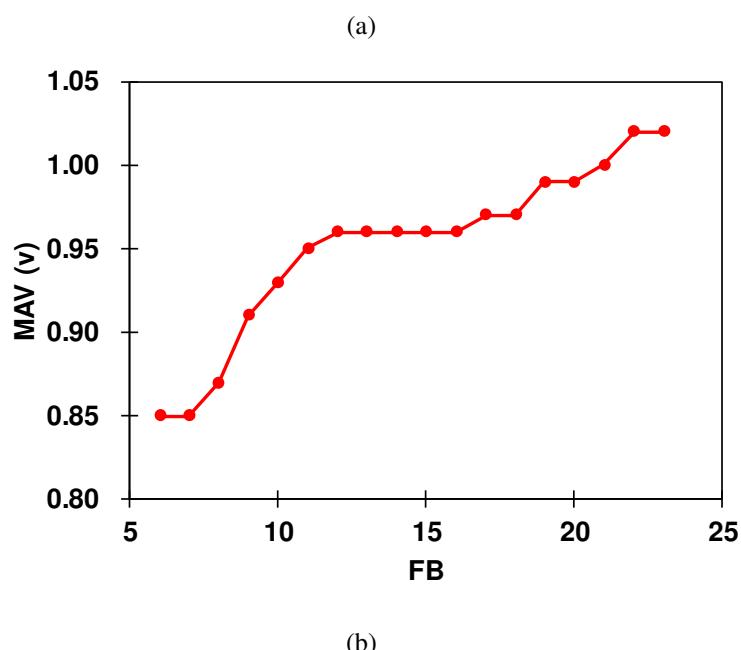

| 4.5  | Trainings w/ fixed FB for (a) CIFAR-10 (b) CIFAR-100. . . . .                                                                                                                                                              | 85 |

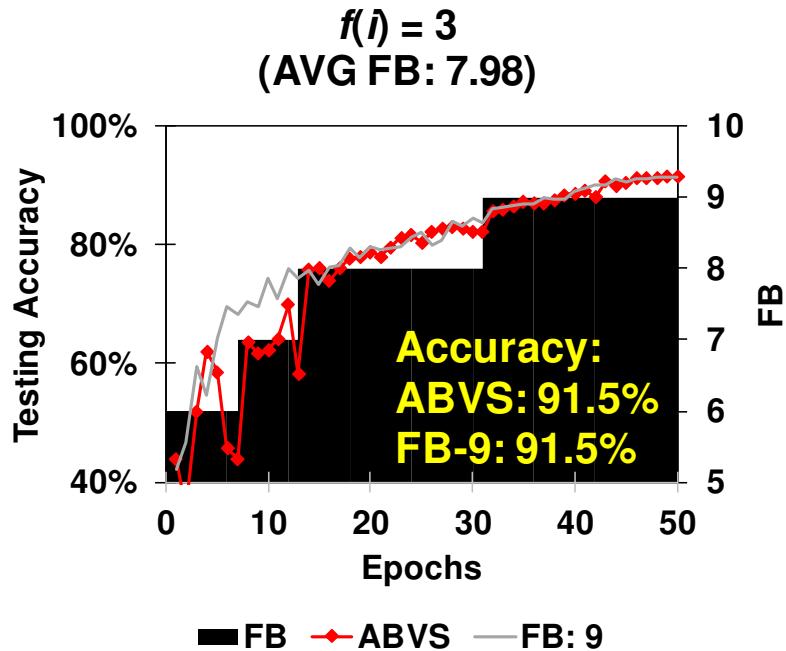

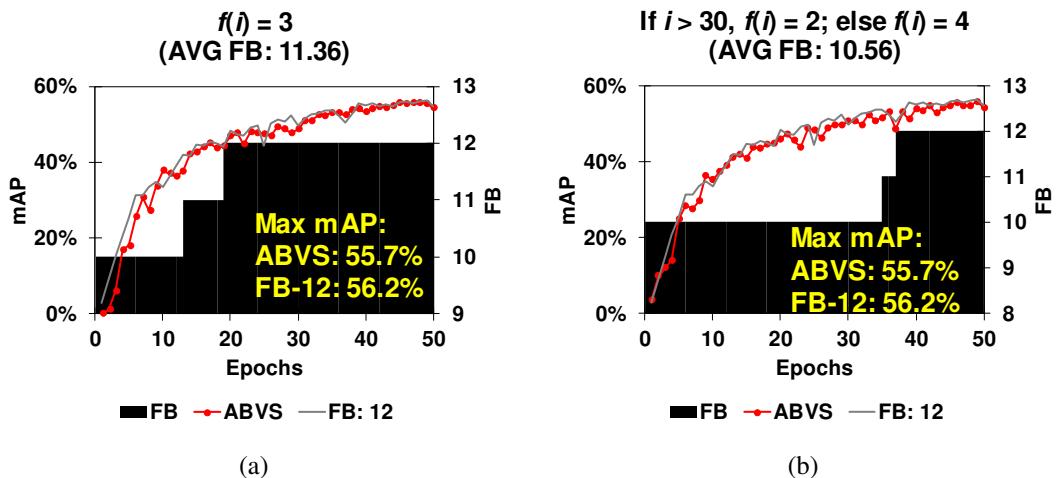

| 4.6  | Trainings w/ ABVS for CIFAR-10 with two checking schedules. . . . .                                                                                                                                                        | 90 |

| 4.7  | Trainings w/ ABVS for CIFAR-100 with two checking schedules. . . . .                                                                                                                                                       | 91 |

| 4.8  | Applying ABVS flow with $FB_{max} = 23$ for CIFAR-10 and CIFAR-100. . . . .                                                                                                                                                | 92 |

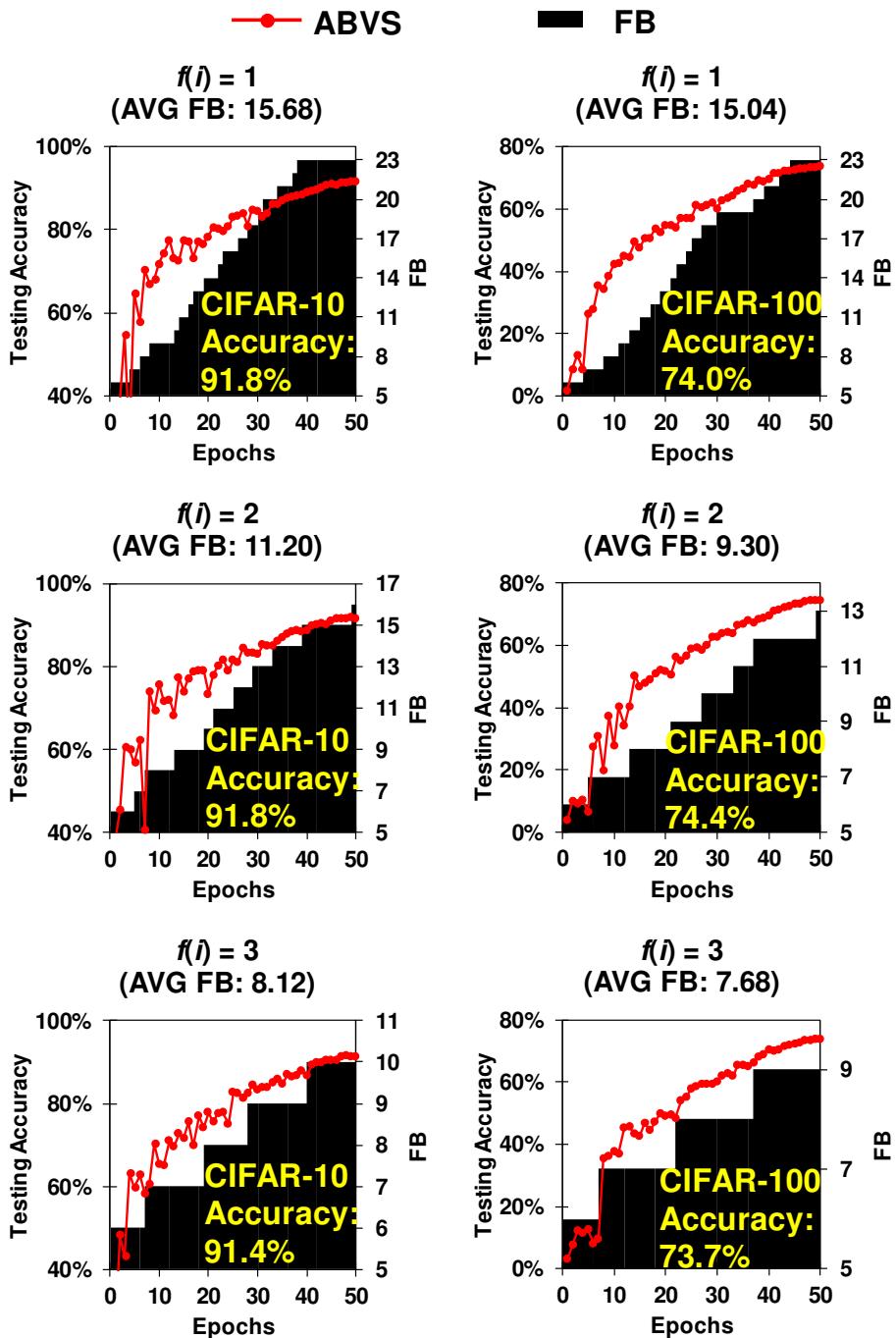

| 4.9  | ABVS results (ImageNet). . . . .                                                                                                                                                                                           | 93 |

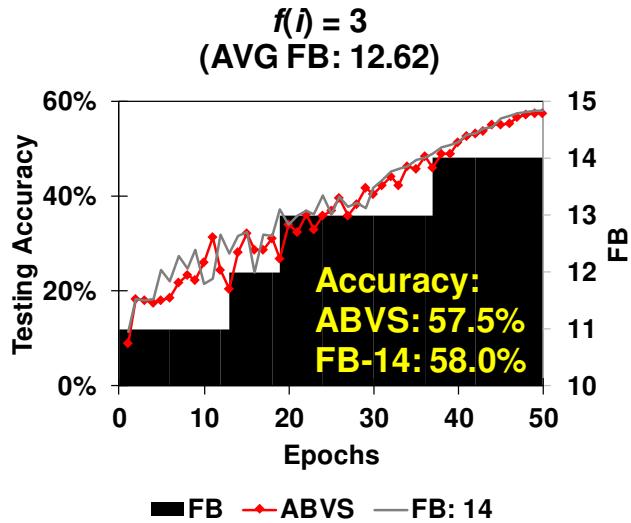

| 4.10 | ABVS results w/ two checking schedules (Pascal VOC). . . . .                                                                                                                                                               | 93 |

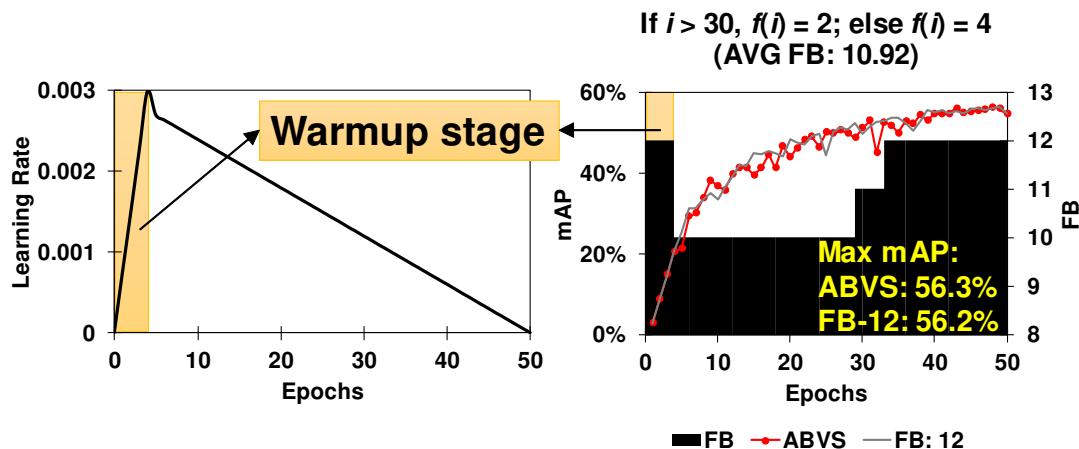

| 4.11 | ABVS results considering warmup stage (Pascal VOC). . . . .                                                                                                                                                                | 94 |

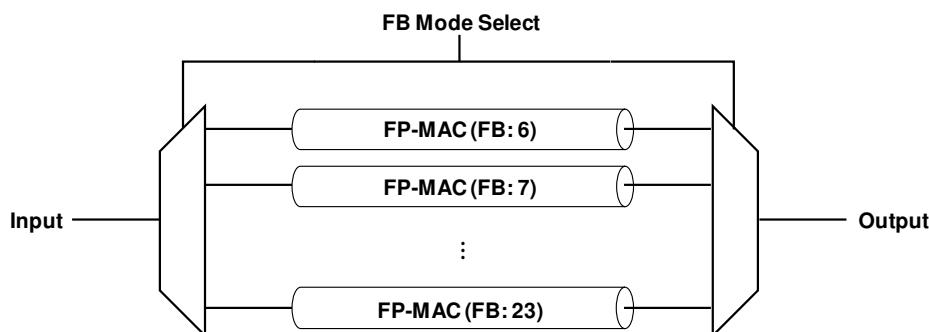

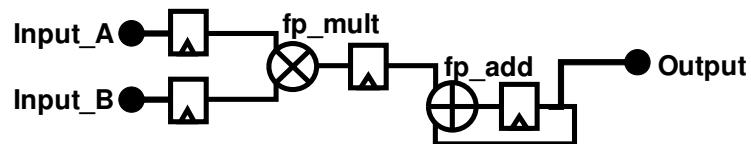

| 4.12 | Assumed FP-MAC with FB configurability. . . . .                                                                                                                                                                            | 94 |

| 4.13 | (a) Schematic of a single FP-MAC with $N$ -bit. (b) MAV results for each FP-MAC with different FBs. . . . .                                                                                                                | 95 |

| 4.14 | Energy of ABVS training (a) normalized by that of least sufficient FB (b) normalized by that of FB: 10 or FB: 23 (c) normalized by that of FB: 10 or FB: 23 for CIFAR-10/CIFAR-100 with unknown dataset treatment. . . . . | 96 |

| 4.15 | MAV comparison between FP-MACs with RTNE and RT0. . . . .                                                                                                                                                                  | 97 |

| 4.16 | Comparison in training quality between RTNE and RT0. . . . .                                                                                                                                                               | 97 |

| 4.17 | Truth-table-based algorithm comparison between RTNE and RTN. . . . .                                                                                                                                                       | 98 |

| 4.18 | Comparison in training quality between RTNE, RTN and RT0. . . . .                                                                                                                                                          | 98 |

| 4.19 | Proposal for a FB-configurable FP-MAC design with less area-overhead. . . . .                                                                                                                                              | 99 |

# List of Tables

|     |                                                                                                                                                        |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1 | Processing time comparison between training and inference phases to train ImageNet for 50 epochs with CPU: Intel E5-v4 + GPU: Tesla V100 DGXS. . . . . | 3  |

| 1.2 | Commercially available products for AI/DNN acceleration. . . . .                                                                                       | 4  |

| 2.1 | Existing works that adopt logarithm-based multipliers in NN. . . . .                                                                                   | 29 |

| 2.2 | NN structures for testcases based on 1-hidden layer. . . . .                                                                                           | 37 |

| 2.3 | Statistics for usage of multipliers, adders, and registers in the dedicated NN hardware. . . . .                                                       | 45 |

| 2.4 | Power estimation results for training larger-size of NN (projected from FOURCLASS benchmarking result). . . . .                                        | 45 |

| 2.5 | Number of logic elements used to implement Nyuzi on FPGA. . . . .                                                                                      | 46 |

| 3.1 | Optimization results for (A) conventional VS (baseline), (B) single-mode ASA + VS, and (C) mode-wise ASA + VS (proposed). . . . .                      | 71 |

| 3.2 | # of false-path specifications in design constraint file for each mode . .                                                                             | 72 |

| 4.1 | Existing works applying AC techniques. FP/BP: forward/back propagation. VS: voltage scaling . . . . .                                                  | 79 |

| 4.2 | # of images in training and testing sets. . . . .                                                                                                      | 84 |

# Abbreviations

|               |                                                       |

|---------------|-------------------------------------------------------|

| <b>ABVS</b>   | Adaptive Bit-width and Voltage Scaling                |

| <b>AC</b>     | Approximate Computing                                 |

| <b>AES</b>    | Advanced Encryption Standard                          |

| <b>AI</b>     | Artificial Intelligence                               |

| <b>ALU</b>    | Arithmetic logic unit                                 |

| <b>ASA</b>    | Activation-aware Slack Assignment                     |

| <b>ASIC</b>   | Application-Specific Integrated Circuit               |

| <b>AVS</b>    | Adaptive Voltage Scaling                              |

| <b>BWS</b>    | Bit-Width Scaling                                     |

| <b>CF-FPI</b> | Cycle-by-cycle Fine-grained False Path Identification |

| <b>CPI</b>    | Critical Path Isolation                               |

| <b>CPU</b>    | Centor Processing Unit                                |

| <b>DNN</b>    | Deep Neuron Network                                   |

| <b>DSA</b>    | Downhill Simplex Algorithm                            |

| <b>ECO</b>    | Engineering Change Order                              |

| <b>EDA</b>    | Electronic Design Automation                          |

| <b>EFM</b>    | Exact floating-point Multiplier                       |

| <b>FB</b>     | Fraction Bit                                          |

| <b>FF</b>     | Flip Flops                                            |

|              |                                                        |

|--------------|--------------------------------------------------------|

| <b>FP</b>    | Floating Point                                         |

| <b>FPGA</b>  | Field Programmable Gate Array                          |

| <b>FPI</b>   | False Path Identification                              |

| <b>FPU</b>   | Floating-Point Unit                                    |

| <b>GPGPU</b> | General Purpose Graphic Processing Unit                |

| <b>GPU</b>   | Graphic Processing Unit                                |

| <b>GTA</b>   | Gradual Training Approximation                         |

| <b>IoT</b>   | Internet of Thing                                      |

| <b>ISA</b>   | Instruction Set Architecture                           |

| <b>LAM</b>   | Logarithm-Approximate Multiplier                       |

| <b>MAC</b>   | Multiply-ACcumulate                                    |

| <b>mAP</b>   | mean Average Precision                                 |

| <b>MCMM</b>  | Multi-Corner Multi-Mode                                |

| <b>ML</b>    | Machine Learning                                       |

| <b>MLP</b>   | Multi-Layer Perceptron                                 |

| <b>MTTF</b>  | Mean-Time-To-Failure                                   |

| <b>MWVS</b>  | Mode-Wise Voltage Scaling                              |

| <b>NCT</b>   | Non-Critical Transition                                |

| <b>NN</b>    | Neural Network                                         |

| <b>PLAN</b>  | Piecewise Linear Approximation of a Nonlinear function |

| <b>RT0</b>   | Round-To-zero                                          |

| <b>RTNE</b>  | Round-To-the-Nearest-Even                              |

| <b>SOC</b>   | System-On-Chip                                         |

| <b>TPU</b>   | Tensor Processing Unit                                 |

| <b>VOS</b>   | Voltage Over-Scaling                                   |

| <b>VS</b>    | Voltage Scaling                                        |

| <b>WNS</b>   | Worst Negative Slack                                   |

# Chapter 1

## Introduction

This chapter provides the background and the objectives of this dissertation. This dissertation aims at providing a design methodology for energy-efficient deep neural network (DNN) training system. First of all, this dissertation briefly describes the basic of neuron networks and then describes the survey for approximate computing and voltage-scaling design paradigms. The major challenge of efficient training with approximate computing and voltage scaling are then discussed. Finally, this chapter provides the objective and the overall organization of the dissertation.

### 1.1 Background

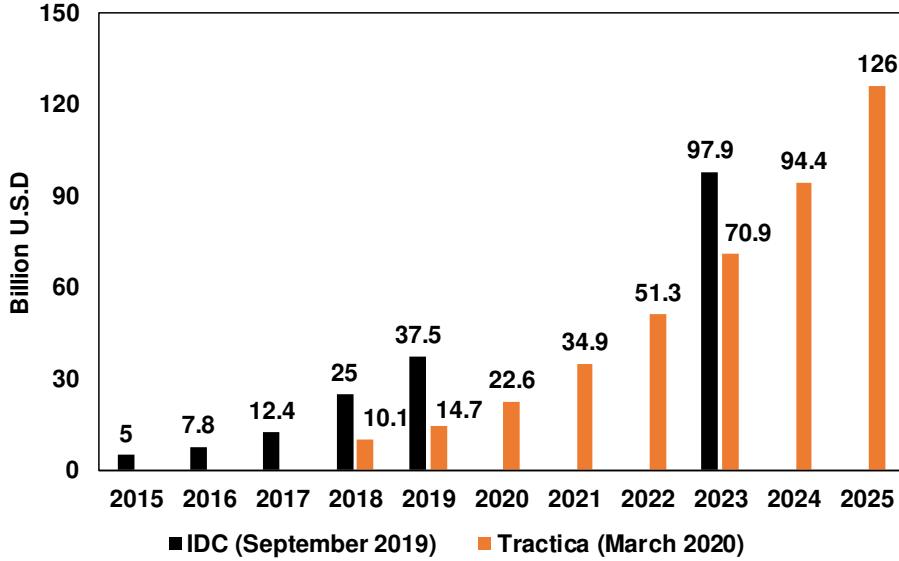

Artificial intelligence (AI) has become the ubiquitous technology indispensable for personal daily life. It drives Big Data analysis and benefits many areas such as medical treatment, finance, and industry. Statistical data also reveals that the investment of AI incredibly grows up in recent years and could even burst in the near future. Fig. 1.1 [1] shows that AI market/revenue grows up to 22.6 billion USD by 2020, and the data forecast that the value would reach 126 billion USD by 2025.

Deep neural network (DNN) has thrived and formed the foundation for many advanced AI applications [2, 3] such as image classification, object detection [4, 5], and speech recognition [6]. DNN model performs excellent feature extraction for the given input data e.g., images, videos, audios, or speech, and it possesses even superior capability than human perception. Therefore, DNN contributes to unprecedented success in many AI tasks thanks to its outstanding accuracy and generality. While DNN already achieves state-of-the-art accuracy, it pays the cost of considerably intensive computation [2, 7].

Generally, a DNN computing system consists of two stages; training and inference. A DNN model needs to optimize its parameters of the network, e.g., weights and bias, during the training stage with a set of data, and then the trained model can perform the inference with the newly given input.

Figure 1.1: Market size/revenue comparison for artificial intelligence worldwide from 2015 to 2025.

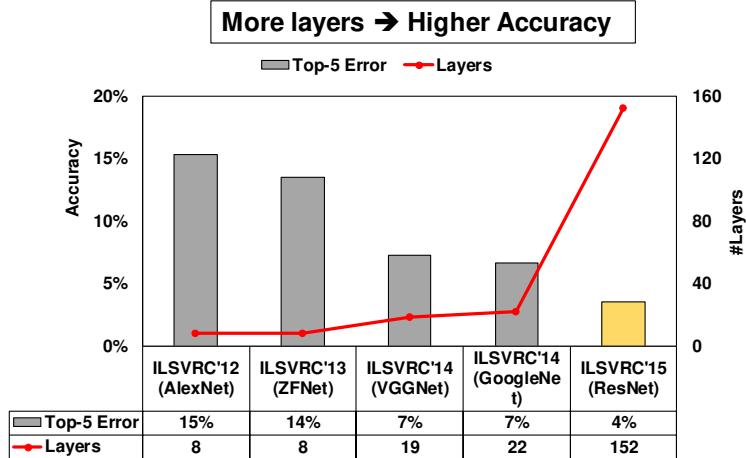

Empirically, a DNN with more sophisticated structure, e.g., deeper layers, possesses higher capability for inference, Fig. 1.2 shows the top competitive DNN models at ILSVRC, a worldwide top contest for image classification and object detection, from 2012 to 2015 (collected by the reference [4, 7, 8]). The ImageNet database [9], which is used for this public challenge, is very popular and representative in academia and industry for evaluating the contemporary DNN models regarding their inference strength. The database includes 1.3 million images for training, 50,000 images for testing, and 1000 classes. Fig. 1.2 shows that more layers would offer higher accuracy. In 2015, ResNet, which is a well-acknowledged DNN model, achieves 4% top-5 error with utilizing up to 152 layers. It is conceivable that such a huge DNN model would demand considerable computations even merely for inference, and the amount of computations for training is further huge. Training needs to conduct more operations according to the algorithm than inference. Besides, compared with inference, training a model requires an even large amount of dataset. Moreover, several iteration cycles are required to optimize and converge the model during the training. Therefore, a more complicated algorithm, a large-size dataset, and many numbers of iterations contribute to the overwhelming amount of computations for training compared with inference.

Table 1.1 based on ImageNet [9] reveals that the CPU time difference between training and inference can lead to 1,300X according to large-scale of dataset (1.3 million images) and tremendous iterations (250,000 times with the batch size of 256). Since  $\text{Energy} = \text{Power} \times \text{Time}$ , even if not considering the power difference, the overwhelming energy cost in training compared with inference is understandable. In order to save

Figure 1.2: Accuracy vs. number of layers in DNN for ImageNet classification (#training dataset: 1.3 million). Empirically, models with more layers achieve higher accuracy.

Table 1.1: Processing time comparison between training and inference phases to train ImageNet for 50 epochs with CPU: Intel E5-v4 + GPU: Tesla V100 DGXS.

| ImageNet dataset on Darknet reference model [12] |                       |        |

|--------------------------------------------------|-----------------------|--------|

| Phase                                            | Processing Time (sec) | Ratio  |

| Training                                         | 52,131                | 1,303X |

| Inference                                        | 40                    | 1X     |

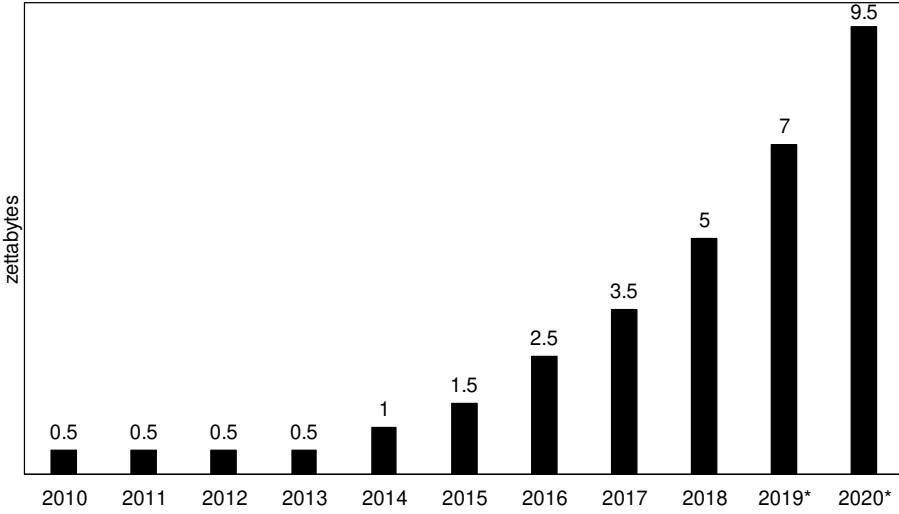

the necessary run time, modern DNN training relies on GPUs (graphic processing units) to achieve higher throughput and shorter latency. GPU contains numerous arithmetic logic units (ALUs) and allows tens-of-thousands of parallel computing assuming it has 1000 cores. Such outstanding capability of parallel computing benefits DNN for realizing training acceleration. However, GPU is known for its huge power consumption [10], considering that the real-time data surges with an astonishing number (about 10 fold from 2014 to 2020) as shown in Fig.1.3 [11], the even bigger data keeps threatening the resource of inference and, not to mentioned, the training systems. Energy-efficient training would benefit GPU for the heat removal and power delivery, which improves the chip-level and system-level reliability and reduces the cost for heat removal and power delivery. To facilitate the marketing revenue in modern AI applications, the trend for the increasing amount of data drives the strong motivation for developing an efficient training mechanism.

Besides GPUs, efficient training based on more size-limited devices, such as FPGA [13, 14], or dedicated application-specific integrated circuit (ASIC) is also demanded [15]. Commercially available products developed based on different platforms to yield machine learning or DNN throughput improvement are exemplified in Table 1.2. Re-

Figure 1.3: Annual size of real-time data in the global datasphere. The Global Datasphere quantifies and analyzes the amount of data created, captured, and replicated in any given year across the world.

Table 1.2: Commercially available products for AI/DNN acceleration.

|      |                                                               |

|------|---------------------------------------------------------------|

| GPU  | NVIDIA A100, V100                                             |

| FPGA | Xilinx Zynq DPU                                               |

| ASIC | Google Coral Edge TPU, Nvidia Jetson Nano, Intel Movidius VPU |

cently, the emerging markets of on-line or transfer learning move the infrastructures of training from the cloud to edge server-level computing [10, 16, 17] or mobile devices, e.g. Internet-of-Things (IoT). Training on server- or device- levels can provide more local and *in situ* services because they have the benefits of shorter latency and privacy protection. However, due to the size and power limitation, it is essential to provide a solution for efficient training systems [18, 19].

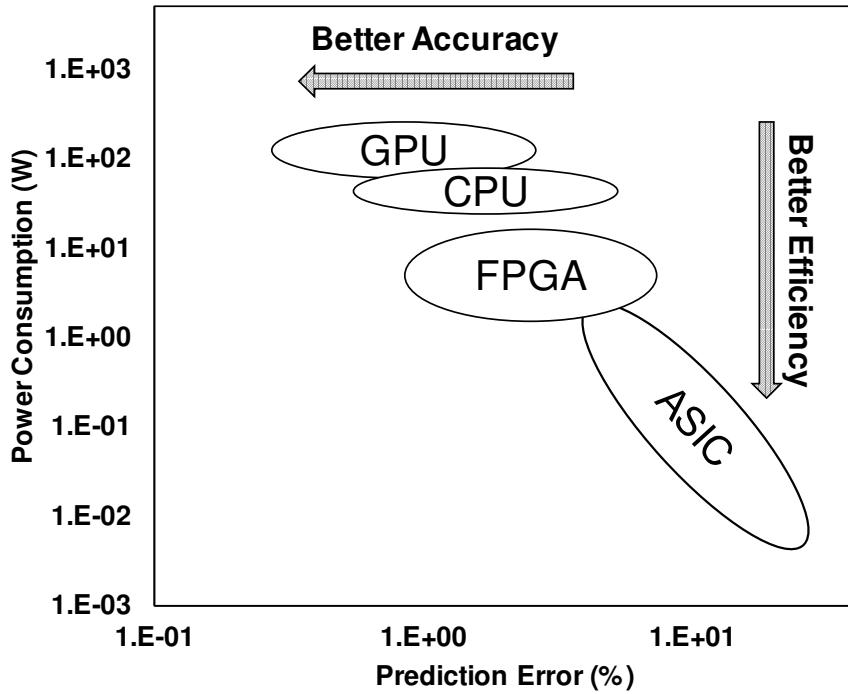

Different computing platforms have different training properties regarding their quality and efficiency. Fig. 1.4 shows the trade-off between the accuracy (denoted as prediction error) and power consumption based on four types of hardware platforms [20]. According to the figures, though GPU can achieve the highest accuracy, it also pays the largest power consumption. On the other hand, Fig. 1.4 shows that the dedicated design (ASIC) is very convenient to trade accuracy with efficiency and could be applicable for many different applications. In addition, ASIC can either operate stand-alone or be embedded into GPU, FPGA, or even CPU, which provides high design freedom and versatility.

Figure 1.4: Prediction error and power consumption of hardware platform.

## 1.2 Basics of Neural Networks

Neural Network (NN) is one of the most widely-used techniques in machine learning, and DNN is one of its subset where they share similar basic architecture. A basic feed-forward NN model is composed of a few to hundreds of layers, each of which includes a number of neurons. The neurons are connected layer by layer through synaptic weights. The synaptic weights are optimized to provide sufficiently high accuracy through the computationally expensive training phase. Hardware NN system is mainly categorized into two types. The first one is the inference engine that processes a network with given pre-trained weights, and the latter is the training engine that has the additional capability of weight optimization in the training phase. Regardless of the inference or training engine, multiply-accumulate (MAC) arithmetic computation is the primary operation. The rapidly increasing trend of NN size to deal with more intricate and sophisticated problems explodes the amount of MAC computation, resulting in a strong demand for efficient hardware engines.

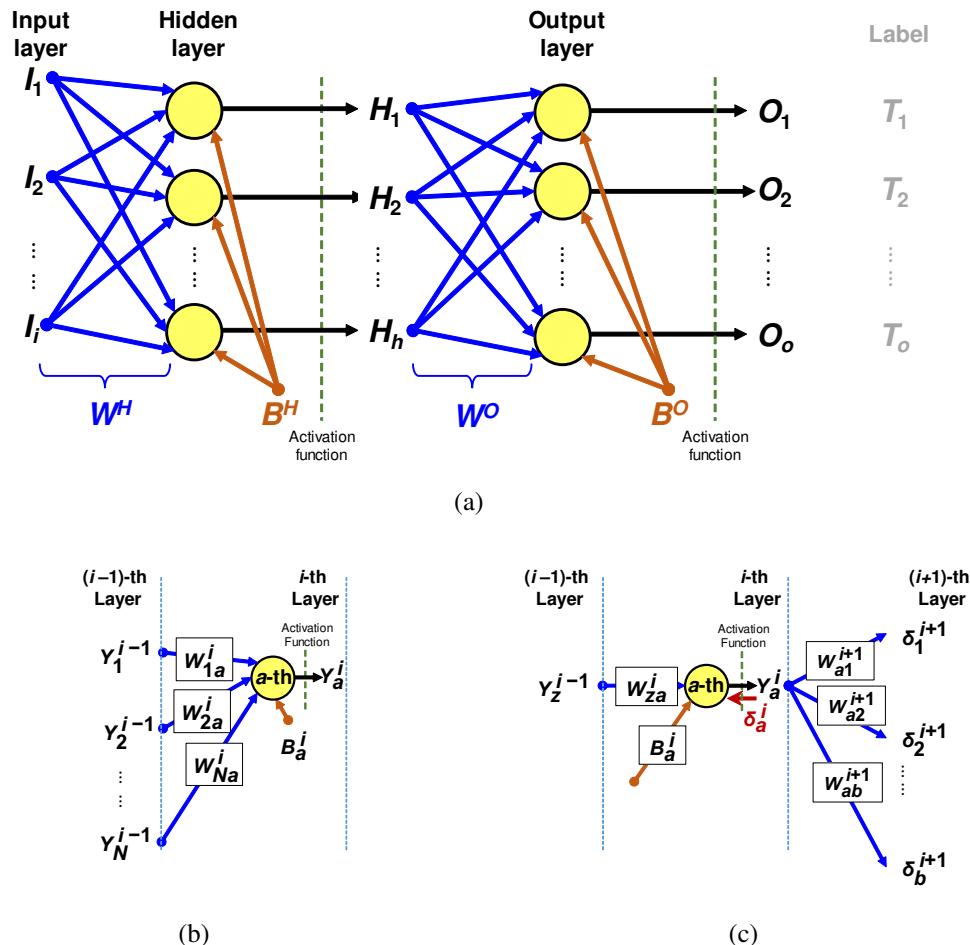

Fig. 1.5(a) illustrates a multilayer perceptron (MLP) structure [21], which is known as a basic feedforward NN. For the sake of clarity, the structure contains only one hidden layer, while the number of hidden layers can be extended to form deeper NNs. The state of each neuron in the network is computed from all the states of neurons in the previous

layer and then is propagated its state to the next layer. Taking the example in Fig. 1.5(b), since all the states are pre-determined in the input layer  $I$ , the state computation starts at each neuron in the hidden layer (neurons are denoted as  $H_1, H_2, \dots, H_h$ ). Each neuron in the hidden layer computes the sum of all the states of neurons in the input layer ( $I_1, I_2, \dots, I_i$ ) multiplied with corresponding synaptic weights ( $W_H$ ), passes the sum with a bias term ( $B_H$ ) through a non-linear activation function to determine its state, and then propagates the state to the output layer. This operation is repeated at the neurons in the output layer ( $O_1, O_2, \dots, O_o$ ) again, but here the sum of all the states of neurons in the hidden layer is computed with weights ( $W_O$ ) and bias ( $B_O$ ) to determine the states. The procedure finishes once all the states of neurons in the output layer are determined.

A basic unit for expressing the above operation is shown in Fig. 1.5(b). Suppose there is the  $a$ -th neuron in the  $i$ -th layer, its state  $Y_a^i$  can be computed by the following formula:

$$Y_a^i = \text{Act} \left( \sum_{k=1}^N W_{ka}^i Y_k^{i-1} + B_a^i \right), \quad (1.1)$$

where  $Y_k^{i-1}$  denotes the state of the  $k$ -th neuron in the  $(i-1)$ -th layer.  $W_{ka}^{i-1}$  represents the synaptic weight connecting from the  $k$ -th neuron in the  $(i-1)$ -th layer, and  $B_a^i$  denotes the bias term for the  $a$ -th neuron in the  $i$ -th layer.  $\text{Act}(\cdot)$  means the activation function, which usually allows passing  $\geq 0$  values or limits the values between -1 and 1. This procedure, so-called forward propagation, keeps going until the states of all the neurons in the output layer are determined, which is the core and dominant operation that an inference engine with pre-trained weights executes.

On the other hand, training NN aims at finding a set of synaptic weights and bias values to minimize the loss function (Loss), which is usually defined as the error squared between the state from the forward propagation results in output layer  $O$  and target label  $T$  ( $T_1, T_2, \dots, T_o$ ) [21]. For illustration purposes, the below describes the standard back-propagation. At the beginning of the training phase, all the weights are randomly initialized, the biases may be initially set to 0, and then forward propagation is launched. The next step is to reduce the loss function according to the contribution of each synaptic weight ( $W$ ) and bias ( $B$ ), which can be obtained through computing their gradient, i.e.  $\partial \text{Loss} / \partial W$  and  $\partial \text{Loss} / \partial B$ . Based on the computed gradients, each synaptic weight and bias can be numerically updated during each iteration. Let us take Fig. 1.5(c) as an example. Suppose a synaptic weight  $W_{za}^i$  connects the  $z$ -th neuron in the  $(i-1)$ -th layer (state =  $Y_z^{i-1}$ ) with the  $a$ -th neuron in the  $i$ -th layer (state =  $Y_a^i$ ) and a bias  $B_a^i$  is for the  $a$ -th neuron in the  $i$ -th layer. Then,  $W_{za}^i$  and  $B_a^i$  are updated by:

$$W_{za}^i += -\eta \frac{\partial \text{Loss}}{\partial W_{za}^i} \text{ where } \frac{\partial \text{Loss}}{\partial W_{za}^i} = \delta_a^i Y_z^{i-1}, \quad (1.2)$$

$$B_a^i += -\eta \frac{\partial \text{Loss}}{\partial B_a^i} \text{ where } \frac{\partial \text{Loss}}{\partial B_a^i} = \delta_a^i. \quad (1.3)$$

The gradient terms  $\partial \text{Loss} / \partial W_{za}^i$  and  $\partial \text{Loss} / \partial B_a^i$  in Eqs. (1.2) and (1.3) share the same term  $\delta_a^i$  while  $\partial \text{Loss} / \partial W_{za}^i$  further includes the term  $Y_z^{i-1}$ . Basically, the gradient terms would decay during the weight and bias update, and thus these are also called gradient decent method.  $\eta$  is the learning rate, and  $\delta_a^i$  is conditionally formulated as follows. If the  $i$ -th layer is the output layer, then  $\delta_a^i$  is:

$$\delta_a^i = \text{Act}'(O_a)(O_a - T_a), \quad (1.4)$$

where  $O_a$  represents the state computed through forward propagation,  $T_a$  means its target state, and  $\text{Act}'$  means the derivative of activation function. If the  $i$ -th layer is not the output layer, then referring to Fig. 1.5(c),  $\delta_a^i$  is expressed as:

$$\delta_a^i = \text{Act}'(Y_a^i) \left( \sum_{n=1}^b W_{an}^{i+1} \delta_n^{i+1} \right), \quad (1.5)$$

where  $W_{an}^{i+1}$  denotes the synaptic weight to the  $n$ -th neuron in the  $(i+1)$ -th layer.  $\delta_n^{i+1}$  can be recursively computed through Eqs. (1.4) and (1.5). Note that, with Eqs. (1.4) and (1.5), the output loss is propagating backward from the output layer, and thus this procedure is named as back propagation [21]. In addition, Eq. (1.5) indicates that the  $\delta_a^i$  in the non-output layer needs to compute all the weighted sum of  $\delta_n^{i+1}$ , meaning that MAC computation is also primary in back propagation. Therefore, the training phase executes huge amount of MAC computations during the iteration loops of forward and back propagation.

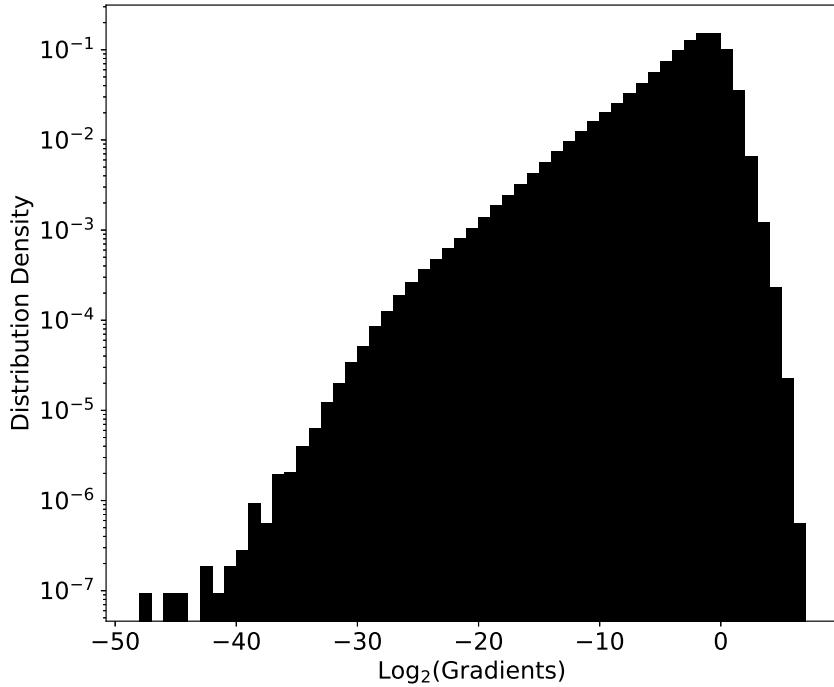

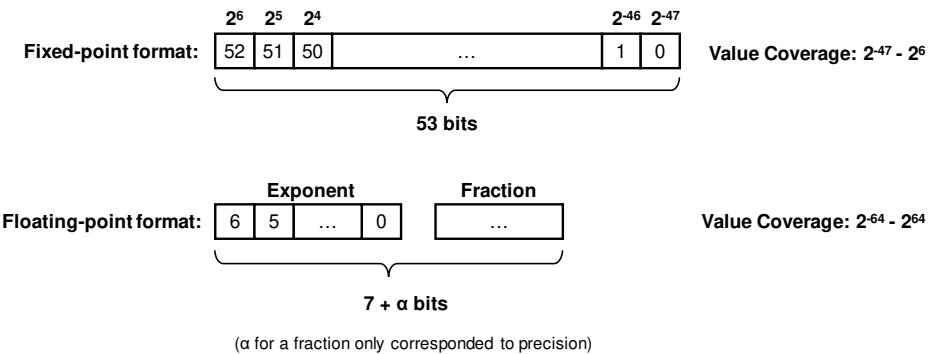

In addition, the gradient terms have a large dynamic range [22]. A simple example can help understand this property. Fig. 1.6 plots the distribution density of the gradient values found when training a NN for MNIST dataset [23]. The gradient values spread from  $2^{-47}$  to  $2^6$ . As shown in Fig. 1.7, if adopting fixed-point expression, more than 50 bits ( $6+47 = 53$ ) are required to cover this range, while floating-point expression spends only a few bits for exponents (e.g. 7 bits if considering bias for negative value) and some extra bits  $\alpha$  for fraction parts (only corresponded to precision rather than coverage) to cover this wide range. Thus, adopting floating-point units (FPUs) is beneficial for training engines to accommodate such gradient computation.

Figure 1.5: Feed-forward neural network. (a) is a schematic of a feed-forward neural network with 1 hidden layer. (b) and (c) are the schematics for illustrating forward- and back-propagation at the  $a$ -th neuron in  $i$ -th layer.

Figure 1.6: Distribution density of gradients observed when a NN is trained for MNIST dataset.  $x$ -axis represents the gradients in log scale with base 2, and  $y$ -axis is the normalized distribution density.

Figure 1.7: Different coverage of value for fixed-point and floating-point data format.

### 1.3 Energy-efficient DNN Training

The works related to efficient training spread over various area because of different motivations [10, 24, 25, 26, 27, 28, 29, 30, 31]. To train a NN with large size of data through high-end GPU systems, some works assume the computing resource is sufficient, e.g., computing in the cloud, and hence introduce “distributed training” to launch huge parallel computing with 256 or even more GPU cards to minimize the training processing time [24, 25, 26]. In other words, these works focus on “run-time” instead of “energy” efficiency.

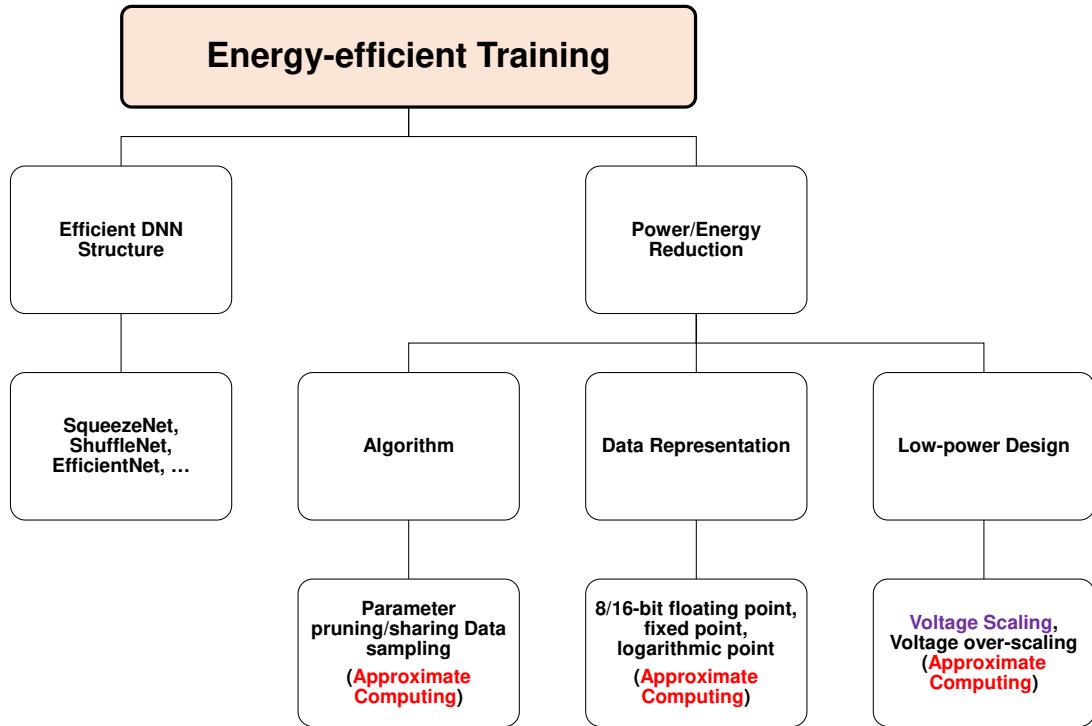

Energy-efficient training roughly contain two categories (1) efficient DNN structures and (2) power/energy reduction, as listed in Fig. 1.8. The first group is about the efficient DNN structures. These works introduce compact DNN structures to effectively compress the model size and the number of parameters, which can enhance the efficiency both in training and inference with sustaining the accuracy. Representative works are like SqueezeNet [29], ShuffleNet [30], EfficientNet [31], etc. These works can also benefit distributed training by requiring less GPUs. Therefore, although the efficient DNN structures may benefit energy saving in use due to the lightweight models, still, the main intention for developing the efficient DNN structures is to improve the “run-time” efficiency when tackling large size of dataset through high-end GPU designs.

On the other hand, most of the motivations of the works in the second group are to accommodate the training into server- and device- level designs instead of high-end GPU design system. Since training in server- or device- level design is limited with size and memory storage, these works pursue higher energy-efficiency in training allowing acceptable quality sacrifice. Researchers in the this group focus on providing the solutions to achieve power/energy reduction through several levels of design methods such as algorithm, data representation, and low-power design methodology. Note that these methods are general means and can be applied to any DNN structures. Algorithm level such as weight/net pruning and sharing [32] or data sampling [24] are proved to be effective for improving efficiency. As for the data representation, training in shorter floating-point (less than 32-bit) [33, 34, 35], fixed-point [27, 28] or in log-domain [36, 37] are the choices for efficiency enhancement. And then for low-power design approach, voltage scaling or voltage over-scaling are the representative mechanisms [38]. Since many techniques applied in the second group require to trade the quality (accuracy) with the power efficiency, this area frequently leverages the knowledge from approximate computing (AC). Besides AC, voltage scaling (VS) is also an effective method in low-power design area, and VS can be considered as an orthogonal way to AC, i.e, AC and VS are combinable.

Figure 1.8: Categories of the area in energy-efficient training.

## 1.4 Approximate Computing to NN

Approximate computing (AC) is recognized as one promising technique to enhance the efficiency of computer systems since many modern applications require large-scale computation and memory storage demands which may burden current available resources [39, 40, 41]. In addition, many growing applications such as recognition, data mining, synthesis, and media processing (audios, images, or videos, graphics) [39, 41], have a common characteristic that it is usually nearly impossible or requires prohibitively high cost for those applications to find an optimal solution but allows to pursue less-than-optimal results or said approximation. Therefore, AC is introduced to be applied to computing systems for trading the efficiency (speed, power/energy, area) with the quality (approximation output results). The AC techniques rely on the statistical properties of computing systems which allows non-zero quality loss for improving efficiency. Although the manufacturing and environmental stochastic variations of the hardware due to process, voltage, temperature, or aging could also induce inaccurate computation results, they are not considered in the definition of AC. AC area assumes that the designed hardware has no stochastic variations [41].

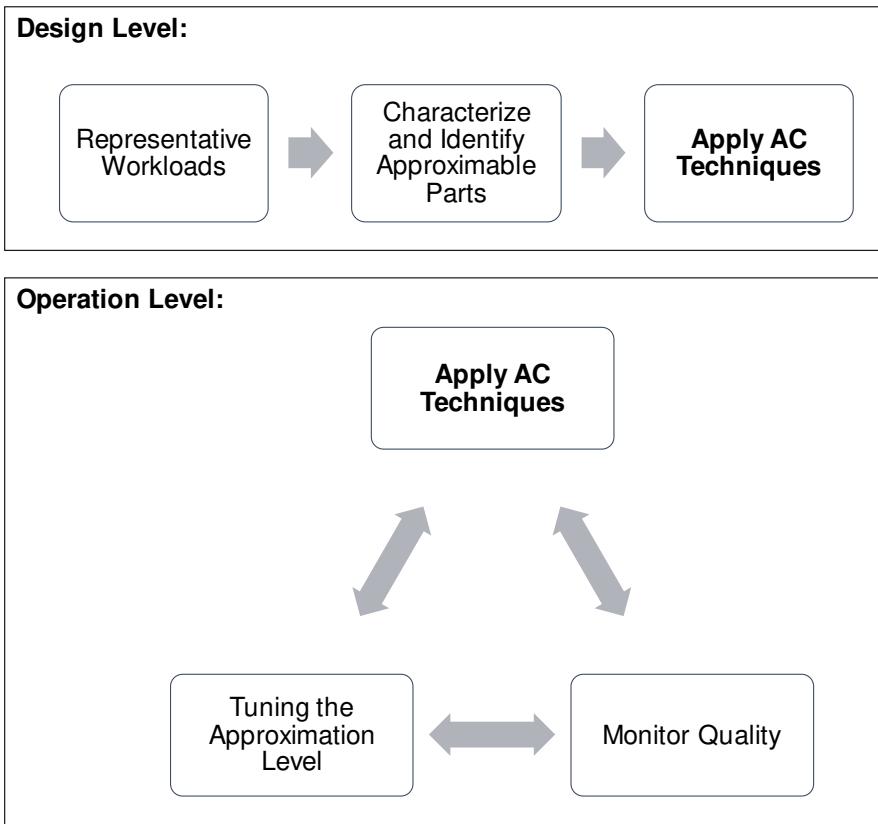

Fig. 1.9 illustrates the overall framework of the AC flow [39]. The AC flow briefly can be categorized into two levels; design level and operation level. The former is

Figure 1.9: Framework of AC.

amenable for the applications (workloads) that are already explicitly specified. Therefore the users can characterize and identify the blocks by observing their impact on the final quality if applying with AC techniques. Finally, the determined approximable blocks can be more aggressively approximated while the other parts adopt light-weight AC techniques or accurate operations. On the other hand, the latter directly applies AC techniques on the system first but with a quality management system to detect the unacceptable error. Once the error is detected, it tunes the approximation level or applies error recovery schemes to improve accuracy. The computing systems have many layers (software, architecture, hardware), and hence the various AC techniques are also distributed in different layers. Note that the AC techniques are not independent in different layers, and occasionally multiple AC techniques and layers are necessary to be invoked simultaneously.

### 1.4.1 Software-level AC Techniques

AC techniques in software mainly relate to the algorithm where the invocations are related to stochastic computations such as average, accumulation, count, and percentile. For these stochastic computations, sampling is recognized as an efficient way to save computing and can achieve acceptable accuracy [42]. Therefore, some iterations of loops can be skipped or reduced (named as loop perforation) for the aforementioned computations in addition to randomized or Monte-Carlo algorithms [43, 44]. Another type of AC technique at the software level corresponds to the programming language that it is capable to annotate or detect which part of the blocks or segments in the codes are approximated, and then system follows the instruction and computes them in approximate storage (architecture-level) or circuits (hardware-level). These kinds of techniques usually need to enhance the present language or develop a new language. It, of course, necessitates AC techniques in compilers and non-software levels as well [45, 46].

### 1.4.2 Architecture-level AC Techniques

AC techniques for architecture-level mainly involve the enhancement of the interface between software and hardware such as instruction set architecture (ISA) to accommodate AC features [47]. Other kinds of AC techniques belong to this group are storage or say memory approximation [47, 48, 49]. The data can be stored in an approximate manner with lower-bit truncation. In SRAM, a lower voltage can be applied as long as the data can be stored with approximated value [48]. The refresh rate in DRAM can be separately assigned with regular values for critical data while the much lower value for non-critical or approximable one [49].

### 1.4.3 Hardware-level AC Techniques

This dissertation mainly applies AC techniques to hardware to improve NN training efficiency. AC techniques at the hardware level are intensively studied since this layer primarily affects efficiency. In addition, regardless of the inference or training phase, NN (DNN) algorithms involve high computation, where the AC techniques in hardware can directly benefit it. Below, existing hardware-oriented AC techniques are described.

#### Approximate Adder

Many applications, such as image processing, need to perform addition [41], and the primary MAC computation in NN algorithm also utilizes addition and accumulation. Therefore, approximate adder circuits are studied [50, 51, 52, 53]. Reference [50] introduced to partition an adder to many segments and the carry operations between the separated segments are truncated to simplify the circuit architecture. Reference [51] directly applies aggressive logic reduction at transistor-level. Conventionally, aggressive

approximation frequently targets least-significant-bit (LSB) to prevent severe accuracy loss. Since the carry operation could be even more complicated along with the increased bits, the partial carry skip manipulation can alleviate the design cost and achieve higher efficiency.

### Approximate Multiplier

Multiplier is one of the most power-hungry and area-expensive operators, especially in FPUs [54]. Therefore, many researchers try hard to develop its approximate version to save computing resources. The approximate multiplier is especially adopted in NN for alleviating heavy MAC computation. A simple way to approximate multiplication can be implemented by directly rounding the input values to fewer bits before multiplication [55]. Also, since the multiplier circuits utilize many half or full adders to handle partial products, the techniques forming approximate adder mentioned in above can also be leveraged to form approximate multipliers. Besides, logarithm based multiplier is also proposed [36, 37, 56, 57, 58, 59] since logarithm converts multiplication to addition.

### Bit-width Scaling

Bit-width scaling (BWS) is a classical AC technique that uses fewer bits in computation. Its precision degrades at a smooth pace, which results in a more moderate approximation than other AC techniques such as an approximate multiplier. Many researches prefer to adopt BWS in NN since fewer bits achieve shorter latency and save incredible computation and even memory consumption [60, 61]. BWS is popular not only for NN inference engine but also for training due to its tractability, even for a very deep DNN model [33, 34, 35]. Although mainstream computing systems such as CPU and GPU conventionally apply FP32 (floating-point expression with 32 bits in total) for training modern DNN model, it is now considered that FP32 is more than necessary. Then, the training with a shorter format is explored for improving the training efficiency, such as FP16 [33, 34] or even partially FP8 [35]. Recently, tensor process unit (TPU) is developed based on an 8/16-bit format rather than 32-bit in order to achieve a light platform and DNN acceleration [15].

### Voltage Over Scaling (VOS)

At the operation level, reducing the voltage while fixing the operation clock period is the most direct way to achieve power/energy reduction [48, 62, 63]. However, regarding a fact that the circuit may experience timing error due to slower delay (latency) under low voltage, many computation errors or system catastrophic issues may happen. On the other hand, as long as those parts have the capability to tolerate the issues from timing error, the voltage can be aggressively scaled down to pursue significant power/energy efficiency. Conventionally, the scaled voltage in conventional VS would convey the

minimum voltage that induces zero timing error. On the other hand, VOS allows a certain timing error, and then it would reach even lower voltage than conventional VS.

### Hardware AC in NN Inference and Training Phase

Several researchers study how to apply AC techniques to NN [32, 38, 55, 60, 62, 64, 65, 66, 67]. A notable thing is that researches related to AC on inference engine are in majority rather than training engine. That is because of the different primary concerns. Given a well pre-trained NN model, the inference engine can be deeply compressed with [32, 64, 65, 66, 67] or without [58, 68, 69, 70] a little additional training. Even distillation is notably studied to shrink the NN model size [71]. Since NN is a kind of highly approximable paradigm, a light-weight inference engine with sustaining acceptable accuracy is realizable, and thus they can be accommodated in mobile systems, such as IoT [72].

On the other hand, quality (accuracy) is the most competitive factor in training NN. A more sophisticated NN (DNN) model accompanied by a large scale of the training dataset is thought to be highly sensitive to the approximation [55, 68], and aggressive approximation may result in low-confidence quality in training. In addition, since training systems need to record more temporal parameters (gradients, updated weights) compared with inference systems, AC techniques applied to training schemes rely on more smooth or moderate approximation in addition to memory-friendly strategy, such as BWS [33, 34, 35]. Training in totally fixed-point [27, 28] or log-domain [37] could be alternative ways since fixed-point and logarithm domain can highly compress the necessary bits of data representation from floating-point values and can significantly save the memory resource.

## 1.5 Low-power Design Methodology: Voltage Scaling

Low-power operations are eagerly demanded in various computing systems, such as IoTs [72, 73], wearable equipment [74], and the sensor networks [75], in addition to mobile terminals. According to long standby time, tiny volume, and limited energy sources, those applications have strong demands for consuming ultra-low power. Also, power consumption becomes the most competitive factor in modern mobile SOC [76], or even high-performance chips [77]. Designers are dedicated to pursuing the maximization of power or energy efficiency.

Voltage scaling (VS) is one of the most common and powerful techniques for power reduction. An AC technique, VOS, can be viewed as its subset and is already investigated to improve DNN efficiency [62]. Voltage reduction remarkably contributes to the quadratic gain of power-saving with the fundamental equation:

$$P = \frac{1}{2}CV^2 \quad (1.6)$$

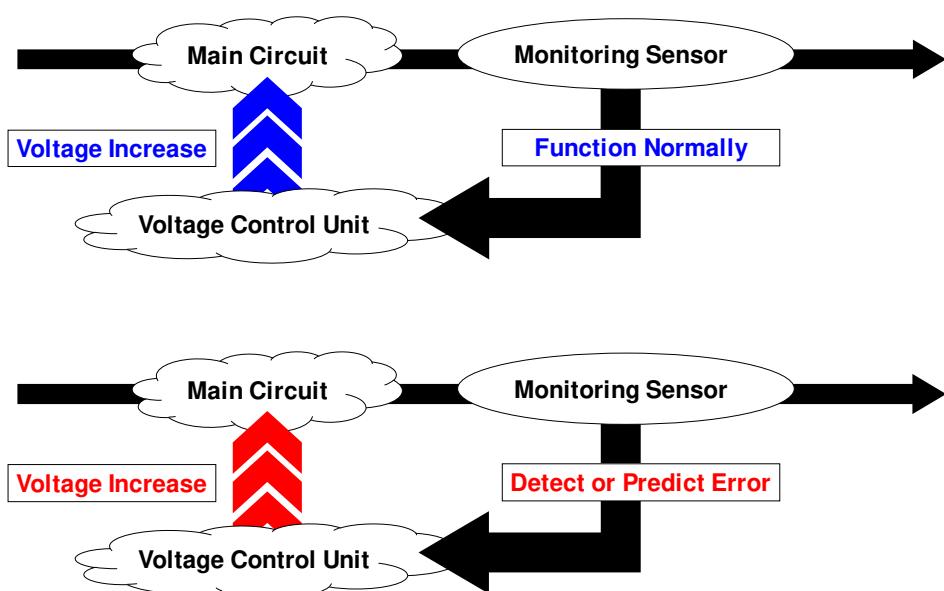

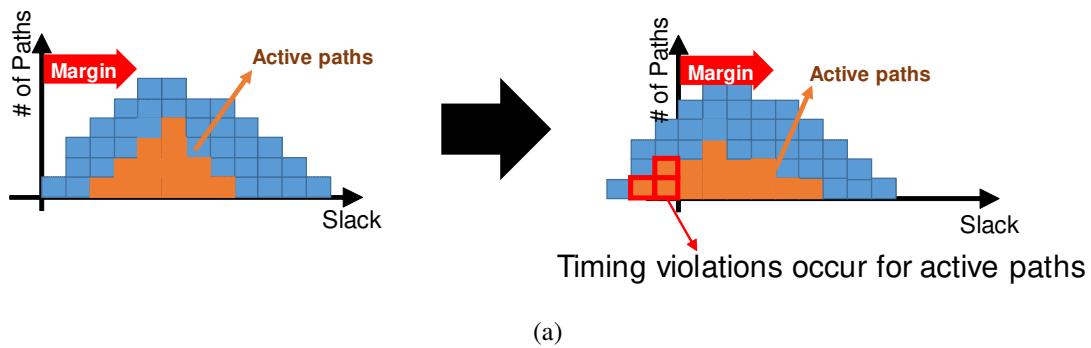

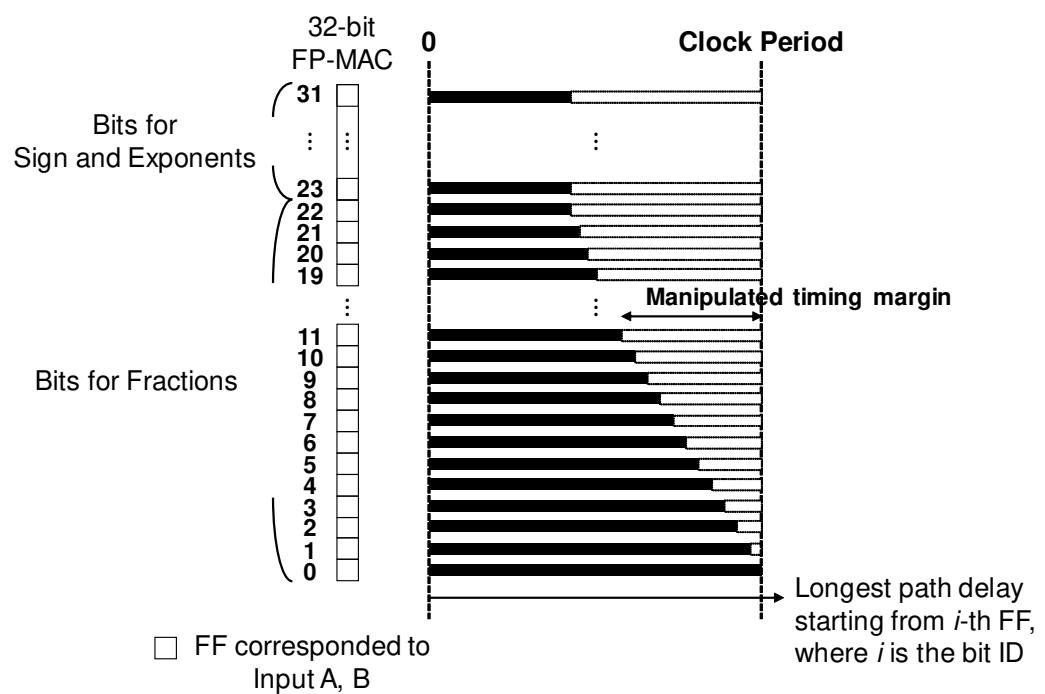

where  $P$  is the power,  $V$  is the voltage and  $C$  is the capacitance which should be invariant for a fabricated circuit. However, voltage decrease involves an increase in the circuit delay and raises the possibility of timing error. Therefore, the techniques to prevent timing errors are studied, and they can be categorized into two levels; operation level and design level. The former implements *in situ* monitoring devices in the circuits to adapt the supply voltage to maximize the power efficiency while sustaining circuit functionalities. These techniques are categorized as adaptive voltage scaling (AVS) techniques. The key idea is to insert the monitoring sensors behind the main circuits to detect or predict the logic error. If the main circuit keeps functional, then the voltage controlling unit keeps lowering down the supply voltage. On the other hand, once the sensors detect or predict the logic error, they would inform the controlling units to increase the voltage to maintain the functionality of the main circuit, as shown in Fig. 1.10. This area includes Razor [78], critical-path replicas [79], or canary flip-flops [80]. On the other hand, the latter intends to re-design the circuit such that the timing margin is manipulated to enhance voltage scaling efficiency. A state-of-the-art technique in this field is an activation-aware slack assignment (ASA), which associates the timing criticality of a path with its topological path delay and activity. A very recent research [81, 82] proposed an ASA method that allocates the timing margin with a stochastic mean-time-to-failure (MTTF) analysis. The timing errors are characterized by statistical static timing analysis and path activation analysis. This method accepts very few yet certain timing errors, and hence voltage can be aggressively scaled down.

Figs. 1.11(a) and 1.11(b) illustrates the concept of ASA, which originates from an earlier technique so-called critical path isolation (CPI) [82, 83, 84, 85]. ASA manipulates a synthesized circuit for the active paths by buffer insertion and cell swapping to allocate timing margin during an engineering change order (ECO) phase. After ASA, the active paths have more timing margin so that VS is applicable without timing error occurrence. Although the manipulation might increase the area due to inserted buffers and larger-size gates, the extra timing margin enables us to apply voltage scaling.