|              |                                                                                                                                                                                                                                                                     |

|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title        | An Experimental Study on Terrestrial Radiation-Induced Single Event Upsets in Planar and FinFET SRAMs                                                                                                                                                               |

| Author(s)    | 黒木, 貴志                                                                                                                                                                                                                                                              |

| Citation     | 大阪大学, 2021, 博士論文                                                                                                                                                                                                                                                    |

| Version Type | VoR                                                                                                                                                                                                                                                                 |

| URL          | <a href="https://doi.org/10.18910/82290">https://doi.org/10.18910/82290</a>                                                                                                                                                                                         |

| rights       | © 2021 IEEE. Reprinted, with permission, from T. Kato et al., "Muon-Induced Single-Event Upsets in 20-nm SRAMs: Comparative Characterization With Neutrons and Alpha Particles," in IEEE Transactions on Nuclear Science, vol. 68, no. 7, pp. 1436-1444, July 2021. |

| Note         |                                                                                                                                                                                                                                                                     |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

# An Experimental Study on Terrestrial Radiation-Induced Single Event Upsets in Planar and FinFET SRAMs

Submitted to

Graduate School of Information Science and Technology

Osaka University

January 2021

Takashi KATO

## Publications

Major publications in this dissertation:

1. **T. Kato**, M. Tampo, S. Takeshita, H. Tanaka, H. Matsuyama, M. Hashimoto, and Y. Miyake, "Muon-induced single-event upsets in 20-nm SRAMs: comparative characterization with neutrons and alpha particles," *IEEE Trans. Nucl. Sci.*, submitted, Oct. 2020.

2. **T. Kato**, M. Hashimoto, and H. Matsuyama, "Angular sensitivity of neutron-induced single-event upsets in 12-nm FinFET SRAMs with comparison to 20-nm planar SRAMs," *IEEE Trans. Nucl. Sci.*, vol. 67, no. 7, pp. 1485–1493, Jul. 2020.

3. **T. Kato**, T. Yamazaki, N. Saito, and H. Matsuyama, "Neutron-induced multiple-cell upsets in 20 nm bulk SRAM: angular sensitivity and impact of multi-well potential perturbation," *IEEE Trans. Nucl. Sci.*, vol. 66, no. 7, pp. 1381–1389, Jul. 2019.

4. **T. Kato**, T. Yamazaki, K. Maruyama, T. Soeda, H. Itsuji, D. Kobayashi, K. Hirose, and H. Matsuyama, "The impact of multiple-cell charge generation on multiple-cell upset in a 20-nm bulk SRAM," *IEEE Trans. Nucl. Sci.*, vol. 65, no. 8, pp. 1900–1907, Aug. 2018.

Other publications:

1. K. Takeuchi, K. Sakamoto, K. Yukumatsu, K. Watanabe, Y. Tsuchiya, **T. Kato**, H. Matsuyama, A. Takeyama, T. Ohshima, S. Kuboyama, and H. Shindo, "Characteristic charge collection mechanism observed in FinFET SRAM cells," in *Proc. Eur. Conf. Radiat. Its Effects Compon. Syst. (RADECS)*, 2020.

2. K. Kobayashi, J. Furuta, H. Maruoka, M. Hifumi, S. Kumashiro, **T. Kato**, and S. Kohri, "A 16 nm FinFET radiation-hardened flip-flop, bistable cross-coupled dual-modular-redundancy FF for terrestrial and outer-space highly-reliable systems," in *Proc. IEEE Int. Reliab. Phys. Symp. (IRPS)*, 2017, pp. SE-2.1–SE-2.3.

3. **T. Kato** and H. Matsuyama, "Impact of deep p-well structure on single event latchup in bulk CMOS," in *Proc. Int. Conf. Simul. Semicond. Process Devices (SISPAD)*, 2015, pp. 365–368.

4. T. Yamazaki, **T. Kato**, T. Uemura, H. Matsuyama, Y. Tada, K. Yamazaki, T. Soeda, T. Miyajima, and Y. Kataoka, "Origin analysis of thermal neutron soft error rate at nanometer scale," *J. Vac. Sci. Technol., B*, vol. 33, no. 2, pp. 020604-1–020604-4, Mar. 2015.

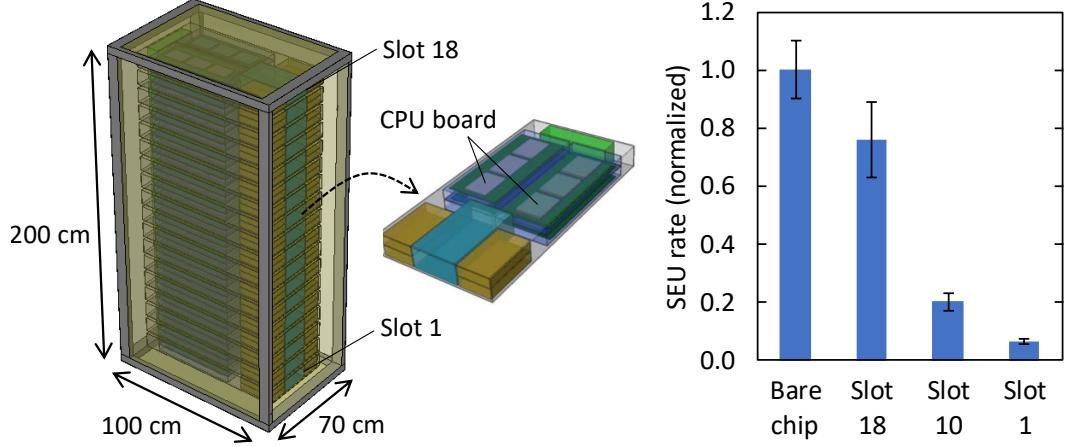

5. **T. Kato**, R. Akano, T. Uemura, Y. Watanabe, and H. Matsuyama, "Neutron shielding effect of stacked servers and its impact on reduction of soft error rate," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 3408–3415, Dec. 2014.

6. T. Uemura, **T. Kato**, R. Tanabe, H. Iwata, J. Ariyoshi, H. Matsuyama, and M. Hashimoto, "Exploring well-configurations for minimizing single event latchup," *IEEE Trans. Nucl. Sci.*, vol. 61, no. 6, pp. 3282–3289, Dec. 2014.

7. **T. Kato**, T. Uemura, and H. Matsuyama, "High-accuracy estimation of soft error rate using PHYSERD with circuit simulation," in *Proc. Int. Conf. Simul. Semicond. Process Devices (SISPAD)*, 2014, pp. 345–348.

8. T. Uemura, **T. Kato**, R. Tanabe, H. Iwata, H. Matsuyama, M. Hashimoto, K. Takahisa, M. Fukuda, and K. Hatanaka, "Preventing single event latchup with deep p-well on p-substrate," in *Proc. IEEE Int. Reliab. Phys. Symp. (IRPS)*, 2014, pp. SE.3.1–SE.3.4.

9. T. Uemura, **T. Kato**, H. Matsuyama, and M. Hashimoto, "Mitigating multi-bit-upset with well-slits in 28 nm multi-bit-latch," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4362–4367, Dec. 2013.

10. T. Uemura, **T. Kato**, H. Matsuyama, and M. Hashimoto, "Soft-error in SRAM at ultra-low voltage and impact of secondary proton in terrestrial environment," *IEEE Trans. Nucl. Sci.*, vol. 60, no. 6, pp. 4232–4237, Dec. 2013.

11. T. Uemura, **T. Kato**, and H. Matsuyama, "Impact of parasitic bipolar action and soft-error trend in bulk CMOS at terrestrial environment," in *Proc. IEEE Int. Reliab. Phys. Symp. (IRPS)*, 2013, pp. 6C.4.1–6C.4.6.

12. **T. Kato**, T. Uemura, H. Mori, Y. Ikeda, K. Suzuki, S. Satoh, and H. Matsuyama, "Impact of parasitic bipolar effect on single-event upset in p-type metal-oxide-semiconductor field effect transistor with embedded SiGe," *Jpn. J. Appl. Phys.*, vol. 52, no. 4S, pp. 04CC15-1–04CC15-5, Mar. 2013.

13. **T. Kato**, T. Uemura, H. Mori, Y. Ikeda, K. Suzuki, S. Satoh, and H. Matsuyama, "Radiation-induced parasitic bipolar effect in PMOS with embedded SiGe," in *Proc. Int. Conf. on Solid State Devices and Materials (SSDM)*, 2012, pp. 847–848.

14. Y. Ikeda, H. Mori, **T. Kato**, T. Uemura, M. Yoshida, M. Onoda, and H. Matsuyama, "Investigation of BTI degradation in LDMOS transistors," in *Proc. Int. Conf. on Solid State Devices and Materials (SSDM)*, 2012, pp. 454–455.

15. H. Mori, Y. Ikeda, **T. Kato**, T. Uemura, and H. Matsuyama, "Lifetime evaluation on AC stress in high-k / metal-gate with using dual-pulsed-test-system," in *Proc. Int. Conf. on Solid State Devices and Materials (SSDM)*, 2012, pp. 122–123.

16. T. Uemura, **T. Kato**, H. Matsuyama, K. Takahisa, M. Fukuda, and K. Hatanaka, "Investigation of multi cell upset in sequential logic and validity of redundancy technique," in *Proc. IEEE Int. On-Line Testing Symp. (IOLTS)*, 2011, pp. 7–12.

## Abstract

In the terrestrial environment, all semiconductor devices are continuously exposed to terrestrial radiations originating from cosmic-rays and natural radioisotopes. A problem is that the terrestrial radiations deposit charge on the semiconductor devices through ionization and can cause transient errors, so-called soft errors.

The growing integration of semiconductor devices, such as system-on-a-chips, has increased the susceptibility to the terrestrial radiations and has made the soft error problem more challenging. At the same time, the soft error phenomena have become complex due to the aggressive scaling of transistors. Among the semiconductor devices, static random access memories (SRAMs) are one of the most susceptible devices to the terrestrial radiations. This is because the SRAM devices have been highly integrated, and because the size and voltage scaling of SRAM cells has drastically decreased the amount of stored charge. Therefore, the appropriate understanding of the terrestrial radiation-induced soft errors in the SRAM devices is necessary to cope with soft error issues in advanced semiconductor devices.

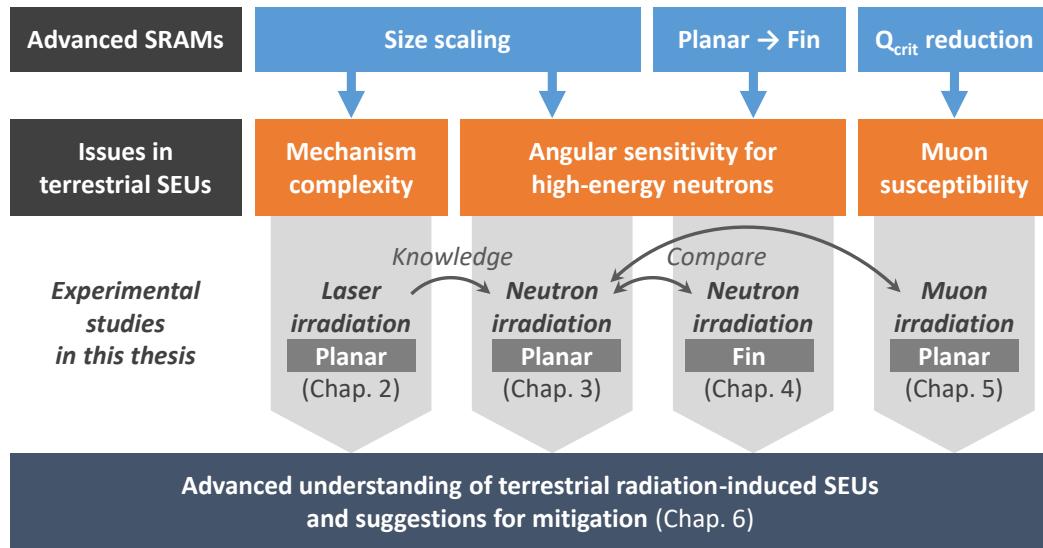

This thesis focuses on single-event upsets (SEUs) and multiple-cell upsets (MCUs) induced by the terrestrial radiations in advanced SRAMs, with the aim of understanding the impact of the technology advancement on the SEU and MCU responses. For the advanced SRAMs, this thesis deals with both planar and fin-shaped field-effect transistor (FinFET) technologies. For the terrestrial radiations, the major sources of the SEUs have been considered to be high-energy neutrons, thermal neutrons, and alpha particles. In addition to these particles, negative and positive muons have recently received great attention as potential sources of the SEUs. This thesis covers all these particles. The SEU and MCU responses of the planar and FinFET SRAMs are extensively studied by a variety of experimental methods. In particular, particle irradiation testing is performed for all the above particles. Moreover, an emerging laser irradiation technique is utilized to explore the underlying mechanism.

The studies in this thesis address the effects of size scaling, critical charge reduction, and transistor geometry change, which are the key factors in the technology advancement of SRAMs. The studies begin with the exploration of MCU mechanisms complicated by the size scaling. Single-pulse laser irradiations unveil a novel mechanism, named multi-well coupled potential unbalancing. The size scaling also affects the angular sensitivity of high-energy neutron-induced SEUs and MCUs. High-energy neutron irradiations at several incidence angles reveal the significant angular dependence of SEU and MCU responses in 20-nm planar SRAMs. This angular sensitivity is also studied in 12-nm FinFET SRAMs. The comparative analyses between the planar and FinFET SRAMs demonstrate the difference in the angular sensitivities due to the transistor geometry change. The final study investigates muon-induced SEUs and MCUs, which can be significant due to the critical charge reduction. The unique SEU and MCU characteristics are clarified in the 20-nm planar SRAMs through negative and positive muon irradiations with comparison to

other terrestrial radiations.

This thesis provides interesting and insightful findings through the studies based on various irradiation experiments and deepens the understanding of the terrestrial radiation-induced SEUs in advanced SRAMs. The findings are meaningful not only for understanding SEU phenomena, but also for developing effective mitigation techniques. On the basis of the obtained findings, some suggestions are offered for SEU mitigation. Therefore, the results yielded in this thesis will be helpful for resolving soft error problems and for achieving radiation tolerance in current and future semiconductor devices.

## *Acknowledgements*

First and foremost, I would like to sincerely thank my supervisor Prof. Masanori Hashimoto of Osaka University for his invaluable advice and patient guidance during the developing of this thesis. Without his dedication and support, I could not have completed it. I feel really fortunate to have the opportunity of this work under his supervision.

I would like to express my sincere gratitude to Prof. Noriyuki Miura of Osaka University, Prof. Kazutoshi Kobayashi of Kyoto Institute of Technology, and Prof. Hiroyuki Nakagawa of Osaka University for their thorough review of this thesis. Their insightful comments and valuable suggestions have significantly helped me to improve and complete this thesis.

I am deeply grateful to Hiroshi Namba, Yoshihiro Ito, and Dr. Hideya Matsuyama of Socionext Inc. Their persistent support and advice have contributed not only to the accomplishment of my work but also to my professional development.

My heartfelt appreciation is extended to Dr. Taiki Uemura of Samsung Electronics, who introduced me to this fascinating field of soft errors. My research would not have started without his leadership and guidance.

I would like to express my appreciation to Dr. Takeshi Soeda, Dr. Takashi Yamazaki, and Dr. Kazunori Maruyama of Fujitsu Laboratories Ltd. for their close collaboration in irradiation experiments and sophisticated analyses.

I would like to thank Prof. Mitsuhiro Fukuda, Prof. Tomokazu Suzuki, , and Sachiko Okajima of Osaka University and Prof. Keiji Takahisa of Kobe Tokiwa University for their enormous support in spallation neutron irradiation experiments at Research Center for Nuclear Physics, Osaka University.

I would like to offer my appreciation to Prof. Kazuyuki Hirose and Prof. Daisuke Kobayashi of Institute of Space and Astronautical Science, Japan Aerospace Exploration Agency and Dr. Hiroaki Itsuji of Hitachi, Ltd. for their significant contribution on laser irradiation experiments.

I wish to express my thanks to Prof. Yasuhiro Miyake, Prof. Soshi Takeshita, and Dr. Motonobu Tampo of High Energy Accelerator Research Organization for their invaluable contribution on muon irradiation experiments at Muon Science Establishment, Japan Proton Accelerator Research Complex. Thanks are also offered to Prof. Wang Liao of Kochi University of Technology, Dr. Izumi Umegaki of Toyota Central R&D Labs., Inc., and Shogo Doiuchi of High Energy Accelerator Research Organization for their valuable advice and technical assistance.

I would like to show my appreciation to Prof. Hiroki Tanaka of Kyoto University for his important contribution on thermal neutron irradiation experiments at Kyoto University Research Reactor.

My special thanks go to Prof. Yukinobu Watanabe of Kyushu University and Dr. Shin-ichiro Abe of Japan Atomic Energy Agency for their fruitful discussion on radiation effects and useful advice on numerical simulation.

Special thanks also go to Shumpei Kohri of Tokyo Institute of Technology, Dr. Shigetaka Kumashiro of Renesas Electronics Corporation, and Prof. Jun Furuta of Kyoto Institute of Technology for their kind support and technical discussion.

I am also indebted to the many other people, in Socionext Inc. and Fujitsu Semiconductor Limited, who have helped my work in numerous ways. This includes Shigeo Satoh, Kaina Suzuki, Hideo Akiyoshi, Tomoya Tsuruta, Ryo Tanabe, Junji Iwahori, Hiroshi Iwata, Masataka Sato, Tsunehisa Sakoda, Hiroko Mori, Noriaki Saito, Yasunori Ichimura, Tomoyuki Oki, Masashi Okamoto, Tsuyoshi Moribe, Takumi Hasegawa, Yoshiyuki Okuda, and Shunichi Okano.

And finally, but most importantly, I thank my wife Makiko and daughters Nina and Mana for their constant support, patience, and love.

# Contents

|                                                                                 |            |

|---------------------------------------------------------------------------------|------------|

| <b>Publications</b>                                                             | <b>iii</b> |

| <b>Abstract</b>                                                                 | <b>v</b>   |

| <b>Acknowledgements</b>                                                         | <b>vii</b> |

| <b>1 Introduction</b>                                                           | <b>1</b>   |

| 1.1 Soft Errors in Semiconductor Devices . . . . .                              | 1          |

| 1.2 Terrestrial Radiation . . . . .                                             | 3          |

| 1.2.1 Neutrons . . . . .                                                        | 5          |

| 1.2.2 Muons . . . . .                                                           | 10         |

| 1.2.3 Alpha Particles . . . . .                                                 | 12         |

| 1.3 Single-Event Upsets in SRAMs . . . . .                                      | 13         |

| 1.3.1 SRAM Circuit . . . . .                                                    | 13         |

| 1.3.2 Single-Event Upset . . . . .                                              | 15         |

| 1.3.3 Classification . . . . .                                                  | 16         |

| 1.3.4 SEU CS and SEU Rate . . . . .                                             | 17         |

| 1.3.5 Technology Dependence . . . . .                                           | 19         |

| 1.3.6 MCU Mechanisms . . . . .                                                  | 22         |

| 1.4 Challenges in Terrestrial Radiation-Induced SEUs . . . . .                  | 25         |

| 1.5 Objective and Overview of This Thesis . . . . .                             | 27         |

| <b>2 Novel MCU Mechanism in Scaled SRAMs</b>                                    | <b>31</b>  |

| 2.1 Introduction . . . . .                                                      | 31         |

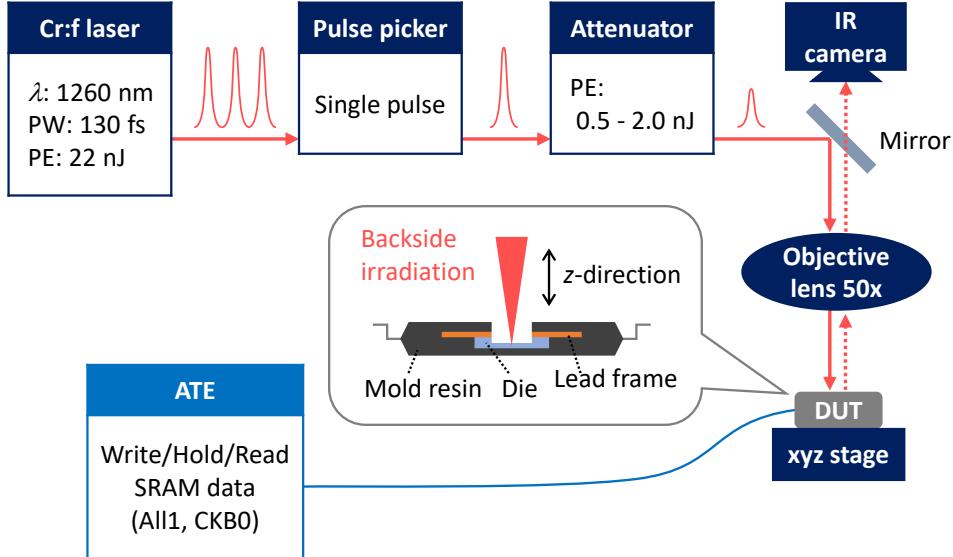

| 2.2 Experimental Setup . . . . .                                                | 33         |

| 2.2.1 TPA Laser Irradiation . . . . .                                           | 33         |

| 2.2.2 Tested Device and Operation . . . . .                                     | 33         |

| 2.3 Results and Discussion . . . . .                                            | 34         |

| 2.3.1 Focal Position Dependence of SEU Susceptibility . . . . .                 | 34         |

| 2.3.2 Effects of Supply Voltage and Data Pattern on TPA-induced MCUs . . . . .  | 36         |

| 2.3.3 Exploration of a Novel MCU Mechanism Based on Fail Bit Patterns . . . . . | 41         |

| 2.3.4 MCU Response to Multiple Single-Pulse Laser Irradiation . . . . .         | 46         |

| 2.4 Conclusion . . . . .                                                        | 50         |

|                                                                            |           |

|----------------------------------------------------------------------------|-----------|

| <b>3 Angular Sensitivity of Neutron-Induced SEUs in Planar SRAMs</b>       | <b>51</b> |

| 3.1 Introduction . . . . .                                                 | 51        |

| 3.2 Experimental Setup . . . . .                                           | 53        |

| 3.2.1 Tested Device and Operation . . . . .                                | 53        |

| 3.2.2 High-Energy Neutron Irradiation . . . . .                            | 53        |

| 3.2.3 Rate Calculation . . . . .                                           | 54        |

| 3.3 Results and Discussion . . . . .                                       | 56        |

| 3.3.1 Angular Dependence of SEU, MCU, and MBU Rates . . . . .              | 56        |

| 3.3.2 Characterization of MCU Events . . . . .                             | 60        |

| 3.3.3 Exploration of the MCU Mechanism . . . . .                           | 65        |

| 3.3.4 Indication of the MWCPU Contribution in FBMs . . . . .               | 68        |

| 3.4 Conclusion . . . . .                                                   | 71        |

| <b>4 Angular Sensitivity of Neutron-Induced SEUs in FinFET SRAMs</b>       | <b>73</b> |

| 4.1 Introduction . . . . .                                                 | 73        |

| 4.2 Experimental Setup . . . . .                                           | 75        |

| 4.2.1 Tested Device and Operation . . . . .                                | 75        |

| 4.2.2 High-Energy Neutron Irradiation . . . . .                            | 76        |

| 4.2.3 Rate Calculation . . . . .                                           | 76        |

| 4.3 Results and Discussion . . . . .                                       | 77        |

| 4.3.1 Angular Dependence of SEU, MCU, and MBU Rates . . . . .              | 77        |

| 4.3.2 Analyses of MCU Ratios and Mechanism Investigation . . . . .         | 82        |

| 4.3.3 Angular Response of MCU Characteristics . . . . .                    | 85        |

| 4.3.4 Voltage Dependence of Pattern-Wise MCU Ratios . . . . .              | 90        |

| 4.4 Conclusion . . . . .                                                   | 92        |

| <b>5 Muon-Induced SEUs With Comparison to Other Terrestrial Radiations</b> | <b>93</b> |

| 5.1 Introduction . . . . .                                                 | 93        |

| 5.2 Experimental Setup . . . . .                                           | 95        |

| 5.2.1 Tested Device and Operation . . . . .                                | 95        |

| 5.2.2 Particle Irradiation . . . . .                                       | 96        |

| Negative and Positive Muons . . . . .                                      | 96        |

| High-Energy Neutron . . . . .                                              | 96        |

| Thermal Neutron . . . . .                                                  | 96        |

| Alpha Particle . . . . .                                                   | 97        |

| 5.2.3 CS Calculation . . . . .                                             | 97        |

| 5.3 Results and Discussion . . . . .                                       | 98        |

| 5.3.1 Muon Energy Dependence of SEU, SBU, and MCU CSs . . . . .            | 98        |

| 5.3.2 Supply Voltage Dependence of SEU, MCU, and MBU CSs . . . . .         | 100       |

| 5.3.3 Analysis of MCU Ratios . . . . .                                     | 104       |

| 5.3.4 Analysis of MCU Characteristics . . . . .                            | 106       |

| 5.4 Conclusion . . . . .                                                   | 110       |

|                                              |            |

|----------------------------------------------|------------|

| <b>6 Conclusion</b>                          | <b>111</b> |

| 6.1 Findings and Contributions . . . . .     | 111        |

| 6.2 Suggestions for SEU Mitigation . . . . . | 114        |

| 6.3 Future Directions . . . . .              | 115        |

| <b>Bibliography</b>                          | <b>117</b> |

# List of Figures

|      |                                                                                                                                                        |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 1.1  | Schematic structures of planar FET and FinFET. . . . .                                                                                                 | 2  |

| 1.2  | Energy spectra of atmospheric neutrons, muons, and protons at sea level. . . . .                                                                       | 3  |

| 1.3  | Energy spectra of atmospheric neutrons at sea level. . . . .                                                                                           | 5  |

| 1.4  | Secondary ions produced by terrestrial high-energy neutrons as a function of the energy. . . . .                                                       | 6  |

| 1.5  | LETs and ranges in silicon for protons, alpha particles, lithium ions, sodium ions, and aluminum ions as a function of energy. . . . .                 | 7  |

| 1.6  | Total track length of secondary ions produced in silicon by terrestrial high-energy neutrons as a function of their LETs. . . . .                      | 8  |

| 1.7  | Cross section of neutron-induced nuclear reactions for $^{28}\text{Si}$ , $^{10}\text{B}$ , and $^{11}\text{B}$ atoms as a function of energy. . . . . | 8  |

| 1.8  | LETs in silicon for an alpha particle of 1.47 MeV and a lithium ion of 0.84 MeV as a function of depth. . . . .                                        | 9  |

| 1.9  | 3DAP analysis of $^{10}\text{B}$ atoms in a tungsten plug [26]. . . . .                                                                                | 10 |

| 1.10 | LETs in silicon for muons and protons as a function of energy. . . . .                                                                                 | 11 |

| 1.11 | LET in silicon for alpha particles with energies of 4.0 MeV to 8.5 MeV as a function of dept. . . . .                                                  | 13 |

| 1.12 | SRAM circuit and schematic cell layout. . . . .                                                                                                        | 14 |

| 1.13 | Simulated SEU contribution of nMOS and pMOS transistors in a 28-nm bulk planar SRAM [37]. . . . .                                                      | 16 |

| 1.14 | SEE classification. . . . .                                                                                                                            | 17 |

| 1.15 | Simulated SEU rate reduction for terrestrial high-energy neutrons due to the shielding effect of a server structure [39]. . . . .                      | 19 |

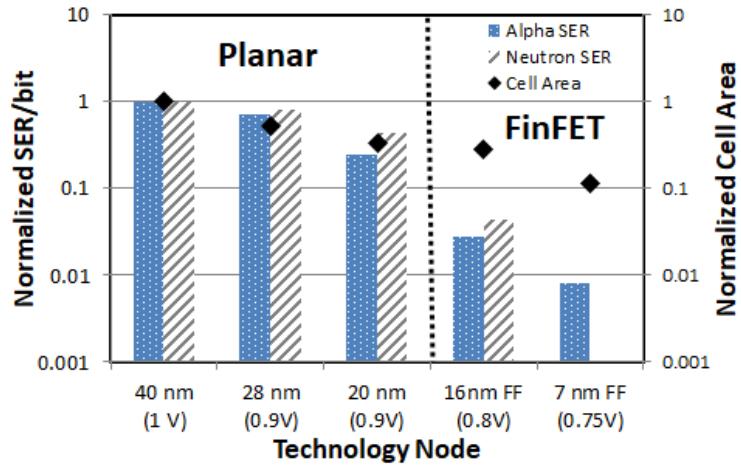

| 1.16 | Technology trend of alpha particle- and high-energy neutron-induced SERs for SRAMs from a 40-nm planar to a 7-nm FinFET technologies [42]. . . . .     | 20 |

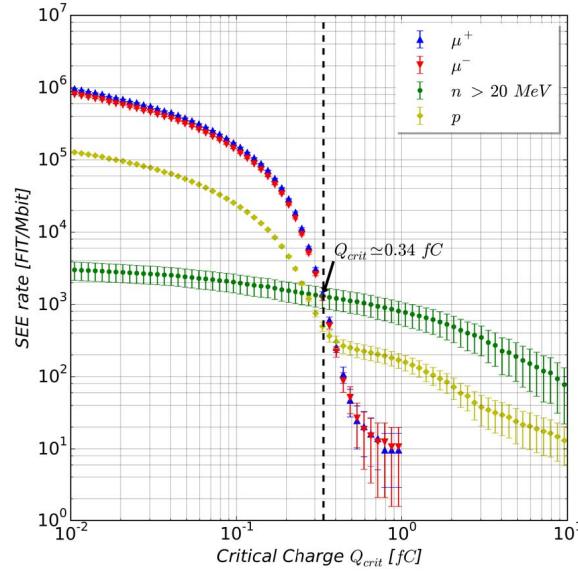

| 1.17 | Simulated SER for terrestrial radiation particles as a function of critical charge [14]. . . . .                                                       | 21 |

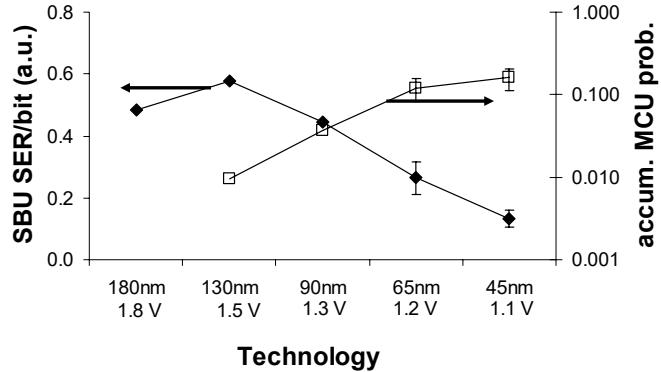

| 1.18 | Neutron-induced SBU SER and MCU probability for SRAMs from a 180-nm to a 45-nm planar technologies [51]. . . . .                                       | 22 |

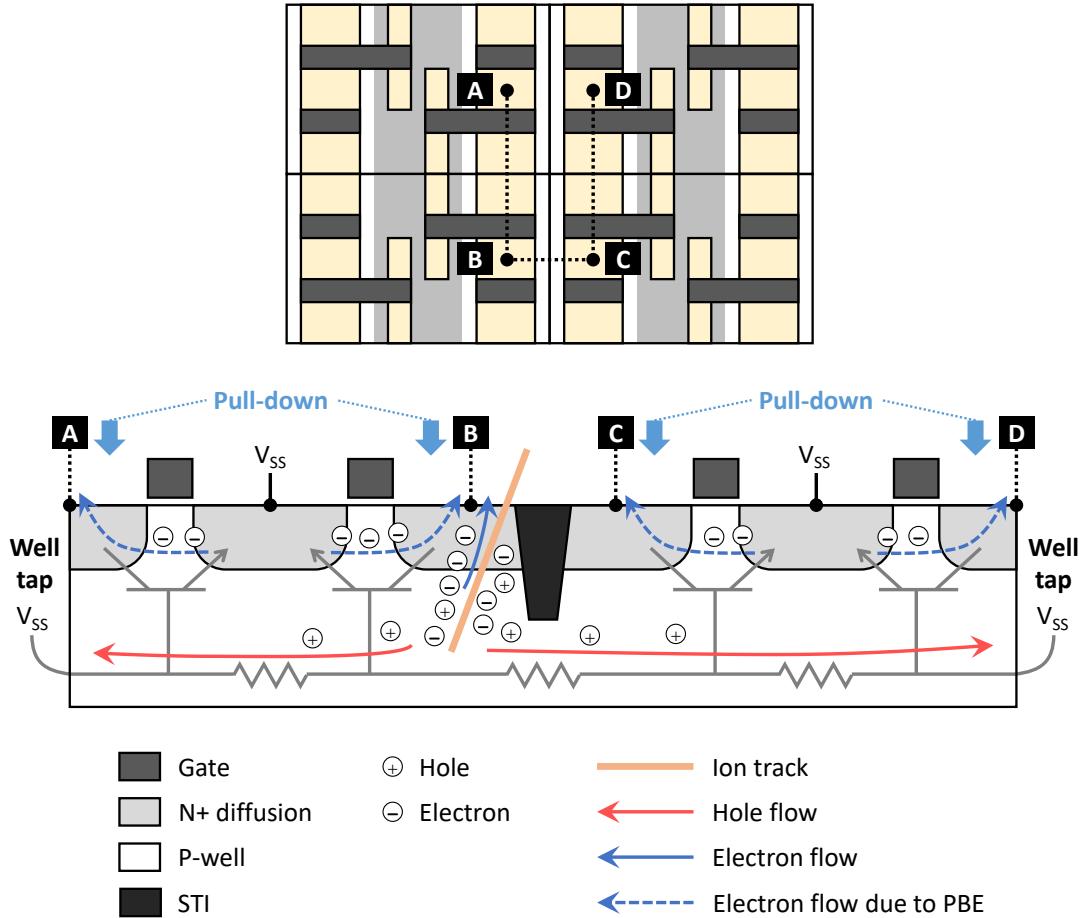

| 1.19 | Conceptual illustration of PBEs in SRAM cells. . . . .                                                                                                 | 24 |

| 1.20 | Overview of this thesis. . . . .                                                                                                                       | 27 |

| 2.1  | TPA-based soft error simulation system with ATE. . . . .                                                                                               | 33 |

|      |                                                                                                                                                                                |    |

|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

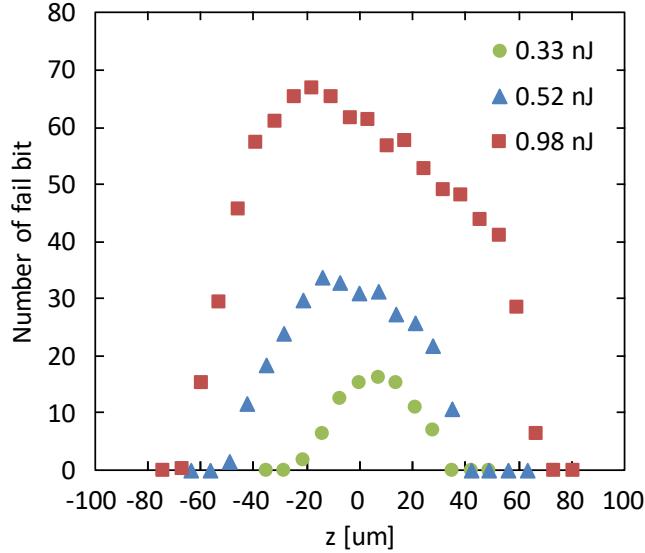

| 2.2  | Number of fail bits as a function of the focal position in $z$ -direction. . . . .                                                                                             | 35 |

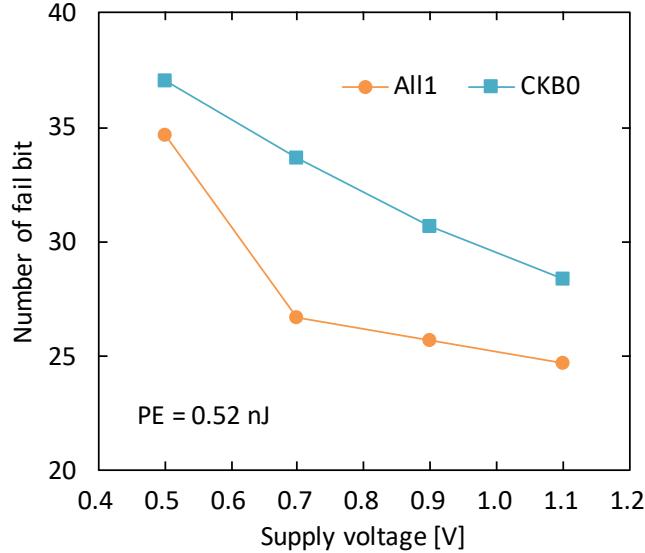

| 2.3  | Supply voltage dependence of the number of fail bits for All0 and CKB0 patterns. . . . .                                                                                       | 37 |

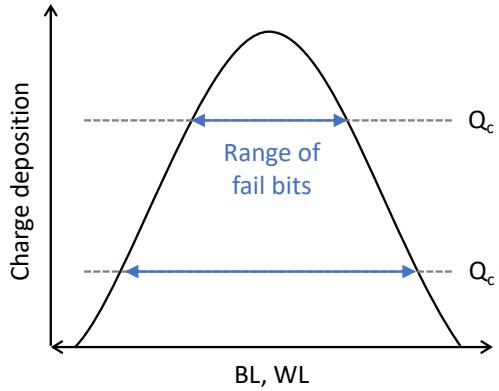

| 2.4  | Conceptual illustration of the relationship between the critical charge and the WL or BL range of fail bits for a given distribution of TPA-induced charge deposition. . . . . | 38 |

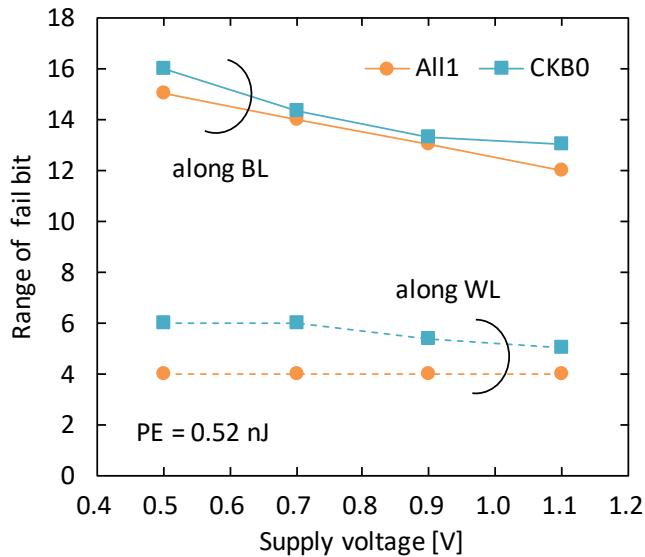

| 2.5  | WL and BL ranges of fail bits as a function of supply voltage for All0 and CKB0 patterns. . . . .                                                                              | 38 |

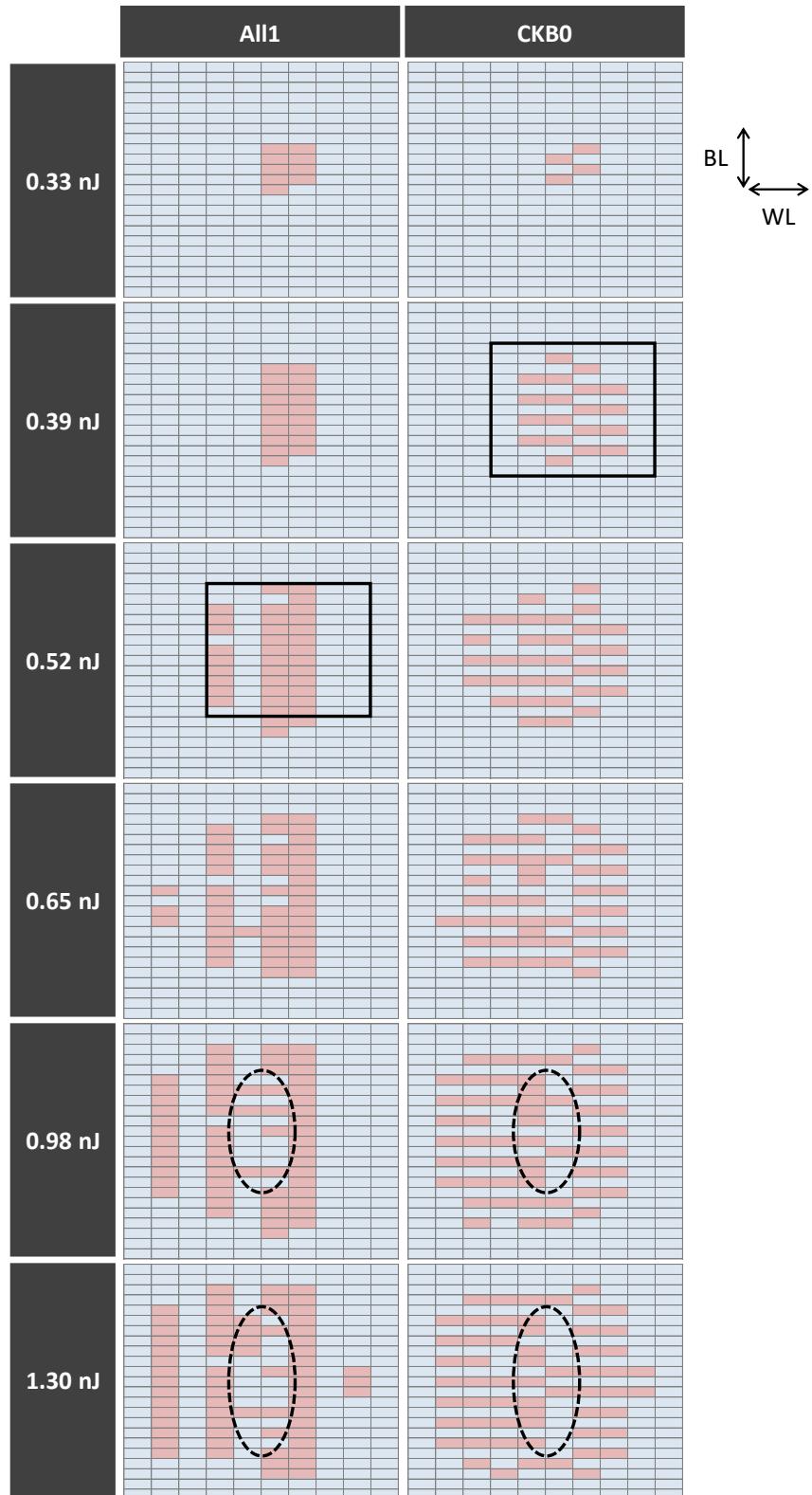

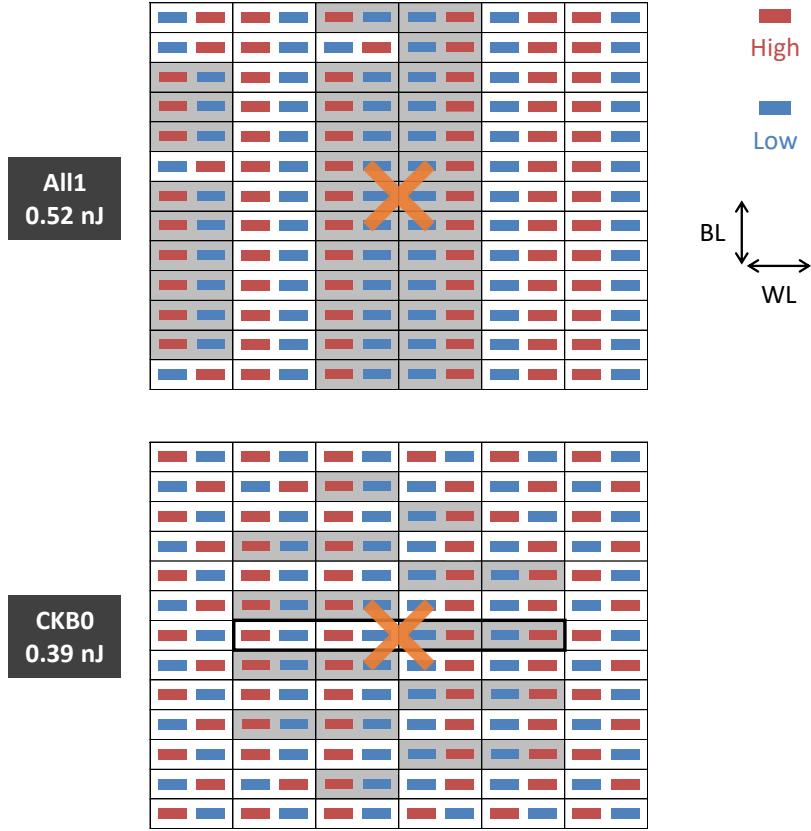

| 2.6  | FBMs for PEs from 0.33 to 1.30 nJ and for All1 and CKB0 patterns. . . . .                                                                                                      | 40 |

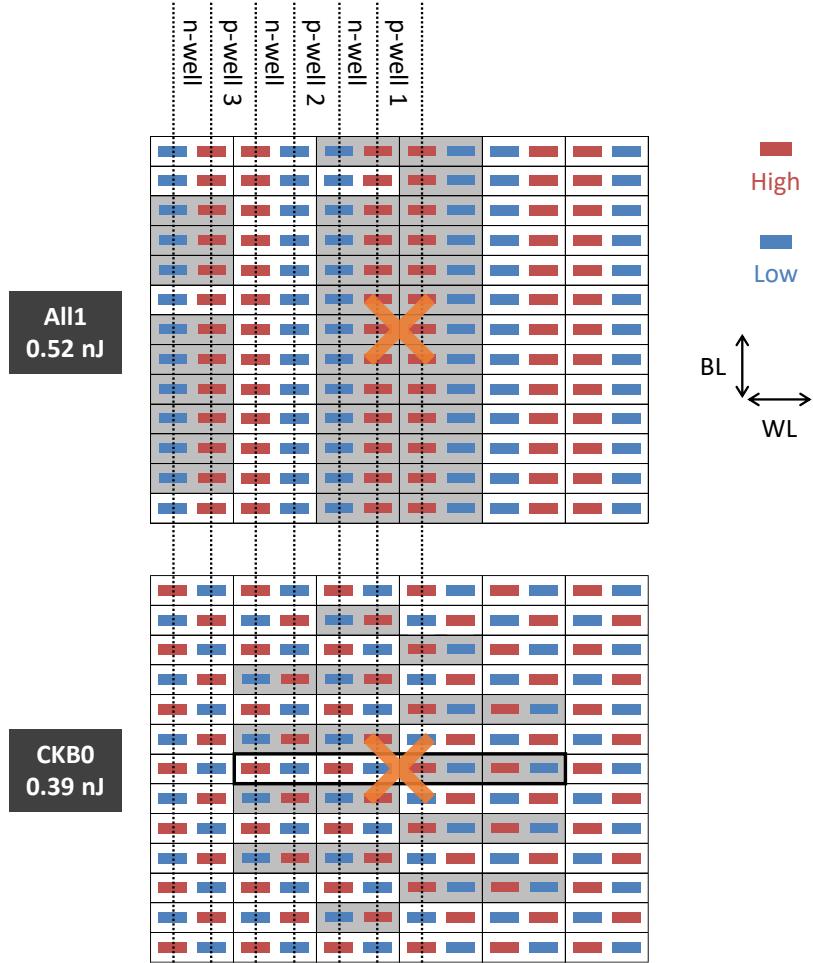

| 2.7  | FBMs with internal node voltages before laser irradiation for All1 and CKB0 patterns. . . . .                                                                                  | 42 |

| 2.8  | FBMs with internal node voltages after laser irradiation for All1 and CKB0 patterns. . . . .                                                                                   | 43 |

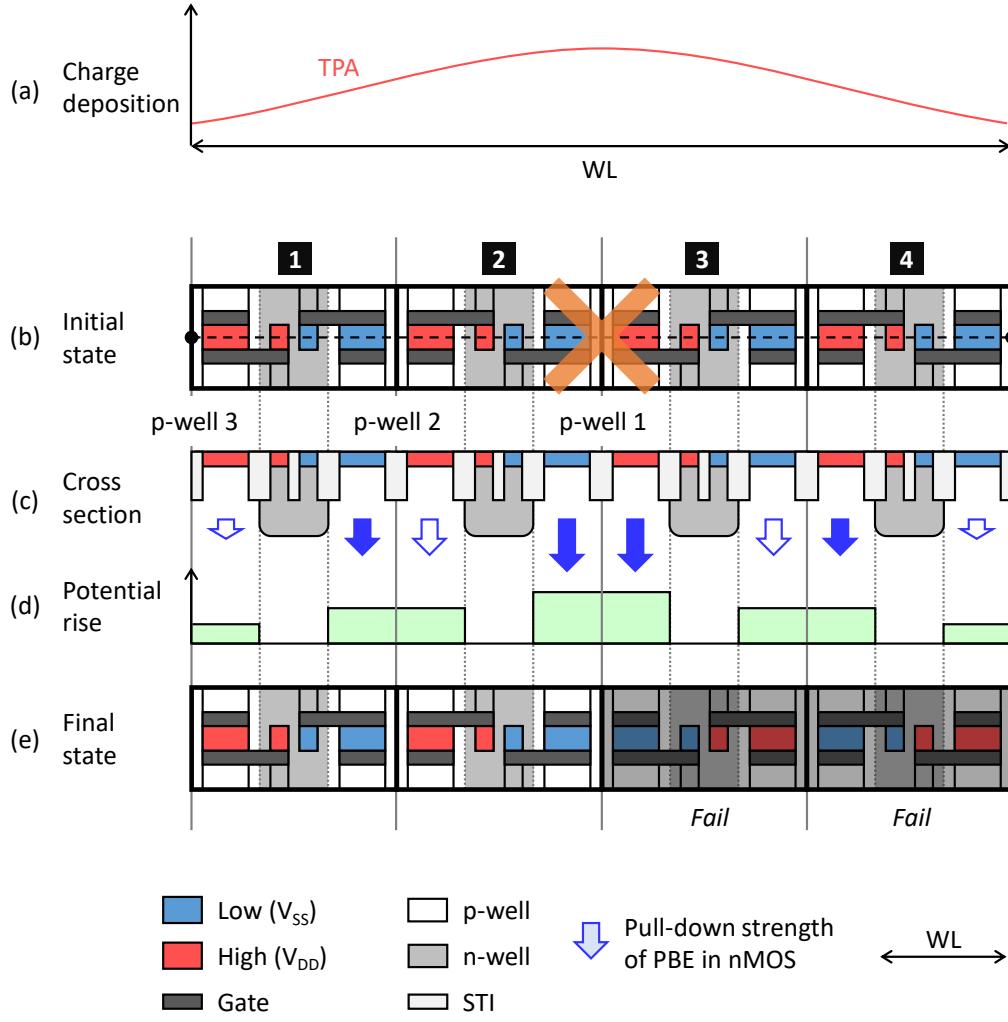

| 2.9  | MWCPU-induced node voltage transition for four SRAM cells in the case of CKB0 pattern. . . . .                                                                                 | 44 |

| 2.10 | Fail bit patterns along the BL direction caused by well potential perturbation. . . . .                                                                                        | 46 |

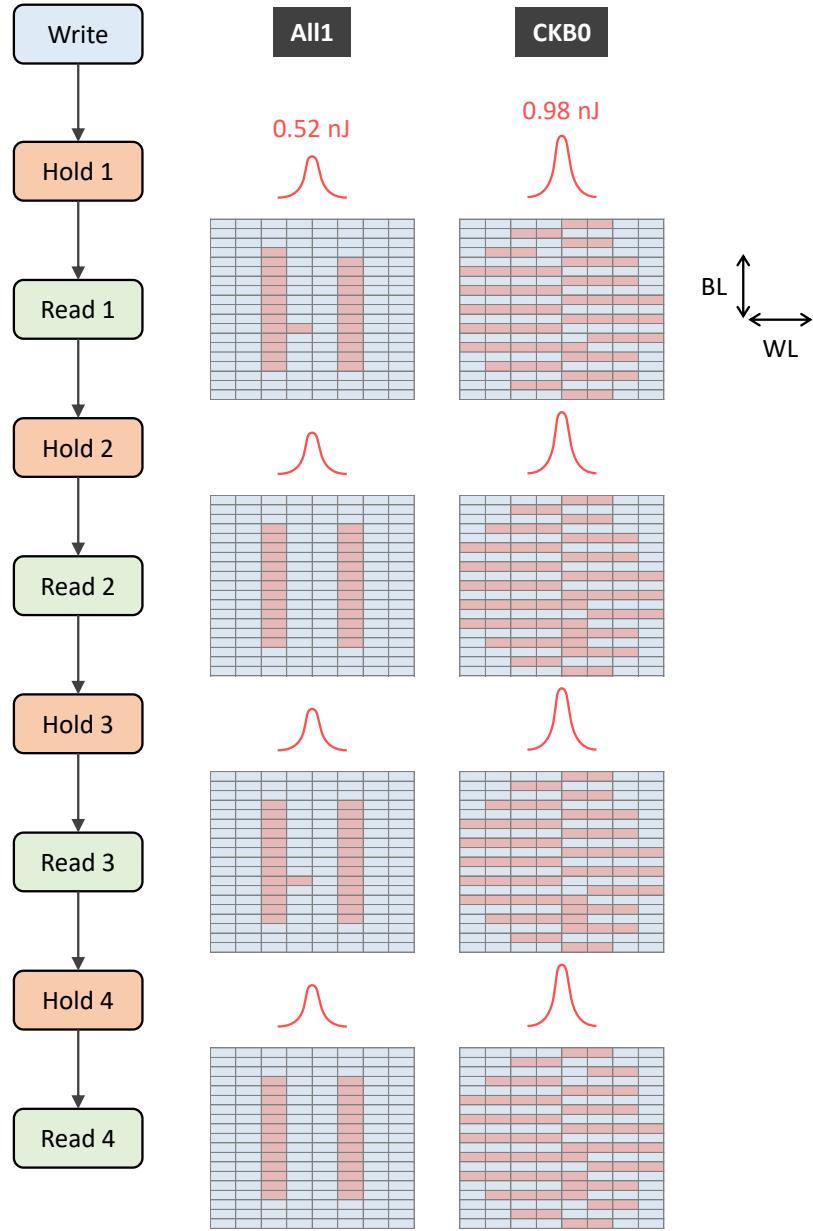

| 2.11 | FBMs in multiple-pulse laser irradiation for All1 and CKB0 patterns. . . . .                                                                                                   | 48 |

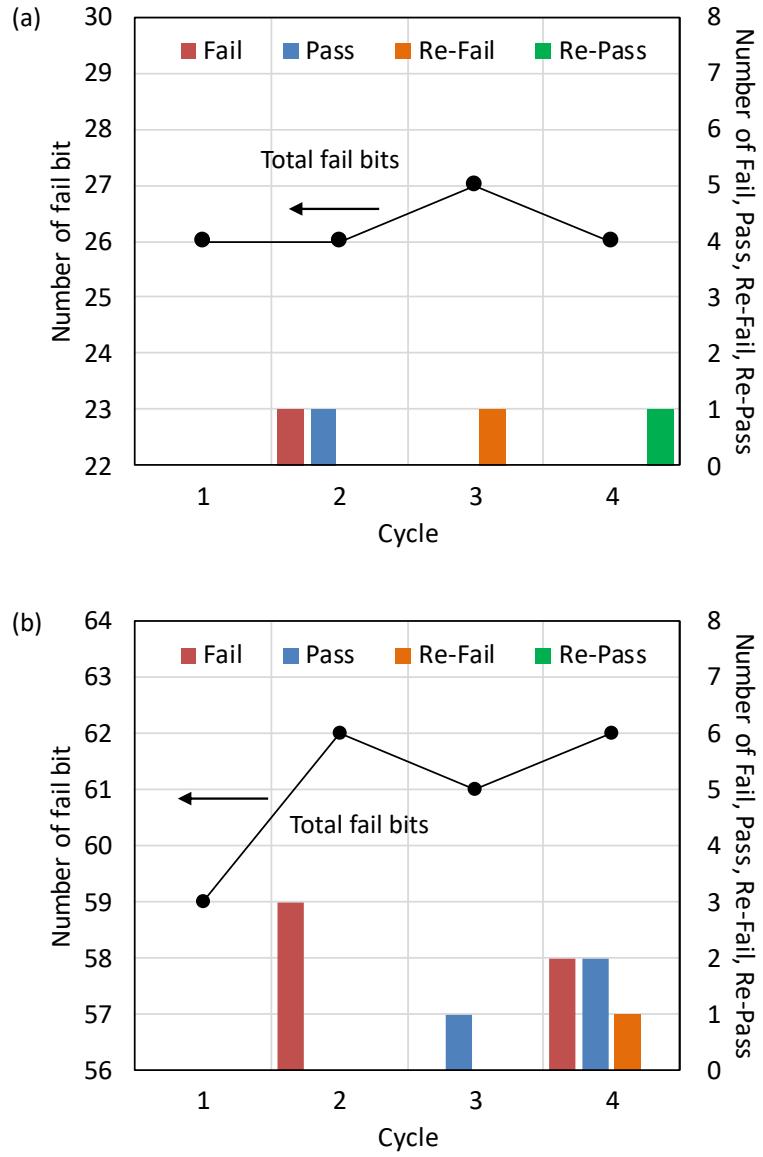

| 2.12 | Numbers of total fail bits and bit state transition as a function of test cycle in multiple-pulse laser irradiation. . . . .                                                   | 49 |

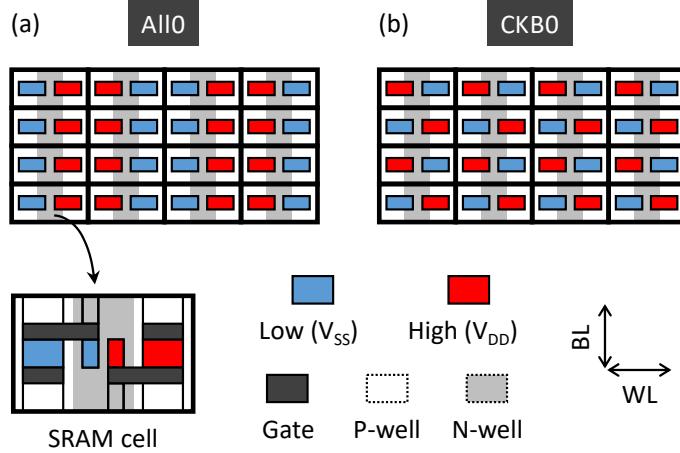

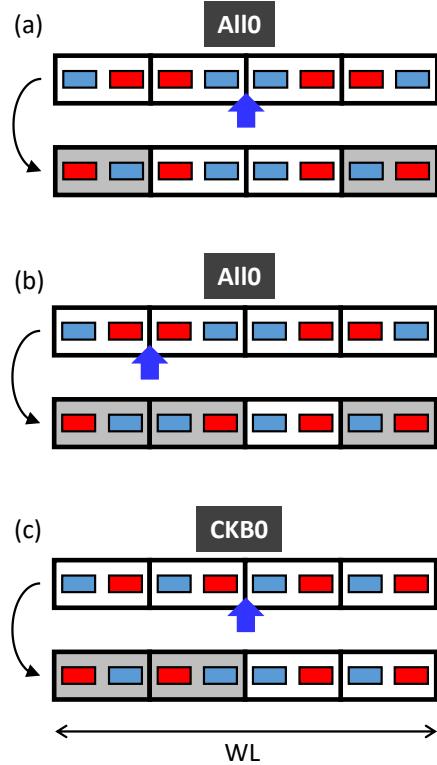

| 3.1  | SRAM node voltages for All0 and CKB0 patterns. . . . .                                                                                                                         | 54 |

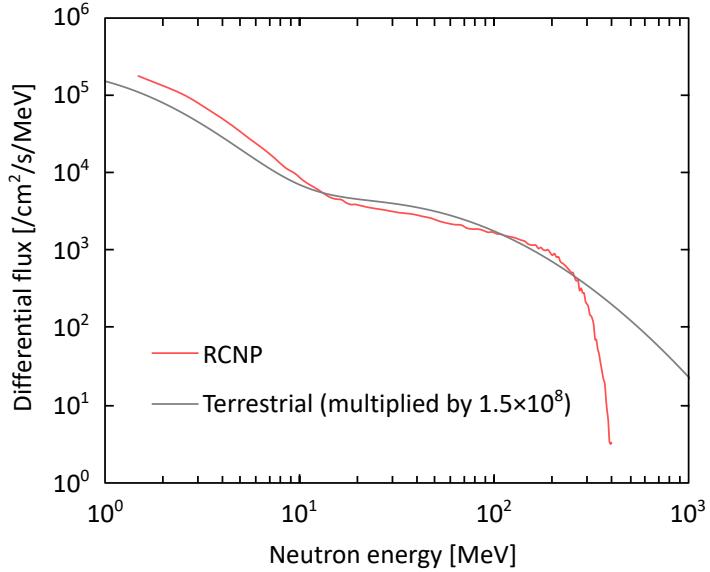

| 3.2  | Neutron energy spectrum of spallation neutron beam at the WN course, RCNP and terrestrial neutron at sea level, New York City. . . . .                                         | 55 |

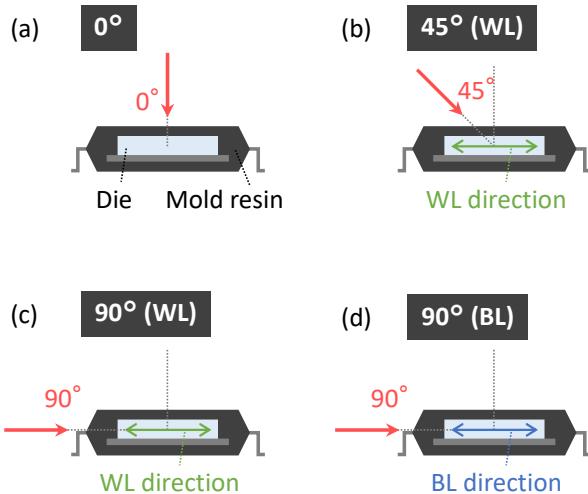

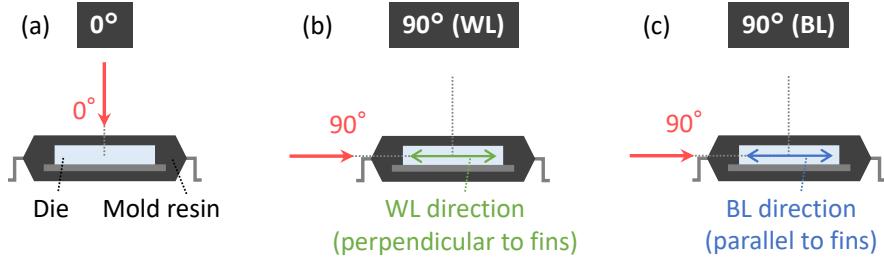

| 3.3  | Four incidence angles of high-energy neutron irradiation: $0^\circ$ , $45^\circ$ (WL), $90^\circ$ (WL), and $90^\circ$ (BL) . . . . .                                          | 55 |

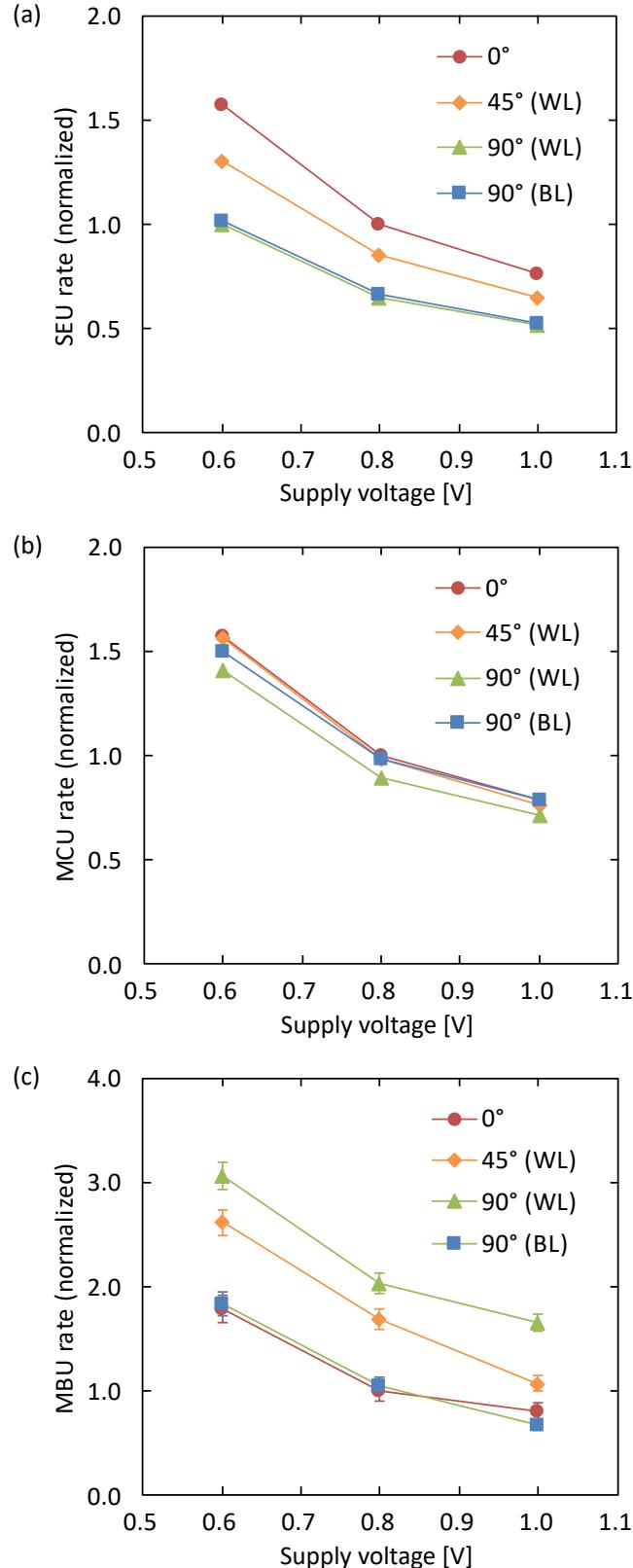

| 3.4  | SEU, MCU, and MBU rates as a function of supply voltage for the neutron incidence angles of $0^\circ$ , $45^\circ$ (WL), $90^\circ$ (WL) and $90^\circ$ (BL). . . . .          | 58 |

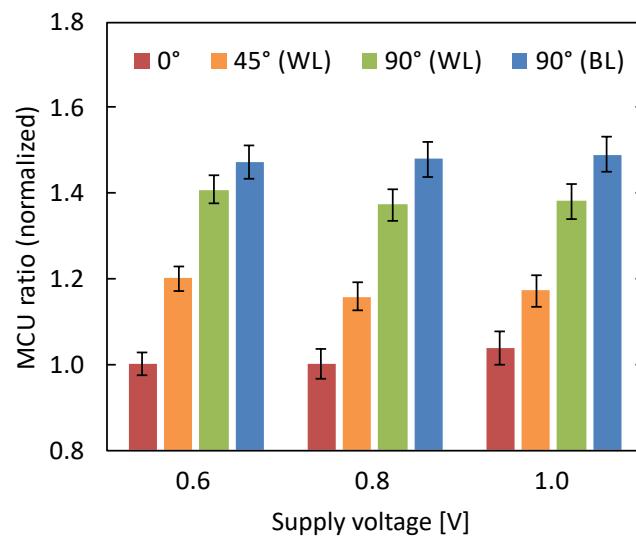

| 3.5  | MCU ratio as a function of supply voltage for the neutron incidence angles of $0^\circ$ , $45^\circ$ (WL), $90^\circ$ (WL) and $90^\circ$ (BL). . . . .                        | 59 |

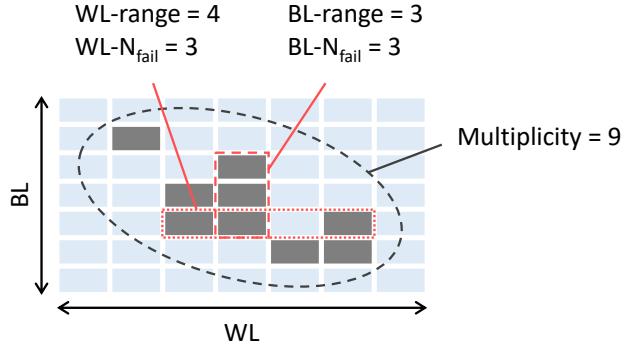

| 3.6  | Example for the characterization of an MCU event. . . . .                                                                                                                      | 60 |

| 3.7  | Multiplicity distributions of high-energy neutron-induced MCU events. . . . .                                                                                                  | 61 |

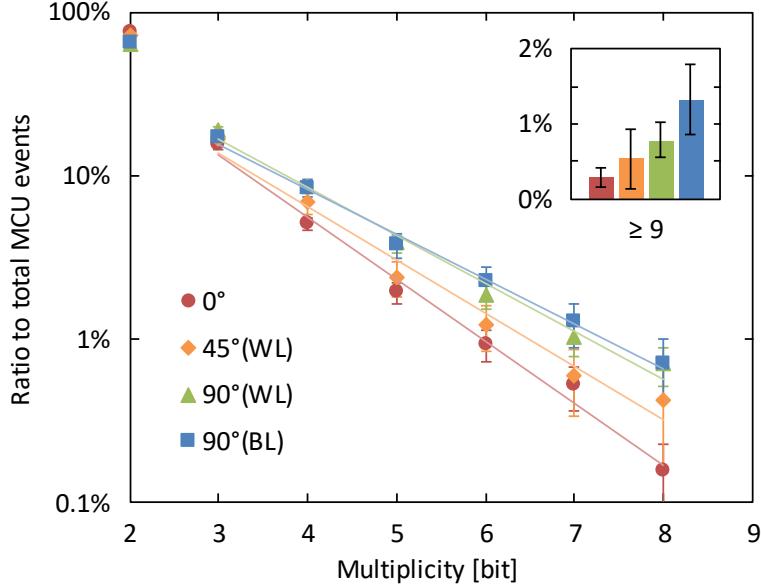

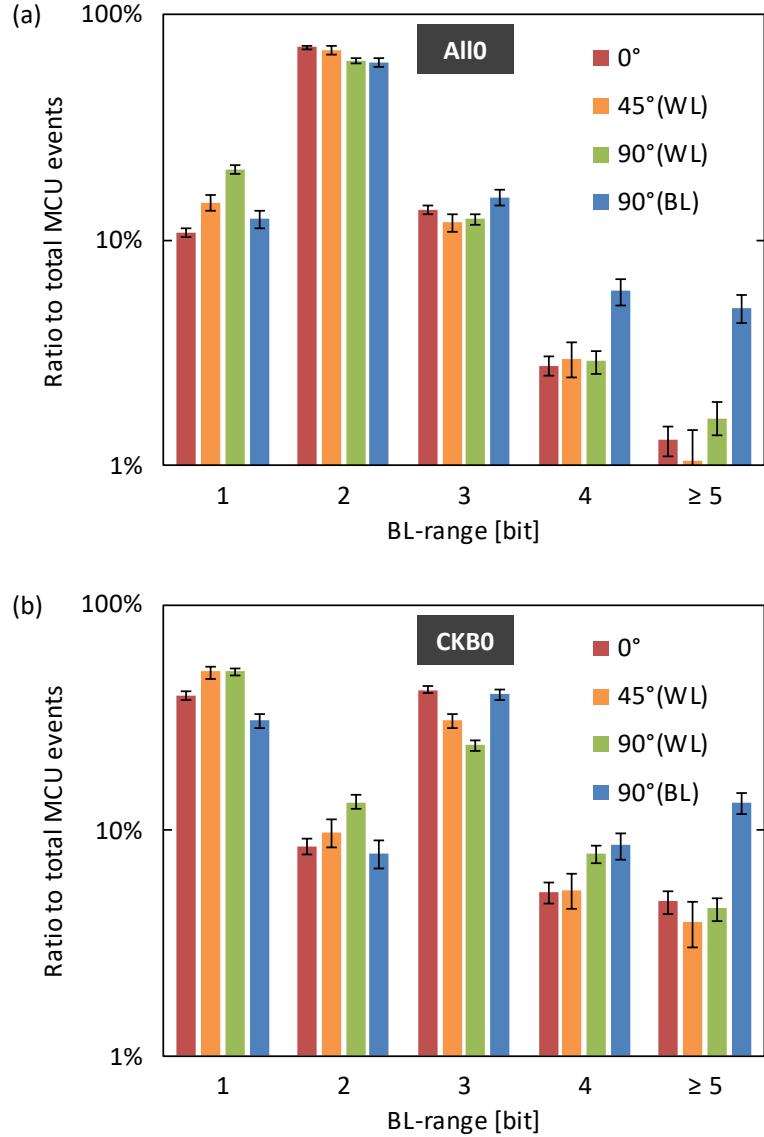

| 3.8  | BL-range distributions of high-energy neutron-induced MCU events for All0 and CKB0 patterns. . . . .                                                                           | 62 |

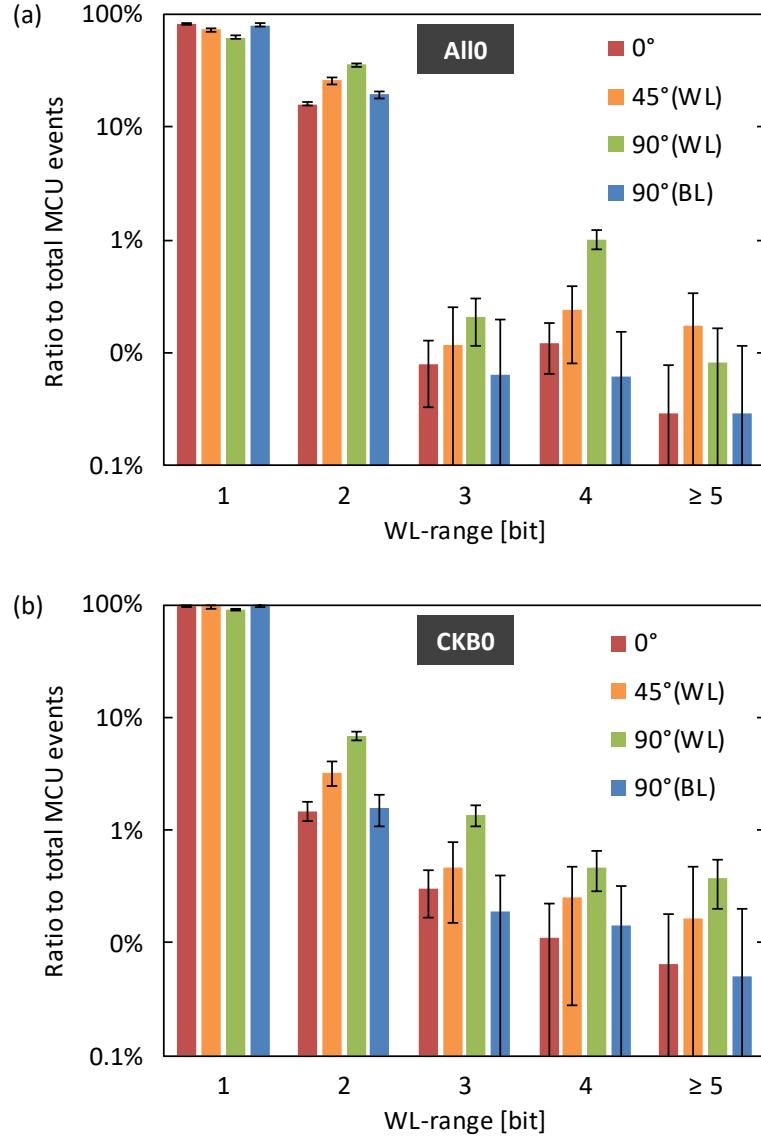

| 3.9  | WL-range distributions of high-energy neutron-induced MCU events for All0 and CKB0 patterns. . . . .                                                                           | 63 |

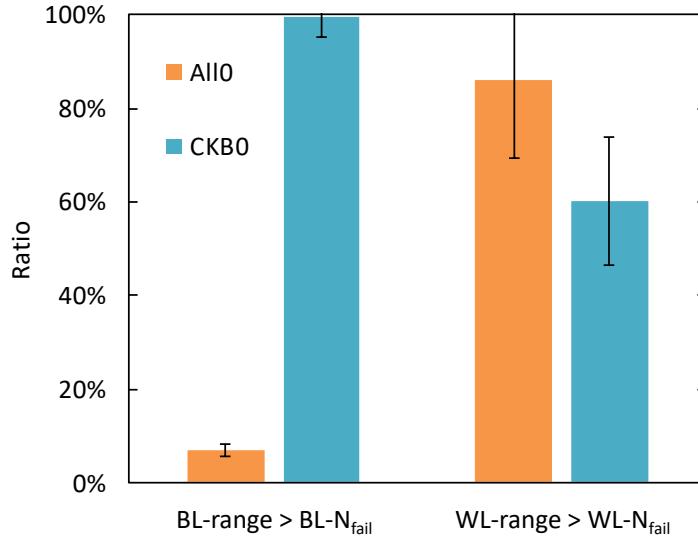

| 3.10 | Ratios of events where $BL(WL)$ -range $> BL(WL)$ - $N_{fail}$ at the incidence angle of $90^\circ$ (WL). . . . .                                                              | 65 |

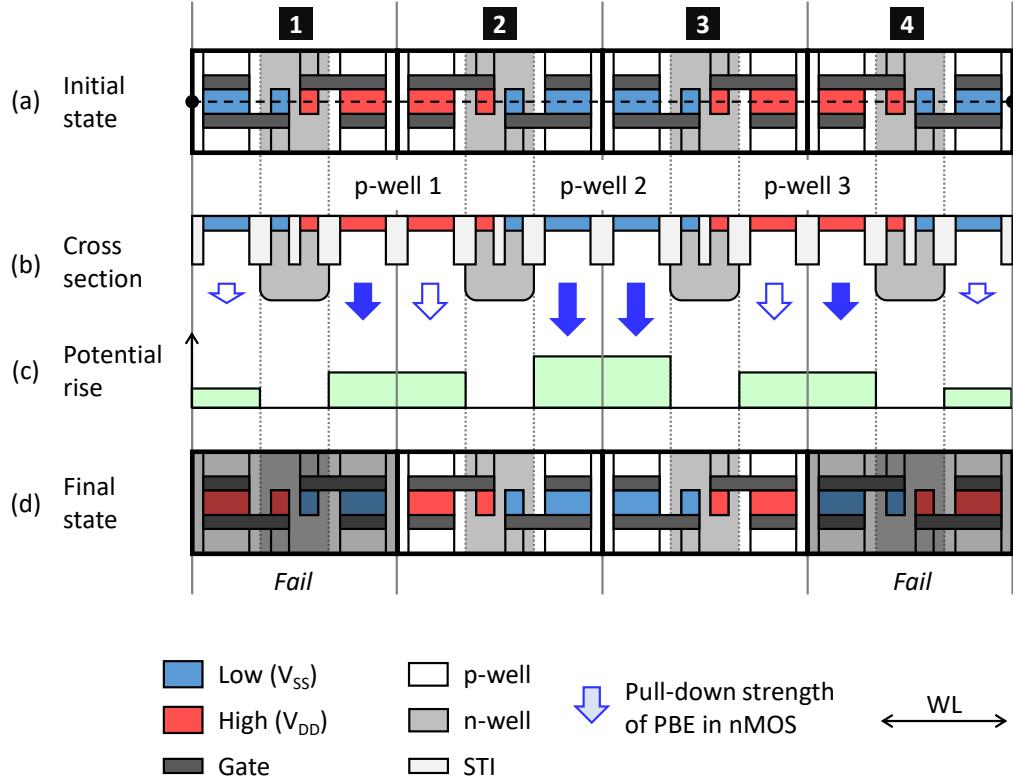

| 3.11 | Conceptual illustration of gap formation in a fail bit pattern through the MWCPU mechanism in the case of the All0 pattern. . . . .                                            | 66 |

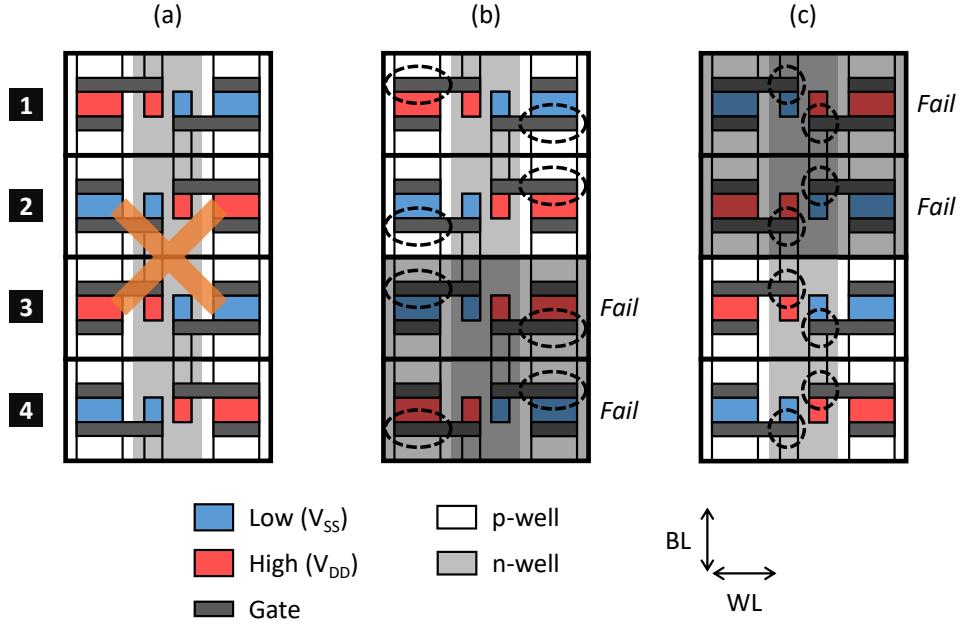

| 3.12 | Fail bit patterns induced by the MWCPU mechanism. . . . .                                                                                                                      | 67 |

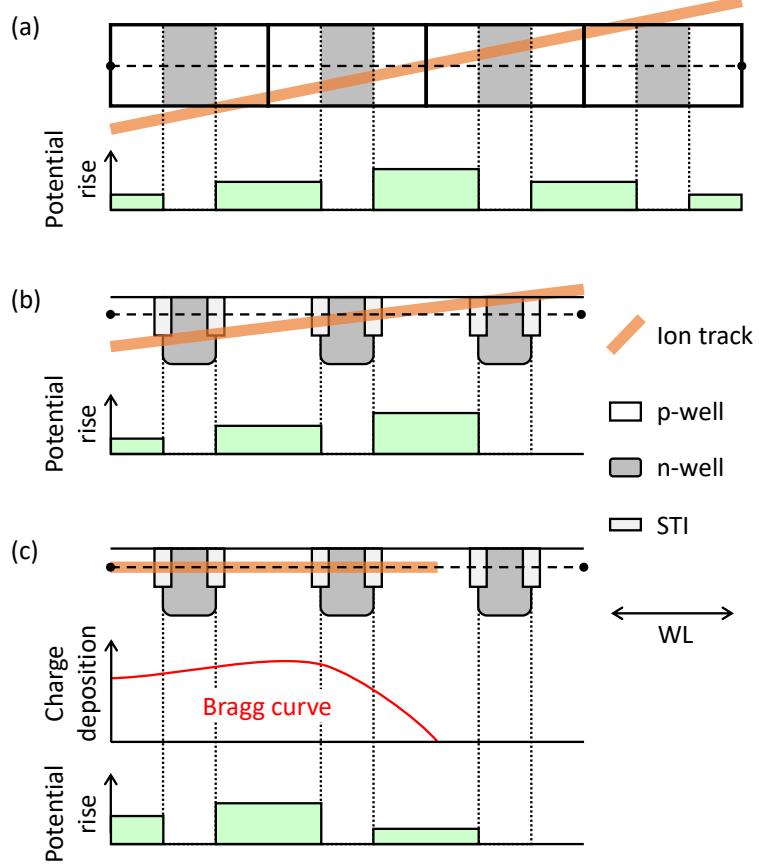

| 3.13 | Ion strike events triggering potential perturbation in multiple p-wells. . . . .                                                                                               | 69 |

|      |                                                                                                                                                                            |     |

|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.14 | Experimental FBM <sub>s</sub> of neutron-induced MCU events at the incidence angles of 45° (WL) and 90° (WL) in the case of the All0 pattern. . . . .                      | 70  |

| 4.1  | Neutron incidence angles of three irradiation conditions. . . . .                                                                                                          | 76  |

| 4.2  | Fin direction in SRAM cells. . . . .                                                                                                                                       | 76  |

| 4.3  | SEU, MCU, MBU rates as a function of supply voltage at the neutron incidence of 0°, 90° (WL), and 90° (BL). . . . .                                                        | 80  |

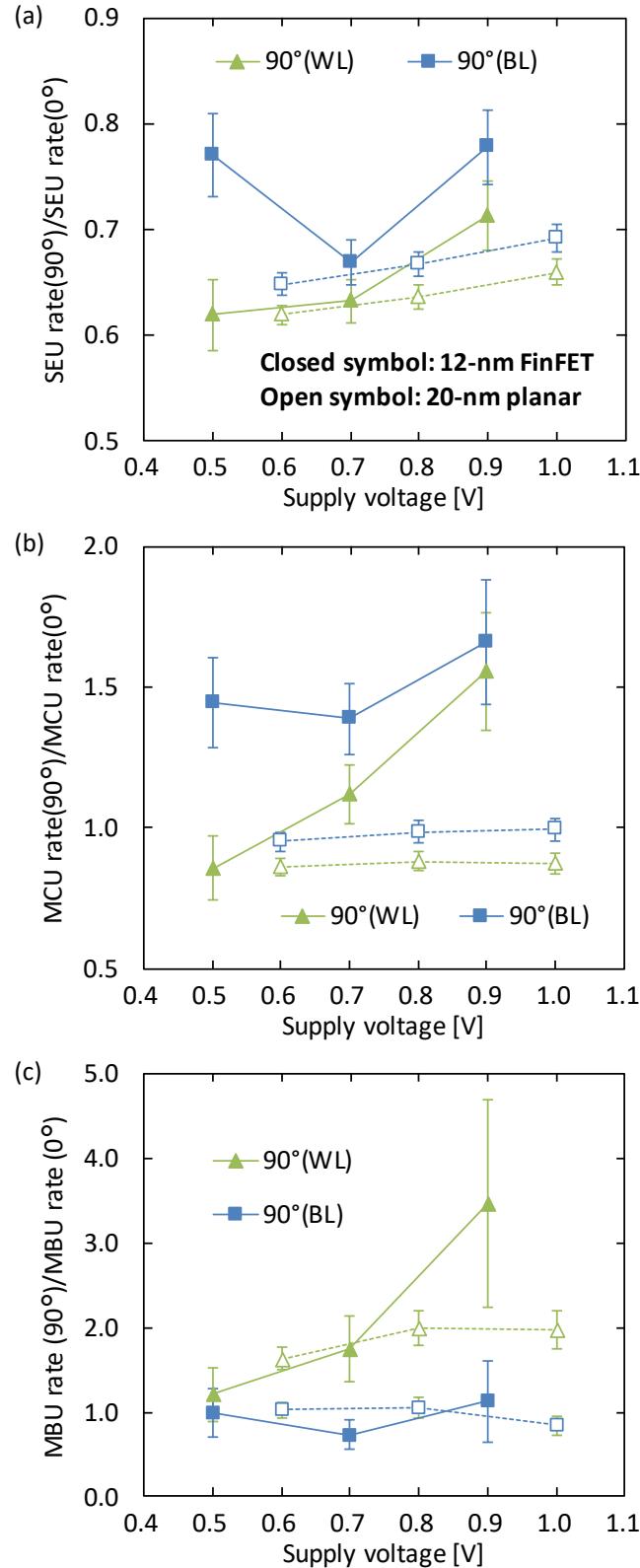

| 4.4  | Ratios of SEU, MCU, and MBU rates at the incidence angles of 90° (WL) and 90° (BL) with respect to the normal incidence case (0°) as a function of supply voltage. . . . . | 81  |

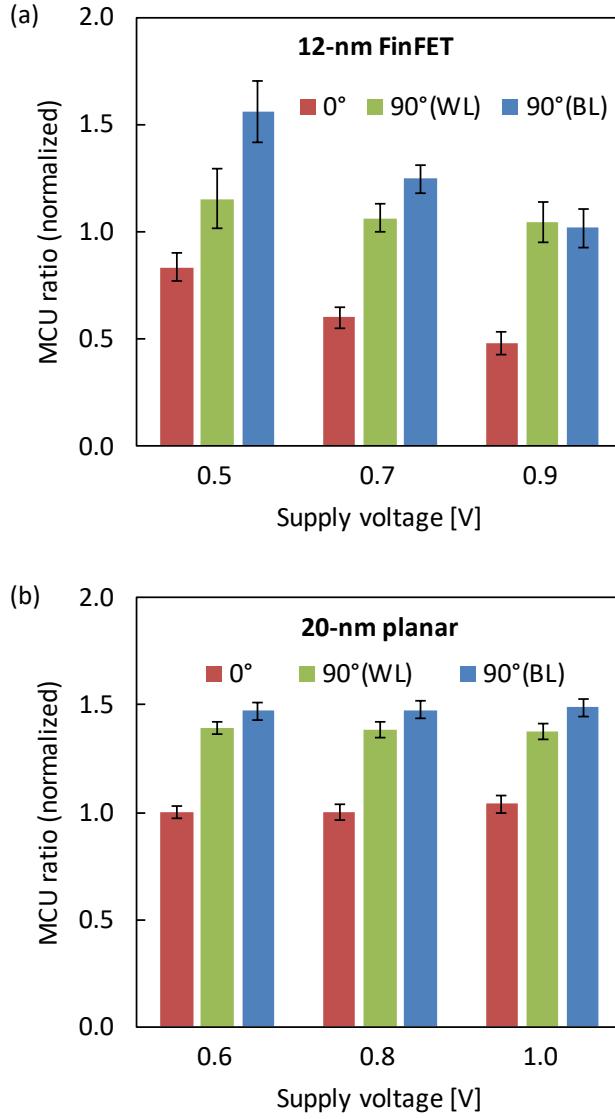

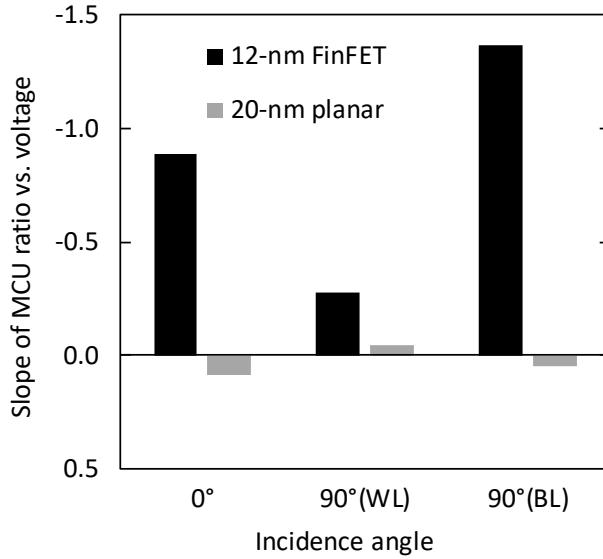

| 4.5  | MCU ratios for 12-nm FinFET and 20-nm planar SRAMs at the neutron incidence angles of 0°, 90° (WL), and 90° (BL). . . . .                                                  | 82  |

| 4.6  | Slope of the linear fitting of MCU ratio versus supply voltage. . . . .                                                                                                    | 83  |

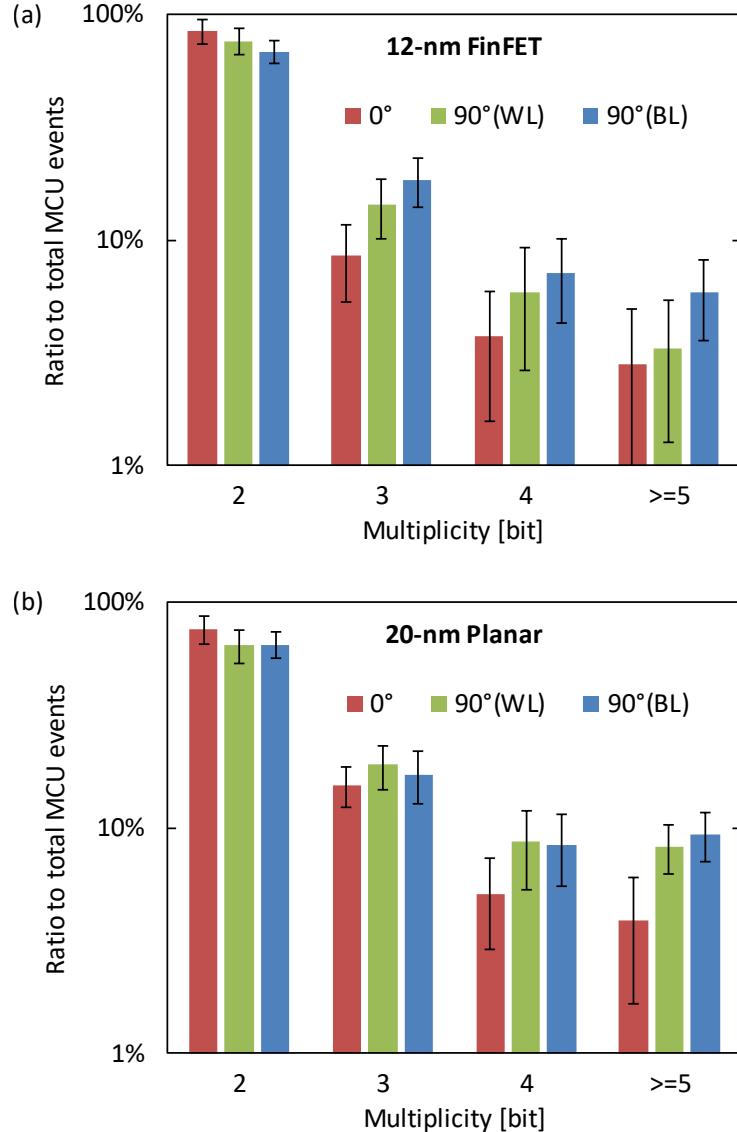

| 4.7  | Multiplicity distributions of neutron-induced MCU events for 12-nm FinFET and 20-nm planar SRAMs. . . . .                                                                  | 86  |

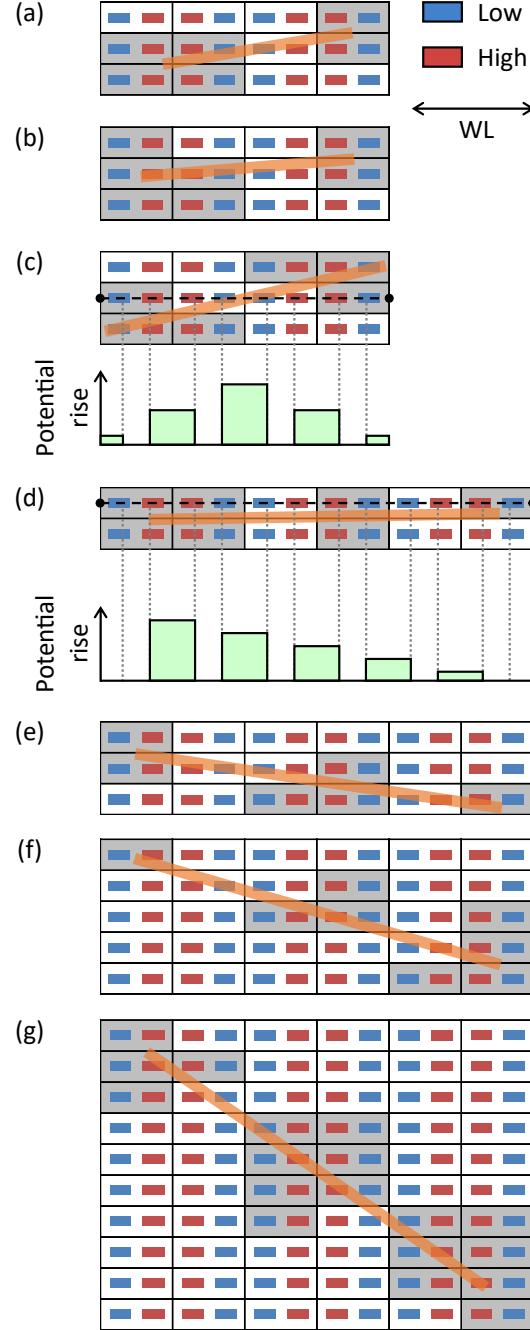

| 4.8  | Groups of fail bit patterns. . . . .                                                                                                                                       | 87  |

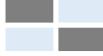

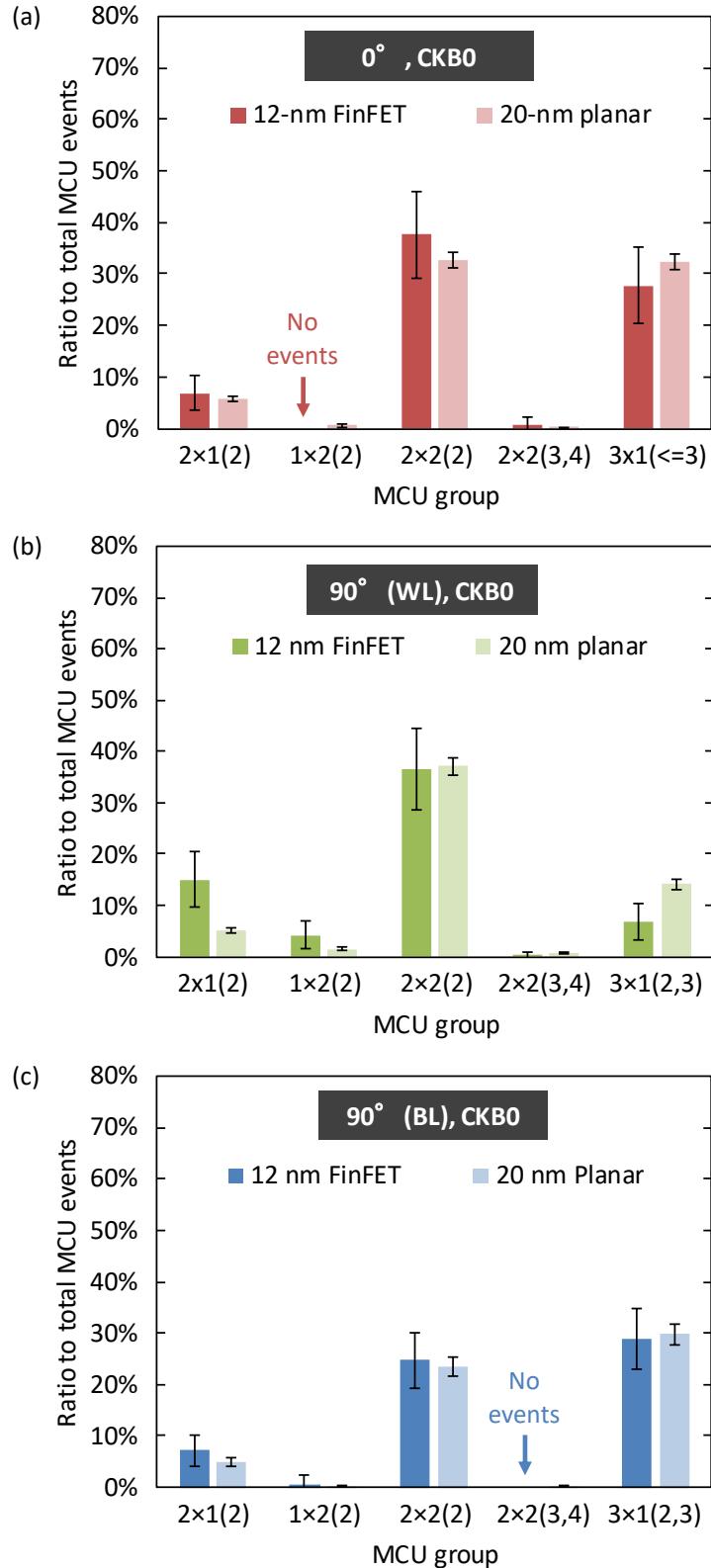

| 4.9  | Ratios for MCU groups in the case of the All0 pattern. . . . .                                                                                                             | 88  |

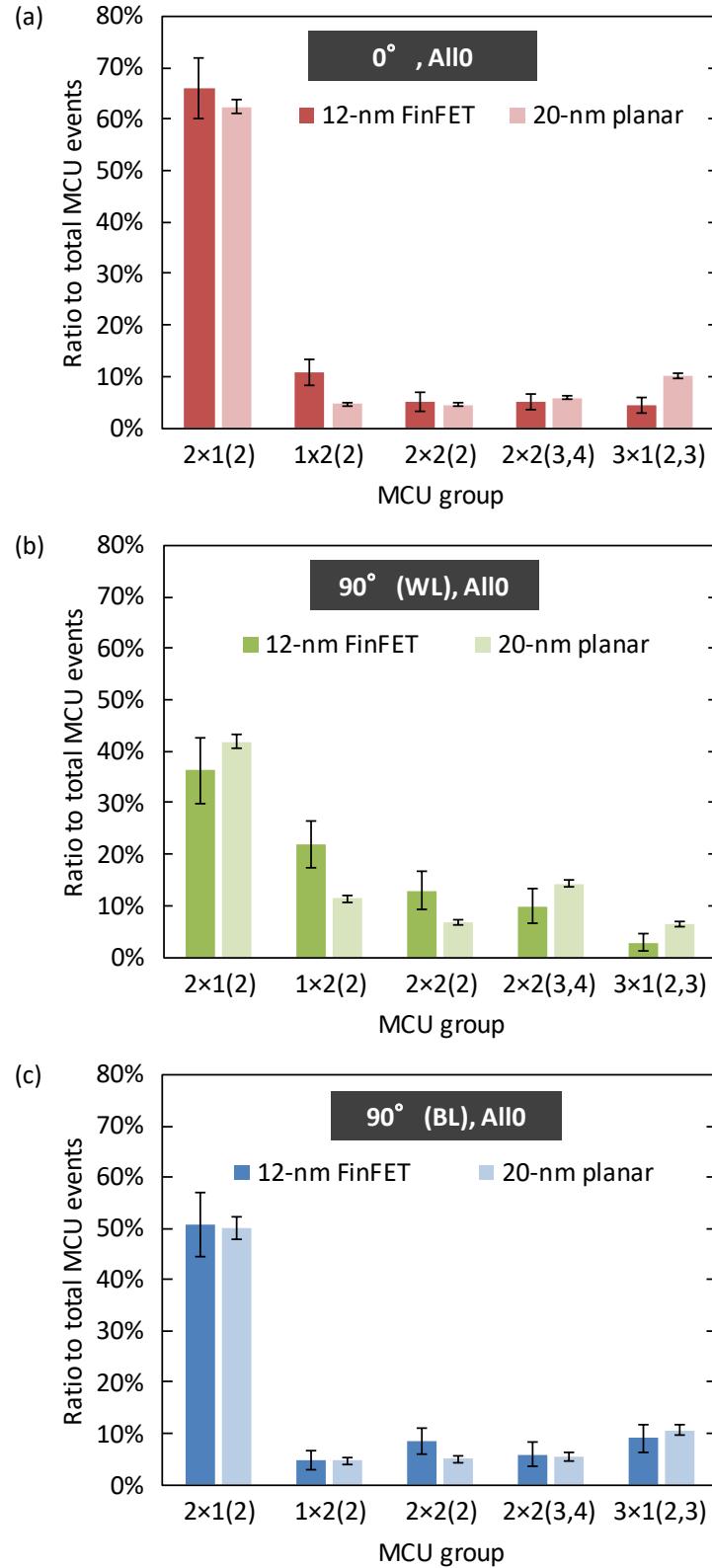

| 4.10 | Ratios for MCU groups in the case of the CKB0 pattern. . . . .                                                                                                             | 89  |

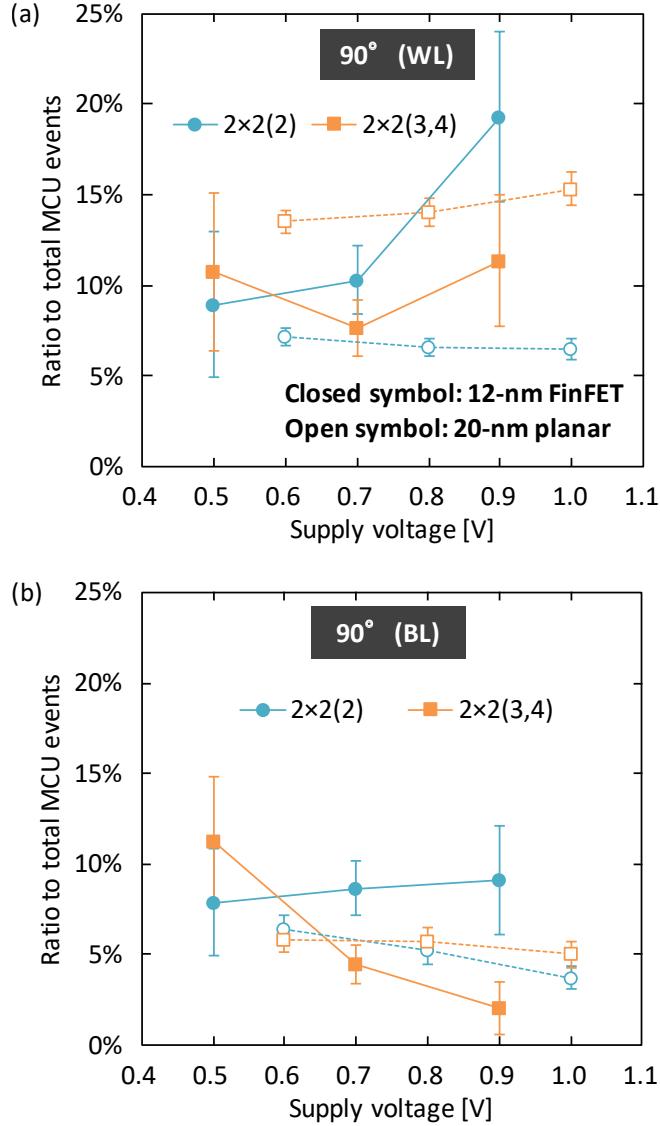

| 4.11 | Ratios of MCU events with 2 × 2 fail bit patterns as a function of supply voltage in the case of the All0 pattern. . . . .                                                 | 91  |

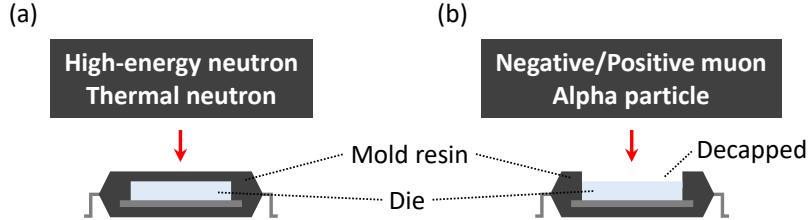

| 5.1  | Irradiation configurations for high-energy and thermal neutrons, negative and positive muons, and alpha particles. . . . .                                                 | 95  |

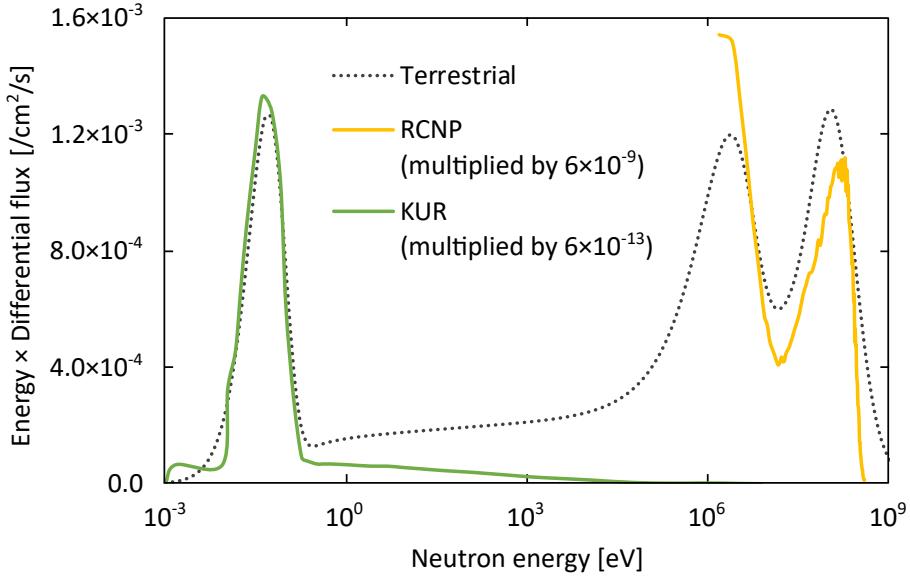

| 5.2  | Energy spectra of the terrestrial neutron, the spallation neutron beam at RCNP, and the thermal neutron beam at KUR. . . . .                                               | 97  |

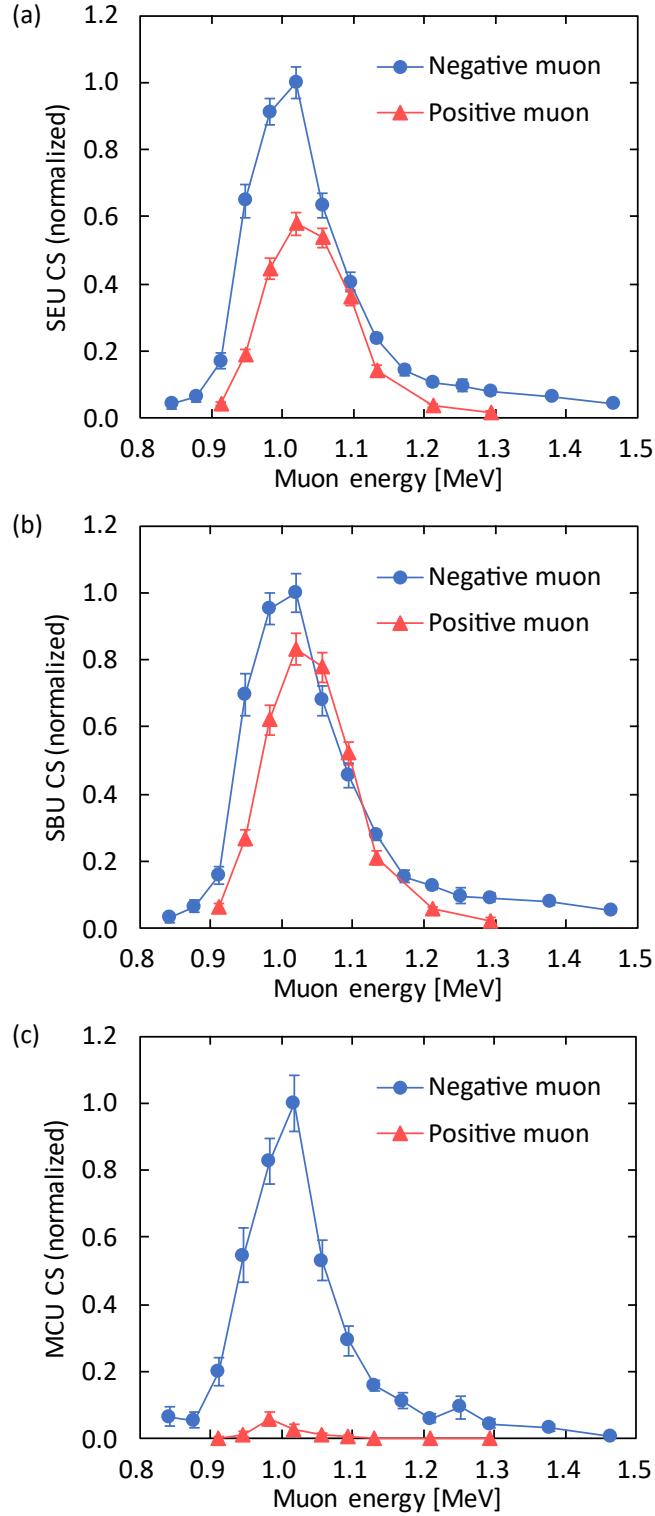

| 5.3  | SEU, SBU, and MCU CS <sub>s</sub> for negative and positive muons as a function of muon energy. . . . .                                                                    | 99  |

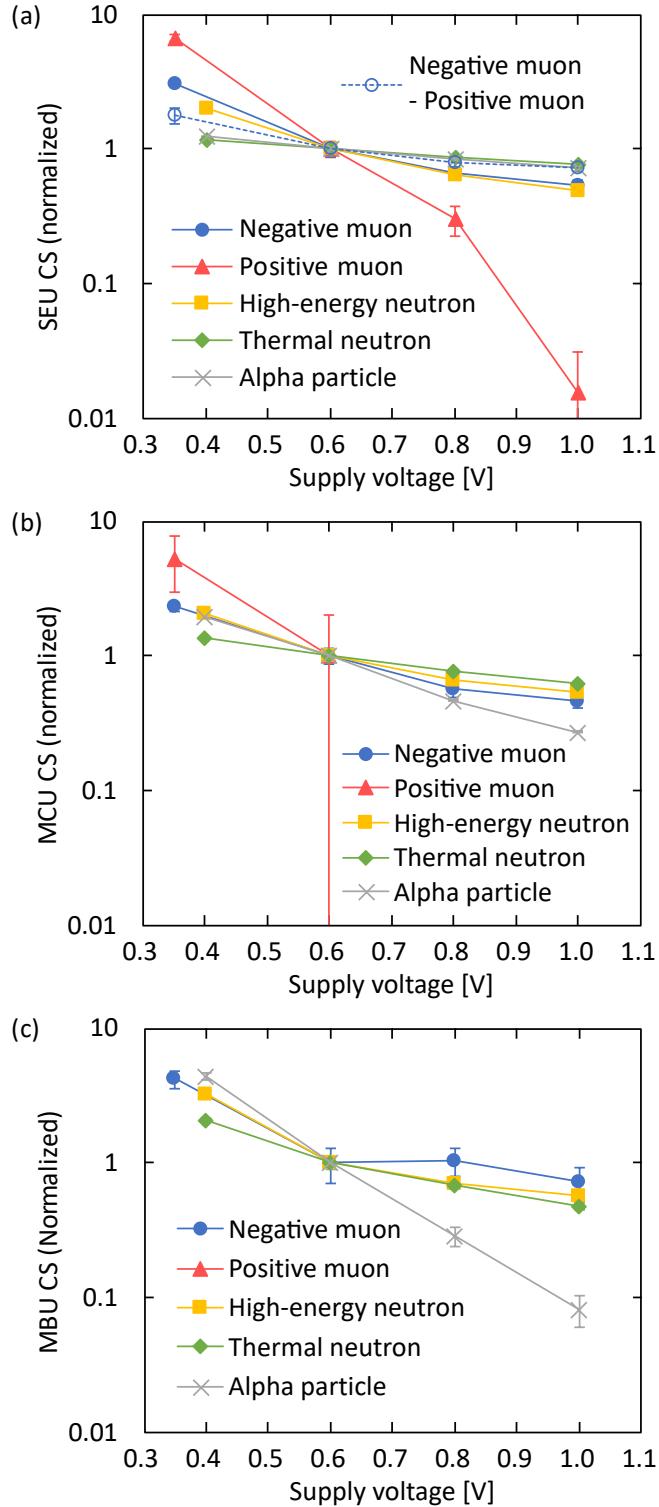

| 5.4  | SEU, MCU, and MBU CS <sub>s</sub> for negative muons, positive muons, high-energy neutrons, thermal neutrons, and alpha particles as a function of supply voltage. . . . . | 103 |

| 5.5  | MCU ratio for negative muons, positive muons, high-energy neutrons, thermal neutrons, and alpha particles as a function of supply voltage. . . . .                         | 104 |

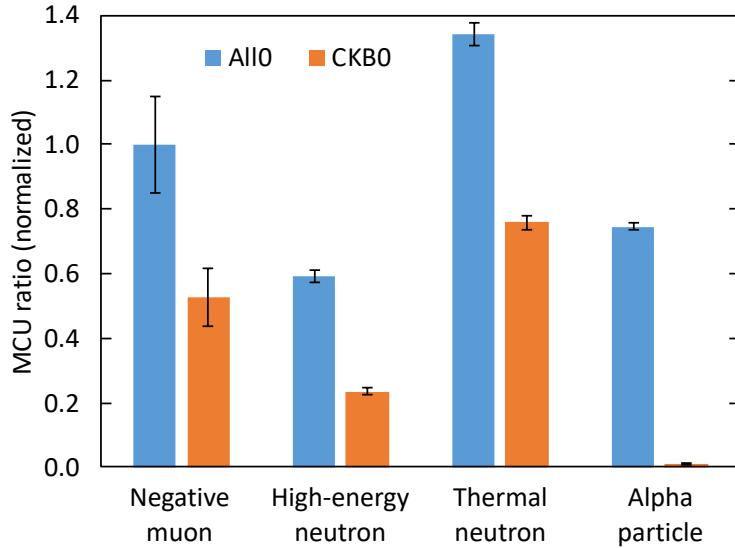

| 5.6  | Data pattern dependence of MCU ratio at 0.6 V. . . . .                                                                                                                     | 105 |

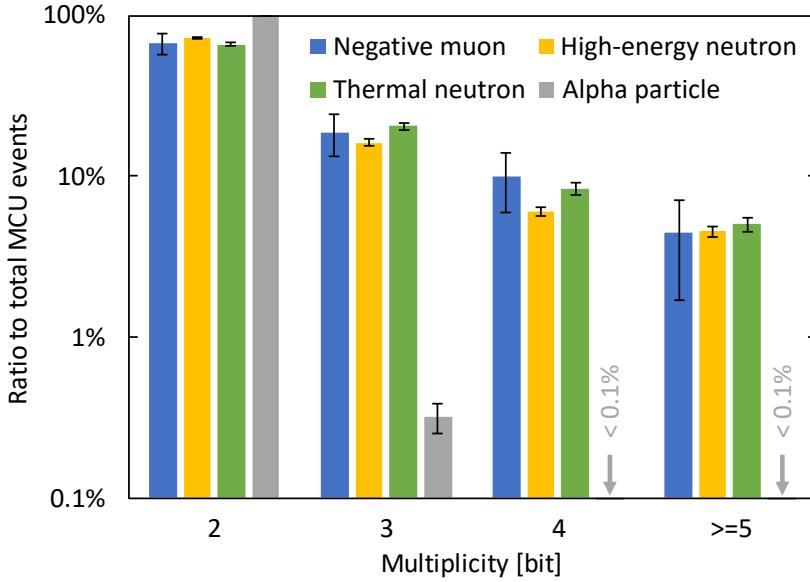

| 5.7  | Multiplicity distribution of MCU events. . . . .                                                                                                                           | 107 |

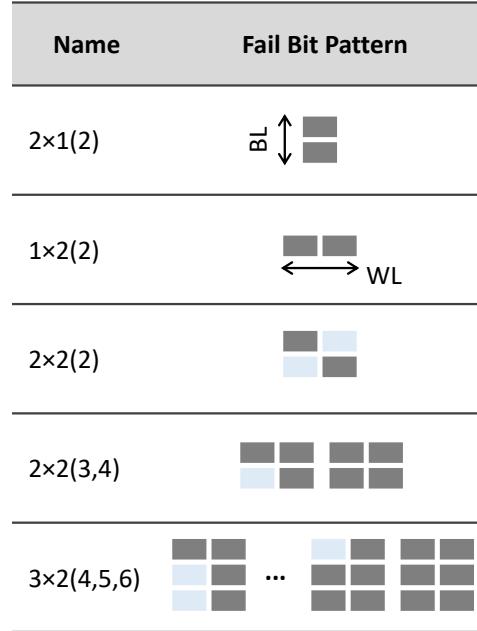

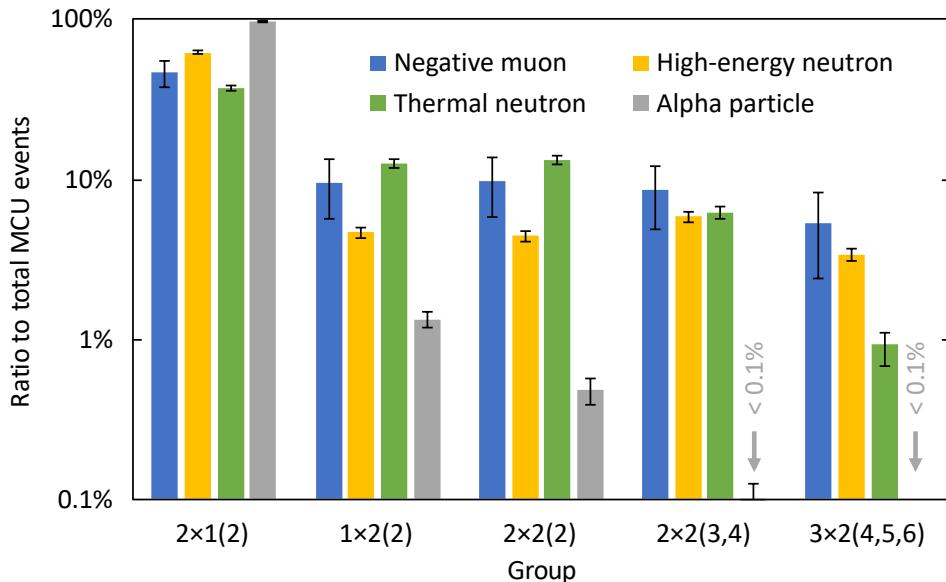

| 5.8  | Groups of fail bit patterns. . . . .                                                                                                                                       | 108 |

| 5.9  | Ratios for MCU groups. . . . .                                                                                                                                             | 108 |

# List of Tables

|     |                                                                                                  |     |

|-----|--------------------------------------------------------------------------------------------------|-----|

| 1.1 | Integral fluxes above 1 MeV for neutron, muon, and proton at sea level, New York City. . . . .   | 4   |

| 1.2 | Alpha particle emissivities for device materials. . . . .                                        | 4   |

| 1.3 | Energy of alpha particles emitted from radioisotopes in the decay chain of thorium [33]. . . . . | 12  |

| 2.1 | Category of bit state transition. . . . .                                                        | 47  |

| 5.1 | Incident Particles and Irradiation Facilities. . . . .                                           | 96  |

| 6.1 | Contributions of This Thesis. . . . .                                                            | 113 |

# List of Abbreviations

|                 |                                                                     |

|-----------------|---------------------------------------------------------------------|

| <b>2D</b>       | Two-Dimensional                                                     |

| <b>3D</b>       | Three-Dimensional                                                   |

| <b>3DAP</b>     | 3D Atom Probe                                                       |

| <b>ATE</b>      | Automated Test Equipment                                            |

| <b>BL</b>       | Bit Line                                                            |

| <b>BPSG</b>     | BoroPhosphoSilicate Glass                                           |

| <b>BTI</b>      | Bias Temperature Instability                                        |

| <b>CMOS</b>     | Complementary Metal-Oxide-Semiconductor                             |

| <b>CMP</b>      | Chemical-Mechanical Polishing                                       |

| <b>CS</b>       | Cross Section                                                       |

| <b>DRAM</b>     | Dynamic Random Access Memory                                        |

| <b>DUT</b>      | Dvice Under Test                                                    |

| <b>ECC</b>      | Error Correction Code                                               |

| <b>EXPACS</b>   | EXcel-based Program for calculating Atmospheric Cosmic-ray Spectrum |

| <b>FBM</b>      | Fail Bit Map                                                        |

| <b>FET</b>      | Field Effect Transistor                                             |

| <b>FF</b>       | Flip-Flop                                                           |

| <b>FinFET</b>   | Fin-shaped Field-Effect Transistor                                  |

| <b>FIT</b>      | Failure In Time                                                     |

| <b>FPGA</b>     | Field-Programmable Gate Array                                       |

| <b>HCI</b>      | Hot Carrier Injection                                               |

| <b>HWNIF</b>    | Heavy Water Neutron Irradiation Facility                            |

| <b>HyENEXSS</b> | Hyper ENvironment for EXploration of Semiconductor Simulation       |

| <b>IoT</b>      | Internet of Things                                                  |

| <b>IR</b>       | InfraRed                                                            |

| <b>JANIS</b>    | JAva-based Nuclear Information Software                             |

| <b>JENDL</b>    | Japanese Evaluated Nuclear Data Library                             |

| <b>J-PARC</b>   | Japan Proton Accelerator Research Complex                           |

| <b>KUR</b>      | Kyoto University Research Reactor                                   |

| <b>LA</b>       | Low Alpha                                                           |

| <b>LET</b>      | Linear Energy Transfer                                              |

| <b>MBU</b>      | Multiple-Bit Upset                                                  |

| <b>MCBI</b>     | Multi-Coupled Bipolar Interaction                                   |

| <b>MCU</b>      | Multiple-Cell Upset                                                 |

|                |                                                                           |

|----------------|---------------------------------------------------------------------------|

| <b>MOS</b>     | Metal-Oxide-Semiconductor                                                 |

| <b>MTBF</b>    | Mean Time Between Failure                                                 |

| <b>MUSE</b>    | MUon Science Establishment                                                |

| <b>MWCPU</b>   | Multi-Well Coupled Potential Unbalancing                                  |

| <b>NA</b>      | Numeric Aperture                                                          |

| <b>nMOS</b>    | n-type MOS                                                                |

| <b>PBE</b>     | Parasitic Bipolar Effect                                                  |

| <b>PE</b>      | Pulse Energy                                                              |

| <b>PHITS</b>   | Particle and Heavy Ion Transport code System                              |

| <b>PHYSERD</b> | PHITS-HYENEXSS integrated code System for Effects of Radiation on Devices |

| <b>pMOS</b>    | p-type MOS                                                                |

| <b>PW</b>      | Pulse Width                                                               |

| <b>RCNP</b>    | Research Center for Nuclear Physics                                       |

| <b>SBU</b>     | Single Bit Upset                                                          |

| <b>SEB</b>     | Single-Event Burnout                                                      |

| <b>SECDED</b>  | Single-bit Error Correction Double-bit Error Detection                    |

| <b>SEE</b>     | Single-Event Effect                                                       |

| <b>SEFI</b>    | Single-Event Functional Interrupt                                         |

| <b>SEGR</b>    | Single-Event Gate Rupture                                                 |

| <b>SEL</b>     | Single-Event Latchup                                                      |

| <b>SER</b>     | Soft Error Rate                                                           |

| <b>SEU</b>     | Single-Event Upset                                                        |

| <b>SoC</b>     | System-on-a-Chip                                                          |

| <b>SRAM</b>    | Static Random Access Memory                                               |

| <b>SRIM</b>    | Stopping and Range of Ions in Matter                                      |

| <b>SULA</b>    | Super Ultra-Low Alpha                                                     |

| <b>TDDB</b>    | Time-Dependent Dielectric Breakdown                                       |

| <b>TPA</b>     | Two-Photon Absorption                                                     |

| <b>ULA</b>     | Ultra-Low Alpha                                                           |

| <b>WCSI</b>    | Well-Collapse Source-Injection                                            |

| <b>WL</b>      | Word Line                                                                 |

## Chapter 1

# Introduction

### 1.1 Soft Errors in Semiconductor Devices

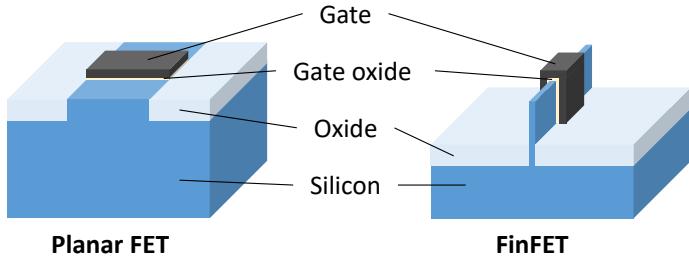

Today, electronic systems are highly dependent on semiconductor devices, such as microcontrollers and system-on-a-chips (SoCs), not only for their performance, but also for their dependability. The semiconductor devices have been evolved to meet the growing demand for more sophisticated systems, such as telecommunication infrastructures and Internet of Things (IoT) platforms. The key factor of this evolution has been the scaling of transistors, but, the scaling is approaching its physical limitation for planar field effect transistors (FETs). To overcome this limitation, three-dimensional (3D) structures have been adopted for the transistors in recent years. In advanced complementary metal-oxide-semiconductor (CMOS) technologies, fin-shaped field-effect transistors (FinFETs) are the most common 3D transistors. As illustrated in Fig. 1.1, the triple gate structure of the FinFETs suppresses short channel effects and provides better electrical characteristics compared to the planar FETs. Meanwhile, the reliability assurance of the semiconductor devices is becoming more challenging with the scaling and geometry change of the transistors. It is therefore essential to address reliability problems in the advanced semiconductor devices to ensure the dependability of current and future electronic systems.

Soft errors induced by radiation are one of the major problems that threaten the reliability of the semiconductor devices. The soft errors are transient errors with no permanent damage on the devices, in contrast to hard errors, such as hot carrier injection (HCI), bias temperature instability (BTI), and time-dependent dielectric breakdown (TDDB). Thanks to this nondestructive nature, malfunctions caused by the soft errors can be recovered by power cycling or resetting of the devices, whereas that caused by the hard errors cannot. However, the soft errors significantly degrade the dependability of mission critical systems, where the power cycling and resetting are not always possible. An important point here is that the mission critical systems are becoming widespread and ubiquitous in contemporary society. One example for such systems is automated driving systems, in which failures in the system can result in serious accidents and hence transient errors in the semiconductor devices should be completely suppressed. Another example is networking systems, which are essential to provide internet services and require continuous operation without

FIGURE 1.1: Schematic structures of planar FET and FinFET.

any interruptions. Thus, the soft error problem can undermine the safety and well-being of the society.

In modern semiconductor devices, the soft errors are caused by terrestrial radiation, such as secondary cosmic-rays and alpha particles. Here, charge deposition induced by such ionizing radiation is the origin of the soft errors. Historically, the soft errors were considered as a problem in space applications, where the semiconductor devices are exposed to hazardous space radiation, such as primary cosmic rays and solar flares. The first report on the soft errors was satellite anomalies caused by unexpected triggering of flip-flops (FFs) in 1975 [1]. After that, in 1978, the soft errors in terrestrial applications were reported for the first time in dynamic random access memories (DRAMs), where the radiation source was alpha particles emitted from radioisotopes in package materials [2]. In 1993 and 1994, it was evidenced that the soft errors in static random access memories (SRAMs) and DRAMs are caused by atmospheric neutrons, which are a part of the secondary cosmic-rays [3], [4]. Since then, the soft errors have become one of the major challenges with increased integration of semiconductor devices used in terrestrial applications. As a result, considerable efforts have been devoted to understand and mitigate the terrestrial radiation-induced soft errors [5]–[9].

An important concern for the soft errors is an increased susceptibility to the terrestrial radiation in advanced semiconductor devices. This is due to the aggressive scaling of CMOS technologies in terms of physical size and supply voltage. The smaller size and lower voltage result in the decreased amount of charge necessary for representing logic states, “0” and “1”, in semiconductor circuits. This leads to the increased vulnerability to electric noises induced by ionizing radiation. In other words, for the scaled devices, unexpected alterations in the logic states are more likely to be caused by the terrestrial radiation. In addition to this scaling, as described above, the FinFETs have been introduced in advanced CMOS technologies. Since the geometry of the FinFETs is significantly different from that of the conventional planar FETs, the responses to the terrestrial radiation are expected to be different from each other. Therefore, it is necessary to investigate and understand the impact of the terrestrial radiation on the advanced planar and FinFET devices.

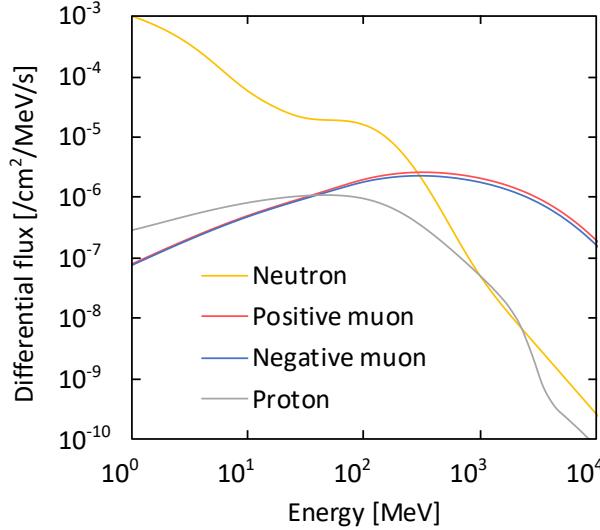

FIGURE 1.2: Energy spectra of neutrons, muons, and protons at sea level, New York City obtained from EXPACS [12].

## 1.2 Terrestrial Radiation

In the terrestrial environment, secondary cosmic-rays and alpha particles from natural radioisotopes are the main radiation sources of the soft errors [7]. The secondary cosmic-rays are constantly produced in the atmosphere by primary cosmic-rays. On the other hand, the natural radioisotopes are inherently present in the materials of the semiconductor devices. Basically, the soft errors caused by the radioisotopes can be reduced by employing materials with low radioisotope content, whereas that caused by the secondary cosmic-rays cannot be suppressed by changing the materials. Therefore, the secondary cosmic-rays are a primary concern for the terrestrial soft errors in recent semiconductor devices [10].

The secondary cosmic-rays originate from interactions between primary cosmic-rays and the Earth's atmosphere. The primary cosmic-rays are predominantly composed of protons ( $\sim 90\%$ ), the energy of which ranges from 10 MeV to  $10^{20}$  eV [11]. When this high-energy protons strike the atmosphere, some of the protons interact with atmospheric atoms, and cascades of various particles are invoked [10]. The particles produced through the cascades are the so-called secondary cosmic-rays. At sea level, the secondary cosmic-rays consist mainly of neutrons, protons, muons, electrons, and photons<sup>1</sup>. Among these particles, the electrons and the photons cannot cause the soft errors. The energy spectra and integral fluxes of the neutrons, the protons and the muons at sea level are shown in Fig. 1.2 and Table 1.1, respectively, where the data are based on Excel-based Program for calculating Atmospheric Cosmic-ray Spectrum (EXPACS) [12]. The muons are the most abundant particles at sea level. The next most abundant particles are the neutrons. At the present time, the neutrons are considered as a major contributor to the terrestrial soft errors [10].

<sup>1</sup>The particles reaching the ground are often called terrestrial cosmic-rays.

TABLE 1.1: Integral fluxes above 1 MeV for neutron, muon, and proton at sea level, New York City estimated from Fig. 1.2.

| Particle      | Flux [/cm <sup>2</sup> /h] |

|---------------|----------------------------|

| Neutron       | 21                         |

| Proton        | 1.3                        |

| Positive muon | 37                         |

| Negative muon | 31                         |

TABLE 1.2: Alpha particle emissivities of device materials [18].

| Material                    | Emissivity [/cm <sup>2</sup> /kh]      |

|-----------------------------|----------------------------------------|

| 30 $\mu$ m thick Cu metal   | < 0.3                                  |

| 20 $\mu$ m thick AlCu metal | < 0.3                                  |

| Mold compound               | < 24 – < 0.5                           |

| Flip chip underfill         | < 4 – < 0.7                            |

| Pb-based solders            | < 7.2 $\times$ 10 <sup>3</sup> – < 0.9 |

Importantly, on the other hand, there is an increasing concern that the muons can be a source of the soft errors in advanced semiconductor devices [13], [14].

The alpha particles originate from the decay of natural radioisotopes in the device materials, such as packages and metal layers. In most cases, the package materials, such as mold resin and solders, are the primary source. In these materials, radioisotopes are naturally present and emit the alpha particles. The emissivity of the alpha particles depends on the abundance of radioisotopes, and hence it varies depending on the materials [15]–[17]. The typical emissivities of the device materials are given in [18], and are presented in Table. 1.2. In the materials used in manufacturing processes, there are several classes with respect to the alpha particle emissivity: low alpha (LA), ultra-low alpha (ULA), and super ultra-low alpha (SULA). The emissivities for the LA, ULA, and SULA classes are generally 2 – 20 /cm<sup>2</sup>/kh, < 2 /cm<sup>2</sup>/kh, and < 1 /cm<sup>2</sup>/kh, respectively. Obviously, by replacing the device materials with, for example, the SULA materials, the soft errors induced by the alpha particles can be suppressed. However, the alpha particle-induced soft errors are still a concern because such replacement may not be allowed due to the increased cost of products.

As described above, the neutrons, the muons, and the alpha particles are major concerns for the terrestrial soft errors in advanced semiconductor devices. In the following subsections, basic characteristics of these particles are described to discuss their impacts on the soft errors in this thesis.

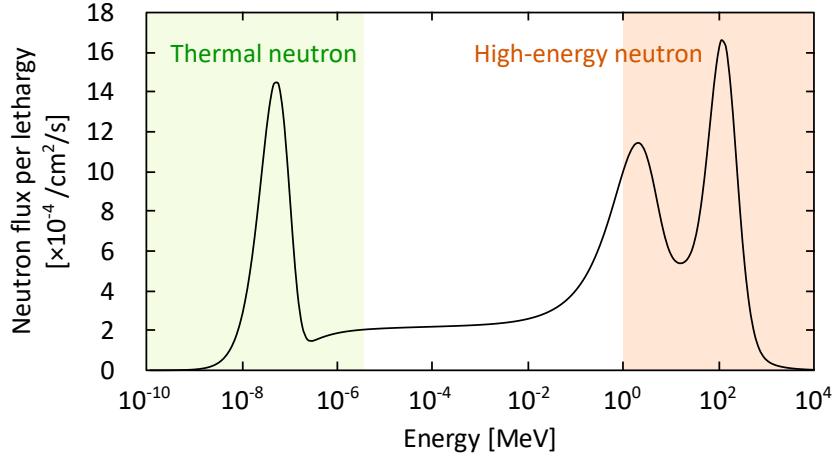

FIGURE 1.3: Energy spectrum of atmospheric neutrons at sea level, New York City obtained from EXPACS [12]. The vertical axis corresponds to (Energy)  $\times$  (Differential flux).

### 1.2.1 Neutrons

The energy spectrum of the terrestrial neutrons ranges from thermal energy to high-energy. In Fig. 1.2, only the high-energy region ( $> 1$  MeV) is shown. The full energy spectrum of the terrestrial neutrons is presented in Fig. 1.3. In addition to the high-energy region, the spectrum has a considerable portion around 0.025 eV, i.e., thermal energy. Generally, neutrons with energies around 0.025 eV and above 1 MeV are called thermal neutrons and high-energy neutrons, respectively. In this spectrum at New York City, the fluxes of the thermal and high-energy neutrons are  $10 / \text{cm}^2/\text{h}$  and  $21 / \text{cm}^2/\text{h}$ , respectively. Importantly, the neutron energy spectrum varies with altitude, geomagnetic location, solar activity, and surrounding materials, and hence the flux also varies. For example, the flux of the high-energy neutrons at Tokyo is  $12 / \text{cm}^2/\text{h}$ , which is smaller than that at New York City [12]. In the evaluation of the soft errors, the integral flux above 10 MeV at sea level, New York City is often used as the reference flux of the high-energy neutrons, where the value is  $13 / \text{cm}^2/\text{h}$  [18]. For the thermal neutrons, the commonly used reference flux is  $6.5 / \text{cm}^2/\text{h}$ , which corresponds to the integral flux below 0.4 eV at sea level, New York City [18].

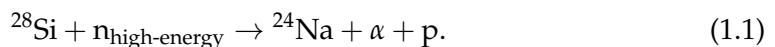

The high-energy neutrons induce the soft errors through interactions with the materials of the semiconductor devices. The neutrons do not directly deposit charge to the devices because they are electrically neutral particles. The charge deposition is induced by secondary ions produced through spallation reactions and recoil reactions in the semiconductor devices. For silicon-based devices, the most important ones are the reactions between the high-energy neutrons and Si atoms, in which various secondary ions are produced: for example,

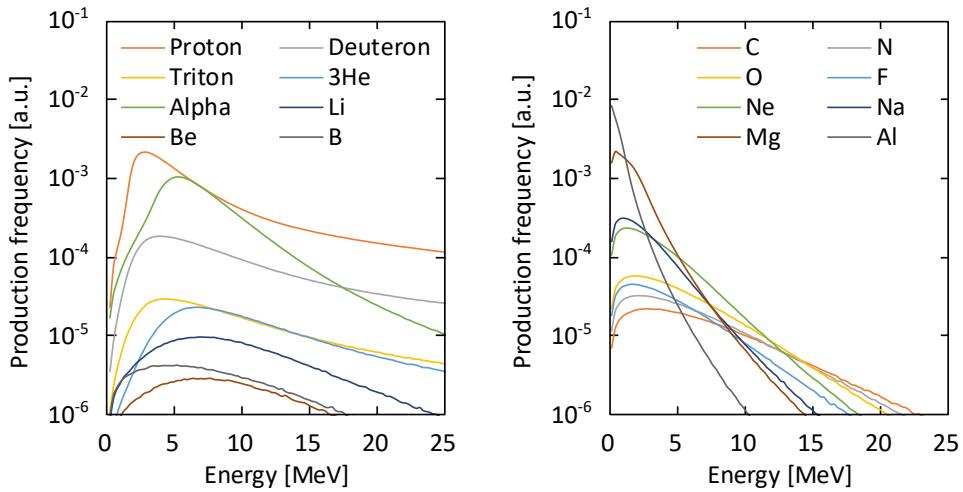

Fig. 1.4 presents the secondary ions produced by the high-energy neutrons with

FIGURE 1.4: Secondary ions produced by terrestrial high-energy neutrons as a function of energy calculated using PHITS [19].

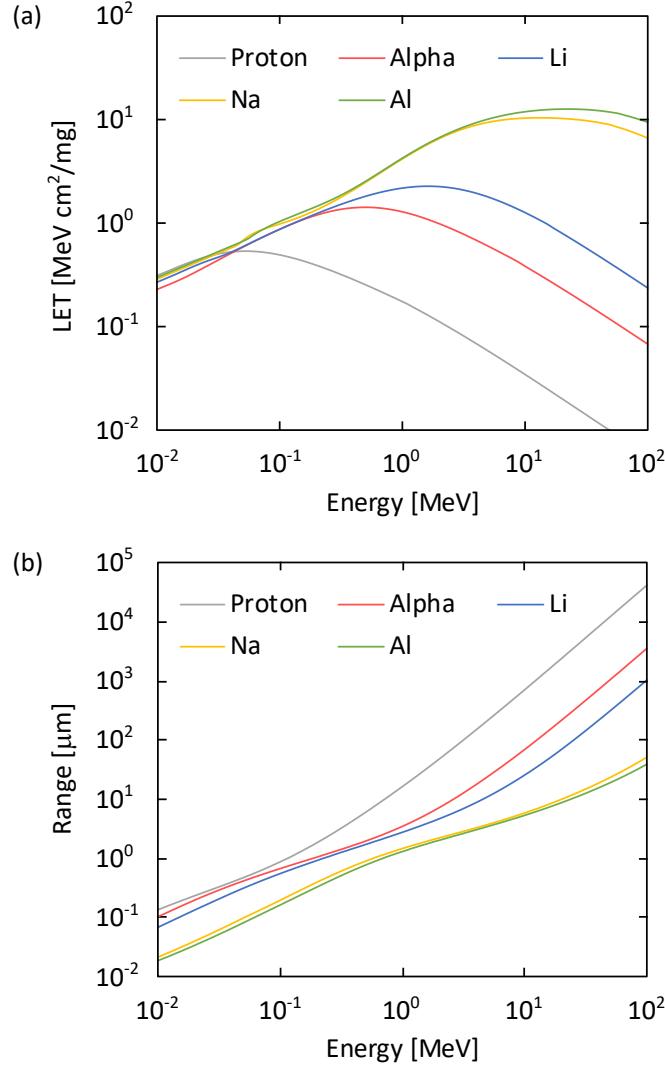

the terrestrial energy spectrum, which are calculated using Particle and Heavy Ion Transport code System (PHITS) [19]. The produced ions range from light elements to heavy elements, where protons are the most abundant element. These secondary ions travel inside the devices and deposit charge along their tracks by ionization. The amount of the charge deposition is often expressed by linear energy transfers (LETs). The LET is defined as the amount of energy loss per unit length. In Fig. 1.5(a), the LETs in silicon for protons, alpha particles, lithium ions, sodium ions, and aluminum ions are shown as a function of the energy, where the calculation is conducted using Stopping and Range of Ions in Matter (SRIM) [20]. The LET depends on the atomic number and energy of ions, as seen in Fig. 1.5(a). Basically, heavier ions have higher LETs and hence can induce larger charge deposition to the semiconductor devices. On the other hand, the ranges of the heavier ions are shorter than those for lighter ions, as shown in Fig. 1.5(b). An interesting feature of the ion energy loss is that the LET reaches its maximum at a certain energy specific to each ion. This LET maximum is called a Bragg peak. The energy at the Bragg peak decreases with the decrease in the atomic number, as observed in Fig. 1.5(a).

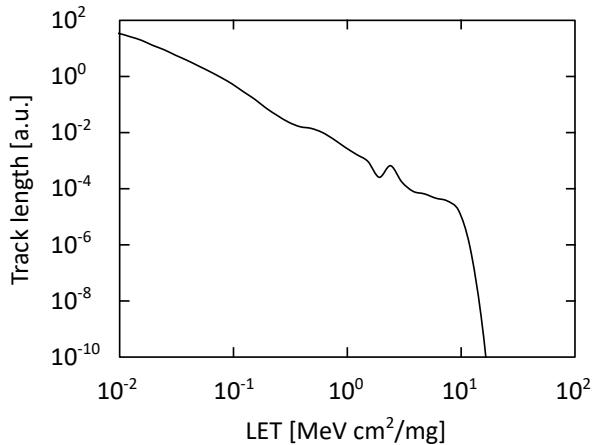

The variety of the secondary ions produced through the interactions between the high-energy neutrons and the device materials results in the broad distribution of the LET. Fig. 1.6 presents a calculation result of the total track length of secondary ions produced in silicon by the high-energy neutrons as a function of their LETs. In this figure, the total track length reflects the number and range of the secondary ions. In other words, the larger number and longer range of the secondary ions with a certain LET results in the longer track length at the LET. As confirmed in Fig. 1.6, the total track length in silicon decreases with increased LET. This means that charge deposition by low-LET ions occurs more frequently than high-LET ions. According to this distribution, the maximum LET is  $\sim 14 \text{ MeV cm}^2/\text{mg}$ . It is worthwhile to note that, in addition to the secondary ions produced through interactions

FIGURE 1.5: (a) LETs and (b) ranges in silicon for protons, alpha particles, lithium ions, sodium ions, and aluminum ions as a function of energy calculated by SRIM [20].

with silicon, those produced through interactions with high-Z materials are also important. This is because the semiconductor devices consist not only of silicon but also of high-Z elements, such as copper, tungsten, and cobalt. The interactions between these high-Z elements and the high-energy neutrons can produce secondary ions with higher-LET than  $14 \text{ MeV cm}^2/\text{mg}$ , leading to larger charge deposition. It is thus necessary to consider the device structure including both silicon and metals for correctly understanding the impact of the high energy neutrons.

Another noteworthy feature of the high-energy neutrons is the anisotropic angular distribution of flux in the terrestrial environment. The angular distribution is expressed as  $\cos^n \theta$ , where  $\theta$  denotes the zenith angle. In this expression, the reasonable value of the exponent  $n$  has been reported as 3 at sea level [21]. This means that the large portion of the high-energy neutrons is directed downward at sea level.

FIGURE 1.6: Total track length of secondary ions produced in silicon by terrestrial high-energy neutrons as a function of their LETs calculated using PHITS [19]. The total track length reflects the number and range of the secondary ions with each LET.

FIGURE 1.7: Cross sections of neutron-induced nuclear reactions for  $^{28}\text{Si}$ ,  $^{10}\text{B}$ , and  $^{11}\text{B}$  atoms as a function of energy obtained from JENDL 4.0 [23] using JANIS [24].

This anisotropic angular distribution can impact on charge deposition in the semiconductor devices because the emission angle of the secondary ions depends on the incident direction of the high-energy neutrons. It is known that the secondary ions produced through spallation reactions tend to be emitted forward, i.e., to the same direction of neutron incidence [22]. These features awaken a concern that the mounting direction of the semiconductor devices may affect the susceptibility to the high-energy neutrons in the terrestrial environment. Therefore, the angular sensitivity of the high-energy neutron-induced soft errors is one of the fundamental issues in terrestrial devices.

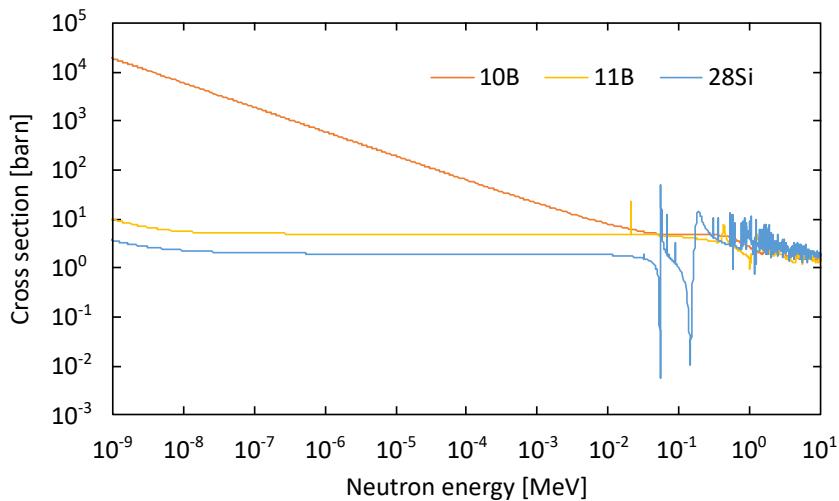

For the thermal neutrons, the soft errors are induced by interactions with  $^{10}\text{B}$  atoms, and hence the sensitivity to the thermal neutrons depends on the abundance of the  $^{10}\text{B}$  atoms in the semiconductor devices. There are two isotopes in natural

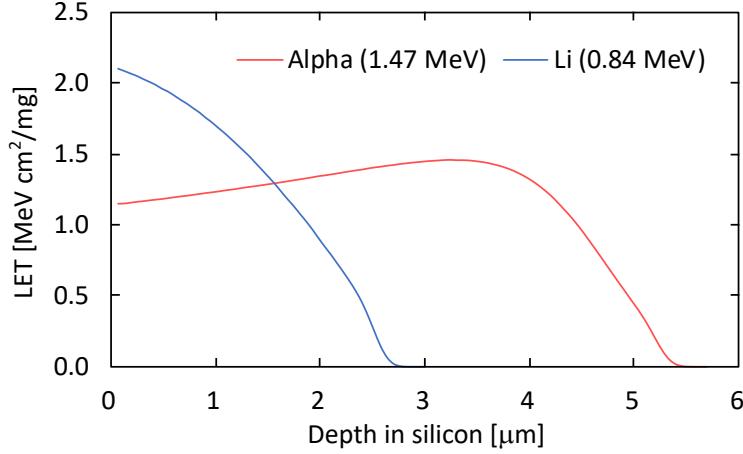

FIGURE 1.8: LETs in silicon for an alpha particle of 1.47 MeV and a lithium ion of 0.84 MeV as a function of depth calculated by SRIM [20].

boron:  $^{11}\text{B}$  (80%) and  $^{10}\text{B}$  (20%). One of the reasons why only the  $^{10}\text{B}$  atom is considered is its large cross section (CS) of nuclear reaction for the thermal neutron. Here, the nuclear reaction CS is defined as the effective area where a target atom can interact with a neutron. In other words, the large CS means the high probability of nuclear reaction. The nuclear reaction CSs for the  $^{10}\text{B}$  and  $^{11}\text{B}$  atoms are compared in Fig. 1.7, where the CS for  $^{28}\text{Si}$  atoms is also shown. The CS for the  $^{10}\text{B}$  atoms at around 0.025 eV is  $\sim 10^4$  barn <sup>2</sup>, which is larger than that for the  $^{11}\text{B}$  and  $^{28}\text{Si}$  atoms by more than three orders of magnitude. Another reason is the production of secondary ions by the fission of the  $^{10}\text{B}$  atoms in neutron capture reaction. When a  $^{10}\text{B}$  atom captures a thermal neutron, a lithium ion, an alpha particle, and a photon (gamma-ray) are emitted:

where no photon is emitted in 6% of the reactions [25]. On the other hand, when a  $^{11}\text{B}$  atom captures a thermal neutron, only a photon is emitted. In the capture reaction of the  $^{10}\text{B}$  atoms, these secondary ions can cause the soft errors through their ionization. The LETs of these ions are shown in Fig. 1.8 as a function of depth in silicon, where the maximum LET is  $\sim 2 \text{ MeV cm}^2/\text{mg}$ . It is worthwhile to point out that the maximum LET induced by the thermal neutrons is considerably lower than that induced by the high-energy neutrons, which  $\sim 14 \text{ MeV cm}^2/\text{mg}$ . [see Fig. 1.6]. Furthermore, the emission direction of the secondary ions is different between the thermal neutrons and the high-energy neutrons. The secondary ions produced in the neutron capture reaction of the  $^{10}\text{B}$  atoms are emitted isotropically, whereas those produced in the spallation reactions induced by the high-energy neutrons are emitted forward, as described above.

<sup>2</sup>1 barn equals to  $10^{-24} \text{ cm}^2$ .

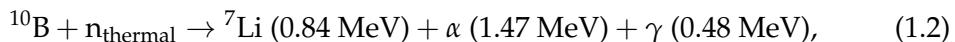

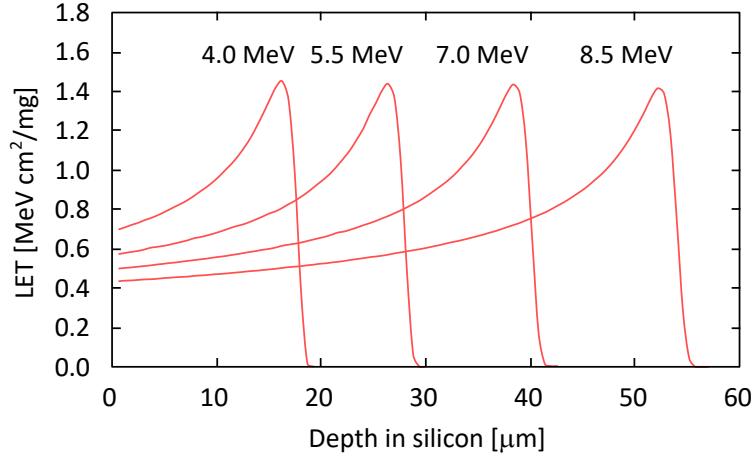

FIGURE 1.9: 3DAP analysis of  $^{10}\text{B}$  atoms in a tungsten plug (reconstructed from [26]). (a) Schematic diagram of the device area used in 3DAP observation. (b) Reconstructed 3D image. (c) Projected image of the reconstructed 3D image along the  $z$ -direction.

In recent semiconductor devices, the  $^{10}\text{B}$  atoms are introduced at the layer of tungsten plugs that serve as contacts between the transistors and the first metal layer. In past devices, the origin of the  $^{10}\text{B}$  atoms was borophosphosilicate glass (BPSG), which was used as a dielectric layer above transistors [27]. For semiconductor devices using the BPSG, the thermal neutrons were considered as a primary source of the terrestrial soft errors [28]. As chemical-mechanical polishing (CMP) was introduced, the BPSG was removed from the device structure, and hence the thermal neutron-induced soft errors were completely suppressed. However, recent manufacturing processes have employed diborane ( $\text{B}_2\text{H}_6$ ) gass instead of silane ( $\text{SiH}_4$ ) gass to improve the performance of the tungsten plugs. The  $^{10}\text{B}$  atoms are present in this diborane gass and remain around the tungsten plug layer of the devices [29]. For example, as shown in Fig. 1.9, the presence of the  $^{10}\text{B}$  atoms was confirmed at the position of the tungsten plug by 3D atom probe (3DAP) analyses [26]. As a result, the thermal neutron-induced soft errors have reemerged as an issue of the terrestrial soft errors.

### 1.2.2 Muons

The atmospheric muons consist of negative and positive muons and are the most abundant particle in the secondary cosmic-rays. From the energy spectra shown in Fig. 1.2, the total integral flux above 1 MeV for the negative and positive muons is  $68 \text{ /cm}^2/\text{h}$ , which is more than three times higher than that for the high-energy neutrons [see Table 1.1]. As seen in Fig. 1.2, a large portion of the negative and positive muons are in the energy range above 100 MeV. The above difference in the integral flux between the muons and the high-energy neutrons mainly reflects the flux difference above 100 MeV. This high abundance of the muons is one of the reasons why the muons are concerned in terrestrial soft errors.

FIGURE 1.10: LETs in silicon for muons and protons as a function of energy calculated by SRIM [20].

Unlike the neutrons, the muons are charged particles and hence can directly deposit charge to the semiconductor devices by ionization. Here, both the negative and positive muons ( $\mu^-$  and  $\mu^+$ ) are unstable particles with the mean lifetime of 2.2  $\mu$ s and decay into three particles:

$$\begin{aligned} \mu^- &\rightarrow e^- + \bar{\nu}_e + \nu_\mu \\ \mu^+ &\rightarrow e^+ + \nu_e + \bar{\nu}_\mu, \end{aligned} \quad (1.3)$$

where  $e^-$  and  $e^+$  are electron and positron,  $\nu_e$  and  $\bar{\nu}_e$  are electron neutrino and electron antineutrino,  $\nu_\mu$  and  $\bar{\nu}_\mu$  are muon neutrino and muon antineutrino, respectively. Although the decayed electrons and positrons are also charged particles, their impact on the soft errors is negligible because their LETs are very low. Fig. 1.10 presents the LETs in silicon for muons and protons as function of the energy. It should be noted that the LETs of the negative and positive muons are almost identical [30]. The LET of the muons is similar to that of the protons, where the maximum LET is  $\sim 0.5$  MeV cm<sup>2</sup>/mg. The discrepancy in the Bragg peak energy is due to the mass difference between the muons and the protons, where the mass of the muons is about one ninth of the mass of the protons [31]. As described above, the proton is one of the secondary ions produced by the high-energy neutrons, and its LET is lower than the other secondary ions [see Fig. 1.5(a)]. This means that the LET of the muons is relatively low compared to the LETs of the secondary ions produced by the high-energy and thermal neutrons. The key point here is that, with the scaling of transistors, the semiconductor devices have become more vulnerable to small charge deposition, i.e., low-LET particles. For this reason, there have been increasing concerns about the muon-induced soft errors in advanced semiconductor devices.

In addition to the direct ionization of the muons, the negative muons can produce secondary ions through muon capture reactions, whereas the positive muons

TABLE 1.3: Energy of alpha particles emitted from radioisotopes in the decay chain of thorium [33].

| Radioisotope      | Half life               | Energy [MeV] |

|-------------------|-------------------------|--------------|

| $^{232}\text{Th}$ | $1.41 \times 10^{10}$ y | 4.013        |

| $^{228}\text{Th}$ | 1.91 y                  | 5.423        |

| $^{224}\text{Ra}$ | 3.66 d                  | 5.685        |

| $^{220}\text{Rn}$ | 55.6 s                  | 6.288        |

| $^{216}\text{Po}$ | 0.15 s                  | 6.778        |

| $^{212}\text{Po}$ | 0.296 $\mu\text{s}$     | 8.784        |

cannot. When the negative muons stop in silicon, 66% of them are captured by silicon nucleus, and the remaining 34% decay as expressed in Eq. (1.3) [32]. In this capture reactions, similarly to the high-energy neutron-induced spallation reactions, various secondary ions are produced: for example,

The resulting secondary ions have higher-LETs than the negative muons and hence can deposit a large amount of charge to the semiconductor devices. An important difference between the muon capture reactions and the neutron-induced spallation reactions is the difference in the emission direction of the secondary ions. In the case of the neutron-induced spallation reactions, the secondary ions are emitted forward. In the case of the muon capture reactions, on the other hand, the secondary ions are emitted isotropically, as is the case of thermal neutron capture reactions of  $^{10}\text{B}$  atoms. This difference could lead to different impacts on the soft errors. Therefore, to properly characterize the negative muon-induced soft errors, it is essential to consider the muon capture reactions and the isotropic emission of the secondary ions.

### 1.2.3 Alpha Particles

The alpha particles are emitted from radioisotopes naturally present in the device materials (mainly packages), as already explained above. The radioisotopes of the primary concern for the soft errors are uranium and thorium and their decay products. For the decay chain of thorium, the radioisotopes emitting the alpha particles and the energy of the emitted alpha particles are listed in Table. 1.3 [33]. There are six radioisotopes emitting the alpha particles, the energy of which is in the range between 4 MeV and 9 MeV.

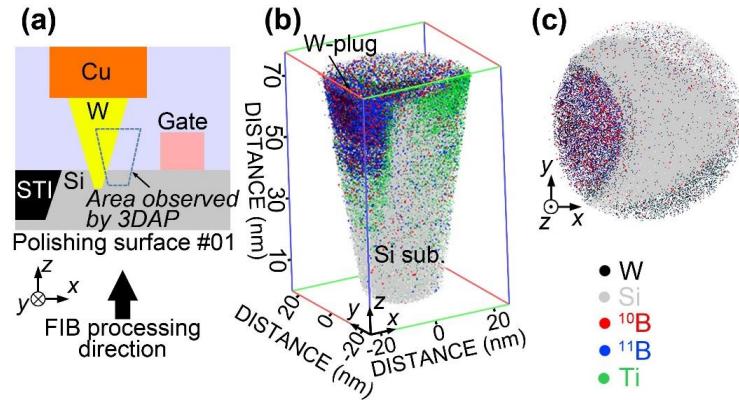

The emitted alpha particles can travel in the semiconductor devices and deposit charge through ionization. The LETs in silicon for the alpha particles with energies from 4.0 MeV to 8.5 MeV are presented in Fig. 1.11 as a function of depth in silicon. The maximum LET is  $\sim 1.5 \text{ MeV cm}^2/\text{mg}$  at the Bragg peaks. A noteworthy feature is the long range of the alpha particle. As confirmed in Fig. 1.11, the range of the

FIGURE 1.11: LET in silicon for alpha particles with energies from 4.0 MeV to 8.5 MeV as a function of depth calculated by SRIM [20].

alpha particle with 5.5 MeV is  $29 \mu\text{m}$  in silicon, which is larger than the scale of the semiconductor device structure, e.g. the thickness of metal layers. This means that the alpha particles emitted in the region of packages can pass through the metal layers of the devices and can reach the region of transistors. This is the reason why the radioisotopes in the packages are of concern in the terrestrial soft errors.

### 1.3 Single-Event Upsets in SRAMs

SRAMs are fundamental memory elements in semiconductor devices because of their high-speed operations. In recent CMOS technologies, SRAM devices are the most susceptible to the terrestrial radiation-induced soft errors [34]. One of the reasons for this is that the size of SRAM cells is considerably small compared to other types of circuit cells, such as latches and FFs. The SRAM cell size has been aggressively scaled down and reaches less than  $0.1 \mu\text{m}^2$  in advanced CMOS technologies [35]. As already mentioned, this size scaling leads to increased vulnerability to radiation-induced charge deposition. Another reason is that, in modern semiconductor devices, such as SoCs, the amount of embedded SRAMs is rapidly growing, and hence the soft errors in the SRAMs can be dominant compared to those in latches, FFs, and combinational logic [34]. Therefore, the impact of the terrestrial radiation on the SRAM devices is of primary concern in the terrestrial soft errors.

#### 1.3.1 SRAM Circuit

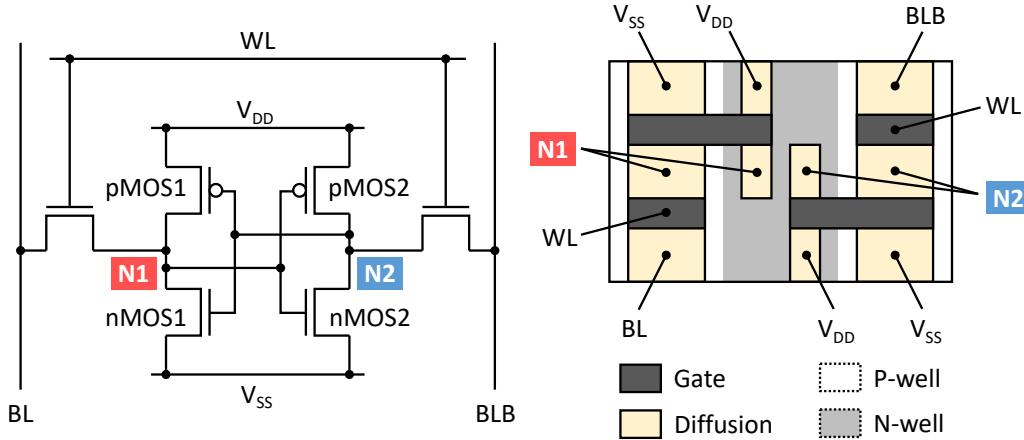

In the SRAM cell, the data value is represented as the voltage levels of two internal nodes of the SRAM circuit. The standard SRAM circuit consists of six transistors: four n-type MOS (nMOS) transistors and two p-type MOS (pMOS) transistors. The schematic circuit and physical layout of the SRAM cell are illustrated in Fig. 1.12. As seen in this illustration, two inverters are connected in a cross-coupled fashion,

FIGURE 1.12: SRAM circuit (left) and schematic cell layout (right).

making a latch circuit. At the same time, two nMOS transistors serve as transfer gates between bit lines (BLs) and the two internal nodes of this latch circuit. In Fig. 1.12, the BLs are denoted as BL and BLB, and the internal nodes are denoted as N1 and N2. The states of the transfer gates are controlled by a word line (WL), which is connected to the gates of these nMOS transistors. In write and read operations of the SRAM cell, the WL is set to high ( $V_{DD}$ ) so as to open the transfer gates. Once the transfer gates are opened, the voltage levels of the two internal nodes, N1 and N2, can be altered or read via the BLs. There are two stable states of the internal nodes, which represent the data values: “0” and “1.” Specifically, if one pair of voltage levels  $(N1, N2) = (\text{high } (V_{DD}), \text{ low } (V_{SS}))$  is defined as the value “1,” another pair  $(N1, N2) = (\text{low } (V_{SS}), \text{ high } (V_{DD}))$  is the value “0.” Since the standard SRAM circuit is a symmetric circuit and the physical layout is symmetric as well, the states of “0” and “1” are topologically identical. Therefore, the noise margins for these two states are essentially the same.

The key point is that the difference in the voltage level of the internal node corresponds to the different amount of charge stored in the node. The amount of charge stored in the high ( $V_{DD}$ ) node can be expressed as  $C_{\text{node}} \times V_{DD}$ , where  $C_{\text{node}}$  denotes the capacitance of the internal node. The capacitance  $C_{\text{node}}$  comprises the gate capacitances of the transistors and various parasitic capacitances inherent in the SRAM cell. Hence, the size scaling of the transistors and the SRAM cell decreases  $C_{\text{node}}$ , resulting in the reduced amount of charge stored in the node. Similarly, the scaling of the supply voltage  $V_{DD}$  also reduces the amount of stored charge. For these reasons, the amount of charge to represent the data value of the SRAM cell decreases with the scaling of CMOS technologies. This apparently leads to the increased vulnerability of the SRAM cells to radiation-induced charge deposition.

### 1.3.2 Single-Event Upset

The most common type of soft errors in the SRAM devices is single-event upsets (SEUs), in which data values stored in one or more SRAM cells are flipped by a single particle strike. When a particle strike deposits charge on an SRAM cell, some charge is collected in the internal nodes. This charge collection can induce a noise current in the SRAM circuit. If the charge collection is significant and the resulting noise current exceeds the noise margin of the SRAM circuit, the internal nodes undergo transition from the current state to another stable state: for example,  $(N1, N2) = (\text{high, low}) \rightarrow (N1, N2) = (\text{low, high})$  in the circuit presented in Fig. 1.12. As a result, a wrong data value is stored in the SRAM cell. Since this state transition is a reversible phenomenon with no permanent damage, the wrong data value can be corrected by rewriting the SRAM cell. Therefore, the SEUs are soft errors.

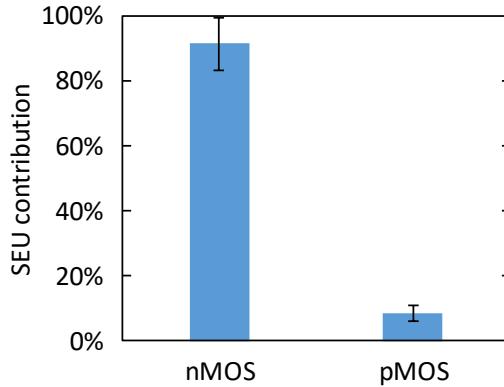

In the physical layout of the SRAM cell, the drain diffusion area of the nMOS transistor in the high node is generally the most sensitive to the particle-induced charge deposition [5]. Basically, the SEUs can occur when transient currents are induced in the off-state transistors of the SRAM circuit. In this sense, both the nMOS transistor in the high node and the pMOS transistor in the low node are sensitive to the charge deposition for the SEU occurrence. On the other hand, there is the difference in the size and driving power between the nMOS and pMOS transistors. In most cases, the size of the nMOS transistor is designed to be larger than that of the pMOS transistor to maximize the performance of the SRAM cell [36]. In this case, the charge collection in the nMOS transistor is more efficient than that in the pMOS transistor because the transient current is generated by charge collection at the drain diffusion and the drain area increases with the size of transistors. At the same time, the driving power is stronger for the nMOS transistors than for the pMOS transistors. Hence, the low node is more resilient to the transient current than the high node because the low level ( $V_{SS}$ ) is kept by the nMOS transistors. For these reasons, the nMOS transistor in the high node is the dominant contributor to the SEU occurrence. As an example, Fig. 1.13 presents a simulation result comparing the contributions of the nMOS and pMOS transistors to the SEU occurrence in a 28-nm bulk planar SRAM [37]. As confirmed in this result, the contribution of the nMOS transistor is dominant, more than 90% in this case. The significant contribution of nMOS transistors was also demonstrated in FFs [38].

One of the important parameters indicating the SEU susceptibility of an SRAM circuit is a critical charge, which is denoted as  $Q_{\text{crit}}$ . The critical charge is the minimum amount of collected charge required for the SEU occurrence. Hence, the SEU susceptibility increases with the decreased critical charge. In the first order approximation, the critical charge equals to the amount of charge stored in the internal node of the SRAM cell:  $Q_{\text{crit}} \sim C_{\text{node}} \times V_{DD}$ . Therefore, the increased SEU susceptibility due to the scaling of the supply voltage and the SRAM cell size can be interpreted as the lowering of the critical charge. It should be noted that the critical charge is different between the high and low nodes of the SRAM circuit. As explained above,

FIGURE 1.13: Simulated SEU contribution of nMOS and pMOS transistors in a 28-nm bulk planar SRAM (reconstructed from [37]).

the high node is typically more vulnerable to transient currents than the low node. This difference leads to the lower critical charge for the high node than for the low node.

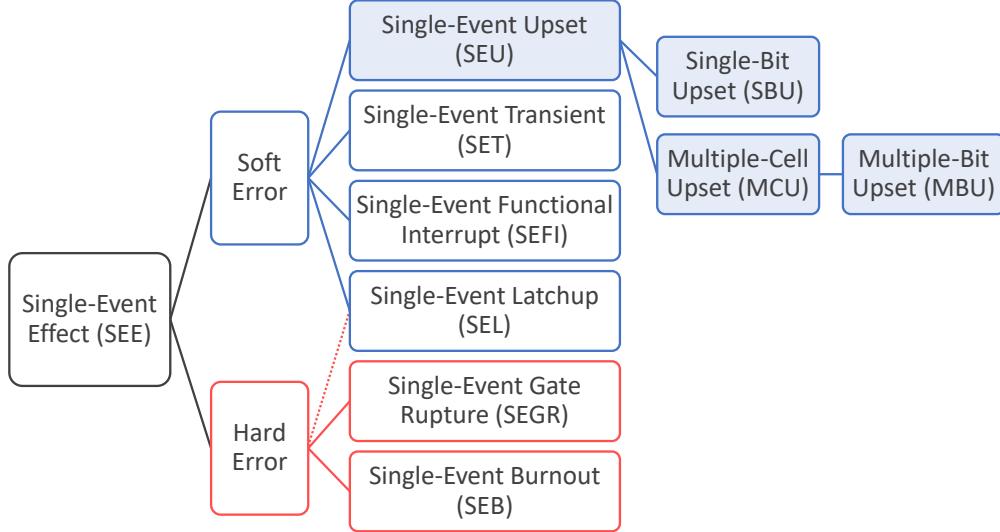

### 1.3.3 Classification