| Title        | チェーンリンク形マルチレベル方式による系統連系用<br>電力変換器の高性能化に関する研究 |

|--------------|----------------------------------------------|

| Author(s)    | 羽田野, 伸彦                                      |

| Citation     | 大阪大学, 2009, 博士論文                             |

| Version Type | VoR                                          |

| URL          | https://hdl.handle.net/11094/844             |

| rights       |                                              |

| Note         |                                              |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

# チェーンリンク形マルチレベル方式による 系統連系用電力変換器の高性能化に関する研究

2009年

羽田野 伸彦

# 内容梗概

電力系統分野におけるパワーエレクトロニクス技術は,50H z 地域と 60H z 地域を連系するための周波数変換装置に始まり、長距離送電系統の安定度対策を目的とした無効電力補償装置、効率的な設備形成や柔軟な系統運用を可能とする直流送電設備などに適用され、電力の安定供給に重要な役割を担ってきた。また、分散形電源や電力貯蔵装置を系統連系するためにも活用され、適用範囲はますます広がりつつある。

系統連系される大容量機器の場合,パワー半導体デバイスを多数個直並列に接続した単体の電力変換器を用いた構成も考えられる。しかし、電圧や電流分担の均等化を図るため、特性を揃えた半導体デバイスの選定や、スナバ回路などの付加が必要となる。また、制御性の向上や発生高調波低減のためにスイッチング周波数を高くすると、半導体デバイスのスイッチング損失やスナバ回路の損失が増加し、機器効率が低下する。このため、半導体デバイスの直並列数とスイッチング周波数は適度に抑え、複数台の電力変換器を直列または並列に接続する多重化方式を採用することが一般的である。

多重化により複数の出力波形を合成すれば、全体として等価的なスイッチング周波数は高くなり、発生高調波を低減できる。さらに、個々の電力変換器のスイッチング周波数は低いため、スイッチング損失を低減でき、機器効率の向上も同時に実現できる。しかし、従来の多重化方式では、鉄心や巻線の構造が複雑な多重変圧器が必要であった。このため、機器の損失増加や大型化を招いていた。また、1 サイクル単位でスイッチング動作がパターン化されており、高調波を取扱うような、高い制御性を必要とされる機器への適用は、今後の課題とされていた。

このような状況の中,電力系統に適用される大容量機器を小型軽量かつ高効率に実現すること を目的に、電力変換器をトランスレスで系統連系するための回路構成や制御に関する研究開発が 盛んになっている。

マルチレベル変換器は、変圧器やリアクトルを用いずに出力波形の合成を行い、電力変換器の大容量化と高調波低減を可能とする。代表的な方式の一つであるチェーンリンク形マルチレベル変換器(Chain Link type Multilevel Converter: CLMC)は、Hブリッジ形の単相変換器を単位セルとし、複数のセルを直列に接続して構成される。この方式は、セルの直列段数を増加させるだけで出力波形のレベル数も増加し、制御性の向上とスイッチング損失の低減を同時に実現できる。

このように、CLMCは、系統連系用電力変換器の抜本的な改善を図るにあたり、優れたポテンシャルを有する。しかし、セルの直列接続に伴い導通損失が増加し、反って機器効率が悪化する場合もある。また、個々のセルに DC 電源が分離して回路構成されるため、特定のセルに出力が集中すると、機器容量を有効に利用できないことにつながる。CLMC を系統連系に用いるためには、これらの制約を解決する必要がある。

以上のような背景を踏まえ、本研究においては、CLMCの適用により系統連系用電力変換器の高性能化を図ると共に、実証試験およびディジタルシミュレーションにより実現可能性を示すことを目的とする。

本論文は、これらの背景と目的より動機づけられた一連の研究から得られた成果をまとめたものであり、7つの章より構成される。

第1章では、本研究の背景として、電力系統分野におけるパワーエレクトロニクス技術の動向、 系統連系用電力変換器の現状、および新たな回路技術としてのマルチレベル変換器について述べ ると共に、技術課題を示し、本研究の目的を明確に位置付ける。

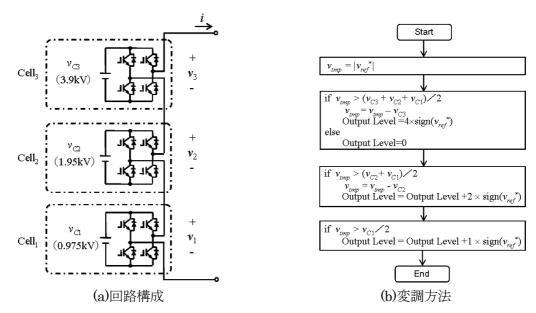

第2章では、CLMCの回路構成上の課題を示し、その解決策として、ハイブリッドCLMCの導入について検討する。まず、セルの直列接続に伴う機器効率低下の可能性と、DC電源分離の必要性について述べる。次に、本研究で用いる方式として、セルの直列段数を抑制するために高周波PWMを混じえたハイブリッドCLMCと、さらに、電圧が2倍ずつ異なるセルを組み合わせ、多レベル化を容易とする2進ハイブリッドCLMCについて、基本的な回路構成と制御手法を示す。

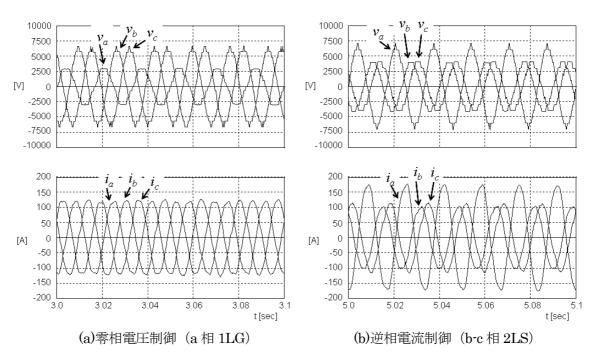

第3章では、三相電力系統に CLMC を適用するための、基本的な制御手法を示す。まず、系統不平衡時には、電力変換器の三相出力にも不平衡が生じることを示す。次に、その解決策として、零相電圧もしくは逆相電流により、三相出力を制御する理論を示す。また、これらの理論の実現に不可欠な技術として、系統電圧に大幅な不平衡が発生しても、過電流に至ることなく、出力電流を指令値通りに制御するための手法を示す。

第4章では、CLMCを、直列形瞬時電圧低下補償装置(Dynamic Voltage Restorer: DVR)に適用するための技術を確立する。まず、一相もしくは二相事故による不平衡な瞬低に対しても、零相電圧により、三相の補償エネルギーを制御できること示す。次に、400V-100kVA級の試験装置で実証する。そして、瞬時値領域に拡張した零相電圧制御を用いた6.6kV三相トランスレスDVRを試設計し、ディジタルシミュレーションにより検証する。

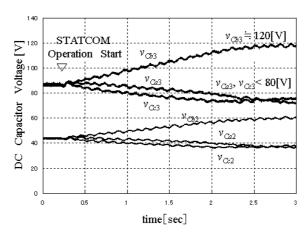

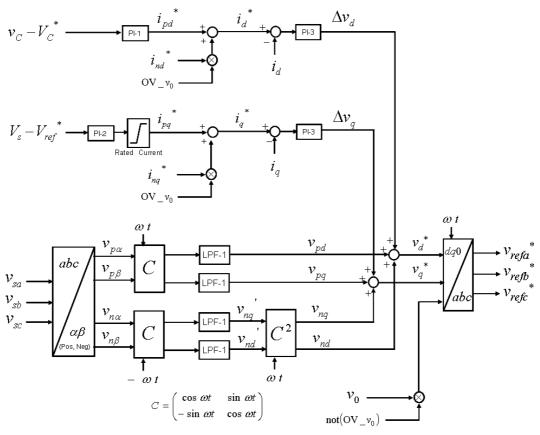

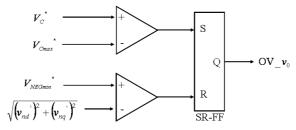

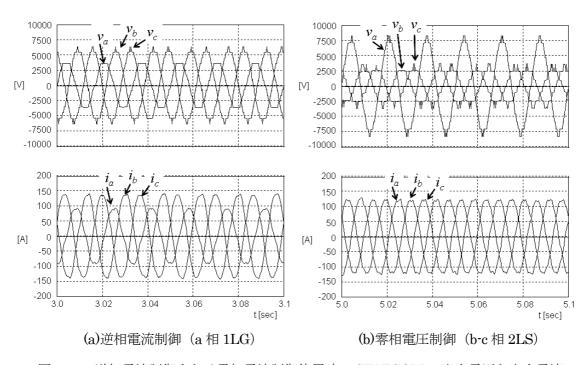

第 5 章では、CLMC を、自励式無効電力補償装置(STATic synchronous COMpensator:STATCOM)に適用するための技術を確立する。まず、系統電圧に不平衡が生じても、逆相電流により各相の CLMC の DC 電圧を制御できることを示す。次に、200V-10kVA 級の試験装置で実証する。そして、逆相電流制御に伴う機能的な制約の解消を目的として、不平衡の大小に応じて、逆相電流制御と零相電圧制御を切り替えて DC 電圧制御を行う 6.6kV 三相トランスレスSTATCOM を試設計し、ディジタルシミュレーションにより検証する。

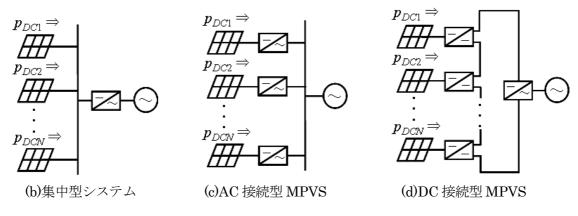

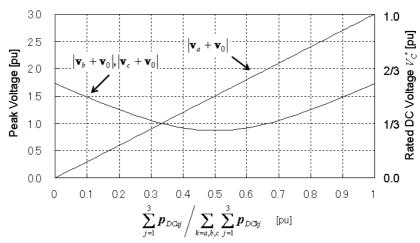

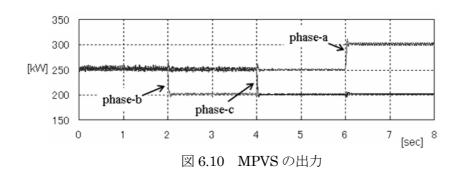

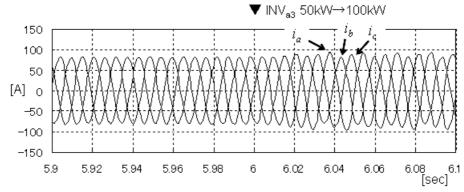

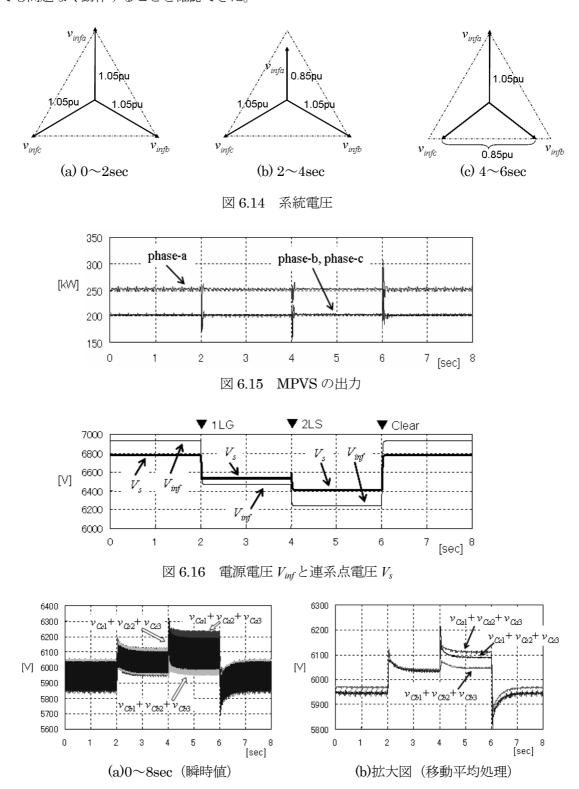

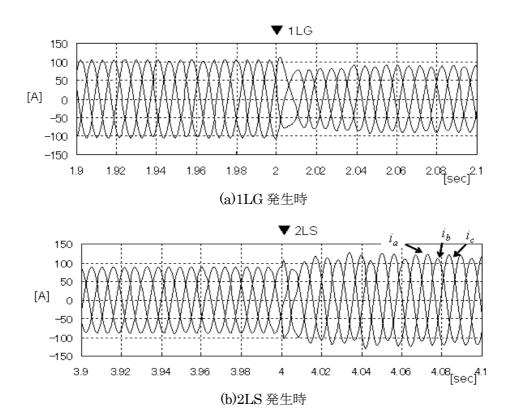

第6章では、CLMCを、分散形電源の系統連系装置に適用するための技術を確立する。まず、零相電圧制御により、DC電源の出力に不平衡が存在する場合にも、電力系統へは三相平衡な電流を出力できることを示す。次に、零相電圧制御の適用範囲を補う目的から、逆相電流制御を併用する三相出力制御を用いた 6.6kV-1MVA システムを試設計し、ディジタルシミュレーションにより検証する。

第7章では、本研究から得られた成果を総括すると共に、今後の課題を述べる。

# 目次

| 第1 | 章   | 緒論    |                                                          |

|----|-----|-------|----------------------------------------------------------|

|    | 1.1 | 研究    | の背景                                                      |

|    |     | 1.1.1 | 電力系統分野におけるパワーエレクトロニクス技術の動向 ・・・・・・・・・ 1                   |

|    |     | 1.1.2 | 系統連系用電力変換器の現状・・・・・・・・・・・・・・・・・1                          |

|    |     | 1.1.3 | マルチレベル変換器の適用 ・・・・・・・・・・・・・・・・・・・・・・・ 2                   |

|    | 1.2 | 本研?   | 究の目的 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 3                     |

|    | 1.3 | 論文    | の概要・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ 4                    |

|    | 参考  | 5文献   | 5                                                        |

| 第2 | 章   | ハイフ   | 「リッド構成によるチェーンリンク形マルチレベル変換器(CLMC)                         |

|    | 2.1 |       |                                                          |

|    | 2.2 |       | 構成上の課題 · · · · · · · · · · · · · · · · · · ·             |

|    |     | 2.2.1 | 電力変換器の直列接続に伴う導通損失の増加・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |

|    |     | 2.2.2 | DC 電源の分離 · · · · · · · · · · · · · · · · · · ·           |

|    | 2.3 | ハイ    | ブリッド変換器の導入 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・          |

|    |     | 2.3.1 | 高周波 PWM を混じえたハイブリッド CLMC ・・・・・・ 11                       |

|    |     |       | 2 進ハイブリッド CLMC · · · · · · · 12                          |

|    |     | 2.3.3 | 2 進構成におけるセルの出力分担制御 ・・・・・・・・・・ 13                         |

|    |     | 2.3.4 | 2 進構成におけるセルの出力分担制御に関する原理実証試験 ・・・・・・・・ 14                 |

|    |     |       |                                                          |

|    | 参考  | 令文献   |                                                          |

| 第3 |     |       | 系統における電力変換器の制御                                           |

|    | 3.1 |       |                                                          |

|    | 3.2 |       | 不平衡の影響 ・・・・・・・・・・・・・・・・・・・・・・・19                         |

|    | 3.3 | 零相1   | 電圧による三相出力制御 ・・・・・・・・・・・・・・・・・・ 21                        |

|    |     | 3.3.1 | 基本原理 • • • • • • • • 21                                  |

|    |     | 3.3.2 | 適用限界 ・・・・・・・・・・・・・・・・・・・・・・ 24                           |

|    | 3.4 | 逆相1   | 電流による三相出力制御 ・・・・・・・・・・・・・・・・・・・・・・・・ 25                  |

|    | 3.5 | 系統    | 事故時における電流制御 ······ 26                                    |

|    |     | 3.5.1 | 検討モデル・・・・・・・・・・・・・・・・・・・・・・・・・・ 26                       |

|    |     | 3.5.2 | 二相短絡事故に対する応答 ・・・・・・・・・・・・・・・・・ 28                        |

|    |     | 3.5.3 | 逆相過電流への対応・・・・・・・・・・・・・・・・・・・29                           |

|    |     |       | 系統事故時の電流制御に関する原理実証試験 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・  |            |

|----|-----|-------|------------------------------------------------------------|------------|

|    |     |       |                                                            |            |

|    | 参考  | 文献・   | •••••                                                      | 33         |

|    |     |       |                                                            |            |

| 第4 | 章   | チェー   | ンリンク形マルチレベル変換器を用いた直列形瞬時電圧低下補償装置(DVR)                       |            |

|    | 4.1 | 緒言    |                                                            | 35         |

|    | 4.2 | DVR   | への適用 ・・・・・・                                                |            |

|    |     | 4.2.1 | 基本構成 · · · · · · · · · · · · · · · · · · ·                 | 36         |

|    |     | 4.2.2 | 零相電圧による三相出力制御の適用 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・      | 37         |

|    | 4.3 | 零相智   | 電圧による三相出力制御に関する原理実証試験 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 40         |

|    |     | 4.3.1 | 試験回路の構成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 40         |

|    |     | 4.3.2 | 制御手法 · · · · · · · · · · · · · · · · · · ·                 |            |

|    |     | 4.3.3 | 試験結果 · · · · · · · · · · · · · · · · · · ·                 | 42         |

|    | 4.4 | 6.6kV | 7 トランスレス DVR の試設計 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・     | 43         |

|    |     | 4.4.1 | 回路設計 · · · · · · · · · · · · · · · · · · ·                 |            |

|    |     | 4.4.2 | 制御系の設計・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 | 48         |

|    |     | 4.4.3 | ディジタルシミュレーションによる検証 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・    | <b>5</b> 3 |

|    | 4.5 | 結言    |                                                            | 57         |

|    | 参考  | 文献・   |                                                            | 57         |

|    |     |       |                                                            |            |

| 第5 | 章   | チェー   | ンリンク形マルチレベル変換器を用いた自励式無効電力補償装置(STATCOM                      | [)         |

|    | 5.1 |       |                                                            |            |

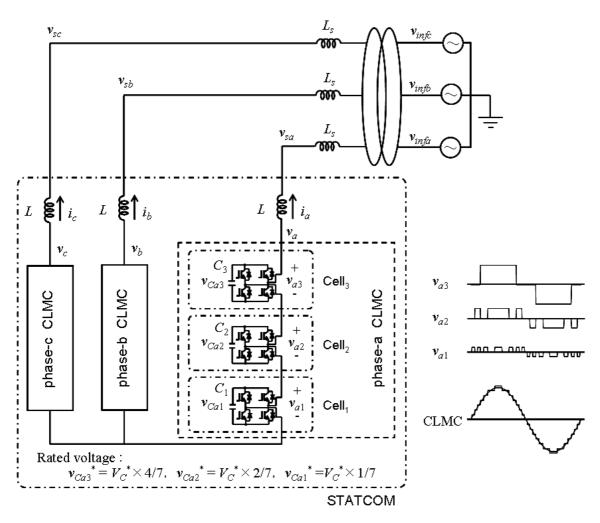

|    | 5.2 | STAT  | 'COM 〜の適用 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・             | 60         |

|    |     | 5.2.1 | 基本構成 · · · · · · · · · · · · · · · · · · ·                 | 60         |

|    |     | 5.2.2 | 逆相電流による三相出力制御の適用・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・       | 61         |

|    | 5.3 |       | 電流による三相出力制御に関する原理実証試験 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ |            |

|    |     | 5.3.1 | 試験回路の構成・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                |            |

|    |     | 5.3.2 | 制御手法・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                   |            |

|    |     | 5.3.3 | 高調波補償試験 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・               | 67         |

|    |     | 5.3.4 | 系統電圧不平衡試験 · · · · · · · · · · · · · · · · · · ·            | 67         |

|    | 5.4 | 6.6kV | 7 トランスレス STATCOM の試設計 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 68         |

|    |     | 5.4.1 | 回路構成 · · · · · · · · · · · · · · · · · · ·                 | 68         |

|    |     | 5.4.2 | 制御系の設計・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 | 69         |

|    |     | 5.4.3 | 制御定数の設定・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                 | <b>7</b> 3 |

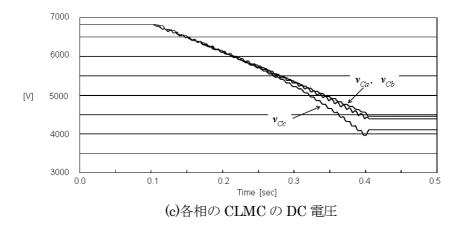

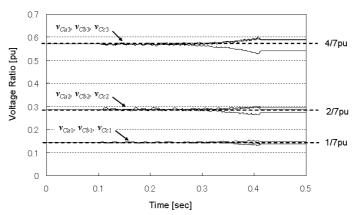

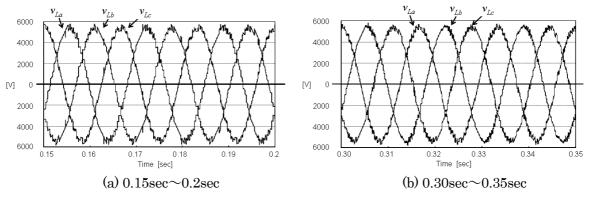

|    |     |       | ディジタルシミュレーションによる検証 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・    |            |

|    | 5.5 | 結言    |                                                            | 78         |

|    | 杂耂  | 4本分   |                                                            | 70         |

| 第6章  | チェーンリンク形マルチレベル変換器を用いた分散形電源の系統連系装置                                    |     |

|------|----------------------------------------------------------------------|-----|

| 6.1  | 緒言                                                                   | 81  |

| 6.2  | モジュラーPV システムへの適用 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                | 82  |

|      | 6.2.1 基本構成                                                           | 82  |

|      | 6.2.2 零相電圧による三相出力制御の適用 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・          | 83  |

|      | <b>6.2.3</b> PV インバータセルの出力分担制御 · · · · · · · · · · · · · · · · · · · | 86  |

| 6.3  | 6.6kV-1MVA システムの試設計・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・              | 87  |

|      | 6.3.1 回路構成                                                           | 87  |

|      | 6.3.2 制御系の設計・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     | 88  |

|      | 6.3.3 ディジタルシミュレーションによる検証 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・        |     |

|      | 結言                                                                   |     |

| 参考   | う文献 ・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                             | 94  |

|      |                                                                      |     |

| 第7章  | 結論                                                                   | 96  |

|      |                                                                      |     |

| 謝辞・・ |                                                                      | 99  |

|      |                                                                      |     |

| 研究業績 | <b>賃 ······</b> ]                                                    | 100 |

# 第1章 緒論

### 1.1 研究の背景

#### 1.1.1 電力系統分野におけるパワーエレクトロニクス技術の動向

電力系統分野におけるパワーエレクトロニクス技術は,50H z 地域と 60H z 地域を連系するための周波数変換装置に始まり、長距離送電系統の安定度対策を目的とした無効電力補償装置、効率的な設備形成や柔軟な系統運用を可能とする直流送電設備などに適用され、電力の安定供給に重要な役割を担ってきた。また、分散形電源や電力貯蔵装置を系統連系するためにも活用され、適用範囲はますます広がりつつある[1]。

今日では、生産設備の高度化、情報化の進展等により、電気の利用は社会のすみずみに行きわたっている。雷害対策なども進歩し、長時間の停電が発生することは稀になってきた。このような状況の中、電力の品質として、瞬低(瞬時電圧低下)が社会的に関心を集めている。従来、瞬低対策は、小容量の UPS(Uninterruptible Power Supply)を負荷機器ごとに設置することにより行われてきた。しかし、対策を必要とする負荷の種類は拡大する傾向にあり、個別機器ごとの対策では抜け落ちが発生する恐れがある。これを解決する手段として、負荷母線あるいは変圧器バンク単位で一括集中補償できる、大容量対策装置が開発された[2][3]。

また、地球環境問題およびエネルギー資源問題の解決策として、自然エネルギー電源である太陽光発電や風力発電、高いエネルギー利用効率が得られる燃料電池などを用いた分散形電源の普及が期待されている。ただし、これらは電力会社より制御を行わず、また、運転状態が把握できない。このため、逆潮流による電圧上昇、並解列に伴う電圧変動、系統事故時の一斉脱落による電圧低下、高調波障害、系統周波数への影響などが懸念されている。現時点では、連系される分散形電源の容量が系統規模に比べて大きくないため、このような問題は顕在化していないが、将来に備え、新たな対策について検討しておく必要がある[4]。

このように,近年では,高品質な電力供給へのニーズや分散形電源の普及促進を背景とした機器開発も,活発に進められている[5][6]。

#### 1.1.2 系統連系用電力変換器の現状

系統連系される大容量機器の場合,パワー半導体デバイスを多数個直並列に接続した単体の電力変換器を用いた構成も考えられる。しかし,電圧や電流分担の均等化を図るため,特性を揃えた半導体デバイスの選定や,スナバ回路などの付加が必要となる。また,制御性の向上や発生高調波低減のためにスイッチング周波数を高くすると、半導体デバイスのスイッチング損失やスナバ回路の損失が増加し、機器効率が低下する。このため、半導体デバイスの直並列数とスイッチング周波数は適度に抑え、複数台の電力変換器を直列または並列に接続する多重化方式を採用することが一般的である[7]-[9]。

例えば、1991年3月に、関西電力(株)の犬山開閉所に設置された±80MVAの自励式無効電力補

償装置は、一相あたりの回路を単相変換器の8段多重で構成している。個々の単相変換器は1パルス動作であるが、各段で7.5度ずつ位相シフトする移相巻線を設けた多重変圧器を用い、出力電圧を正弦波に近い波形とし、高調波を低減するように設計されている[10]。また、2004年6月に、関西電力(株)の神崎変電所に設置された±80MVAの自励式無効電力補償装置は、3レベル変換器を採用することで多重台数を低減し、全体を小型化している。スイッチング方式には、予めパルスパターンをテーブル化しておき出力電圧に応じて選択する、特定次数消去3パルスPWM制御を採用している。この方式では、パルスパターンを適切に設定することにより、高い電圧利用率と発生高調波の低減が可能となる[11]。

多重化により複数の出力波形を合成すれば、全体として等価的なスイッチング周波数は高くなり、発生高調波を低減できる。さらに、個々の電力変換器のスイッチング周波数は低いため、スイッチング損失を低減でき、機器効率の向上も同時に実現できる。しかし、従来の多重化方式では、鉄心や巻線の構造が複雑な多重変圧器が必要であった。このため、機器の損失増加や大型化を招いていた[12]。また、1 サイクル単位でスイッチング動作がパターン化されており、高調波を取扱うような、高い制御性を必要とされる機器への適用は、今後の課題とされていた[13][14]。

このような状況の中、電力系統に適用される大容量機器を小型軽量かつ高効率に実現することを目的に、電力変換器をトランスレスで系統連系するための回路構成や制御に関する研究開発が盛んになっている[15]-[19]。

#### 1.1.3 マルチレベル変換器の適用

マルチレベル変換器は、変圧器やリアクトルを用いずに出力波形の合成を行い、電力変換器の大容量化と高調波低減を可能とする。代表的な方式としては、ダイオードクランプ形マルチレベル変換器(Diode Clamped type Multilevel Converter: DCMC)と、チェーンリンク形マルチレベル変換器(Chain Link type Multilevel Converter: CLMC)があげられる[20][21]。

DCMC は、電動機駆動などの用途に普及が進んでいるが、次のような制約がある。まず、任意の N レベルの回路を構成することも可能であるが、一相あたり 2(N-2)個のクランプダイオードが必要になり、部品点数の増加を招く。また、5 レベル以上の構成では、電圧調整のための外部回路が必要になる。

一方、CLMCは、Hブリッジ形の単相変換器を単位セルとし、複数のセルを直列に接続して構成される。この方式は、セルの直列段数を増加させるだけで出力波形のレベル数も増加し、制御性の向上とスイッチング損失の低減を同時に実現できる。そして、DCMCにおけるクランプダイオードやクランプコンデンサのような補助回路が不要となり、電力変換器をシンプルに構成できるメリットがある。

このように、CLMCは、系統連系用電力変換器の抜本的な改善を図るにあたり、優れたポテンシャルを有する。しかし、セルの直列接続に伴い導通損失が増加し、反って機器効率が悪化する場合もある。また、個々のセルに DC 電源が分離して回路構成されるため、特定のセルに出力が集中すると、機器容量を有効に利用できないことにつながる。CLMC を系統連系に用いるためには、これらの制約を解決する必要がある。

## 1.2 本研究の目的

以上のような背景を踏まえ、本研究においては、CLMCの適用により系統連系用電力変換器の高性能化を図ると共に、実証試験およびディジタルシミュレーションにより実現可能性を示すことを目的とする。

CLMC を系統連系に用いるにあたっての制約は、前述の通りである。これらの解決のため、要素技術と応用技術の観点から、次のように具体的な研究課題を設定する。

#### 要素技術

多重化変換器においてセルの台数を抑制する方策として、電圧やスイッチング周波数が異なる複数のセルを組み合わせるハイブリッド変換器が提案されている[22]-[24]。文献[22]では高周波 PWM を混じえた方式が、また、文献[23][24]では DC 電圧が 2 倍ずつの関係にある電力変換器を組み合わせる方式が報告されている。本研究では、これらの考え方を、系統連系用のCLMC に用いることを試みる。

系統連系用電力変換器は、系統電圧や出力電流の変化に追従しなければならない。このとき、出力電圧の波高値が一定以上低下すれば、CLMCでは全てのセルを動作させる必要はない。しかし、このように制御すると、停止させたセルに設置された DC 電源が利用されない。また、三相構成では、出力電圧や電流が不平衡になると、出力が特定の相に偏り、機器容量が出力の大きい CLMC に制限される。さらに、各相の CLMC の DC 電源の出力に、不平衡が生じることもありうる。本研究では、このような状況においても、セルや CLMC の出力を個別に制御し、機器容量を有効に利用する手法を確立する。

#### 応用技術

CLMC を, 直列形瞬低補償装置 (Dynamic Voltage Restorer: DVR), 自励式無効電力補償装置 (STATic synchronous COMpensator: STATCOM), および分散形電源の系統連系装置 に適用することを目的に, 前述した要素技術をこれらの機器に組み込む方策を検討する。

DVR は、電力系統と負荷の間に直列に接続され、瞬低が発生した際には電圧変動分を補償するよう動作する装置である。実系統で発生する瞬低では、電圧の低下幅は様々である。また大半の場合、位相の急変も発生する。さらに、補償を進めるにつれ、DC 電源の充電エネルギーが低下する。本研究では、このような条件下で、個々の DC 電源の充電エネルギーを有効に利用するための技術を確立する。

一方、STATCOM は、電力系統に無効電力を供給し、系統電圧の変動や負荷力率を改善するよう動作する装置である。現実の電力系統が完全に三相平衡であることは稀であり、さらに事故時には、系統電圧の振幅や位相が急変し、大幅な不平衡が生じる。これに伴い、STATCOMから逆相電力を出力すると、各相の CLMC の DC 電圧を制御できなくなり、機器停止に至る。本研究では、このような状況でも STATCOM が運転継続できるよう、三相出力を制御する手法を確立する。

また、CLMC を分散形電源の系統連系装置に適用すれば、個々の DC 電源の特性が異なって

も、それぞれについて最適な動作点で運転することができ、発電効率の向上が期待できる。しかし、DC 電源ごとの出力が異なれば、AC 側に不平衡な電流を出力することになる。本研究では、このような状況においても、三相平衡な電流を出力するための制御手法について検討する。

# 1.3 論文の概要

本論文は、上記の背景と目的より動機づけられた一連の研究から得られた成果をまとめたものであり、7つの章より構成される。

本章では、本研究の背景として、電力系統分野におけるパワーエレクトロニクス技術の動向、 系統連系用電力変換器の現状、および新たな回路技術としてのマルチレベル変換器について述べると共に、技術課題を示し、本研究の目的を明確に位置付けた。

第2章では、CLMCの回路構成上の課題を示し、その解決策として、ハイブリッドCLMCの導入について検討する。まず、セルの直列接続に伴う機器効率低下の可能性と、DC電源分離の必要性について述べる。次に、本研究で用いる方式として、セルの直列段数を抑制するために高周波PWMを混じえたハイブリッドCLMCと、さらに、電圧が2倍ずつ異なるセルを組み合わせ、多レベル化を容易とする2進ハイブリッドCLMC[25]について、基本的な回路構成と制御手法を示す。第3章では、三相電力系統にCLMCを適用するための、基本的な制御手法を示す。まず、系統不平衡時には、電力変換器の三相出力にも不平衡が生じることを示す。次に、その解決策として、零相電圧[26]もしくは逆相電流[27]により、三相出力を制御する理論を示す。また、これらの理論の実現に不可欠な技術として、系統電圧に大幅な不平衡が発生しても、過電流に至ることなく、出力電流を指令値通りに制御するための手法を示す[28]。

第4章では、CLMC を、三相 DVR に適用するための技術を確立する。まず、一相もしくは二相事故による不平衡な瞬低に対しても、零相電圧により、三相の補償エネルギーを制御できること示す。次に、400V-100kVA級の試験装置で実証する[29]。そして、瞬時値領域に拡張した零相電圧制御[26]を用いた 6.6kV 三相トランスレス DVR を試設計し、ディジタルシミュレーションにより検証する。

第5章では、CLMCを、三相STATCOMに適用するための技術を確立する。まず、系統電圧に不平衡が生じても、逆相電流により各相のCLMCのDC電圧を制御できることを示す。次に、200V-10kVA級の試験装置で実証する[30]。そして、逆相電流制御に伴う機能的な制約の解消を目的として、不平衡の大小に応じて、逆相電流制御[27]と零相電圧制御[31]を切り替えてDC電圧制御を行う6.6kV三相トランスレスSTATCOMを試設計し、ディジタルシミュレーションにより検証する。

第6章では、CLMCを、分散形電源の系統連系装置に適用するための技術を確立する。まず、零相電圧制御により、DC電源の出力に不平衡が存在する場合にも、電力系統へは三相平衡な電流を出力できることを示す。次に、零相電圧制御の適用範囲を補う目的から、逆相電流制御を併用する三相出力制御を用いた 6.6kV-1MVA システムを試設計し、ディジタルシミュレーションにより検証する[31]。

第7章では、本研究から得られた成果を総括すると共に、今後の課題を述べる。

## 参考文献

- [1] 「電力系統用パワーエレクトロニクス設備の現状と設計・保守基準」, 電気協同研究, 第 57 巻第 2 号, pp.5-13 (2001)

- [2] 岡田雅彦,山口寿士:「電力会社における瞬低への取り組み」,電気評論,2002 年 4 月号,pp.11-17 (2002)

- [3] 佐藤寛, 佐野耕市: 「大容量瞬低対策装置の開発状況と課題」, 電気評論, 2002 年 4 月号, pp.37-42 (2002)

- [4] 石川忠夫: 「分散電源の電力系統連系技術の最新動向」, 電気学会論文誌 B, Vol.126-B, No.10, pp.964-968 (2006)

- [5] 「配電系統に適用されるパワーエレクトロニクス技術の最新動向」,電気学会技術報告,第 1093 号,pp.27-55 (2007)

- [6] 「電力品質調整用パワーエレクトロニクスの適用動向」,電気学会技術報告,第 978 号, pp.16-30 (2004)

- [7] 「多重化電力変換器とその応用技術」,電気学会技術報告,第 556 号, pp.4-18 (1995)

- [8] 「パワーエレクトロニクス機器の制御技術」,電気学会技術報告,第 1084 号, pp.8-11 (2007)

- [9] 「半導体電力変換回路」,電気学会 半導体電力変換方式調査専門委員会,pp.46-50 (1987)

- [10] 長谷川泰三,別井孝司,大西修一,竹田正俊,瀬戸誠,村上昇太郎,光庵豊一:「系統安定 化用大容量自励式無効電力補償装置の開発」,電気学会論文誌 D, Vol.111-D, No.10, pp.845-854 (1991)

- [11] T.Fujii, H.Chisyaki, H.Teramoto, T.Sato, Y.Matsusita, Y.Shinki, S.Funahashi, N.Morishima: "Performance of the ±80MVA GCT STATCOM under Commercial Operation", 電気学会論文誌 D, Vol.128-D, No.4, pp.354-360 (2008)

- [12] 「自励式変換器の電力系統への適用技術」,電気学会技術報告,第 919 号, p.59 (2003)

- [13] 「電力系統の電圧·無効電力制御」,電気学会技術報告,第 743 号, p.56 (1999)

- [14] 「静止型無効電力補償装置の現状と動向」,電気学会技術報告,第 874 号,p.67 (2002)

- [15] 近藤洋介,藤田英明,赤木泰文: 「5 レベル変換器を用いた 6.6kV トランスレス STATCOM」, 電気学会論文誌 D, Vol.127-D, No.5, pp.493-500(2007)

- [16] 吉井剣, 井上重徳, 赤木泰文: 「6.6kV トランスレス・カスケード PWM STATCOM」, 電気学会論文誌 D, Vol.127-D, No.8, pp.781-788 (2007)

- [17] R.E.Bet, T.J.Summers: "Using a Cascaded H-Bridge STATCOM for Rebalancing Unbalanced Voltages", The 7th International Conference on Power Electronics, THE3-2 (2007)

- [18] 木村紀之,森實俊充,谷口勝則,舟木剛:「マルチレベル変換器を用いた BTB 直流連系」, 電気学会論文誌 B, Vol.120-B, No.12, pp.1706-1711 (2000)

- [19] 高崎昌洋、岡田有功、酒井洋満、江口吉雄、古関庄一郎、中村知治:「6.6kV-1MVA ループバスコントローラの開発」、平 18 年電気学会電力・エネルギー部門大会、376 (2006)

- [20] 「パワーエレクトロニクス回路」, 電気学会 半導体電力変換システム調査専門委員会, pp.52-53, p.142 (2000)

- [21] J.Arrillaga, Y.H.Liu, N.R.Watson: "Flexible Power Transmission", Wiley, pp. 141-167 (2007)

- [22] 李東昇,福田昭治,久保佑允,北野正之:「三相直列多重ハイブリッド変換器」,電気学会論 文誌 D, Vol.124-D, No.5, pp.503-509 (2004)

- [23] 大西徳生:「組み合わせ制御方式単相多重化 PWM インバータ」, 電気学会論文誌 D, Vol.115-D, No.1, pp. 63-69 (1995)

- [24] Madhav D.Manjrekar, Peter K.Steimer, Thomas A.Lipo: "Hybrid Multilevel Power Conversion System", IEEE Transactions on Industry Applications, Vol.36, No.3, pp. 834-841 (2000)

- [25] 羽田野伸彦,岸田行盛,山田正樹,岩田明彦: 「階調制御型瞬低補償装置における高速充電制御」,電気学会論文誌 D, Vol.125-D, No.12, pp. 1122-1128 (2005)

- [26] 羽田野伸彦: 「三相トランスレスDVRの一制御手法」,電気学会論文誌 D, Vol.128-D, No.9, pp. 1065-1074 (2008)

- [27] N.Hatano, T.Ise: "A configuration and control method of cascade H-bridge STATCOM", IEEE PES General Meeting 2008, Pittsburgh (USA), 08GM0551, July (2008)

- [28] 羽田野伸彦,谷口雄二,胡内勝彦:「瞬時電圧低下時における分散形電源用インバータの制御手法」,電気学会論文誌 D, Vol.128-D, No.1, pp.71-82 (2008)

- [29] 羽田野伸彦,山田正樹,岩田明彦,菊永敏之:「階調制御型瞬低補償装置における相間エネルギー流用制御」,電気学会論文誌 D, Vol.125-D, No.1, pp.38-45 (2005)

- [30] 羽田野伸彦, 岸田行盛, 岩田明彦: 「階調制御型変換器を用いた自励式無効電力補償装置」, 電気学会論文誌 D, Vol.127-D, No.8, pp.789-795 (2007)

- [31] 羽田野伸彦, 伊瀬敏史: 「チェーンリンク形マルチレベル変換器を用いたモジュラーPV システム」, 電気学会 半導体電力変換研究会, SPC-09-13, (2009)

# 第 2 章 ハイブリッド構成によるチェーンリンク 形マルチレベル変換器 (CLMC)

## 2.1 緒言

系統連系に用いられる大容量電力変換器は、複数台の変換器を多重接続して構成されることが一般的である。多重接続を用いると、個々の変換器のスイッチング周波数は低くても、制御性の向上、発生高調波の低減、機器効率向上を同時に実現できる[1]。代表的なマルチレベル方式の一つであるチェーンリンク形マルチレベル変換器(Chain Link type Multilevel Converter: CLMC)は、Hブリッジ形の単相変換器をセル(単位変換器)とし、これらを直列に接続して回路構成される。この方式は、セルの直列段数を増加させるだけで、出力波形のレベル数も増加できる。

しかし、CLMCでは、セルの直列段数を増加させると、スイッチング損失は低減できるが、導通損失が増加する。一方、電圧やスイッチング周波数が異なる複数のセルを組み合わせる、ハイブリッド変換器が提案されている。文献[2]-[4]では、GTO(Gate Turn-off Thyristor)変換器を1パルス、IGBT(Insulated Gate Bipolar Transistor)変換器を高周波PWMで動作させ、大容量化と高調波低減を同時に図る方式が報告されている。提案された回路にはAC側に多重変圧器が用いられているが、考え方をCLMCに適用すれば、直列段数を抑制しつつ高調波の低減を図ることが可能となる。

また、電圧が2倍ずつ異なるセルを組み合わせ、セルの直列段数に対して2のべき乗で出力電圧のレベル数の増加を図る方式も報告されている[5][6]。特に文献[5]では、3台以上のセルを組み合わせる方式について検討されている。この文献でも、提案された回路にはAC側に多重変圧器が用いられているが、考え方をCLMCに適用すれば、直列段数を抑制しつつ多レベル化を図ることが可能となる。以下では、この方式を、2進ハイブリッドCLMCと呼ぶことにする。

しかし、いずれの方式を適用しても、CLMCでは、セルごとにDC電源が分離される。このため、特定のDC電源に出力を集中させないよう、セルの出力分担制御が必要になる[7]-[11]。特に2進ハイブリッド方式については、文献[5][6]においても、このような制御は報告されていない。

以下本章では、CLMCの回路構成上の課題を述べ、その解決策としてハイブリッドCLMCの導入について検討し、基本的な回路構成と制御手法を示す。

2.2節では、CLMCにおける、セルの直列接続に伴う機器効率低下の可能性と、DC電源分離の必要性について述べる。

2.3節では、本研究で用いる2種類のハイブリッドCLMCについて述べる。まず、高周波PWM を混じえたハイブリッドCLMCと、その変調方法を示す。次に3直列で構成した2進ハイブリッド CLMCを導入することにより、レベル数と導通損失のトレードオフの解消を試みる。また、2進 方式におけるセルの出力分担制御を提案し、原理実証試験を行った結果を示す[12]。

2.4節では、本章の検討結果をまとめる。

#### 2.2 回路構成上の課題

#### 2.2.1 電力変換器の直列接続に伴う導通損失の増加

電力変換器を系統連系するにあたっては、高調波の低減が不可欠になる。CLMCでは、セルの 直列段数を増加させるだけで、出力波形のレベル数も増加できる。これにより、個々のセルのス イッチング周波数は低くとも、CLMC全体の等価的なスイッチング周波数は高くなるため、高調 波を低減でき、さらにスイッチング損失の低減も実現できる[1]。しかし、同時に導通損失も増加 する。以下では、CLMCの直列段数と機器損失の関係を試算し、傾向を把握する。

試算に用いるパワー半導体デバイスの諸元を、表2.1 に示す。これらは、現在市販されているデバイスのカタログデータ[13]-[15]を元に、DC電圧( $V_{CC}$ )と通電電流( $I_c$ )の比で按分して作成したものである。

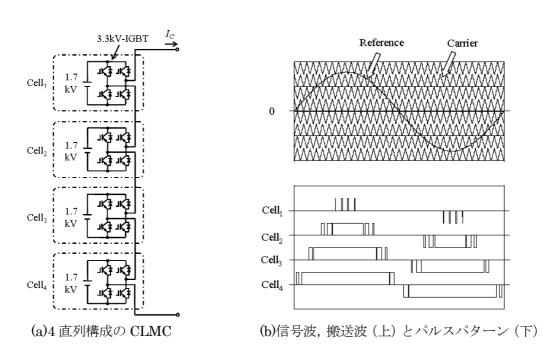

図2.1に、モデルとするCLMCの回路構成と各セルの動作を示す。半導体スイッチには 3.3kV-IGBTを用い、セルを4直列に接続した構成とする。セルのDC電圧は、いずれも1.7kVとする。このような構成のCLMCを、図2.1(b)のように、多段化された搬送波と信号波を比較することによってPWM動作させる。

| ,                       | H 15/1 1/14 9           | - 1 1311 /  | , , , , ,   |             |

|-------------------------|-------------------------|-------------|-------------|-------------|

|                         |                         | 6.5kV- IGBT | 3.3kV- IGBT | 1.7kV- IGBT |

| C-E Saturation Voltage  | $V_{CE(sat)}[V]$        | 5.7 *1      | 3.5 *1      | 2.2 *1      |

| Turn-on Switching Loss  | $E_{on}$ [J/P]          | 3.4 *2      | 0.77 *3     | 0.13 *4     |

| Turn-off Switching Loss | $E_{off}[\mathrm{J/P}]$ | 2.7 *2      | 0.90 *3     | 0.38 *4     |

| Reverse Recovery Loss   | $E_{rr}$ [J/P]          | 1.9 *2      | 0.77 *3     | 0.19 *4     |

表 2.1 試算に用いるパワー半導体デバイスの諸元

図 2.1 回路モデルと各セルの動作

4台のセルCell<sub>1</sub>, Cell<sub>2</sub>, Cell<sub>3</sub>, Cell<sub>4</sub>は,信号波(Reference,正弦波)と,搬送波(Carrier,三角波)の大小関係により,それぞれ図2.1(b)下図のパルスパターンで動作する。CLMCの出力電流 $I_c$ は,8個のIGBTまたは逆並列ダイオードを常時通流するため,仮に $I_c$ =600Aであったすると,導通損失 $I_{CD}$ は,次のように計算できる。ただし,概算であり,逆並列ダイオードの順方向電圧降下は,IGBTのコレクターエミッタ間飽和電圧 $I_{CE(sat)}$ に等しいとしている。

$$L_{CD} = V_{CE(sat)} \times I_c \times 8 = 3.5 \times 600 \times 8 = 16800[W]$$

(2.1)

また、搬送波のほぼ1サイクルごとに、いずれか1組の上下アームの半導体スイッチがオン・オフ動作を行い、 $Cell_1$ 、 $Cell_2$ 、 $Cell_3$ 、 $Cell_4$ のいずれか1台の出力電圧がパルス状に変化する。したがって、CLMC全体としてのスイッチング周波数はキャリア周波数 $f_c$ とほぼ一致し、スイッチング損失 $L_{SW}$ は、概ね次のように計算できる。ただし、 $E_{on}$ はターンオンスイッチング損失, $E_{of}$ はターンオフスイッチング損失, $E_{of}$ は逆回復損失である。

$$L_{SW} = (E_{on} + E_{off} + E_{rr}) \times f_C = (0.77 + 0.90 + 0.77) \times f_C = 2.44 \times f_C[W]$$

(2.2)

(2.1)式と(2.2)式より、モデルとした CLMC の損失  $L_{CLMC}$ は、次のように表される。

$$L_{CLMC} = L_{SW} + L_{CD} = 2.44 \times f_C + 16800[W]$$

(2.3)

次に、この 4 直列構成の CLMC-4S と、1.7kV-IGBT と 0.85kV の DC 電源を用いたセルを 8 直列で構成した CLMC-8S と、6.5kV-IGBT と 3.4kV の DC 電源を用いたセルを 2 直列で構成した CLMC-2S について、同様の方法により、キャリア周波数と損失の関係を試算する。図 2.2 に、結果を示す。

キャリア周波数がおよそ 500Hz 以下では、導通損失が支配的であり、CLMC-2S が有利となった。次に、キャリア周波数の増加とともにスイッチング損失も増加し、 $500\sim2500$ Hz の間では、CLMC-4S が有利となった。そして、2500Hz を超えると、CLMC-8S が有利となった。

このように、出力電圧のレベル数を増加しても、反って損失が増加する場合がある。したがって、セルの直列段数を適度にとどめ、スイッチング周波数を上げて発生高調波を低減する必要が生じる。

図 2.2 キャリア周波数と損失の関係

#### 2.2.2 DC 電源の分離

系統連系用変換器は、系統電圧や出力電流の変化に追従する必要がある。これに伴い、CLMCにおいては、セルごとに動作が異なる場合もある。しかし、CLMCでは、DC電源の正極端子と負極端子に短絡(PN短絡)が生じるため、DC電源を分離しなければならず、DC電源の過負荷や充電エネルギーの偏った消耗などが生じる可能性がある。

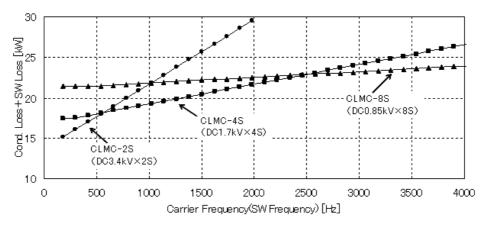

図2.3(a)は、標準的な直列多重化方式である。図では、"×"を記したIGBTをオフ状態、他のIGBTをオン状態としている。この回路構成では、AC側で多重変圧器により絶縁されているため、半導体スイッチの開閉状態に関わらず、PN短絡は発生しない。したがって、1台のDC電源を共有することができる。また、図2.3(b)は、直流送電システムへの適用を目的に、文献[7][8]で報告された方式である。DCコンデンサの電圧分担を制御する必要があるが、AC側の多重変圧器により、やはりPN短絡は発生しない。

ところが、AC側の多重変圧器を省略するCLMCでは、例えば図2.3(c)に示す半導体スイッチの開閉状態においては、 $Cell_1$ と $Cell_4$ のDC電源にPN短絡が生じる。したがって、図2.1(a)に示すように、セルごとにDC電源を分離しなければならない。

このとき例えば、図2.1(b)に示したパルスパターンで動作させると、セルの出力は、 $Cell_1$ 、 $Cell_2$ 、 $Cell_3$ 、 $Cell_4$ の順に大きくなり、DC電源の過負荷や充電エネルギーの偏った消耗などが生じる。このような理由により、CLMCにおいては、セルの出力分担制御が必要になる。

# 2.3 ハイブリッド変換器の導入

CLMCでは、全てのセルに同様の動作を割り当てても良いが、個々のセルの動作には制約がなく、全く異なる動作を割り当てることも可能である。本論文では、電圧やスイッチング周波数が明らかに異なるセルを組み合わせる方式のCLMCを総称して、ハイブリッドCLMCと呼ぶ。ハイブリッドCLMCでは、様々な回路構成や制御が可能となるが、以下では、本研究で用いる2種類の方式を示す。

図2.3 DC電源分離の必要性

#### 2.3.1 高周波 PWM を混じえたハイブリッド CLMC

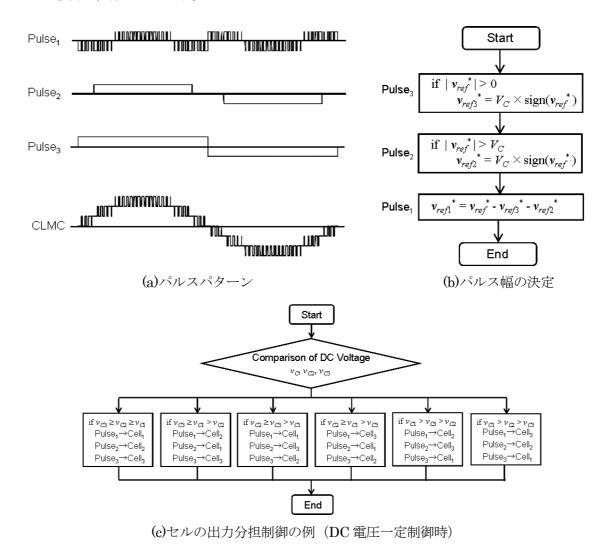

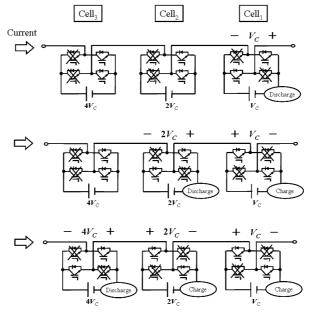

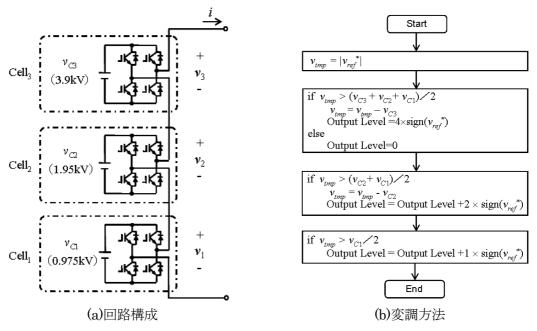

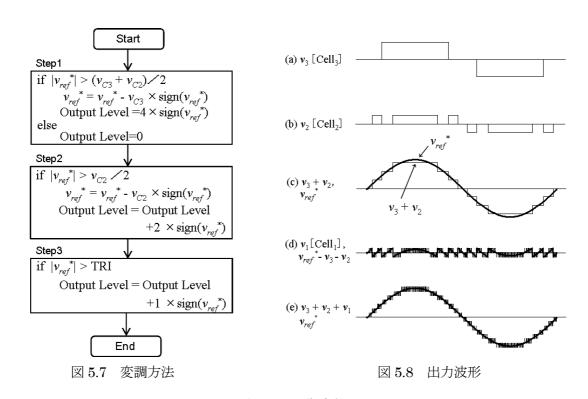

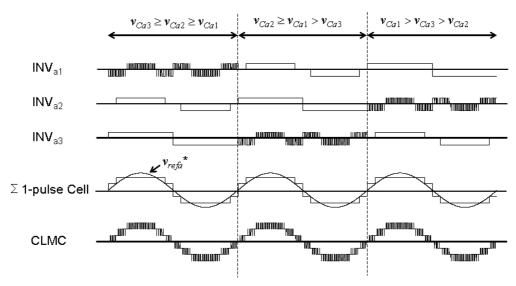

CLMCでは、一部のセルに高周波PWMを行わせることにより、直列段数を無理に増加させることなく、発生高調波を低減することができる。3台のセル $Cell_1$ 、 $Cell_2$ 、 $Cell_3$ を直列接続した構成を例にとり、本研究で用いる変調方法を図2.4に示す。

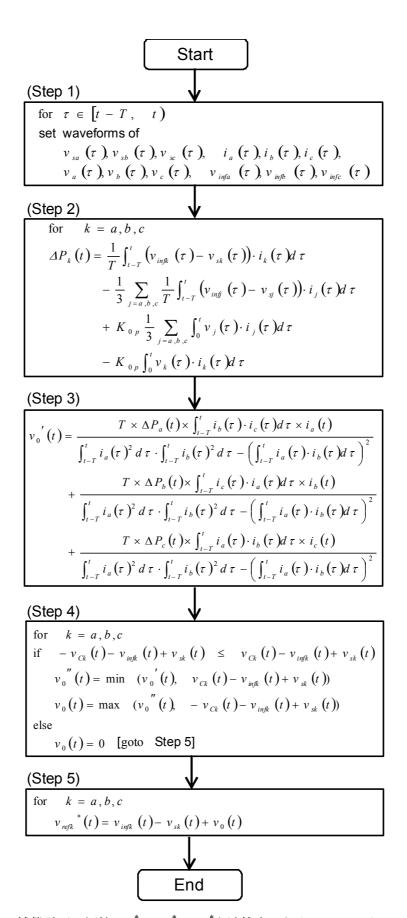

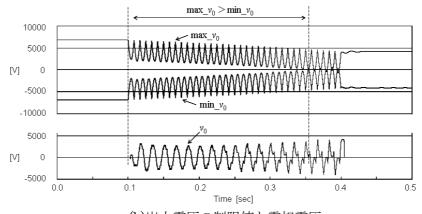

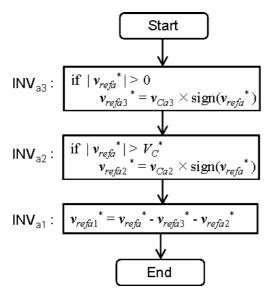

Pulse<sub>1</sub>, Pulse<sub>2</sub>, Pulse<sub>3</sub>は、いずれかのセルに割り当てるパルスパターンである。これらのパルスは、図2.4(b)に示した演算フローにより決定する。高周波動作を行うPulse<sub>1</sub>により、低次高調波が低減される。一方、Pulse<sub>2</sub>とPulse<sub>3</sub>では、それらによる出力電圧の合計と出力電圧指令値 $v_{ref}^*$ との誤差がDC電圧の基準値 $V_c$ 以下になる範囲で、1パルス動作を行う。

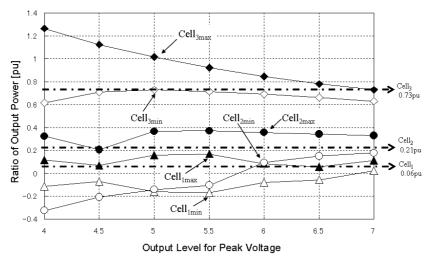

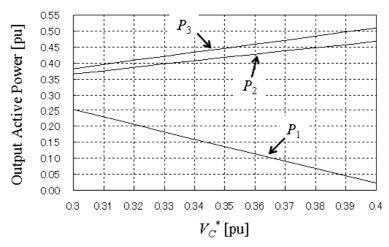

図 2.4(c)に、DC 電圧一定制御における、セルの出力分担制御の例を示す。各セルの DC 電圧が CLMC の出力する基本波成分の 1/3pu 程度以上であり、かつ CLMC は基本波有効電流を出力しているとすると、出力される有効電力は、Pulse3 > Pulse2 > Pulse1 の順に高くなる。したがって、セルの DC 電圧  $v_{C1}$ ,  $v_{C2}$ ,  $v_{C3}$  の高い順に Pulse3、Pulse2、Pulse1を割り当てることにより、 $v_{C1}$ ,  $v_{C2}$ ,  $v_{C3}$  と平均値の誤差が補正される。なお、ここに示したセルの出力分担制御に関する定量的な検討は、第 6 章に示す。

図 2.4 高周波ハイブリッド CLMC の変調方法

#### 2.3.2 2 進ハイブリッド CLMC

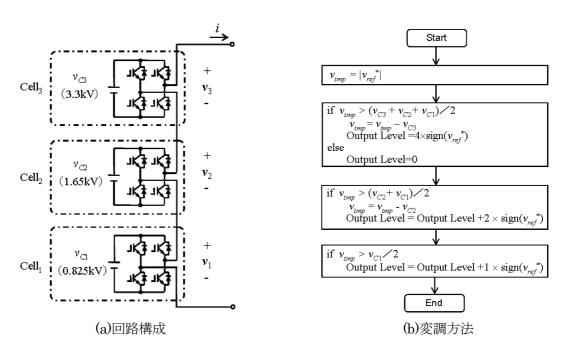

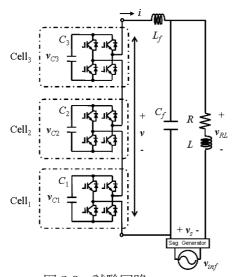

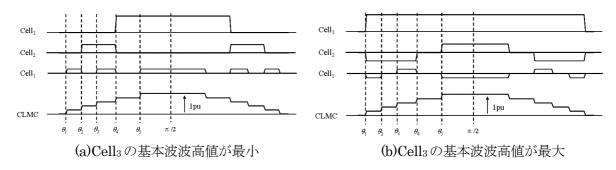

次に、電圧が2倍ずつの関係にあるセルを組み合わせる2進ハイブリッドCLMCを導入し、多レベル化と導通損失のトレードオフの解消を試みる。パワー半導体デバイスの候補には、定格電圧が6.5kV、4.5kV、3.3kV、2.5kV、1.7kVのIGBTなどがある[1]。まず、導通損失と部品点数の抑制を考え、1台のセルには、定格電圧が最大である6.5kV-IGBTを用いる。これに、3.3kV-IGBTを用いたセルを組み合わせると、文献[6]に示されたものと同様に、7レベルの出力電圧が得られる。そしてさらに、1.7kV-IGBTを用いたセルを加えて、図2.5(a)に示すように、3直列-2進ハイブリッドCLMCを構成する。

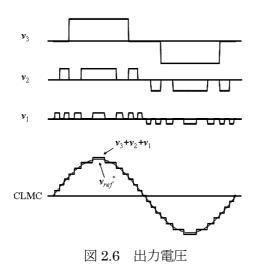

この CLMC を、図 2.5(b)に示す変調方法を用いて制御したときの動作波形を図 2.6 に示す。図 2.5(b)中の変数"Output Level"は-7~+7 の値をとり、CLMC の出力電圧はこれに対応して 15 段階の出力レベルを持つ波形となる。このときの各セルの動作は、基本周波数あたりで、 $Cell_3$  が 1

図 2.5 3 直列-2 進ハイブリッド CLMC の回路構成と変調方法

図 2.7 出力電圧の高調波含有率

表 2.2 各種構成の CLMC の比較

|                                                             | Output Levels | Sum of V <sub>CE(sat)</sub> *1 |

|-------------------------------------------------------------|---------------|--------------------------------|

| 3S-Binary-Hybrid CLMC (Fig. 2.5)                            | 15            | 22.8                           |

| CLMC-8S $(1.7\text{kV-IGBT Cell} \times 8 \text{ Series})$  | 17            | 35.2                           |

| CLMC-4S $(3.3 \text{kV-IGBT Cell} \times 4 \text{ Series})$ | 9             | 28.0                           |

| CLMC-2S $(6.5 \text{kV-IGBT Cell} \times 2 \text{ Series})$ | 5             | 22.8                           |

\*1:表2.1に示すデータを用い、1台のセルあたり2個の半導体デバイスを通流するものとして計算している

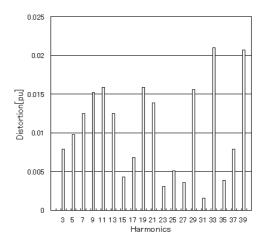

パルス、 $Cell_2$ が3パルス、 $Cell_1$ が7パルスである。図2.7に、出力電圧 $v_1+v_2+v_3$ の高調波含有率を示す。系統電圧歪率の抑制対象とされる40次以下の高調波成分によるTHD(Total Harmonic Distortion)は5%程度で、負荷供給電圧としてそのまま用いることも可能である[16][17]。

他の構成のCLMCと比較した結果を、表2.2に示す。3直列-2進ハイブリッドCLMCのレベル数は、CLMC-8Sに次ぐ、15レベルとなる。また、電流経路に存在するパワー半導体デバイスのコレクターエミッタ間飽和電圧 $V_{CE(sat)}$ の合計は、CLMC-8Sより30%以上低減され、6.5kV-IGBTを用いたセルを2直列で構成したCLMC-2Sと等しくなる。これにより、導通損失が抑制できる。

レベル数の少ないCLMC-2Sでは、主に搬送波周波数付近の高調波成分の影響により、THDが20%程度となる。したがって、40次以下の高調波成分によるTHDにおいて、3直列-2進ハイブリッドCLMCと同程度の出力電圧の品質を実現するためには、数kHz程度のスイッチング周波数が必要となり、スイッチング損失の増加につながる。

このように、2進ハイブリッドCLMCは、導通損失を抑制しつつも、多レベル化による高品質な電力供給が可能となる。

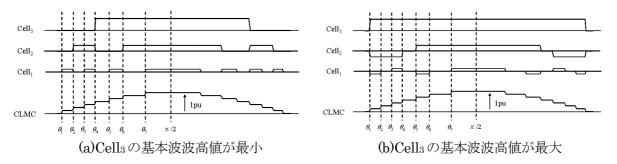

#### 2.3.3 2 進構成におけるセルの出力分担制御

CLMCでは、セルごとに独立した動作を行わせることが可能である。そして、同じ電圧レベルを出力する場合にも、複数の動作パターンが存在する[18]。これを利用して、2進ハイブリッド CLMCにおけるセルの出力分担の制御を試みる。

図2.8に、例を示す。Cell<sub>1</sub>、Cell<sub>2</sub>、Cell<sub>3</sub>のDC電圧を、 $V_C$ 、 $2V_C$ 、 $4V_C$ とする。レベル 1(電圧  $V_C$ )を出力するとき、CLMCは、" $V_C$ "、" $2V_C$ - $V_C$ "、" $4V_C$ - $2V_C$ - $V_C$ "という三種類の動作パターンを選択できる。動作パターン" $V_C$ "では、Cell<sub>1</sub>が放電する。動作パターン" $2V_C$ - $V_C$ "では、Cell<sub>2</sub>が放電し、Cell<sub>3</sub>が放電し、Cell<sub>2</sub>が放電し、Cell<sub>2</sub>が放電し、Cell<sub>3</sub>が放電し、Cell<sub>2</sub>とCell<sub>1</sub>が充電される。このように、動作パターンによって充放電されるセルが異なることから、個々のDC電源の充放電量を監視し、動作パターンを使い分けることにより、セルの出力分担を制御できる。

3直列-2進ハイブリッドCLMCの全ての動作パターンを、表2.3に示す。CLMCの出力電圧(3台のセルの出力電圧の合計)と出力電流が同極性である場合、表中の"1"は、該当するセルより出力電流と同極性の電圧が出力され、DC電源が放電することを示す。"-1"は、逆極性の電圧が出力され、DC電源が充電されることを示す。出力電圧と電流の極性が異なる場合は、表中の"1"と"-1"に対する充放電の関係が反転する。

図 2.8 レベル 1 (電圧  $V_C$ ) 出力時にとりうる動作パターン

表 2.3 3 直列-2 進ハイブリッド CLMC の動作パターン (1: 放電, -1: 充電)

| Output Level                              | 1 |    |    | 2 |    | 3 |    | 4  | 5 |   | 6  | 7 |   |

|-------------------------------------------|---|----|----|---|----|---|----|----|---|---|----|---|---|

| $\operatorname{Cell}_1(V_{\mathcal{O}})$  | 1 | -1 | -1 |   |    | 1 | -1 | 1  |   | 1 | -1 |   | 1 |

| $\operatorname{Cell}_2(2V_{\mathcal{C}})$ |   | 1  | -1 | 1 | -1 | 1 |    | -1 |   |   | 1  | 1 | 1 |

| Cell <sub>3</sub> (4V <sub>C</sub> )      |   |    | 1  |   | 1  |   | 1  | 1  | 1 | 1 | 1  | 1 | 1 |

なお、セルの出力分担は任意の量を制御できるわけではない。表2.3において、複数の動作パターンは、出力レベルが1、2、3、5についてのみ存在し、制御できる範囲は、これらのレベルを出力している間にCLMCを通流する電流に依存する。この制約を考慮した上でDC電源を構成する方法に関しては、第4章で検討を行う。

#### 2.3.4 2 進構成におけるセルの出力分担制御に関する原理実証試験[12]

コンデンサを DC 電源とする 2 進ハイブリッド CLMC を用いた直列形瞬時電圧低下補償装置 (Dynamic Voltage Restorer: DVR) において、AC 側を通流する負荷電流を用いて DC 電圧の 比率を基準値 1: 2:4 に維持しながらコンデンサを充電する試験により、セルの出力分担を制御できることを実証する。

試験回路を図 2.9、回路定数を表 2.4 に示す。本試験では、 $Cell_1$ 、 $Cell_2$ 、 $Cell_3$ を 3 直列に接続して、CLMC を構成する。電源  $v_{inf}$ は、定格電圧 187V(波高値 265V)、基本周波数 60Hz の交流電源である。"Sag Generator"は、常時は  $v_{inf}$  より入力される電圧を  $v_s$  として出力するが、外部指令により 80%の瞬時電圧低下を発生できる。定格電流  $I_{AC}$  は、それぞれのセルに用いた IGBT の定格電流が 300A であったため、電流波高値に約 2 倍の余裕を見込んで、実効値で 100A とする。DC 電源には、予め充電されたコンデンサ  $C_1$ 、 $C_2$ 、 $C_3$  を用いる。セルの DC 電圧  $v_{C1}$ 、 $v_{C2}$ 、

$v_{\rm C3}$  は,1:2:4 の比率を基準とする。初期値  $v_{\rm C1}^*$ , $v_{\rm C2}^*$ , $v_{\rm C2}^*$ , $v_{\rm C3}^*$  は,それらの合計が定格電圧の波高値  $265{\rm V}$  よりも若干高めとなるよう, $45{\rm V}$ , $90{\rm V}$ , $180{\rm V}$  とする。 $C_1$ , $C_2$ , $C_3$  の容量は,ゼロ充電状態から初期 (フル) 状態までの充電を数秒程度で完了するよう, $66{\rm mF}$ , $136{\rm mF}$ , $330{\rm mF}$  とする。試験用負荷には, $2\Omega$  の抵抗 R と  $2.7{\rm mH}$  のリアクトル L を直列に接続して構成する。この負荷に定格電圧を印加すると,定格  $I_{AC}$  の約 80% の電流が通流する。また,負荷力率は 0.9 である。なお,リアクトル  $L_f$  とコンデンサ  $C_f$  からなる高調波フィルタは,負荷電圧の測定において高周波成分を除去するために設置するものである。

制御ブロック図は,図 2.10 に示す通りである。試験開始の時点では,制御信号  $S_1$ は 0 に設定されている。DSP は,電源電圧  $v_{inf}$ ,"Sag Generator"の出力電圧  $v_s$ ,DC 電圧  $v_{C1}$ , $v_{C2}$ , $v_{C3}$  を,AD 変換器を介して監視している。ここで, $S_1$ を 1 に設定すると, $v_s$ は  $v_{inf}$ の 0.2pu となる。DSP は, $v_{inf}$ と  $v_s$ の差と図 2.5(b)に示した変調方法により出力レベルを決定し,さらに,表 2.3 に示した動作パターンの中から, $v_{C1}$ , $v_{C2}$ , $v_{C3}$  を 1:2:4 の比率で規格化した値が最も大きいコンデンサが放電するよう動作パターンを選択する。DSP の出力チャネルの制約から,後段には FPGA を置き,動作パターンをデコードし,さらに出力するタイミングを整え,各 IGBT を駆動する。次に, $S_1$ を 2 に設定すると, $v_s$  は  $v_{inf}$  と一致する。一方,DSP は, $v_s$  に対して位相差が  $180^\circ$ で振幅 0.05pu の電圧を,CLMC の出力電圧指令値として設定する。この電圧指令値と出力電流 i から定

表 2.4 回路定数

| •               |                                                             | . —               |

|-----------------|-------------------------------------------------------------|-------------------|

| Voltage Source  | $v_{inf}$                                                   | AC187V, 60Hz      |

| Rated Current   | $I_{AC}$                                                    | 100A              |

| Capacitance,    | $C_3$ , $v_{C3}^{*}$                                        | 66mF, 180V        |

| Initial Voltage | $C_3, \ {v_{C3}}^*$ $C_2, \ {v_{C2}}^*$ $C_1, \ {v_{C1}}^*$ | 136mF, 90V        |

|                 | $C_1$ , $v_{Cl}^*$                                          | 330mF, 45V        |

| Load            | R                                                           | 2.0Ω              |

|                 | L                                                           | $2.7 \mathrm{mH}$ |

| Filter          | $L_f$                                                       | 0.3mH             |

|                 | $C_f$                                                       | $200\mu$ F        |

図 2.9 試験回路

図 2.10 制御ブロック図

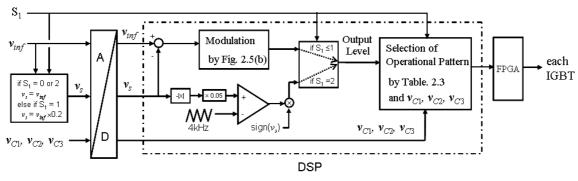

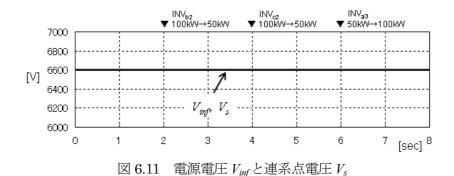

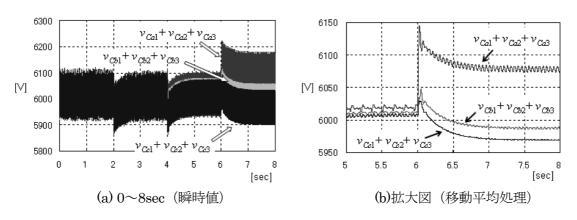

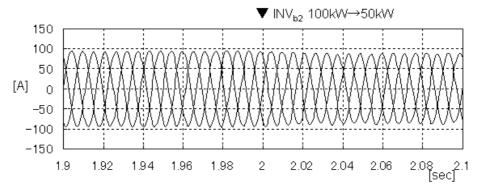

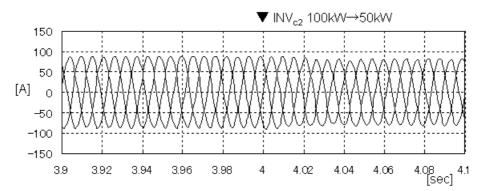

まるエネルギーは平均的に負となり、これが CLMC に注入され、コンデンサが再充電される。 なお、振幅 0.05pu に相当する基本波を精度良く出力させるため、CLMC は、図 2.11 に示すように、 $1 \ge 0$  の 2 つのレベルを用い、キャリア周波数 4kHz で高周波 PWM を行うよう動作させる。 ここで、レベル 1 出力時には、図 2.8 に示したいずれかの動作パターンを用い、DC 電圧  $v_{CI}$ ,  $v_{CZ}$

図 2.11 充電時の動作

図 2.12 原理実証試験の結果

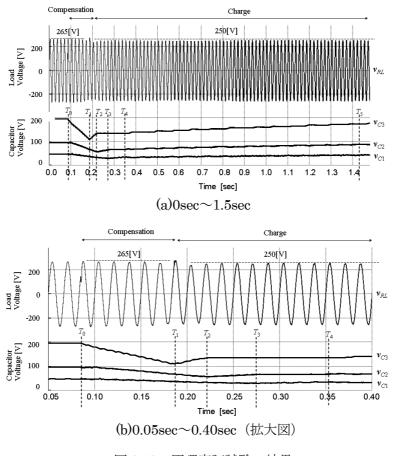

$v_{C3}$ を 1:2:4の比率で規格化した値が最も小さいコンデンサを充電するよう、パターンを選択する。 図 2.12 に、試験結果を示す。時刻 0 から  $T_0$ までは、前述の  $S_1$ =0 の状態に相当し、 $v_s$ の波高値は定格である 265V となり、CLMC は 0 レベルを出力し、負荷には  $v_s$  が直接印加されている。次に、時刻  $T_0$  から  $T_1$  までは、前述の  $S_1$ =1 の状態に相当し、 $v_s$ は 53V に低下し、CLMC は、DVR として、この電圧低下を補償する。この結果、一旦コンデンサ  $C_1$ 、 $C_2$ 、 $C_3$  が放電し、時刻  $T_1$  では、DC 電圧  $v_{C1}$ 、 $v_{C2}$ 、 $v_{C3}$ は、それぞれ 33V、65V、110V まで低下した。次に、時刻  $T_1$ 以降では、前述の  $S_1$ =2 の状態に相当し、 $v_s$ を 265V に戻すと供に、 $v_s$ に対して位相差が 180°で振幅 0.05pu の電圧を、CLMC より出力する。この結果、時刻  $T_5$ では、 $v_{C1}$ 、 $v_{C2}$ 、 $v_{C3}$ は、それぞれ 43V、88V、

以上のように、本試験では、2 進ハイブリッド CLMC において、セルごとに出力を制御できることを検証した。

#### 2.4 結言

174V と、ほぼ初期状態まで再充電された。

本章では、CLMCの回路構成上の課題を示し、その解決策としてのハイブリッドCLMCの導入 について検討した。

まず、CLMCにおけるセルの直列段数と、導通損失およびスイッチング損失の関係について評価し、レベル数を増加できても、反って損失が増加する場合があることを示した。また、DC電源をセルごとに分離しなければならない理由と、それに伴いセルの出力分担制御が必要になることを示した。

次に、本研究で用いる方式として、セルの直列段数を抑制するために高周波 PWM を混じえた ハイブリッド CLMC と、さらに、電圧が 2 倍ずつ異なるセルを組み合わせ、多レベル化を容易 とする 2 進ハイブリッド CLMC について、基本的な回路構成と制御手法を示した。

# 参考文献

- [1] 「パワーエレクトロニクス機器の制御技術」, 電気学会技術報告, 第 1084 号, pp.6-11 (2007)

- [2] 李東昇,福田昭治,久保佑允,北野正之:「三相直列多重ハイブリッド変換器」,電気学会論 文誌 D, Vol.124-D, No.5, pp.503-509 (2004)

- [3] 李東昇,福田昭治,久保佑允:「直列三多重ハイブリッド変換器」,電気学会論文誌 D, Vol.124-D, No.9, pp.924-929 (2004)

- [4] 李東昇,福田昭治:「直列多重ハイブリッド変換器の STATCOM への応用」,電気学会論文誌 D, Vol.125-D, No.2, pp.179-184 (2005)

- [5] 大西徳生:「組み合わせ制御方式単相多重化PWMインバータ」,電気学会論文誌 D, Vol.115-D, No.1, pp. 63-69 (1995)

- [6] Madhav D.Manjrekar, Peter K.Steimer, Thomas A.Lipo: "Hybrid Multilevel Power Conversion System", IEEE Transactions on Industry Applications, Vol.36, No.3, pp. 834-841 (2000)

- [7] 杉本重幸, S.C.Verma, 小川重明, 小西博雄: 「HVDC/BTB システムへのチェインリンクコンバータの適用検討」, 電気学会 電力技術・電力系統技術合同研究会, PE-01-23, PSE-01-17 (2001)

- [8] 小西博雄, 杉本重幸, S.C.Verma: 「チェインリンクコンバータ適用 HVDC/BTB システムの試作モデルによる動作検証」,電気学会 電力技術・電力系統技術合同研究会, PE-03-31, PSE-03-42 (2003)

- [9] Fang Z.Peng, J.S.Lai, J.W. McKeever, V.Coevering: "A multilevel voltage-source inverter with separate dc sources for static var generation", IEEE Transactions on Industry Applications., Vol. 32, No. 5, pp. 1130-1138 (1996)

- [10] 吉井剣, 井上重徳, 赤木泰文: 「6.6kV トランスレス・カスケード PWM STATCOM」, 電気学会論文誌 D, Vol.127-D, No.8, pp.781-788 (2007)

- [11] J. Arrillaga, Y. H. Liu, N. R. Watson: "Flexible Power Transmission", Wiley, pp.141-167 (2007)

- [12] 羽田野伸彦,岸田行盛,山田正樹,岩田明彦:「階調制御型瞬低補償装置における高速充電制御」,電気学会論文誌 D, Vol.125-D, No.12, pp. 1122-1128 (2005)

- [13] 日立製作所 半導体データシート, MBN600H65E, Spec.No.IGBT-SP-06003 R3

- [14] 日立製作所 半導体データシート, MBN1200H33E, Spec.No.IGBT-SP-06025 R1

- [15] 日立製作所 半導体データシート, MBN1200E17E, Spec.No.IGBT-SP-06038 P1

- [16] 「配電系統の高調波障害防止対策」,電気協同研究,第 37 巻,第 3 号,pp.129-139 (1981)

- [17] 「電力系統における高調波とその対策」,電気協同研究,第46号,第2号,pp.87-90 (1990)

- [18] 山田正樹, 鈴木昭弘, 岩田明彦, 菊永敏之, 吉安一, 山本和生, 羽田野伸彦: 「階調制御型 瞬低補償装置におけるエネルギー流用制御」, 電気学会論文誌 D, Vol.125-D, No.2, pp. 126-132 (2005)

# 第3章 三相系統における電力変換器の制御

### 3.1 緒言

三相系統では、必ずしも系統電圧が三相平衡であるとは限らない。定常時においても、系統定数の不揃いや単相負荷の存在により、僅かながらも系統電圧に不平衡が発生する。また、落雷等により一相または二相事故が発生すれば、系統電圧の振幅と位相が急変し、大幅な不平衡が生じる[1][2]。これらの結果より、三相系統に連系される電力変換器には、三相出力の不平衡が容易に発生する[3]-[5]。

三相ブリッジ形の電力変換器であれば、AC 出力に不平衡が生じても、DC 電源には問題は生じない。しかし、チェーンリンク形マルチレベル変換器(Chain Link type Multilevel Converter: CLMC)では、DC 電源が個々のセル(単位変換器)に分離して設置される。このため、出力が特定のセルに集中すれば、DC 電源の過負荷、充電エネルギーの偏った消耗などの不具合が起こりうる。したがって、CLMC を用いた系統連系用変換器においては、三相不平衡への対策を見出すことが、重要な課題となる。

以下本章では、CLMC を三相系統に適用するための基本的な制御手法として、系統電圧や出力 電流に不平衡が存在する場合にも、前述の不具合が生じないよう三相出力を等しく制御するため の手法を検討する。

- 3.2 節では、電力系統の不平衡が、三相出力に及ぼす影響について述べる。

- 3.3 節では、出力電圧の零相成分により、三相出力を制御する理論を示す[6]。また、この零相電圧制御の適用限界について述べる。

- 3.4 節では、出力電流の逆相成分により、三相出力を制御する理論を示す[7]。また、この逆相 電流制御により生じる制約について述べる。

- 3.5 節では、これらの理論の実現に不可欠な技術として、系統事故などにより系統電圧に大幅な不平衡が存在する場合にも、過電流を生じることなく、電力変換器の出力電流を指令値通りに制御するための手法を示す[8]。

- 3.6 節では、本章の検討結果をまとめる。

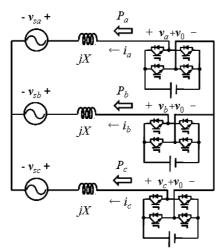

### 3.2 系統不平衡の影響

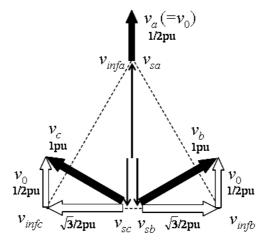

図 3.1 に、検討モデルを示す。3 台の単相変換器を Y 結線して三相 3 線式の電力変換器を構成し、リアクトルを介して三相電源  $v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$  に接続する。DC 電源は、個々のセルに分離して設置しなければならない。これは、電力変換器の半導体スイッチの開閉状況によって、正極と負極が短絡する場合があるためである。なお、このモデルにおいては、三相変換器の出力電圧の内、正相成分と逆相成分の和を  $v_a$ ,  $v_b$ ,  $v_c$ , 零相成分を  $v_0$  と表記する。

ここで、 $v_0$ が 0 であるとし、 $v_a$ 、 $v_b$ 、 $v_c$ は、(3.1)式のように表されたとする。右辺第一項は正相成分、第二項は逆相成分である。 $\varphi_m$ は、正相成分と逆相成分の、a 相を基準とした位相差である。

図 3.1 検討モデル

$$\begin{bmatrix} v_{a} \\ v_{b} \\ v_{c} \end{bmatrix} = \sqrt{\frac{2}{3}} V_{p} \begin{bmatrix} \cos(\omega t) \\ \cos(\omega t - \frac{2\pi}{3}) \\ \cos(\omega t + \frac{2\pi}{3}) \end{bmatrix} + \sqrt{\frac{2}{3}} V_{n} \begin{bmatrix} \cos(\omega t + \varphi_{vn}) \\ \cos(\omega t + \varphi_{vn} + \frac{2\pi}{3}) \\ \cos(\omega t + \varphi_{vn} - \frac{2\pi}{3}) \end{bmatrix}$$

(3.1)

また、電力変換器の出力電流  $i_a$ ,  $i_b$ ,  $i_c$ は、(3.2)式で表されたとする。 $\varphi_{ip}$  と $\varphi_{in}$ は、出力電圧の正相成分との、 $\alpha$  相を基準とした位相差である。

$$\begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix} = \sqrt{\frac{2}{3}} I_{p} \begin{bmatrix} \cos(\omega t + \varphi_{ip}) \\ \cos(\omega t + \varphi_{ip} - \frac{2\pi}{3}) \\ \cos(\omega t + \varphi_{ip} + \frac{2\pi}{3}) \end{bmatrix} + \sqrt{\frac{2}{3}} I_{n} \begin{bmatrix} \cos(\omega t + \varphi_{in}) \\ \cos(\omega t + \varphi_{in} + \frac{2\pi}{3}) \\ \cos(\omega t + \varphi_{ip} - \frac{2\pi}{3}) \end{bmatrix}$$

(3.2)

(3.1)式と(3.2)式より、電力変換器の a 相, b 相, c 相から出力される平均有効電力  $P_a$ ,  $P_b$ ,  $P_c$  は、次のように計算される。

$$\begin{bmatrix}

P_{a} \\

P_{b} \\

P_{c}

\end{bmatrix} = \frac{1}{3} V_{p} I_{p} \begin{bmatrix}

\cos \varphi_{ip} \\

\cos \varphi_{ip} \\

\cos \varphi_{ip}

\end{bmatrix} + \frac{1}{3} V_{n} I_{n} \begin{bmatrix}

\cos(\varphi_{in} - \varphi_{vn}) \\

\cos(\varphi_{in} - \varphi_{vn}) \\

\cos(\varphi_{in} - \varphi_{vn})

\end{bmatrix} + \frac{1}{3} V_{p} I_{n} \begin{bmatrix}

\cos(\varphi_{in} - \frac{2\pi}{3}) \\

\cos(\varphi_{in} - \frac{2\pi}{3}) \\

\cos(\varphi_{in} + \frac{2\pi}{3})

\end{bmatrix} + \frac{1}{3} V_{n} I_{p} \begin{bmatrix}

\cos(\varphi_{ip} - \varphi_{vn}) \\

\cos(\varphi_{ip} - \varphi_{vn} + \frac{2\pi}{3}) \\

\cos(\varphi_{ip} - \varphi_{vn} - \frac{2\pi}{3})

\end{bmatrix} ..... (3.3)$$

右辺第一項は、正相成分の積から生成され、三相とも等しい値となる。第二項は、逆相成分の積から生成されるもので、やはり三相とも等しい値となる。一方、第三項と第四項は、正相成分と逆相成分の積から生成されるものであり、各相で値が異なる。したがって、単相変換器に基づく三相変換器では、特定の相に出力が偏り、DC 電源の過負荷、充電エネルギーの偏った消耗などの不具合が起こりうる。

#### 3.3 零相電圧による三相出力制御

### 3.3.1 基本原理

系統連系される三相 3 線式の電力変換器では、出力電圧の零相成分は出力電流に影響を及ぼさないため、その決定に自由度が発生する[9]。例えば、図 3.1 のモデルでは、出力電流  $i_a$ 、 $i_b$ 、 $i_c$ は次式より定まり、零相電圧  $v_0$ とは関係を持たない。なお、太字はフェーザ表示であり、以下でも同様とする。

$$\mathbf{v}_{sa} + jX\mathbf{i}_{a} - \mathbf{v}_{a} - (\mathbf{v}_{sb} + jX\mathbf{i}_{b} - \mathbf{v}_{b}) = 0

\mathbf{v}_{sb} + jX\mathbf{i}_{b} - \mathbf{v}_{b} - (\mathbf{v}_{sc} + jX\mathbf{i}_{c} - \mathbf{v}_{c}) = 0

\mathbf{i}_{a} + \mathbf{i}_{b} + \mathbf{i}_{c} = 0$$

(3.4)

そして,電力変換器から三相電源  $v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$  に供給される電力は  $i_a$ ,  $i_b$ ,  $i_c$  により定まるため, $v_0$  は任意に設定することが可能となる。本節では,この自由度を活用して,零相電圧による電力変換器の三相出力制御を試みる[6][10]。

このとき、電力変換器の有効出力 $P_a$ 、 $P_b$ 、 $P_c$ は、次式より定まる。ここで、演算"・"は、フェーザを複素ベクトルとして取扱った場合の内積である。

$$P_{a} = (\mathbf{v}_{a} + \mathbf{v}_{0}) \cdot \mathbf{i}_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} + \mathbf{v}_{0} \cdot \mathbf{i}_{a}$$

$$P_{b} = (\mathbf{v}_{b} + \mathbf{v}_{0}) \cdot \mathbf{i}_{b} = \mathbf{v}_{b} \cdot \mathbf{i}_{b} + \mathbf{v}_{0} \cdot \mathbf{i}_{b}$$

$$P_{c} = (\mathbf{v}_{c} + \mathbf{v}_{0}) \cdot \mathbf{i}_{c} = \mathbf{v}_{c} \cdot \mathbf{i}_{c} + \mathbf{v}_{0} \cdot \mathbf{i}_{c}$$

$$(3.5)$$

(3.5)式において、右辺第一項は、正相成分と逆相成分の和により、一意に定まる。一方、右辺第二項からは、 $P_a$ 、 $P_b$ 、 $P_c$ を、 $v_0$ により制御できるのではないかと予想される。

仮に、定数 A、B、C を用いて、voを次のように表す。

$$\mathbf{v}_0 = \mathbf{A}\mathbf{i}_a + \mathbf{B}\mathbf{i}_b + \mathbf{C}\mathbf{i}_c \tag{3.6}$$

(3.5)式と(3.6)式より、 $P_a$ 、 $P_b$ 、 $P_c$ は、次のように計算される。

$$P_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} + \mathbf{A} |\mathbf{i}_{a}|^{2} + \mathbf{B} (\mathbf{i}_{a} \cdot \mathbf{i}_{b}) + \mathbf{C} (\mathbf{i}_{c} \cdot \mathbf{i}_{a})$$

$$P_{b} = \mathbf{v}_{b} \cdot \mathbf{i}_{b} + \mathbf{A} (\mathbf{i}_{a} \cdot \mathbf{i}_{b}) + \mathbf{B} |\mathbf{i}_{b}|^{2} + \mathbf{C} (\mathbf{i}_{b} \cdot \mathbf{i}_{c})$$

$$P_{c} = \mathbf{v}_{c} \cdot \mathbf{i}_{c} + \mathbf{A} (\mathbf{i}_{c} \cdot \mathbf{i}_{a}) + \mathbf{B} (\mathbf{i}_{b} \cdot \mathbf{i}_{c}) + \mathbf{C} |\mathbf{i}_{c}|^{2}$$

$$(3.7)$$

右辺の対称性より、A、B、Cを、定数 A、B、C'を用いて次のように置きなおす。

$$A = A'(\mathbf{i}_b \cdot \mathbf{i}_c)

B = B'(\mathbf{i}_c \cdot \mathbf{i}_a)

C = C'(\mathbf{i}_a \cdot \mathbf{i}_b)$$

(3.8)

すると、(3.7)式は、次のように整理できる。

$$P_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} + \mathbf{A}'(\mathbf{i}_{b} \cdot \mathbf{i}_{c})|\mathbf{i}_{a}|^{2} + (\mathbf{B}' + \mathbf{C}')(\mathbf{i}_{c} \cdot \mathbf{i}_{a})(\mathbf{i}_{a} \cdot \mathbf{i}_{b})$$

$$P_{b} = \mathbf{v}_{b} \cdot \mathbf{i}_{b} + \mathbf{B}'(\mathbf{i}_{c} \cdot \mathbf{i}_{a})|\mathbf{i}_{b}|^{2} + (\mathbf{C}' + \mathbf{A}')(\mathbf{i}_{a} \cdot \mathbf{i}_{b})(\mathbf{i}_{b} \cdot \mathbf{i}_{c})$$

$$P_{c} = \mathbf{v}_{c} \cdot \mathbf{i}_{c} + \mathbf{C}'(\mathbf{i}_{a} \cdot \mathbf{i}_{b})|\mathbf{i}_{c}|^{2} + (\mathbf{A}' + \mathbf{B}')(\mathbf{i}_{b} \cdot \mathbf{i}_{c})(\mathbf{i}_{c} \cdot \mathbf{i}_{a})$$

$$(3.9)$$

さらに, (3.9)式右辺の対称性より, A', B', C'の間に次の関係を設ける。

$$A' + B' + C' = 0$$

(3.10)

これを用いると、(3.9)式は次のように整理できる。

$$P_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} + \mathbf{A}' \left[ \left( \mathbf{i}_{b} \cdot \mathbf{i}_{c} \right) \left| \mathbf{i}_{a} \right|^{2} - \left( \mathbf{i}_{c} \cdot \mathbf{i}_{a} \right) \left( \mathbf{i}_{a} \cdot \mathbf{i}_{b} \right) \right]$$

$$P_{b} = \mathbf{v}_{b} \cdot \mathbf{i}_{b} + \mathbf{B}' \left[ \left( \mathbf{i}_{c} \cdot \mathbf{i}_{a} \right) \left| \mathbf{i}_{b} \right|^{2} - \left( \mathbf{i}_{a} \cdot \mathbf{i}_{b} \right) \left( \mathbf{i}_{b} \cdot \mathbf{i}_{c} \right) \right]$$

$$P_{c} = \mathbf{v}_{c} \cdot \mathbf{i}_{c} + \mathbf{C}' \left[ \left( \mathbf{i}_{a} \cdot \mathbf{i}_{b} \right) \left| \mathbf{i}_{c} \right|^{2} - \left( \mathbf{i}_{b} \cdot \mathbf{i}_{c} \right) \left( \mathbf{i}_{c} \cdot \mathbf{i}_{a} \right) \right]$$

(3.11)

ここで,系統連系される三相 3 線式の電力変換器では, $i_a+i_b+i_c=0$  が成り立つため,次の関係が得られる。

$$(\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2} - |\mathbf{i}_{a}|^{2} |\mathbf{i}_{b}|^{2} = (\mathbf{i}_{b} \cdot \mathbf{i}_{c}) |\mathbf{i}_{a}|^{2} - (\mathbf{i}_{c} \cdot \mathbf{i}_{a}) (\mathbf{i}_{a} \cdot \mathbf{i}_{b})$$

$$= (\mathbf{i}_{c} \cdot \mathbf{i}_{a}) |\mathbf{i}_{b}|^{2} - (\mathbf{i}_{a} \cdot \mathbf{i}_{b}) (\mathbf{i}_{b} \cdot \mathbf{i}_{c}) \qquad (3.12)$$

$$= (\mathbf{i}_{a} \cdot \mathbf{i}_{b}) |\mathbf{i}_{c}|^{2} - (\mathbf{i}_{b} \cdot \mathbf{i}_{c}) (\mathbf{i}_{c} \cdot \mathbf{i}_{a})$$

これを用いて(3.11)式を整理すると、次式が得られる。

$$P_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} + \mathbf{A}' \left[ (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2} - |\mathbf{i}_{a}|^{2} |\mathbf{i}_{b}|^{2} \right]$$

$$P_{b} = \mathbf{v}_{b} \cdot \mathbf{i}_{b} + \mathbf{B}' \left[ (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2} - |\mathbf{i}_{a}|^{2} |\mathbf{i}_{b}|^{2} \right]$$

$$P_{c} = \mathbf{v}_{c} \cdot \mathbf{i}_{c} + \mathbf{C}' \left[ (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2} - |\mathbf{i}_{a}|^{2} |\mathbf{i}_{b}|^{2} \right]$$

$$(3.13)$$

したがって、A'、B'、C'を次式のように設定すると、 $P_a$ 、 $P_b$ 、 $P_c$ は三相等しくなる。

$$\mathbf{A}' = \left[ \frac{1}{3} \sum_{k=a,b,c} \mathbf{v}_{k} \cdot \mathbf{i}_{k} - \mathbf{v}_{a} \cdot \mathbf{i}_{a} \right] / \left[ (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2} - |\mathbf{i}_{a}|^{2} |\mathbf{i}_{b}|^{2} \right]$$

$$\mathbf{B}' = \left[ \frac{1}{3} \sum_{k=a,b,c} \mathbf{v}_{k} \cdot \mathbf{i}_{k} - \mathbf{v}_{b} \cdot \mathbf{i}_{b} \right] / \left[ (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2} - |\mathbf{i}_{a}|^{2} |\mathbf{i}_{b}|^{2} \right]$$

$$\mathbf{C}' = \left[ \frac{1}{3} \sum_{k=a,b,c} \mathbf{v}_{k} \cdot \mathbf{i}_{k} - \mathbf{v}_{c} \cdot \mathbf{i}_{c} \right] / \left[ (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2} - |\mathbf{i}_{a}|^{2} |\mathbf{i}_{b}|^{2} \right]$$

$$(3.14)$$

なお、もしも  $i_a$ 、 $i_b$  の位相差が 0 または  $\pi$  の場合は、(3.14)式により  $v_0$  を計算することができず、提案手法の適用対象外となる。しかし、三相 3 線式による系統連系の場合は  $i_a+i_b+i_e=0$  であるため、 $i_a$ 、 $i_b$ に対する  $i_e$  の位相差も 0 または  $\pi$  となり、現実的には稀なケースとなる。

以上のように、(3.6)式、(3.8)式、(3.14)式より、電力変換器の出力を三相等しく制御するための $v_0$ を得ることができるが、これをさらに(3.15)式のように拡張すれば、任意の比率X、Y、Zで、電力変換器の出力を制御することができる。

$$\mathbf{v}_{0} = \frac{\Delta P_{a}(\mathbf{i}_{b} \cdot \mathbf{i}_{c})\mathbf{i}_{a} + \Delta P_{b}(\mathbf{i}_{c} \cdot \mathbf{i}_{a})\mathbf{i}_{b} + \Delta P_{c}(\mathbf{i}_{a} \cdot \mathbf{i}_{b})\mathbf{i}_{c}}{|\mathbf{i}_{a}|^{2}|\mathbf{i}_{b}|^{2} - (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2}}$$

$$\Delta P_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} - \frac{X}{X + Y + Z} \sum_{k=a,b,c} \mathbf{v}_{k} \cdot \mathbf{i}_{k}$$

$$\Delta P_{b} = \mathbf{v}_{b} \cdot \mathbf{i}_{b} - \frac{Y}{X + Y + Z} \sum_{k=a,b,c} \mathbf{v}_{k} \cdot \mathbf{i}_{k}$$

$$\Delta P_{c} = \mathbf{v}_{c} \cdot \mathbf{i}_{c} - \frac{Z}{X + Y + Z} \sum_{k=a,b,c} \mathbf{v}_{k} \cdot \mathbf{i}_{k}$$

(3.15)

a 相を例にとると、電力変換器の出力  $P_a$ は、次のように計算される。

$$P_{a} = (\mathbf{v}_{a} + \mathbf{v}_{0}) \cdot \mathbf{i}_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} + \frac{\Delta P_{a}(\mathbf{i}_{b} \cdot \mathbf{i}_{c})|\mathbf{i}_{a}|^{2} + (\Delta P_{b} + \Delta P_{c})(\mathbf{i}_{a} \cdot \mathbf{i}_{b})(\mathbf{i}_{c} \cdot \mathbf{i}_{a})}{|\mathbf{i}_{a}|^{2}|\mathbf{i}_{b}|^{2} - (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2}} \dots (3.16)$$

ここで、(3.15)式より、 $\Delta P_b + \Delta P_c = -\Delta P_a$ であるため、(3.16)式は次のように整理できる。

$$P_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} + \frac{\Delta P_{a} \left[ \left( \mathbf{i}_{b} \cdot \mathbf{i}_{c} \right) \left| \mathbf{i}_{a} \right|^{2} - \left( \mathbf{i}_{a} \cdot \mathbf{i}_{b} \right) \left( \mathbf{i}_{c} \cdot \mathbf{i}_{a} \right) \right]}{\left| \mathbf{i}_{a} \right|^{2} \left| \mathbf{i}_{b} \right|^{2} - \left( \mathbf{i}_{a} \cdot \mathbf{i}_{b} \right)^{2}}$$

$$(3.17)$$

さらに、 $i_a+i_b+i_c=0$  を用いて  $i_c$  を、また(3.15)式を用い $\Delta P_a$  を消去すると、(3.17)式は次のように整理できる。

$$P_{a} = \mathbf{v}_{a} \cdot \mathbf{i}_{a} + \frac{\Delta P_{a} \left[ -\left( \mathbf{i}_{b} \cdot \left( \mathbf{i}_{a} + \mathbf{i}_{b} \right) \right) \left| \mathbf{i}_{a} \right|^{2} + \left( \mathbf{i}_{a} \cdot \mathbf{i}_{b} \right) \left( \left( \mathbf{i}_{a} + \mathbf{i}_{b} \right) \cdot \mathbf{i}_{a} \right) \right]}{\left| \mathbf{i}_{a} \right|^{2} \left| \mathbf{i}_{b} \right|^{2} - \left( \mathbf{i}_{a} \cdot \mathbf{i}_{b} \right)^{2}}$$

$$= \mathbf{v}_{a} \cdot \mathbf{i}_{a} - \Delta P_{a}$$

$$= \frac{X}{X + Y + Z} \sum_{k=ab} \mathbf{v}_{k} \cdot \mathbf{i}_{k} \qquad (3.18)$$

同様の計算により、電力変換器のb相とc相の出力 $P_b$ ,  $P_c$ は、次のよう整理できる。

$$P_{b} = \frac{Y}{X + Y + Z} \sum_{k=a,b,c} \mathbf{v}_{k} \cdot \mathbf{i}_{k}$$

$$P_{c} = \frac{Z}{X + Y + Z} \sum_{k=a,b,c} \mathbf{v}_{k} \cdot \mathbf{i}_{k}$$

(3.19)

(3.18)式と(3.19)式のように、正相成分と逆相成分の和  $v_a$ 、 $v_b$ 、 $v_c$  に(3.15)式の  $v_0$  を加えることにより、電力変換器の a 相、b 相、c 相から、任意の比率 X、Y、Z で有効電力  $P_a$ 、 $P_b$ 、 $P_c$  を出力させることが可能となる。

#### 3.3.2 適用限界

前節では、系統連系される三相3線式の電力変換器では、出力電圧の零相成分により、出力電流に影響を与えることなく、三相出力を制御できることを示した。しかし、電力変換器が出力できる電圧波高値は DC 電圧に制約を受けるため、(3.15)式による零相電圧を必ずしも出力できるとは限らない。

例えば図 3.1 のモデルにおいて,電力変換器は,図 3.2(a)に示す出力電圧  $v_a$ ,  $v_b$ ,  $v_c$  と出力電流  $i_a$ ,  $i_b$ ,  $i_c$ により,三相電源  $v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$ に無効電力を供給していたとする。次に, $\mathbf{b}$ - $\mathbf{c}$  相の短絡事故が発生し,電力変換器の出力電圧が,図 3.2(b)に示すように変化したとする。また,この時の出力電圧と出力電流が,(3.20)式と(3.21)式のように表されるものとする。ここで, $\mathbf{e}^{i\phi}$ は,基準電圧と位相差 $\phi$ で,振幅 1pu のフェーザを表す。

$$\mathbf{v}_{a} = V\mathbf{e}^{j0}$$

$$\mathbf{v}_{b} = \mathbf{v}_{c} = \frac{V}{2}\mathbf{e}^{j\pi}$$

$$(3.20)$$

$$\mathbf{i}_{a} = I \mathbf{e}^{j\frac{\pi}{2}}

\mathbf{i}_{b} = I \mathbf{e}^{j\frac{\pi}{2} - j\frac{2\pi}{3}}

\mathbf{i}_{c} = I \mathbf{e}^{j\frac{\pi}{2} + j\frac{2\pi}{3}}$$

(3.21)

(3.15)式に、(3.20)式と(3.21)式を代入すると、 $v_0$ は次式となる。ただし、ここでは(3.15)式の比率 X、Y、Zを、何れも 1 としている。

$$\mathbf{v}_0 = \frac{1}{2} V \mathbf{e}^{j0} \tag{3.22}$$

$v_0$ を用いた電力変換器の出力電圧は、図 3.3 に示すように、a 相では定格の 1.5pu となる。(3.20) 式~(3.22)式を用いた計算の上では三相出力は等しくなるが、このような電圧を出力できる余裕を DC 電源に設けることは、電力変換器の容量にも、それに見合った余裕が必要になり、機器のイニシャルコストに影響する。したがって、零相電圧制御を選択することは、必ずしも最善策であるとは限らない。

また,回転機のベアリング電流のような負荷への影響や,地絡保護リレーの誤動作についても, 注意する必要がある。

図 3.2 出力電圧と出力電流の関係

図 3.3 零相電圧制御時の出力電圧と 出力電流の関係

## 3.4 逆相電流による三相出力制御[7]

3.2 節で示したように、逆相電流を出力することにより、不平衡かつ三相合計がゼロになる電力が、電力変換器から出力される。例えば、三相平衡な出力電圧に対して、a 相の位相が一致した逆相電流を出力すれば、a 相から出力される有効電力の 1/2 ずつが b 相と c 相に回生される。

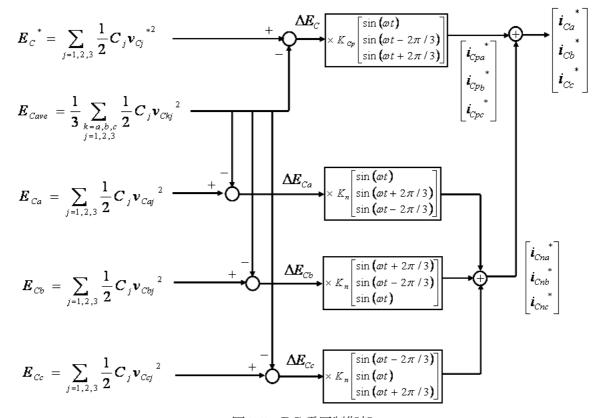

この性質を利用し,(3.23)式の右辺第三項に示す逆相成分を出力電流に加えることにより,電力変換器の三相出力制御を試みる。ここで, $e_a$ , $e_b$ , $e_c$  は電力変換器の各相に充電されたエネルギー, $K_n$  は制御ゲインである。

$$\begin{bmatrix} i_{a} \\ i_{b} \\ i_{c} \end{bmatrix} = \sqrt{\frac{2}{3}} I_{p} \begin{bmatrix} \cos(\omega t + \varphi_{ip}) \\ \cos(\omega t + \varphi_{ip} - \frac{2\pi}{3}) \\ \cos(\omega t + \varphi_{ip} + \frac{2\pi}{3}) \end{bmatrix} + \sqrt{\frac{2}{3}} I_{n} \begin{bmatrix} \cos(\omega t + \varphi_{in}) \\ \cos(\omega t + \varphi_{in} + \frac{2\pi}{3}) \\ \cos(\omega t + \varphi_{in} - \frac{2\pi}{3}) \end{bmatrix}$$

$$+ \sqrt{\frac{2}{3}} K_{n} \begin{cases} e_{a} \begin{bmatrix} \cos(\omega t) \\ \cos(\omega t + \frac{2\pi}{3}) \\ \cos(\omega t + \frac{2\pi}{3}) \end{bmatrix} + e_{b} \begin{bmatrix} \cos(\omega t + \frac{2\pi}{3}) \\ \cos(\omega t - \frac{2\pi}{3}) \end{bmatrix} + e_{c} \begin{bmatrix} \cos(\omega t) \\ \cos(\omega t) \end{bmatrix}$$

$$= \cos(\omega t)$$

$$= \cos(\omega t$$

(3.1)式の電圧と(3.23)式の電流より定まる各相の有効出力 $P_a$ ,  $P_b$ ,  $P_c$ は、次のように計算できる。

$$\begin{bmatrix} P_{a} \\ P_{b} \\ P_{c} \end{bmatrix} = \begin{bmatrix} \frac{\omega}{2\pi} \int_{0}^{\frac{2\pi}{\omega}} v_{a} \cdot i_{a} dt \\ \frac{\omega}{2\pi} \int_{0}^{\frac{2\pi}{\omega}} v_{b} \cdot i_{b} dt \\ \frac{\omega}{2\pi} \int_{0}^{\frac{2\pi}{\omega}} v_{c} \cdot i_{c} dt \end{bmatrix} = \begin{bmatrix} P \\ P \\ P \end{bmatrix} + \begin{bmatrix} P_{na} \\ P_{nb} \\ P_{nc} \end{bmatrix} + \frac{1}{2} V_{p} K_{n} \begin{bmatrix} e_{a} - \frac{e_{a} + e_{b} + e_{c}}{3} \\ e_{b} - \frac{e_{a} + e_{b} + e_{c}}{3} \\ e_{c} - \frac{e_{a} + e_{b} + e_{c}}{3} \end{bmatrix}$$

(3.24)

ただし、P,  $P_{na}$ ,  $P_{nb}$ ,  $P_{nc}$ は次式の通りである。

$$P = \frac{1}{3} V_{p} I_{p} \cos \varphi_{ip} + \frac{1}{3} V_{n} I_{n} \cos(\varphi_{in} - \varphi_{vn})$$

$$+ \frac{1}{3} V_{n} K_{n} \left[ e_{a} \cos \varphi_{vn} + e_{b} \cos(\varphi_{vn} - \frac{2\pi}{3}) + e_{c} \cos(\varphi_{vn} + \frac{2\pi}{3}) \right]$$

$$P_{na} = \frac{1}{3} V_{p} I_{n} \cos \varphi_{in} + \frac{1}{3} V_{n} I_{p} \cos(\varphi_{ip} - \varphi_{vn})$$

$$P_{nb} = \frac{1}{3} V_{p} I_{n} \cos(\varphi_{in} - \frac{2\pi}{3}) + \frac{1}{3} V_{n} I_{p} \cos(\varphi_{ip} - \varphi_{vn} + \frac{2\pi}{3})$$

$$P_{nc} = \frac{1}{3} V_{p} I_{n} \cos(\varphi_{in} + \frac{2\pi}{3}) + \frac{1}{3} V_{n} I_{p} \cos(\varphi_{ip} - \varphi_{vn} - \frac{2\pi}{3})$$

$$(3.25)$$

ここで、(3.23)式右辺第二項のパラメータ  $I_n$  と $\varphi_{in}$  を、次のように設定したとする。

$$I_{n} = -\frac{V_{n}}{V_{p}} I_{p}$$

$$\varphi_{in} = \varphi_{vn} - \varphi_{ip}$$

$$(3.26)$$

(3.24)式,(3.25)式,(3.26)式より, $P_a$ , $P_b$ , $P_c$ は,次のように整理できる。

$$\begin{bmatrix} P_{a} \\ P_{b} \\ P_{c} \end{bmatrix} = \begin{bmatrix} P \\ P \\ P \end{bmatrix} + \frac{1}{2} V_{p} K_{n} \begin{bmatrix} e_{a} - \frac{e_{a} + e_{b} + e_{c}}{3} \\ e_{b} - \frac{e_{a} + e_{b} + e_{c}}{3} \\ e_{c} - \frac{e_{a} + e_{b} + e_{c}}{3} \end{bmatrix}$$

(3.27)

ここで,右辺第一項のPは次式の通りである。

$$P = \frac{V_p^2 - V_n^2}{3V_n} I_p \cos \varphi_{ip} + \frac{V_n K_n}{3} \left[ e_a \cos \varphi_{vn} + e_b \cos \left( \varphi_{vn} - \frac{2\pi}{3} \right) + e_c \cos \left( \varphi_{vn} + \frac{2\pi}{3} \right) \right] \dots (3.28)$$

(3.27)式の右辺第二項は、 $e_a$ 、 $e_b$ 、 $e_c$  の平均値との誤差を補正するよう作用する。このように、(3.23)式による逆相電流を用いることにより、三相の充電エネルギーを制御することが可能となる。ただし、(3.26)式のように、出力できる逆相電流は一意に定まるため、例えば逆相電流補償ができなくなるなど、機能的な制約が生じることに留意する必要がある。

#### 3.5 系統事故時における電流制御[8]

3.3 節と 3.4 節では、系統電圧や出力電流に不平衡が存在しても、零相電圧や逆相電流により電力変換器の三相出力を制御できることを、理論的に示した。しかし、事故時のように大幅な不平衡が存在する電力系統に連系される電力変換器には、提案した理論を適用する以前に、過電流が容易に生じるという課題が存在する[3][5]。本節では、このような課題に対し、系統不平衡時においても電力変換器の出力電流を目標値通りに制御するための手法について検討する。

#### 3.5.1 検討モデル

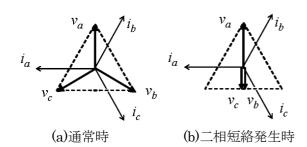

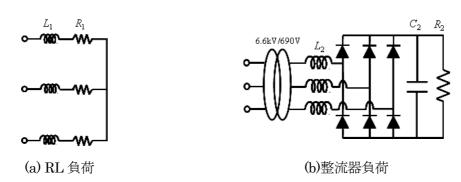

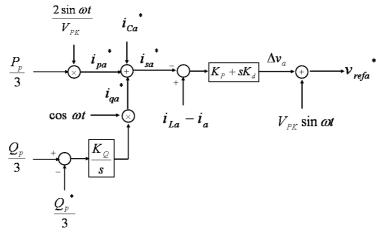

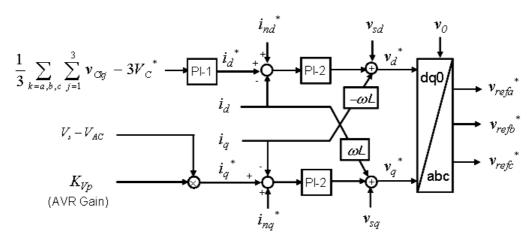

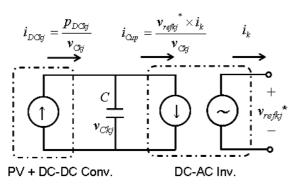

分散形電源の系統連系用インバータを検討モデルとし、構成は、図 3.4 に示すように、太陽電池などを想定した DC 電源、三相 200V-4kW の電力変換器、三相電源からなるものとする。電力変換器は、三相フルブリッジインバータと昇圧チョッパを組合せたものとする。いずれも、高周波 PWM により、電圧形電流制御を行う方式とする。インバータは、DC 電圧一定制御により動作する。チョッパは、常時は DC 電源に一定電力を出力させるよう動作する。また、系統側で一定以上の電圧低下が生じた際には、インバータが出力する正相有効電流に過電流が生じないよう、系統電圧の正相成分に比例して、DC 電源から取り出す電力を制限する機能を有する。

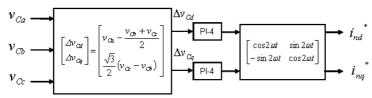

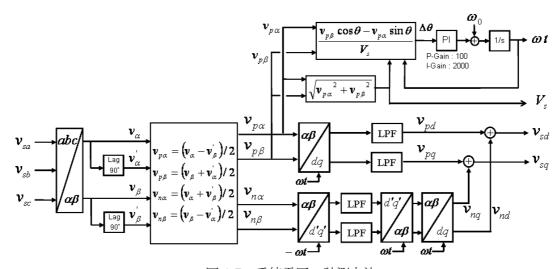

ベースモデルとなる制御ブロック図を、図 3.5 に示す。この制御では、系統電圧や出力電流などの交流分を、dq 座標において取扱う。なお、dq 変換[11]にあたり、系統電圧の位相 $\omega t$ の検出

図 3.6 系統電圧との同期方法

については図3.6に示す方法を用いる。

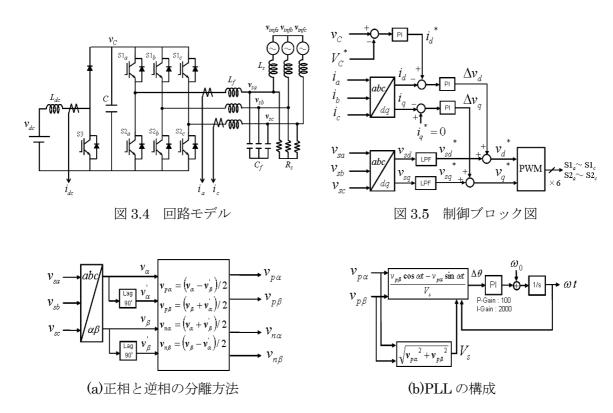

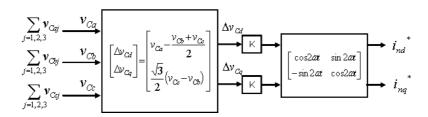

図 3.6(a)では、まず系統電圧  $v_{sa}$ 、  $v_{sb}$ 、  $v_{sc}$  を三相一二相変換により  $\alpha\beta$ 座標に変換し[11]、次に正相成分  $v_{pa}$ 、  $v_{p\beta}$  と逆相成分  $v_{na}$ 、  $v_{n\beta}$ に分離している。ここで、"Lag90°"と示した制御要素は、入力  $v_{a}$ 、  $v_{\beta}$  を基本周波数の 1/4 サイクル分遅延させた  $v'_{a}$ 、  $v'_{\beta}$  を出力する。  $v_{sa}$ 、  $v_{sb}$ 、  $v_{sc}$  が(3.1)式の  $v_{a}$ 、  $v_{b}$ 、  $v_{c}$  と等しいとすると、  $v_{a}$ 、  $v_{b}$ ,  $v_{c}$  が(3.1)式の  $v_{a}$  のように計算される。

$$\begin{bmatrix} v_{\alpha} \\ v_{\beta} \end{bmatrix} = V_{p} \begin{bmatrix} \cos \omega t \\ \sin \omega t \end{bmatrix} + V_{n} \begin{bmatrix} \cos(\omega t + \varphi_{vn}) \\ -\sin(\omega t + \varphi_{vn}) \end{bmatrix}$$

(3.29)

$$\begin{bmatrix} v'_{\alpha} \\ v'_{\beta} \end{bmatrix} = V_p \begin{bmatrix} \sin \omega t \\ -\cos \omega t \end{bmatrix} + V_n \begin{bmatrix} \sin(\omega t + \varphi_{vn}) \\ \cos(\omega t + \varphi_{vn}) \end{bmatrix}$$

(3.30)

(3.29)式と(3.30)式より、正相成分 $v_{pa}$ 、 $v_{p\beta}$ と逆相成分 $v_{na}$ 、 $v_{n\beta}$ は、次のように分離できる。

$$\begin{bmatrix} v_{p\alpha} \\ v_{p\beta} \end{bmatrix} = \frac{1}{2} \begin{bmatrix} v_{\alpha} - v_{\beta} \\ v_{\beta} + v_{\alpha} \end{bmatrix} = V_{p} \begin{bmatrix} \cos \omega t \\ \sin \omega t \end{bmatrix}$$

(3.31)

$$\begin{bmatrix} v_{n\alpha} \\ v_{n\beta} \end{bmatrix} = \frac{1}{2} \begin{bmatrix} v_{\alpha} + v_{\beta}' \\ v_{\beta} - v_{\alpha}' \end{bmatrix} = V_n \begin{bmatrix} \cos(\omega t + \varphi_{vn}) \\ -\sin(\omega t + \varphi_{vn}) \end{bmatrix}$$

(3.32)

制御要素"Lag90"の遅延時間に系統周波数の変動は反映しないが、分散形電源の周波数上昇リレ

ーおよび周波数低下リレーに通常用いられる整定範囲(約 $\pm 2$ Hz 以内)の変動であれば、計算される位相 $\omega t$  に与える影響は僅かであり、誤差は無視することとした。

1/2 サイクル窓の移動平均フィルタを用いる正相と逆相の分離方法[12]と比較すると、図 3.6 に示した方法は、1/4 サイクルと高速に $v_{pa}$ ,  $v_{p\beta}$ ,  $v_{na}$ ,  $v_{n\beta}$ を分離でき、事故などのように、系統電圧 $v_a$ ,  $v_\beta$  が急変する場合に有利である。ただし、系統電圧の基本波成分の検出には、高調波成分を除去するためのローパスフィルタ処理が必要となり、その分の検出遅れが生じることに注意が必要である。

#### 3.5.2 二相短絡事故に対する応答

図 3.5 に示したベースモデルの制御ブロック図では、系統電圧  $v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$  を dq 変換した  $v_{sd}$ ,  $v_{sq}$  に、高周波成分を除去するためのローパスフィルタ処理を施すことにより、インバータの出力電圧目標値  $v_d^*$ ,  $v_q^*$ の演算に用いる系統電圧の基本波成分  $v_{sd}^*$ ,  $v_{sq}^*$ を求めている。ここで、 $v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$  が(3.1)式の  $v_a$ ,  $v_b$ ,  $v_c$  と等しいとすると、これを dq 変換した  $v_{sd}$ ,  $v_{sq}$  は、次のように表される。

$$\begin{bmatrix} v_{sd} \\ v_{sq} \end{bmatrix} = V_p \begin{bmatrix} 1 \\ 0 \end{bmatrix} + V_n \begin{bmatrix} \cos(2\omega t + \varphi_{vn}) \\ -\sin(2\omega t + \varphi_{vn}) \end{bmatrix}$$

(3.33)

(3.33)式の第一項に表れる正相成分は,直流となるため,ローパスフィルタ処理を行っても正確に検出される。しかし,第二項に表れる逆相成分は,基本波の 2 倍の周波数で振動するため,ローパスフィルタ処理を行うと誤差が生じる。したがって,系統電圧が不平衡な場合, $v_{sd}^*$ 、 $v_{sq}^*$ を正確に検出することができなくなる。

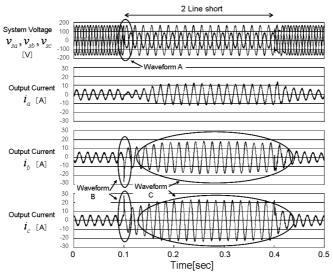

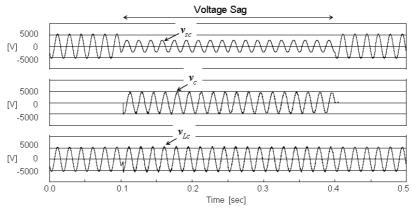

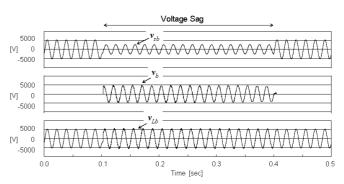

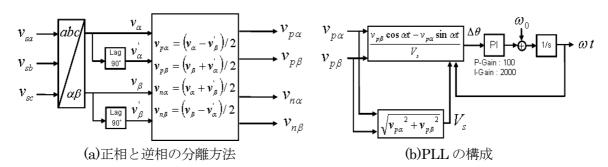

図 3.4~図 3.6 に示した回路と制御ブロックを用いたインバータの応答について,実測例を示す。試験回路と制御系には,後述する表 3.1,表 3.2 に示す定数を用いた。インバータが 1.5kW を出力していた時に,b-c 相の二相短絡事故を模擬した電圧を,電源  $v_{infa}$ ,  $v_{infb}$ ,  $v_{infc}$  より 300msec の間発生させた。

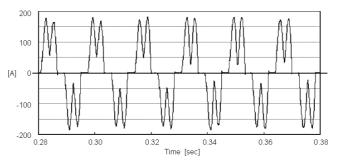

測定した系統電圧  $v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$  とインバータの出力電流  $i_a$ ,  $i_b$ ,  $i_c$  を,図 3.7 に示す。事故開始の

図 3.7 分散形電源用インバータ (ベースモデル) の二相短絡事故への応答

タイミングにある Waveform A では、b 相と c 相の電圧  $v_{sb}$ 、 $v_{sc}$  が急変する。そして、Waveform C では b 相と c 相の電流  $i_b$ 、 $i_c$ が、不平衡な状態で大幅に増加した。以下では、この現象を逆相過電流と呼ぶことにする。この測定では、インバータが過電流で脱落しないように、出力を定格の4 割程度に抑えて行ったが、出力を上げておれば、過電流検出レベルに達し、インバータが脱落する原因となりうる。

# 3.5.3 逆相過電流への対応

系統電圧に大幅な不平衡が生じた際には、前述のように、系統電圧の検出誤差により、電力変換器の出力に逆相過電流が発生する場合がある。これに対し、系統電圧の検出値として以下のように求める $v_{sd}^*$ ,  $v_{sq}^*$ を用いて、逆相過電流の抑制を試みる。

制御にあたっては、図 3.6(a)の制御ブロックにより系統電圧  $v_{sa}$ ,  $v_{sb}$ ,  $v_{sc}$  から分離された正相成分と逆相成分を用いる。次式のように、正相成分  $v_{pa}$ ,  $v_{p\beta}$ に対しては通常の dq 変換を行い、さらに時定数 T のローパスフィルタにより高調波分を除去した  $v_{pd}$ ,  $v_{pq}$  を、系統電圧検出値の正相成分とする。ただし、記号"  $\mathcal{E}$ " はラプラス変換を表す。

$$\begin{bmatrix} v_{pd} \\ v_{pq} \end{bmatrix} = \mathcal{L}^{-1} \left\{ \frac{1}{1+sT} \mathcal{L} \begin{bmatrix} \cos \omega t & \sin \omega t \\ -\sin \omega t & \cos \omega t \end{bmatrix} \begin{bmatrix} v_{p\alpha} \\ v_{p\beta} \end{bmatrix} \right\}$$

(3.34)

(3.31)式に示す $v_{pa}$ 、 $v_{p\beta}$ を用いると、(3.34)式は次のように整理される。

$$\begin{bmatrix} v_{pd} \\ v_{pq} \end{bmatrix} = \mathcal{L}^{-1} \left\{ \frac{1}{1+sT} \mathcal{L} \left( V_p \begin{bmatrix} 1 \\ 0 \end{bmatrix} \right) \right\} \dots (3.35)$$

このように、正相成分  $v_{pd}$ 、  $v_{pq}$  は、ローパスフィルタの時定数 T にかかわらず、正確に検出することができる。

一方,逆相成分の計算にあたっては、次式に示すように、 $v_{n\alpha}$ 、 $v_{n\beta}$ を、正相成分と逆方向に回転する  $\mathbf{d}$ ' $\mathbf{q}$ '座標上に、一旦変換する。

$$\begin{bmatrix} v_{nd}' \\ v_{nq}' \end{bmatrix} = \mathcal{L}^{-1} \left\{ \frac{1}{1+sT} \mathcal{L} \begin{pmatrix} \cos \omega t & -\sin \omega t \\ \sin \omega t & \cos \omega t \end{pmatrix} \begin{bmatrix} v_{n\alpha} \\ v_{n\beta} \end{bmatrix} \right\}$$

(3.36)

(3.32)に示す $v_{n\alpha}$ 、 $v_{n\beta}$ を用いると、(3.36)式は、次のように整理される。

$$\begin{bmatrix} v_{nd} \\ v_{nq} \end{bmatrix} = \mathcal{L}^{-1} \left\{ \frac{1}{1+sT} \mathcal{L} \left( V_n \begin{bmatrix} \cos \varphi_{vn} \\ -\sin \varphi_{vn} \end{bmatrix} \right) \right\} \dots (3.37)$$

このように、 $\mathbf{d'q'}$ 座標上では逆相成分  $v_{nd'}$ 、 $v_{nq'}$ は直流となるため、ローパスフィルタ処理を行っても正確に検出される。次に、 $v_{nd'}$ 、 $v_{nq'}$ を正相成分と順方向に  $\mathbf{2}$  倍の角周波数で回転させることにより、 $\mathbf{dq}$  座標上の逆相成分  $v_{nd}$ 、 $v_{nq}$ を得る。

$$\begin{bmatrix} v_{nd} \\ v_{nq} \end{bmatrix} = \begin{bmatrix} \cos 2\omega t & \sin 2\omega t \\ -\sin 2\omega t & \cos 2\omega t \end{bmatrix} \begin{bmatrix} v_{nd} \\ v_{nq} \end{bmatrix}$$

(3.38)

そして、次式のように、これらの和より得られる $v_{sd}^*$ 、 $v_{sq}^*$ を、系統電圧の検出値として用いる。

$$\begin{bmatrix} v_{sd} \\ v_{sq} \\ v_{sq} \end{bmatrix} = \begin{bmatrix} v_{pd} \\ v_{pq} \end{bmatrix} + \begin{bmatrix} v_{nd} \\ v_{nq} \end{bmatrix}$$

(3.39)

さらに、この方法では、ローパスフィルタは AC 側の高調波を除去するだけでよいので、時定数を大きく設定する必要が無い。このため、逆相成分を正確に検出できるだけではなく、系統電圧を高速に検出できるメリットもある。

#### 3.5.4 系統事故時の電流制御に関する原理実証試験

試験回路は、図 3.4 に示した通りであり、電源  $v_{infa}$ 、 $v_{infb}$ 、 $v_{infc}$ 、電源側インピーダンスを模擬するためのリアクトル  $L_s$ 、抵抗負荷  $R_s$ 、三相フルブリッジインバータと昇圧チョッパ、そして DC 電源を組み合わせて構成する。インバータは、PWM により制御され、スイッチング周波数は 6kHz である。電源  $v_{infa}$ 、 $v_{infb}$ 、 $v_{infc}$  には、指定した時刻に電圧を急変させることができる試験用電源装置を用いている。

表 3.1 回路定数

| Rated Voltage           | $V_{\scriptscriptstyle AC}$          | $3\phi$ AC200V                  |

|-------------------------|--------------------------------------|---------------------------------|

| Rated Active Power      | P                                    | 4kW                             |

| Line angular frequency  | $\omega_0$                           | $2 \pi \times 60 \text{ rad/s}$ |

| Line Inductance         | $L_{\scriptscriptstyle \mathcal{S}}$ | 0.47mH (1.8%)                   |

| Load Resistance         | $R_{\scriptscriptstyle \mathcal{S}}$ | 10Ω (4kW)                       |

| Filter Capacitance      | $C_f$                                | 30 μ F                          |

| Filter Inductance       | $L_{\!f}$                            | 1.6mH (6%)                      |

| DC Capacitance          | C                                    | 3000 μ F                        |

| Rated Capacitor Voltage | ${V_C}^*$                            | 365V                            |

表 3.2 制御定数

| PI-1: | Proportional gain | $K_{Cp}$ | 0.4   |

|-------|-------------------|----------|-------|

| PI-1: | Integral gain     | $K_{Ci}$ | 7.4   |

| PI-2: | Proportional gain | $K_p$    | 9.6   |

| PI-2: | Integral gain     | $K_{i}$  | 290   |

| LPF:  | Time constant     | T        | 1.3ms |

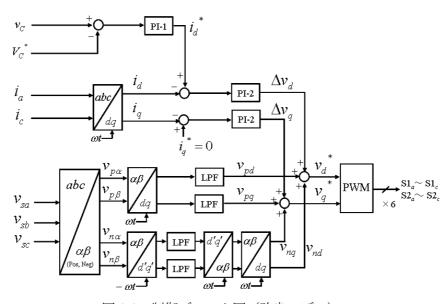

図3.8 制御ブロック図(改良モデル)

表 3.1 に、回路定数を示す。インバータの定格出力は、4kW である。抵抗負荷  $R_s$  は、電源  $v_{infa}$ 、 $v_{infb}$ 、 $v_{infb}$ 、 $v_{infc}$  が有効電力をほとんど吸収できない仕様であるため、インバータの出力を消費するよう設けたものである。抵抗値は、定格出力に相当する  $10\Omega$  とした。連系リアクトル  $L_f$  と、電源側インピーダンスを模擬したリアクトル  $L_s$  のリアクタンスは、定格出力に対して、それぞれ 6%、1.8% とする。フィルタコンデンサ  $C_f$  と、連系リアクトル  $L_f$  との組み合わせによるカットオフ周波数は、726Hz となる。DC コンデンサ C の容量は、チョッパの出力電流に生じるリプルを許容できるよう選定する。

改良モデルの制御ブロック図と制御定数を、図 3.8 と表 3.2 に示す。 $v_{sa}$ 、 $v_{sb}$ 、 $v_{sc}$  から  $v_{pa}$ 、 $v_{p\beta}$ 、 $v_{na}$ 、 $v_{nb}$ への変換には、(3.29)式~(3.32)式に示した手法を用いている。

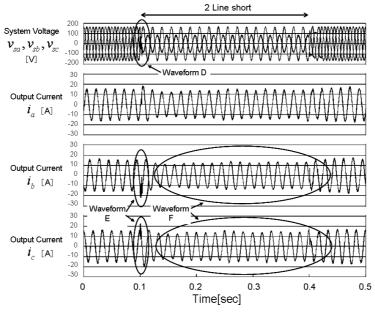

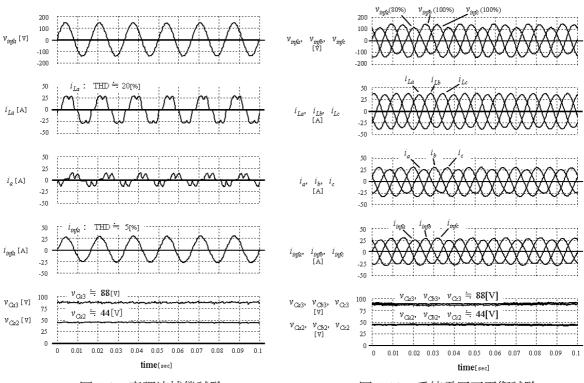

以上に示した試験装置を用いて、改良モデルの応答を検証した。試験結果を、図 3.9 に示す。インバータが定格の 4kW を出力しているところに、図 3.7 に示したベースモデルを用いた測定と同様に、b-c 相の二相短絡事故を模擬した電圧を、電源  $v_{infa}$ 、 $v_{infb}$ 、 $v_{infc}$ より 300msec の間発生させた。

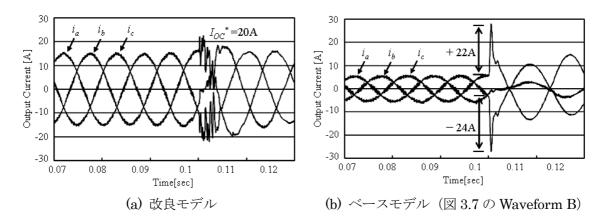

図 3.9 の Waveform F では、図 3.7 の Waveform C で見られたような、電流増加は発生していない。このように、改良モデルのインバータは、不平衡な系統電圧に対しても、ほぼ三相平衡な電流を出力できており、逆相過電流を抑制するための制御は良好に動作したと考えられる。

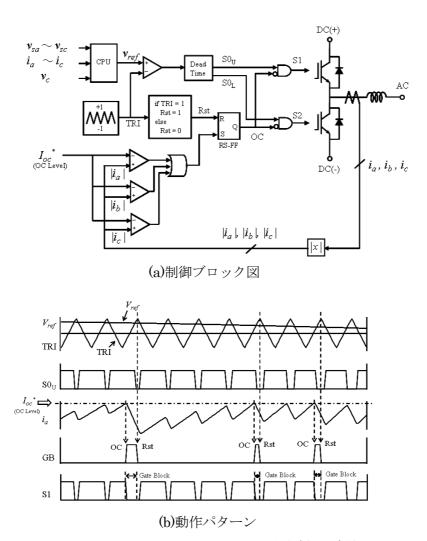

なお、図 3.10(a)は、図 3.9 の Waveform E を拡大した波形であるが、図 3.10(b)(図 3.7 の Waveform B)に見られるスパイク状の過電流は発生していない。これは、図 3.11 に示した、パルスバイパルスと呼ばれる手法を導入したためである。この手法では、出力電流  $i_a$ ,  $i_b$ ,  $i_c$  のいずれかが過電流保護レベル  $I_{oc}^*$ を上回れば、過電流信号 OC が H レベルとなり、インバータのスイッチング素子は上下アームともオフし、ゲートブロック状態となる。ここで、信号 OC は RS-FFでラッチされているため、ゲートブロック状態は、次に三角波 TRI がピーク値となり、信号 Rstが H レベルになって RS-FF がリセットされるまで継続し、この間に出力電流  $i_a$ ,  $i_b$ ,  $i_c$  は抑制される。

図 3.9 分散形電源用インバータ (改良モデル) の二相短絡事故への応答

図 3.10 事故直後の出力電流波形

図 3.11 パルスバイパルスによる過電流抑制方法

## 3.6 結言

本章では、CLMCの三相電力系統への適用を目的とし、系統電圧や電力変換器の出力電流に不 平衡が存在する場合にも、三相出力を制御するための基本的な手法を示した。

まず、電力系統の不平衡が電力変換器の出力に及ぼす影響について述べた。電力系統に不平衡

が存在する場合には、電力変換器の特定の相に出力が偏り、機器容量を有効に利用できない可能 性があることを示した。

次に、零相電圧制御により、電力変換器の三相出力を任意の比率で制御する理論を示した。三相電力系統に連系する電力変換器では、出力電圧の零相成分は出力電流に影響を及ぼさないため、 その設定に自由度が発生する。この自由度を利用して、三相出力を制御できることを示した。

また, DC 電圧の制限により零相電圧制御が適用できない場合の対策として, 出力電流の逆相成分を制御することによっても, 電力変換器の三相出力を等しく制御する理論を示した。

ただし、零相電圧制御では DC 電圧による適用限界が、逆相電流制御では出力できる電流に制約が生じることも示した。

そして,これらの理論の実現に不可欠な技術として,系統事故などにより大幅な不平衡が生じた場合にも,電力変換器の出力電流を目標値通りに制御するための手法を検討した。この手法では,系統電圧を正相成分と逆相成分に分離して精度よく検出することにより,逆相過電流を抑制することを可能とした。

## 参考文献

- [1] 「瞬時電圧低下対策」, 電気協同研究, 第 46 巻第 3 号, p. 17 (2002)

- [2] M.H.J.Bollen: "Voltage Recovery after Unbalanced and Balanced Voltage Dips in Three-Phase System", IEEE Transactions on Power Delivery, Vol.18, No.4, pp. 1376-1381, October (2003).

- [3] 高崎昌洋, 宜保直樹, 竹中清, 林敏之, 小西博雄, 田中誠二, 伊東英俊: 「自励式直流送電システムにおける系統事故時の制御保護方式」, 電気学会論文誌 B, Vol.118-B, No.12, pp.1363-1373 (1998)

- [4] T.Fujii, S.Funahashi, N.Morishima, M.Azuma, H.Teramoto, N.Iio, H.Yonezawa, D.Takayama, Y.Shinki: "A±80MVA GCT STATCOM for the Kanzaki Substation", The 2005 International Power Electronics Conference, S37-1 (2005)

- [5] 萩原誠,和田圭二,藤田英明,赤木泰文: 「線間 21 レベル自励式 BTB システムの一線地絡時における過渡特性」,電気学会論文誌 D, Vol.126-D, No.3, pp.352-359 (2006)

- [6] 羽田野伸彦: 「三相トランスレスDVRの一制御手法」,電気学会論文誌 D, Vol.128-D, No.9, pp.1065-1074 (2008)

- [7] N.Hatano, T.Ise: "A configuration and control method of cascade H-bridge STATCOM", IEEE PES General Meeting 2008, Pittsburgh (USA), 08GM0551, July (2008)

- [8] 羽田野伸彦,谷口雄二,胡内勝彦:「瞬時電圧低下時における分散形電源用インバータの制御手法」,電気学会論文誌 D, Vol.128-D, No.1, pp.71-82 (2008)

- [9] 「半導体電力変換回路」,電気学会 半導体電力変換方式調査専門委員会,pp.129-133 (1987)

- [10] R.E.Betz, T.J.Summers: "Using a Cascaded H-Bridge STATCOM for Rebalancing Unbalanced Voltages", The 7th International Conference on Power Electronics, THE3-2 (2007)

- [11] 「パワーエレクトロニクス回路」, 電気学会 半導体電力変換システム調査専門委員会, pp.80-82 (2000)

- [12] B.Blazic, I.Papic: "Improved D-Statcom Control for Operation With Unbalanced Currents and Voltages", IEEE Transactions on Power Delivery, Vol. 21, No.1, pp. 225-233 (2006)

# 第4章 チェーンリンク形マルチレベル変換器を 用いた直列形瞬時電圧低下補償装置(DVR)

## 4.1 緒言

電力系統における瞬低(瞬時電圧低下)とは、系統事故が発生した場合に、それを検出し、しゃ断器で除去するまでの間に、負荷供給電圧が低下する現象である。ごく短時間の電圧低下であるが、生産ラインや情報機器などに深刻な被害を及ぼす[1]。

瞬低を補償するにあたっては、停電対策のように大きなエネルギーが必要ないことから、専用の対策装置として、コンデンサをエネルギー源とした DVR(Dynamic Voltage Restorer)が実用化されている[2]-[5]。DVR は、電源と負荷の間に直列に接続され、電源電圧の低下を補償する装置であり、インバータには昇圧用変圧器や高調波フィルタが用いられている。

一方、チェーンリンク形マルチレベル変換器 (Chain Link type Multilevel Converter: CLMC) は、セル(単位変換器)を交流側で直列に接続して構成するため、高電圧の出力が容易である。また、マルチレベル化により高調波を低減できるというメリットを併せ持つ[6]-[8]。このように、CLMC によるインバータシステムでは、昇圧用変圧器や高調波フィルタを省略することが容易になり、特に高電圧・大容量システムにおいて、従来装置と比べて大幅なコンパクト化・低コスト化が期待できる。

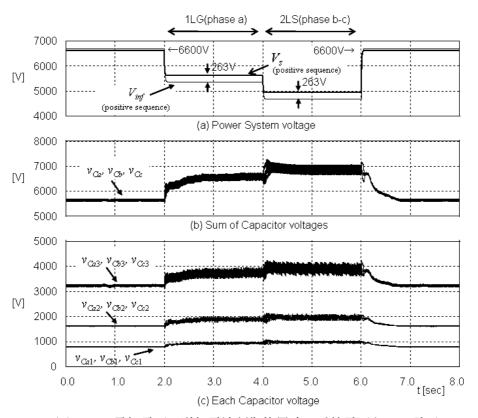

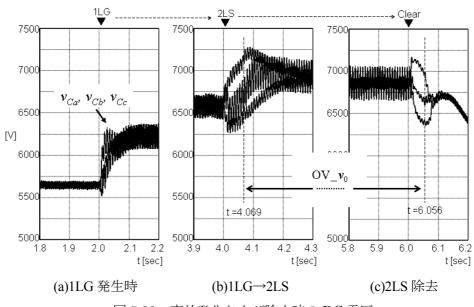

ところが、CLMC を用いたトランスレス DVR を三相系統に適用する場合、DC 電源をセルごとに分離して設置することになる。したがって、三相の出力が均等でない場合には、大きな補償エネルギーを出力する相のコンデンサ充電電圧がいち早く低下し、他相に充電エネルギーの余裕を残したまま、十分な波高値の補償電圧を出力できなくなる。三相系統において、瞬低の原因は、一相または二相の系統事故が約 8 割と大半を占める[1]。このため、三相トランスレス DVR は、DC 電源の利用率の良くない装置となる可能性がある。

以下本章では、CLMC を三相トランスレス DVR に適用するための技術を確立することを目的に、補償電圧に不平衡が存在する場合にも、三相等しく補償エネルギーを出力するための制御手法について検討する。

4.2 節では、2 進ハイブリッド CLMC を用いた DVR の基本構成を示す。次に零相電圧制御により、DVR の三相出力を制御できることを示す。

4.3 節では、400V-100kVA 級の試験装置により、原理実証した結果を示す[9]。

4.4 節では、3 直列-2 進ハイブリッド CLMC を用いた、6.6 kV-1MVA トランスレス DVR の試設計を行う。この際には、零相電圧制御の瞬時値領域への拡張を試みる[10]。

4.5 節では、本章の検討結果をまとめる。

## 4.2 DVR への適用

## 4.2.1 基本構成

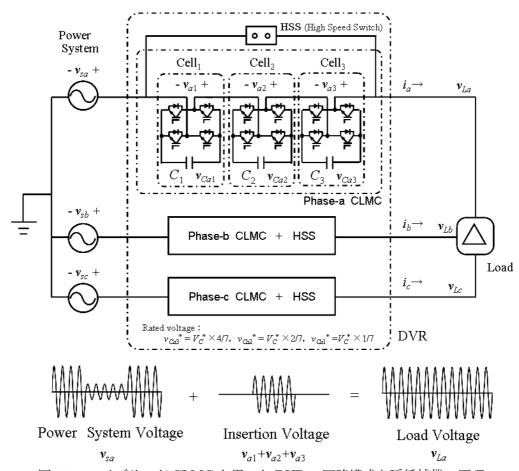

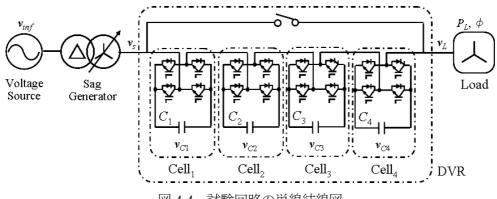

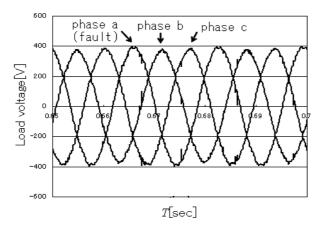

CLMC を用いたトランスレス DVR の回路構成を図 4.1 に示す。装置は、ハイブリッド CLMC、補償エネルギー源である DC コンデンサ、高速しゃ断器(High Speed Switch: HSS)から構成される。通常時は、HSS を通じて負荷に電力供給する。この際、系統電圧を監視し、あらかじめ基準電圧を定めておく。瞬低時には HSS を開極し、基準電圧と系統電圧の差分を補償電圧として出力する。

図 4.1 ハイブリッド CLMC を用いた DVR の回路構成と瞬低補償の原理

図 4.2 各セルの動作タイミング

装置の特徴である 2 進ハイブリッド CLMC は、DC 電圧  $v_{Cl}$ 、 $v_{C2}$ 、 $v_{C3}$  が 2 倍ずつの関係にある 3 台のセル Cell<sub>1</sub>、Cell<sub>2</sub>、Cell<sub>3</sub>を直列に接続して構成される。図 4.1 には、半導体スイッチとして IGBT (Insulated Gate Bipolar Transistor) を用いているが、GTO (Gate Turn-off Thyristor) や GCT(Gate Commutated Thyristor)などを用いることも可能である。

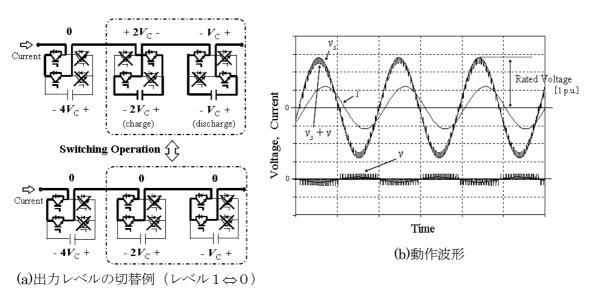

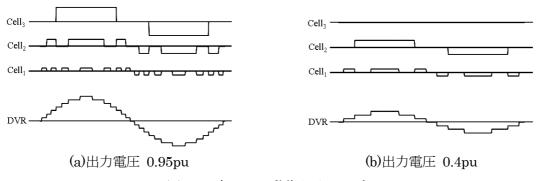

このような構成により、DVR は、図 4.2(a)に示す 15 レベルの交流電圧を出力できる。なお、 ☑ 4.2(a)では  $Cell_1$ ,  $Cell_2$ ,  $Cell_3$  を全て動作させているが、瞬低補償にあたっては、☑ 4.2(b)のように、電圧低下量に応じて必要なセルを動作させる。

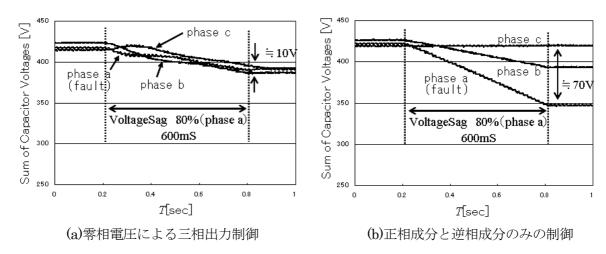

#### 4.2.2 零相電圧による三相出力制御の適用

ここでは、三相系統おける零相電圧設定の自由度[11]を活用し、いずれかの相に設置されたコンデンサの充電エネルギーを、他相に回生できることを示す。

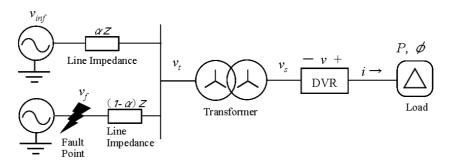

図 4.3 のモデルにおいて,変圧器一次側電圧 $v_t$ は,基準電圧 $v_{inf}$ と事故点の電圧 $v_f$ が,系統インピーダンス $\alpha Z$ , $(I-\alpha)Z$  の比により分圧されたものとする。連系点の系統電圧 $v_s$ は,非接地の変圧器を介することにより, $v_t$ から零相成分が除去されたものとなる。

ここで、基準電圧  $v_{inf}$  と負荷電流 i の、a 相、b 相、c 相の成分は、(4.1)式と(4.2)式で表されるものとする。ただし、太字はフェーザ表示である。また、単位は pu 値としている。 $e^{i\phi}$ は、基準電圧と位相差 $\phi$ で、振幅 1pu のフェーザを表す。

$$\mathbf{v}_{infa} = \mathbf{e}^{j0}$$

$$\mathbf{v}_{infb} = \mathbf{e}^{-j\frac{2\pi}{3}}$$

$$\mathbf{v}_{infc} = \mathbf{e}^{+j\frac{2\pi}{3}}$$

$$(4.1)$$

$$\mathbf{i}_{a} = \mathbf{e}^{j\phi}

\mathbf{i}_{b} = \mathbf{e}^{j\left(\phi - \frac{2\pi}{3}\right)}

\mathbf{i}_{c} = \mathbf{e}^{j\left(\phi + \frac{2\pi}{3}\right)}$$

(4.2)

このモデルにおいて、二相短絡(2LS)、一相地絡(1LG)および二相地絡(2LG)による瞬低が発生した場合の系統電圧 $v_s$ を、(4.3)式、(4.4)式、(4.5)式に示す。

図 4.3 系統モデル (単線結線図)

$$\mathbf{v}_{sa_{2LS}} = \mathbf{e}^{j0}$$

$$\mathbf{v}_{sb_{2LS}} = \mathbf{e}^{-j\frac{2\pi}{3}} - \frac{\sqrt{3}\alpha}{2} \mathbf{e}^{-j\frac{\pi}{2}}$$

$$\mathbf{v}_{sc_{2LS}} = \mathbf{e}^{+j\frac{2\pi}{3}} - \frac{\sqrt{3}\alpha}{2} \mathbf{e}^{+j\frac{\pi}{2}}$$

(4.3)

$$\mathbf{v}_{sa\_1LG} = \mathbf{e}^{j0} - \frac{2\alpha}{3} \mathbf{e}^{j0}$$

$$\mathbf{v}_{sb\_1LG} = \mathbf{e}^{-j\frac{2\pi}{3}} - \frac{\alpha}{3} \mathbf{e}^{j\pi}$$

$$\mathbf{v}_{sc\_1LG} = \mathbf{e}^{+j\frac{2\pi}{3}} - \frac{\alpha}{3} \mathbf{e}^{j\pi}$$

(4.4)

$$\mathbf{v}_{sa_{2}LG} = \mathbf{e}^{j0} - \frac{\alpha}{3} \mathbf{e}^{j0}$$

$$\mathbf{v}_{sb_{2}LG} = \mathbf{e}^{-j\frac{2\pi}{3}} - \frac{\sqrt{3}\alpha}{2} \mathbf{e}^{-j\frac{\pi}{2}} - \frac{\alpha}{6} \mathbf{e}^{j\pi}$$

$$\mathbf{v}_{sc_{2}LG} = \mathbf{e}^{+j\frac{2\pi}{3}} - \frac{\sqrt{3}\alpha}{2} \mathbf{e}^{+j\frac{\pi}{2}} - \frac{\alpha}{6} \mathbf{e}^{j\pi}$$

(4.5)

DVR は、補償電圧の正相成分と逆相成分の和  $v_a$ 、 $v_b$ 、 $v_c$ 、基準電圧  $v_{infa}$ 、 $v_{infb}$ 、 $v_{infc}$ 、および系統電圧  $v_{sa}$ 、 $v_{sb}$ 、 $v_{sc}$  の間に、次の関係を満たすよう動作するものとする。

$$\mathbf{v}_{a} = \mathbf{v}_{infa} - \mathbf{v}_{sa} \\

\mathbf{v}_{b} = \mathbf{v}_{infb} - \mathbf{v}_{sb} \\

\mathbf{v}_{c} = \mathbf{v}_{infc} - \mathbf{v}_{sc}$$

(4.6)

さらに、DVR は、 $v_a$ 、 $v_b$ 、 $v_c$  に零相電圧  $v_0$  を加えた補償電圧を出力するものとする。このとき、負荷に供給される相電圧  $v_{La}$ 、 $v_{Lb}$ 、 $v_{Lc}$ と、線間電圧  $v_{Lab}$ 、 $v_{Lbc}$ 、 $v_{Lca}$  は、(4.7)式と(4.8)式の通りとなる。相電圧には $v_0$ が現れるが、線間電圧は $v_0$ の影響を受けない。三相負荷は線間電圧で駆動されるため、補償電圧に任意の $v_0$  を加えても、瞬低補償は可能となる。

$$\mathbf{v}_{La} = \mathbf{v}_{sa} + (\mathbf{v}_{a} + \mathbf{v}_{0}) = \mathbf{v}_{infa} + \mathbf{v}_{0}$$

$$\mathbf{v}_{Lb} = \mathbf{v}_{sb} + (\mathbf{v}_{b} + \mathbf{v}_{0}) = \mathbf{v}_{infb} + \mathbf{v}_{0}$$

$$\mathbf{v}_{Lc} = \mathbf{v}_{sc} + (\mathbf{v}_{c} + \mathbf{v}_{0}) = \mathbf{v}_{infc} + \mathbf{v}_{0}$$

$$(4.7)$$

$$\mathbf{v}_{Lab} = \mathbf{v}_{La} - \mathbf{v}_{Lb} = \mathbf{v}_{infa} - \mathbf{v}_{infb}$$

$$\mathbf{v}_{Lbc} = \mathbf{v}_{Lb} - \mathbf{v}_{Lc} = \mathbf{v}_{infb} - \mathbf{v}_{infc}$$

$$\mathbf{v}_{Lca} = \mathbf{v}_{Lc} - \mathbf{v}_{La} = \mathbf{v}_{infc} - \mathbf{v}_{infa}$$

$$(4.8)$$

DVR の三相出力制御には、第3章で導出した(3.15)式と同様に、零相電圧に(4.9)式の $v_0$ を用いる[10]。ただし、演算"・"は、フェーザを複素ベクトルとして取り扱った場合の内積である。

$$\mathbf{v}_{0} = \frac{\Delta P_{a}(\mathbf{i}_{b} \cdot \mathbf{i}_{c})\mathbf{i}_{a} + \Delta P_{b}(\mathbf{i}_{c} \cdot \mathbf{i}_{a})\mathbf{i}_{b} + \Delta P_{c}(\mathbf{i}_{a} \cdot \mathbf{i}_{b})\mathbf{i}_{c}}{|\mathbf{i}_{a}|^{2}|\mathbf{i}_{b}|^{2} - (\mathbf{i}_{a} \cdot \mathbf{i}_{b})^{2}}$$

$$\Delta P_{a} = (\mathbf{v}_{infa} - \mathbf{v}_{sa}) \cdot \mathbf{i}_{a} - \frac{1}{3} \sum_{k=a,b,c} (\mathbf{v}_{infk} - \mathbf{v}_{sk}) \cdot \mathbf{i}_{k}$$

$$\Delta P_{b} = (\mathbf{v}_{infb} - \mathbf{v}_{sb}) \cdot \mathbf{i}_{b} - \frac{1}{3} \sum_{k=a,b,c} (\mathbf{v}_{infk} - \mathbf{v}_{sk}) \cdot \mathbf{i}_{k}$$

$$\Delta P_{c} = (\mathbf{v}_{infc} - \mathbf{v}_{sc}) \cdot \mathbf{i}_{c} - \frac{1}{3} \sum_{k=a,b,c} (\mathbf{v}_{infk} - \mathbf{v}_{sk}) \cdot \mathbf{i}_{k}$$

$$(4.9)$$

(4.9)式と、(4.1)式 $\sim$ (4.5)式を用いて計算した $\nu_0$ を、(4.10)式、(4.11)式、(4.12)式に示す。

$$\mathbf{v}_{0\_2LS} = \frac{\alpha}{2} \mathbf{e}^{j2\phi} \tag{4.10}$$

$$\mathbf{v}_{0_{\text{_}1LG}} = -\frac{\alpha}{3} \mathbf{e}^{j2\phi}$$

.....(4.11)

$$\mathbf{v}_{0\_2\mathrm{LG}} = \frac{\alpha}{3} \mathbf{e}^{j2\phi} \dots (4.12)$$

次に、これらを用いて瞬低補償を行った場合の補償電力を、(4.13)式、(4.14)式、(4.15)式に示す。いずれも、三相等しく出力されている。

$$P_{a_{2LS}} = \left(\mathbf{v}_{infa} - \mathbf{v}_{sa_{2LS}} + \mathbf{v}_{0_{2LS}}\right) \cdot \mathbf{i}_{a} = \frac{\alpha}{2} \mathbf{e}^{j2\phi} \cdot \mathbf{e}^{j\phi} = \frac{\alpha}{2} \cos \phi$$

$$P_{b_{2LS}} = \left(\mathbf{v}_{infb} - \mathbf{v}_{sb_{2LS}} + \mathbf{v}_{0_{2LS}}\right) \cdot \mathbf{i}_{b} = \left(\frac{\sqrt{3}\alpha}{2} \mathbf{e}^{-j\frac{\pi}{2}} + \frac{\alpha}{2} \mathbf{e}^{j2\phi}\right) \cdot \mathbf{e}^{j\left(\phi - \frac{2\pi}{3}\right)} = \frac{\alpha}{2} \cos \phi$$

$$P_{c_{2LS}} = \left(\mathbf{v}_{infc} - \mathbf{v}_{sc_{2LS}} + \mathbf{v}_{0_{2LS}}\right) \cdot \mathbf{i}_{c} = \left(\frac{\sqrt{3}\alpha}{2} \mathbf{e}^{j\frac{\pi}{2}} + \frac{\alpha}{2} \mathbf{e}^{j2\phi}\right) \cdot \mathbf{e}^{j\left(\phi + \frac{2\pi}{3}\right)} = \frac{\alpha}{2} \cos \phi$$

$$(4.13)$$

$$P_{a_{\perp}\text{ILG}} = \left(\mathbf{v}_{infa} - \mathbf{v}_{sa_{\perp}\text{ILG}} + \mathbf{v}_{0_{\perp}\text{ILG}}\right) \cdot \mathbf{i}_{a} = \left(\frac{2\alpha}{3} \mathbf{e}^{j0} - \frac{\alpha}{3} \mathbf{e}^{j2\phi}\right) \cdot \mathbf{e}^{j\phi} = \frac{\alpha}{3} \cos \phi$$

$$P_{b_{\perp}\text{ILG}} = \left(\mathbf{v}_{infb} - \mathbf{v}_{sb_{\perp}\text{ILG}} + \mathbf{v}_{0_{\perp}\text{ILG}}\right) \cdot \mathbf{i}_{b} = \left(\frac{\alpha}{3} \mathbf{e}^{j\pi} - \frac{\alpha}{3} \mathbf{e}^{j2\phi}\right) \cdot \mathbf{e}^{j\left(\phi - \frac{2\pi}{3}\right)} = \frac{\alpha}{3} \cos \phi$$

$$P_{c_{\perp}\text{ILG}} = \left(\mathbf{v}_{infc} - \mathbf{v}_{sc_{\perp}\text{ILG}} + \mathbf{v}_{0_{\perp}\text{ILG}}\right) \cdot \mathbf{i}_{c} = \left(\frac{\alpha}{3} \mathbf{e}^{j\pi} - \frac{\alpha}{3} \mathbf{e}^{j2\phi}\right) \cdot \mathbf{e}^{j\left(\phi + \frac{2\pi}{3}\right)} = \frac{\alpha}{3} \cos \phi$$

$$(4.14)$$

$$P_{a_{-}2LG} = \left(\mathbf{v}_{infa} - \mathbf{v}_{sa_{-}2LG} + \mathbf{v}_{0_{-}2LG}\right) \cdot \mathbf{i}_{a} = \left(\frac{\alpha}{3} \mathbf{e}^{j0} + \frac{\alpha}{3} \mathbf{e}^{j2\phi}\right) \cdot \mathbf{e}^{j\phi} = \frac{2\alpha}{3} \cos \phi$$

$$P_{b_{-}2LG} = \left(\mathbf{v}_{infb} - \mathbf{v}_{sb_{-}2LG} + \mathbf{v}_{0_{-}2LG}\right) \cdot \mathbf{i}_{b} = \left(\frac{\sqrt{3}\alpha}{2} \mathbf{e}^{-j\frac{\pi}{2}} + \frac{\alpha}{6} \mathbf{e}^{j\pi} + \frac{\alpha}{3} \mathbf{e}^{j2\phi}\right) \cdot \mathbf{e}^{j\left(\phi - \frac{2\pi}{3}\right)} = \frac{2\alpha}{3} \cos \phi$$

$$P_{c_{-}2LG} = \left(\mathbf{v}_{infc} - \mathbf{v}_{sc_{-}2LG} + \mathbf{v}_{0_{-}2LG}\right) \cdot \mathbf{i}_{c} = \left(\frac{\sqrt{3}\alpha}{2} \mathbf{e}^{j\frac{\pi}{2}} + \frac{\alpha}{6} \mathbf{e}^{j\pi} + \frac{\alpha}{3} \mathbf{e}^{j2\phi}\right) \cdot \mathbf{e}^{j\left(\phi + \frac{2\pi}{3}\right)} = \frac{2\alpha}{3} \cos \phi$$

39

## 4.3 零相電圧による三相出力制御に関する原理実証試験[9]

ここでは、原理実証を目的とし、簡易演算で求める零相電圧を正相成分と逆相成分からなる補 償電圧に加えることにより、三相出力を制御できることを示す。

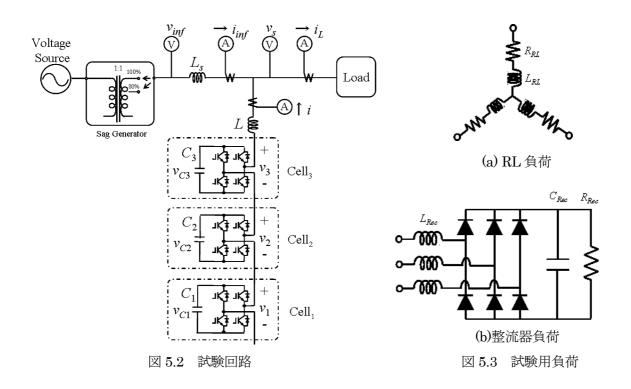

#### 4.3.1 試験回路の構成

三相電源, 4 直列-2 進ハイブリッド CLMC を用いた DVR, および誘導性負荷を用いて, 図 4.4 のように試験回路を構成する。回路定数は,表 4.1 に示す通りである。

三相電源 $v_{inf}$ の相電圧波高値 $V_{PK}$ は390Vであり、出力側に設けた瞬低発生装置(Sag Generator)により、各相個別に20%、40%、60%、80%の電圧低下を発生できる。

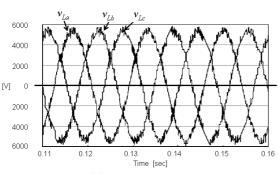

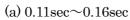

DVRは、Cell<sub>1</sub>、Cell<sub>2</sub>、Cell<sub>3</sub>、Cell<sub>4</sub>を直列に接続して構成する。DC電源には、予め充電されたコンデンサ $C_1$ 、 $C_2$ 、 $C_3$ 、 $C_4$ を用いる。個々のセルのDC電圧 $v_{C1}$ 、 $v_{C2}$ 、 $v_{C3}$ 、 $v_{C4}$ は、1:2:4:8の比率を基準とする。それらの初期値 $v_{C1}$ \*、 $v_{C2}$ \*、 $v_{C3}$ \*、 $v_{C4}$ \*は、CLMCが出力できる最大電圧が電源の波高値 $V_{PK}$ の約1割増しとなるよう、28V、56V、112V、224Vとする。これにより、DVRは、1レベルが28Vで31レベルの近似正弦波を出力できる。 $C_1$ 、 $C_2$ 、 $C_3$ 、 $C_4$ の容量は、初期充電状態から定格電圧478Vと定格電流100Aを0.2秒間出力したときに、充電電圧の低下が10%程度となるよう、0.75F、1.5F、3.0F、6.0Fとする。なお、0.2秒は瞬低発生総数の8割程度に対応できるよう[1]、また、コンデンサ容量は後述する(4.16)式~(4.20)式を用いて定めたものである。

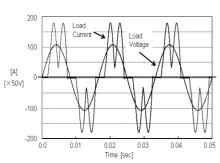

また、直列に接続された $2.0\Omega$ の抵抗と2.7mHのリアクトルをY結線し、定格100kVA、力率0.9の試験用負荷を構成する。

制御系の構成は、第2章の図2.10に示したものと、ほぼ同様である。

図 4.4 試験回路の単線結線図

表 4.1 回路定数

| Voltage Source v <sub>inf</sub>   |   | 3φ AC478V, 60Hz | Capacitance,    | C4, VC4 *            | 0.75F, 224V |

|-----------------------------------|---|-----------------|-----------------|----------------------|-------------|

| Peak Line Voltage V <sub>PK</sub> |   | 390V            | Initial Voltage | C3, VC3              | 1.5F. 112V  |

| Rated Power                       | P | 100kVA          | inniai (onage   | *                    |             |

| Load                              | R | 2.0Ω            |                 | $C_2, v_{C2}$        | 3.0F, 56V   |

| (100kW, pf 0.9)                   | L | 2.7mH           |                 | $C_1$ , $v_{C1}^{*}$ | 6.0F, 28V   |

## 4.3.2 制御手法

三相均等な補償エネルギーの出力を実現するにあたり、各セルの DC 電圧を常時監視し、それらで a 相、b 相、c 相の基準電圧を重み付けして、零相電圧  $v_0$  を合成する方法を試みる。

まず、零相電圧 $v_0$ と DC 電圧の関係を、単純な形で定式化する。図 4.4 に示した DVR が瞬低補償を行った際には、コンデンサの充電エネルギーと出力した補償エネルギーの間に、(4.16)式の関係が成り立つ。 $v_{Ckj}$ は、k 相の  $Cell_j$  (k=a,b,c, j=1,2,3,4) の DC 電圧、 $C_1$ ,  $C_2$ ,  $C_3$ ,  $C_4$ はコンデンサの容量を表す。右辺は、期間 $[t, t+T_e]$ において DVR のk 相(k=a,b,c)が出力した補償エネルギーであり、基準電圧 $v_{infk}$ 、系統電圧 $v_{sk}$ 、零相電圧 $v_0$ 、および負荷電流 $i_k$ より定まる。

$$\sum_{j=1}^{4} \frac{1}{2} C_{j} \left[ v_{Ckj}(t)^{2} - v_{Ckj}(t + T_{e})^{2} \right] = \left[ \left( \mathbf{v}_{injk} - \mathbf{v}_{sk} + \mathbf{v}_{0} \right) \cdot \mathbf{i}_{k} \right] \times T_{e}$$

(4.16)

ここで、個々のセルの DC 電圧の比は 1:2:4:8 に維持できているとし、時刻 t における CLMC のコンデンサの充電エネルギーを、次のように近似する。

$$\sum_{j=1}^{4} \frac{1}{2} C_j \cdot v_{Ckj}(t)^2 = \sum_{j=1}^{4} \frac{1}{2} C_j \cdot \left( \frac{2^{j-1}}{15} \sum_{n=1}^{4} v_{Ckn}(t) \right)^2 = \sum_{j=1}^{4} \frac{1}{2} \frac{2^{2j-2}}{15^2} C_j \cdot \left( \sum_{n=1}^{4} v_{Ckn}(t) \right)^2 = \frac{1}{2} C \cdot v_{Ck}(t)^2 \cdots (4.17)$$

ただし、 $v_{Ck}$  と C は、等価的な DC 電圧とコンデンサ容量として、次のように定義する。

$$v_{Ck}(t) = \sum_{n=1}^{4} v_{Ckn}(t)$$

(4.18)

$$C = \sum_{j=1}^{4} \frac{2^{2j-2}}{15^2} C_j \tag{4.19}$$

(4.16)式 $\sim$ (4.19)式より、零相電圧  $v_0$  と DC 電圧  $v_{Ck}$  との間に、次の単純な関係が得られる。

$$\frac{1}{2}C \cdot v_{Ck}(t)^2 - \frac{1}{2}C \cdot v_{Ck}(t + T_e)^2 = \left[ \left( \mathbf{v}_{infk} - \mathbf{v}_{sk} + \mathbf{v}_0 \right) \cdot \mathbf{i}_k \right] \times T_e$$

(4.20)

次に、 $v_0$ の微小変化と $v_{Ck}$ の変化の関係から、本試験で用いる $v_0$ の合成方法を導出する。まず、 $v_0$ の微小変化  $\Delta v_{Ok}(t)\cdot v_{infk}$  と、DC 電圧の変化  $\Delta v_{Ck}(t+T_e)$  との関係を、次のように近似する。

$$\frac{1}{2}C \cdot v_{Ck}(t+T_e)^2 - \frac{1}{2}C \cdot \left[v_{Ck}(t+T_e) - \Delta v_{Ck}(t+T_e)\right]^2 = \Delta v_{0k}(t) \cdot \left(\mathbf{v}_{infk} \cdot \mathbf{i}_k\right) \cdot T_e$$

(4.21)

さらに、 $\Delta v_{Ck}(t+T_e)$ を時刻 t において存在した k 相の DC 電圧  $v_{Ck}$ の平均値との誤差と考え、それを時間  $T_e$  で補正するための成分として、 $\Delta v_{Ok}(t)$ を次式のように近似する。なお、 $T_e$ は十分小さく、 $\Delta v_{Ck}(t+T_e)$ の二乗の項を無視し、また、 $v_{Ck}(t+T_e)$ は  $v_{Ck}(t)$ と等しいと近似した。