| Title        | Insight into enhanced field-effect mobility of 4H-SiC MOSFET with Ba incorporation studied by Hall effect measurements |

|--------------|------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Fujita, Eigo; Sometani, Mitsuru; Hatakeyama,<br>Tetsuo et al.                                                          |

| Citation     | AIP Advances. 2018, 8(8), p. 085305                                                                                    |

| Version Type | VoR                                                                                                                    |

| URL          | https://hdl.handle.net/11094/85477                                                                                     |

| rights       | © 2018 Author(s). This article is licensed under a Creative Commons Attribution 4.0 International License.             |

| Note         |                                                                                                                        |

## The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

## Insight into enhanced field-effect mobility of 4H-SiC MOSFET with Ba incorporation studied by Hall effect measurements

Cite as: AIP Advances **8**, 085305 (2018); https://doi.org/10.1063/1.5034048 Submitted: 09 April 2018 • Accepted: 27 July 2018 • Published Online: 07 August 2018

Eigo Fujita, 🔟 Mitsuru Sometani, Tetsuo Hatakeyama, et al.

## ARTICLES YOU MAY BE INTERESTED IN

Characterization of SiO<sub>2</sub>/SiC interface states and channel mobility from MOSFET characteristics including variable-range hopping at cryogenic temperature AIP Advances 8, 045217 (2018); https://doi.org/10.1063/1.5027695

Ideal phonon-scattering-limited mobility in inversion channels of 4H-SiC(0001) MOSFETs with ultralow net doping concentrations

Applied Physics Letters 115, 132102 (2019); https://doi.org/10.1063/1.5115304

Study of  $SiO_2/4H$ -SiC interface nitridation by post-oxidation annealing in pure nitrogen gas AIP Advances 5, 097134 (2015); https://doi.org/10.1063/1.4930980

## Insight into enhanced field-effect mobility of 4H-SiC MOSFET with Ba incorporation studied by Hall effect measurements

Eigo Fujita,<sup>1</sup> Mitsuru Sometani,<sup>2</sup> Tetsuo Hatakeyama,<sup>2</sup> Shinsuke Harada,<sup>2</sup> Hiroshi Yano,<sup>3</sup> Takuji Hosoi,<sup>1</sup> Takayoshi Shimura,<sup>1</sup> and Heiji Watanabe<sup>1,a</sup>

<sup>1</sup>Graduate School of Engineering, Osaka University, Suita, Osaka 565-0871, Japan

(Received 9 April 2018; accepted 27 July 2018; published online 7 August 2018)

Improved performance in 4H-SiC metal-oxide-semiconductor field-effect transistors (MOSFETs) by incorporating Ba into insulator/SiC interfaces was investigated by using a combination of the Hall effect and split capacitance-voltage measurements. It was found that a moderate annealing temperature causes negligible metal-enhanced oxidation, which is rather beneficial for increments in field-effect mobility ( $\mu_{FE}$ ) of the FETs together with suppressed surface roughness of the gate oxides. The combined method revealed that, while severe  $\mu_{FE}$  degradation in SiC-MOSFETs is caused by a reduction of effective mobile carriers due to carrier trapping at the SiO<sub>2</sub>/SiC interfaces, Ba incorporation into the interface significantly increases mobile carrier density with greater impact than the widely-used nitrided interfaces. © 2018 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution (CC BY) license (http://creativecommons.org/licenses/by/4.0/). https://doi.org/10.1063/1.5034048

Silicon carbide (SiC) is a wide bandgap semiconductor that has great potential in power device applications. In addition to the superior physical properties of SiC, such as a very high breakdown field and good thermal conductivity over conventional Si, silicon dioxide (SiO<sub>2</sub>) as a gate insulator in metal-oxide-semiconductor field-effect transistors (MOSFETs) can be grown by thermal oxidation of SiC substrates. However, the field-effect mobility ( $\mu_{FE}$ ) that determines the on-resistance of SiC-MOSFETs is still far below expectations.<sup>2</sup> This is due to the poor quality of thermally-grown SiO<sub>2</sub>/SiC interfaces with a significant amount of electrical defects, 3,4 which leads to carrier trapping and scattering in the inversion channels of FETs. Although SiC-MOSFETs with a conventional thermal oxide exhibit low μ<sub>FE</sub> values, typically less than 10 cm<sup>2</sup>/Vs,<sup>2</sup> the incorporation of particular elements, i.e., hydrogen,<sup>5</sup> nitrogen,<sup>6-8</sup> and phosphorous<sup>9</sup> atoms, has been proven to passivate interface defects. Among these elements, nitrogen is known to provide reproducible  $\mu_{FF}$  enhancement with minor drawbacks. Consequently, interface nitridation with high-temperature annealing in a nitric oxide (NO) ambience is widely used for fabricating stateof-the-art commercial SiC-MOSFETs. However, the resulting peak mobility of around 35 cm<sup>2</sup>/Vs is insufficient, 8 so further improvement is indispensable for the development of next-generation SiC-MOSFETs.

The impacts of incorporating alkali metal and alkaline earth metal atoms into the SiO<sub>2</sub>/SiC interfaces on mobility enhancement have been previously discussed. As with Si oxidation, <sup>10–13</sup> these elements are also known to have catalytic effects in thermal oxidation of SiC surfaces called metal-enhance oxidation (MEO). <sup>14–21</sup> The MEO phenomenon is beneficial for reducing oxidation temperatures and time, especially for SiC-MOS fabrication. However, the use of alkali metals, such

<sup>&</sup>lt;sup>2</sup>National Institute of Advanced Industrical Science and Technology, Tsukuba, Ibaraki 305-8569, Japan

<sup>&</sup>lt;sup>3</sup>Graduate School of Pure and Applied Sciences, University of Tsukuba, Tsukuba, Ibaraki 305-8573, Japan

<sup>&</sup>lt;sup>a</sup>E-mail: watanabe@mls.eng.osaka-u.ac.jp

as sodium and potassium, is unacceptable for practical applications owing to an ion drift (mobile charges) in the gate stacks causing severe bias-temperature instability (BTI) of MOSFETs. Recently, Lichtenwalner *et al.* demonstrated high mobility SiC-MOSFETs by incorporating barium (Ba) into the SiO<sub>2</sub>/SiC interface, <sup>17</sup> in which the BTI due to the ion drift was remarkably suppressed thanks to the strong chemical bonding of Ba atoms to form a stable silicate phase. In the pioneering research, a few monolayer thick Ba films (ranging from 0.6 to 0.8 nm) were formed beneath the SiO<sub>2</sub> cap dielectrics, then oxidation annealing (MEO) in an  $O_2/N_2$  gas mixture was conducted at 900 or 950°C. A subsequent study also reported the effect of stress relaxation near the Ba-passivated SiO<sub>2</sub>/SiC interface on improved electrical properties. <sup>18</sup>

In spite of the promising aspects of SiC-MOSFETs with Ba-incorporated interfacial layers, very few cases of Ba-MEO have been reported so far. Previous research was done with limited conditions (Ba thickness ranging from 0.6 to 0.8 nm and MEO at 900 or 950°C). <sup>17</sup> Moreover, regarding mobility enhancement mechanisms, there has been no systematic report other than the strain analysis mentioned above. Despite some drawbacks of Ba-MEO relating to surface morphology and leakage current as described later, we think that understanding of mobility enhancement mechanisms provides a helpful clue to solve the long-standing problem of degraded field-effect mobility in SiC-MOSFETs. In the current study, we therefore explored optimal Ba-MEO conditions for further improvement of the SiC-MOS interface in the first step. Then, mechanisms of Ba-induced  $\mu_{FE}$  increment were investigated by discriminating free (mobile) and trapped carriers from the total charge in the inversion channel by means of a combination of the Hall effect and split capacitance-voltage (C-V) measurements of SiC-MOSFETs.

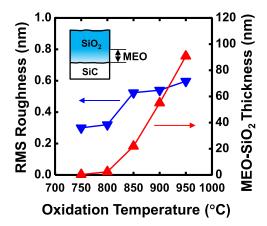

In our previous study, a 0.5-nm-thick metallic Ba layer was directly deposited on a 4H-SiC(0001) substrate using a Knudsen effusion cell at room substrate temperature, followed by capping with the chemical vapor deposition (CVD) grown  $SiO_2$  film. Then, MEO at  $950^{\circ}C$  was conducted in oxygen ambience.  $^{19,20}$  We observed a reduction of interface state density ( $D_{it}$ ) for the Ba-incorporated SiC-MOS capacitors after the prolonged MEO over four hours, but it was found that significant surface roughness leading to harmful electric field concentration in the gate dielectric was induced even on the CVD-grown  $SiO_2$  surface with the MEO. Therefore, we reconsidered the oxidation temperature to improve surface morphology. Figure 1 shows the changes in the surface roughness and additive oxide growth depending on the MEO temperature. In this experiment, since MEO proved to occur with just a tiny amount of Ba atoms with an areal density on the order of  $10^{14}$  cm<sup>-2</sup>,  $^{19}$  a minimal Ba layer (0.1 nm thick) was directly deposited on the wet-cleaned 4H-SiC(0001) substrate with an n-type epilayer ( $N_d$ :  $1 \times 10^{16}$  cm<sup>-3</sup>) purposed for improving surface morphology. The sample was covered with a 35-nm-thick  $SiO_2$  capping layer with a plasma-enhanced CVD using

FIG. 1. Oxidation temperature dependence of additive SiO<sub>2</sub> growth and surface morphology induced by Ba-MEO. CVD-SiO<sub>2</sub>(35 nm)/Ba(0.1 nm)/SiC stacked structures were annealed in O<sub>2</sub> ambience at various temperatures for 4 h. The additive oxide growth was estimated by subtracting initial thickness of CVD-SiO<sub>2</sub> (35 nm) from the measured value. The changes in the RMS roughness value (blue symbols) and additive oxide growth (red symbols) caused by Ba-MEO were plotted as a function of MEO temperature.

tetraethyl orthosilicate (TEOS) and oxygen  $(O_2)$  mixtures as reactant gases, followed by oxidation (Ba-MEO) at various temperatures in pure  $O_2$  ambience for four hours. The resulting surface morphology (root mean square (RMS) roughness value) and thickness of the newly formed  $SiO_2$  by Ba-MEO were evaluated by using atomic force microscopy (AFM) and spectroscopic ellipsometry (SE). As shown in Fig. 1, enhanced SiC oxidation by incorporating Ba was clearly observed at temperatures above  $850^{\circ}$ C (red symbols). It should be noted that, compared with our previous result with the 0.5-nm-thick Ba interfacial layer (RMS = 1.97 nm),  $^{20}$  the RMS roughness values were significantly reduced to less than 0.6 nm by minimizing the amount of Ba atoms for MEO, indicating an impact with a reduction of the excess Ba atoms in an improved gate oxide surface morphology. In addition, the RMS values of the CVD-grown  $SiO_2$  films remained almost constant at around 0.3 nm for the MEO temperatures below  $850^{\circ}$ C, which is a reasonable trend because additive Ba-MEO was negligible, probably a few monolayers in thickness, at this temperature range.

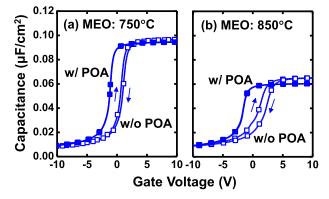

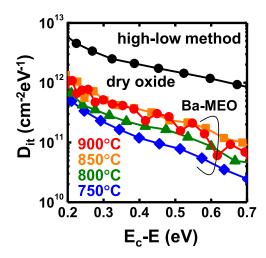

The electrical properties of these Ba-incorporated SiO<sub>2</sub>/SiC interfaces were investigated by conventional C-V measurements. After performing Ba-MEO at various temperatures ranging from 750 to 900°C, Al gate electrodes and back contacts were formed by vacuum evaporation to fabricate SiC-MOS capacitors. Some samples were subjected to the post MEO annealing (POA) in pure N<sub>2</sub> ambience at 950°C for 30 min prior to electrode formation to improve the quality of the CVD-SiO<sub>2</sub> film and/or Ba-incorporated SiO<sub>2</sub>/SiC interface. Figure 2 represents typical C-V characteristics of the SiC-MOS capacitors with and without POA in N<sub>2</sub> ambience. Bidirectional C-V curves were taken with 1 MHz measurement frequency, in which gate voltage was swept from depletion (-10 V) to accumulation (+10 V), and vice versa at room temperature. For both cases (MEO at 750 and 850°C), maximum accumulation capacitance coincides with the physical thickness of the gate oxides estimated by SE analysis. Moreover, whereas clockwise C-V hysteresis was observed before the POA (open symbols), hysteresis-free C-V curves were achieved with the POA regardless of the MEO temperature (closed symbols), indicating a reduction of the slow traps within the bulk portion of the CVD-SiO<sub>2</sub> films. 22 The Dit values of the SiC-MOS capacitors were evaluated using a high-low method and the change in D<sub>it</sub> distribution depending on the MEO temperature is summarized in Fig. 3. It's clear that a reduced Dit was achieved with the Ba-MEO technique compared to results for the reference dry oxide (see black symbols). More interestingly, the lower Dit values were obtained with the lower MEO temperatures. This finding implies that additive thick oxide growth caused by Ba-MEO is not crucial to the improvement of interface quality in SiC-MOS devices. Actually, our supplementary experiments also revealed that the Dit distribution is dependent not severely on the MEO time, but on the oxidation temperature (data not shown). Therefore, considering the morphology and uniformity of the SiO<sub>2</sub> gate oxides, we concluded that Ba-MEO with a sub-monolayer of Ba atoms (0.1 nm thick) and low MEO temperature (around 750°C) are plausible conditions for fabricating advanced SiC-MOSFETs.

FIG. 2. Typical bidirectional C-V characteristics of Ba-incorporated SiC-MOS capacitors fabricated by MEO with a 0.1-nm-thick Ba interfacial layer at (a)  $750^{\circ}$ C and (b)  $850^{\circ}$ C for 4 h. Results with and without POA in  $N_2$  ambience are indicated by the filled and open symbols, respectively.

FIG. 3. Change in the energy distribution of  $D_{it}$  for Ba-incorporated SiC-MOS capacitors depending on the MEO temperature. Ba-MEO was conducted at various temperatures ranging from 750 to 900°C for 4 h.  $D_{it}$  values were estimated using a high-low method. All SiO<sub>2</sub>/SiC structures received POA prior to electrode deposition.  $D_{it}$  distribution taken from the reference device with a thermal oxide (dry oxide) grown at  $1150^{\circ}$ C [20] was also shown.

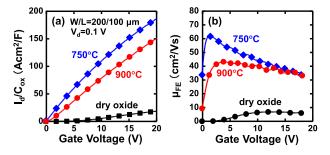

Figure 4 represents the basic performance of Ba-incorporated SiC-MOSFETs fabricated with MEO at 750 or 900°C, followed by POA at 950°C for 30 min. Here, the MEO time was shortened to 1 hour for reducing variation in the gate oxide thickness especially for MEO at 900°C. The results for the reference device with a pure  $SiO_2$  gate dielectric grown by dry oxidation at 1300°C are also shown. To compare transistor performance with various gate oxides having different capacitance equivalent thickness (CET), drain current ( $I_d$ ) was normalized by the gate oxide capacitance ( $C_{ox}$ ). As shown in Fig. 4(a), we confirmed there was a significant impact of Ba incorporation into the  $SiO_2/SiC$  interface on the  $I_d$  enhancement in SiC-MOSFETs. Figure 4(b) shows  $\mu_{FE}$  of these SiC-MOSFETs with and without Ba as determined from the transfer characteristics. The peak mobility of the SiC-MOSFET fabricated by Ba-MEO at 750°C was estimated to be 62 cm²/Vs, which is higher than those for other devices in Fig. 4 and the nitrided interface formed by high-temperature NO annealing. These results again indicate an importance in the existence of Ba atoms at the  $SiO_2/SiC$  interface rather than the additive thick oxide growth by MEO.

Recently, one of the authors, Hatakeyama, *et al.* discussed mechanisms of  $\mu_{FE}$  degradation in SiC-MOSFETs on the basis of Hall effect measurements combined with the common FET characterizations, in which they discriminated free carriers that contributed to the actual  $I_d$  from the inversion charge accumulated at the interface. The inversion charge, i.e. total charge density ( $n_{total}$ ) was characterized by an established split C-V method. The free carrier density ( $n_{free}$ ) at the interface depending on the applied gate voltage ( $V_g$ ) was determined on the basis of Hall effect measurements

FIG. 4. Basic performance of Ba-incorporated SiC-MOSFETs fabricated with MEO at 750 or 900°C for 1 h: (a)  $I_d$ - $V_g$  characteristics normalized by  $C_{ox}$ , and (b)  $\mu_{FE}$  extracted from the transfer characteristics. Results from a reference thermal oxide (dry oxide) formed at 1300°C without Ba incorporation are also shown. The gate width and length of the devices (W/L) and drain voltage for  $I_d$ - $V_g$  measurements are indicated.

FIG. 5. Analysis of  $\mu_{FE}$  enhancement factors in Ba-incorporated SiC-MOSFETs: (a) relationship between the  $n_{total}$  and  $n_{free}$ , respectively, extracted from the split C-V and Hall effect measurements plotted as a function of the gate voltage  $(V_g-V_{th})$ . Here, the carrier density (n) was normalized by CET, (b) the  $\mu_{Hall}$  plotted as a function of carrier density accumulated in the inversion channel. Ba-MEO temperatures and results from the reference device with the pure thermal oxide (dry oxide) are indicated in each figure.

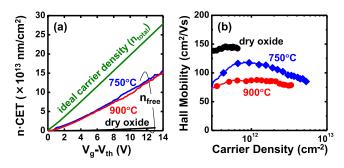

using the van der Pauw technique. Consequently, the  $V_g$ -dependent trapped carrier density ( $n_{trap}$ ) was extracted by subtracting  $n_{free}$  from  $n_{total}$  for each device. Moreover, Hall effect measurements provided net mobility for the free carriers, which is Hall mobility (µ<sub>Hall</sub>) in the inversion channel. We applied this combination method to quantitatively analyze the impact of incorporating Ba into the SiO<sub>2</sub>/SiC interface by assuming a Hall scattering factor of unity. The split C-V measurements were conducted at 10 Hz using the ultra-low-frequency measurement system to extract the gate-channel capacitance. The p-well region was grounded, DC bias was applied to the gate electrode, and then an AC signal with an oscillation level of 20 mV was input to the source and drain regions. Figure 5(a) shows both n<sub>free</sub> and ntotal for the SiC-MOSFETs with and without Ba incorporation, in which the charge densities (vertical axis) were normalized by CET to compare the carrier density ratio (nfree/ntotal) of the devices with different gate oxide thickness. Since the normalized ntotal values estimated from the split C-V method were mostly identical for the Ba-incorporated SiC-MOSFETs, they were represented by a single trend line labeled as "ideal carrier density" in Fig. 5. As previously reported, only three percent of the ideal carriers counted as mobile carriers in the case of the reference thermal oxide (black line in Fig. 5(a)). It should be noted that the free carrier ratio significantly increased to 55% with Ba-incorporation into the SiO<sub>2</sub>/SiC interfaces and that MEO conditions had little or no influence on the carrier ratio in the temperature range. Considering that the free carrier ratio extracted by the same procedure for the nitrided SiO<sub>2</sub>/SiC interface under the optimized conditions was still about 30%, the impact of incorporating Ba was more pronounced in terms of the generation of mobile carriers in SiC-MOS structures. As shown in Fig. 5(b), the  $\mu_{Hall}$  of the reference pure oxide was severely degraded as compared with the reported bulk mobility of 4H-SiC. This indicates that, even for the mobile free carriers, their transport at the SiO<sub>2</sub>/SiC interface was significantly disturbed by intrinsic electrical defects at the interface. The \(\mu\_{\text{Hall}}\) was found to further deteriorate with Ba incorporation relative to the reference pure oxide, which suggesting carrier scattering due to Ba-related defects at the interface. However, the  $\mu_{Hall}$  degradation was suppressed with Ba-MEO at 750°C. This accounts for the higher  $I_d$  and  $\mu_{FE}$ achieved with Ba-MEO at the lower annealing temperature shown in Fig. 4(b). From these findings, we concluded that performance improvement in Ba-incorporated SiC-MOSFETs was mostly due to a significant increase in the free carrier density that overcomes slight mobility degradation (µHall). Regarding the physical origins for the anomalous carrier trapping at the SiO<sub>2</sub>/SiC interface and for both carrier generation and scattering due to the Ba incorporation, we have no plausible model so far. However, since the obtained  $\mu_{\text{Hall}}$  values shown in Fig. 5(b) were still below expectations from the SiC bulk property as mentioned above, there might be room for further improvement in SiC-MOSFETs by means of Ba incorporation and additive combination techniques to increase inversion carrier mobility.

In summary, we investigated the impacts of incorporating Ba into SiO<sub>2</sub>/SiC interfaces on the performance of MOSFETs. Physical and electrical characterizations demonstrated that a sub-monolayer of Ba atoms and a moderate MEO temperature, together with high-temperature POA, are beneficial in Ba-MEO for improving SiC-MOS devices in terms of gate oxide morphology and interface

quality. We also found that, while most of the inversion carriers were trapped by electrical defects at the thermally-grown  $SiO_2/SiC$  interface, Ba incorporation significantly increased mobile free carriers that directly affect device performance. As a result, the high free carrier ratio up to 55% and increased  $\mu_{FE}$  about  $62~cm^2/Vs$  over the conventional nitrided interface were achieved by using the Ba-MEO technique.

This work was partly supported by the Council for Science, Technology, and Innovation (CSTI), Cross-ministerial Strategic Innovation Promotion Program (SIP), "Next-generation power electronics" (funding agency: NEDO).

- <sup>1</sup> A. Agarwal, S.-H. Ryu, J. Palmour, W. J. Choyke, H. Matsunami, and G. Pensl, in *Silicon Carbide—Recent Major Advances*, edited by W. J. Choyke (Springer, Berlin, 2004).

- <sup>2</sup> N. S. Saks and A. K. Agarwal, Appl. Phys. Lett. 77, 3281 (2000).

- <sup>3</sup> V. V. Afanas'ev, A. Stesmans, M. Bassler, G. Pensl, and M. J. Schulz, Appl. Phys. Lett. **76**, 336 (2000).

- <sup>4</sup> H. Watanabe, T. Hosoi, T. Kirino, Y. Kagei, Y. Uenishi, A. Chanthaphan, A. Yoshigoe, Y. Teraoka, and T. Shimura, Appl. Phys. Lett. 99, 021907 (2011).

- <sup>5</sup> K. Fukuda, S. Suzuki, T. Tanaka, and K. Arai, Appl. Phys. Lett. **76**, 1585 (2000).

- <sup>6</sup> H.-F. Li, S. Dimitrijev, H. B. Harrison, and D. Sweatman, Appl. Phys. Lett. **70**, 2028 (1997).

- <sup>7</sup> A. Chanthaphan, T. Hosoi, T. Shimura, and H. Watanabe, AIP Adv. 5, 97134 (2015).

- <sup>8</sup> T. Hatakeyama, Y. Kiuchi, M. Sometani, S. Harada, D. Okamoto, H. Yano, Y. Yonezawa, and H. Okumura, Appl. Phys. Express 10, 046601 (2017).

- <sup>9</sup> D. Okamoto, H. Yano, K. Hirata, T. Hatayama, and T. Fuyuki, IEEE Electron Device Lett. **31**, 710 (2010).

- <sup>10</sup> P. Soukiassian, T. M. Gentle, M. H. Bakshi, and Z. Hurych, J. Appl. Phys. 60, 4339 (1986).

- <sup>11</sup> E. G. Michel, E. M. Oellig, M. C. Asensio, and R. Miranda, Surf. Sci. **189**, 245 (1987).

- <sup>12</sup> C. A. Papageorgopoulos, S. Foulias, S. Kennou, and M. Kamaratos, Surf. Sci. 211, 991 (1989).

- <sup>13</sup> W. C. Fan and A. Ignatiev, Phys. Rev. B **44**, 3110 (1991).

- <sup>14</sup> Z. Zheng, R. E. Tressler, and K. E. Spear, Corros. Sci. 33, 545 (1992).

- <sup>15</sup> F. Allerstam, H. Ö. Ólafsson, G. Gudjónsson, D. Dochev, E. Ö. Sveinbjörnsson, T. Rödle, and R. Jos, J. Appl. Phys. 101, 124502 (2007).

- <sup>16</sup> B. R. Tuttle, S. Dhar, S.-H. Ryu, X. Zhu, J. R. Williams, L. C. Feldman, and S. T. Pantelides, J. Appl. Phys. 109, 23702 (2011).

- <sup>17</sup>D. J. Lichtenwalner, L. Cheng, S. Dhar, A. Agarwal, and J. W. Palmour, Appl. Phys. Lett. **105**, 182107 (2014).

- <sup>18</sup> J. H. Dycus, W. Xu, D. J. Lichtenwalner, B. Hull, J. W. Palmour, and J. M. LeBeau, Appl. Phys. Lett. 108, 201607 (2016).

- <sup>19</sup> A. Chanthaphan, Y. Katsu, T. Hosoi, T. Shimura, and H. Watanabe, Jpn. J. Appl. Phys. 55, 120303 (2016).

- <sup>20</sup> A. Chanthaphan, Y. Katsu, T. Hosoi, T. Shimura, and H. Watanabe, Mater. Sci. Forum 897, 340 (2017).

- <sup>21</sup> K. Muraoka, H. Sezaki, S. Ishikawa, T. Maeda, T. Sato, T. Kikkawa, and S.-I. Kuroki, Mater. Sci. Forum 897, 348 (2017).

- <sup>22</sup> M. Sometani, R. Hasunuma, M. Ogino, H. Kuribayashi, Y. Sugahara, A. Uedono, and K. Yamabe, Jpn. J. Appl. Phys. 51, 021101 (2012).

- <sup>23</sup> C. G. Sodini, T. W. Ekstedt, and J. L. Moll, Solid-State Electron. **25**, 833 (1982).