| Title        | Study of SiO2/4H-SiC interface nitridation by post-oxidation annealing in pure nitrogen gas           |

|--------------|-------------------------------------------------------------------------------------------------------|

| Author(s)    | Chanthaphan, Atthawut; Hosoi, Takuji; Shimura,<br>Takayoshi et al.                                    |

| Citation     | AIP Advances. 2015, 5(9), p. 097134                                                                   |

| Version Type | VoR                                                                                                   |

| URL          | https://hdl.handle.net/11094/85478                                                                    |

| rights       | © 2015 Author(s). This article is licensed under a Creative Commons Attribution 3.0 Unported License. |

| Note         |                                                                                                       |

## The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

## Study of SiO<sub>2</sub>/4H-SiC interface nitridation by post-oxidation annealing in pure nitrogen gas

Cite as: AIP Advances **5**, 097134 (2015); https://doi.org/10.1063/1.4930980 Submitted: 01 June 2015 • Accepted: 31 August 2015 • Published Online: 10 September 2015

🧓 Atthawut Chanthaphan, Takuji Hosoi, Takayoshi Shimura, et al.

## **ARTICLES YOU MAY BE INTERESTED IN**

Generation of very fast states by nitridation of the SiO<sub>2</sub>/SiC interface

Journal of Applied Physics 112, 024520 (2012); https://doi.org/10.1063/1.4740068

Ultrahigh-temperature rapid thermal oxidation of 4H-SiC(0001) surfaces and oxidation temperature dependence of SiO<sub>2</sub>/SiC interface properties

Applied Physics Letters 109, 182114 (2016); https://doi.org/10.1063/1.4967002

Accurate evaluation of interface state density in SiC metal-oxide-semiconductor structures using surface potential based on depletion capacitance

Journal of Applied Physics 111, 014502 (2012); https://doi.org/10.1063/1.3673572

## Study of SiO<sub>2</sub>/4H-SiC interface nitridation by post-oxidation annealing in pure nitrogen gas

Atthawut Chanthaphan, <sup>a</sup> Takuji Hosoi, <sup>b</sup> Takayoshi Shimura, and Heiji Watanabe *Graduate School of Engineering, Osaka University, 2-1 Yamadaoka*,

Suita, Osaka 565-0871, Japan

(Received 1 June 2015; accepted 31 August 2015; published online 10 September 2015)

An alternative and effective method to perform interface nitridation for 4H-SiC metal-oxide-semiconductor (MOS) devices was developed. We found that the high-temperature post-oxidation annealing (POA) in N<sub>2</sub> ambient was beneficial to incorporate a sufficient amount of nitrogen atoms directly into thermal SiO<sub>2</sub>/SiC interfaces. Although N<sub>2</sub>-POA was ineffective for samples with thick thermal oxide layers, interface nitridation using N<sub>2</sub>-POA was achieved under certain conditions, i.e., thin SiO<sub>2</sub> layers (< 15 nm) and high annealing temperatures (> 1350°C). Electrical characterizations of SiC-MOS capacitors treated with high-temperature N<sub>2</sub>-POA revealed the same evidence of slow trap passivation and fast trap generation that occurred in NO-treated devices fabricated with the optimized nitridation conditions. © 2015 Author(s). All article content, except where otherwise noted, is licensed under a Creative Commons Attribution 3.0 Unported License. [http://dx.doi.org/10.1063/1.4930980]

Traditional power devices have suffered from performance limits due to the physical properties of silicon (Si). Hence, silicon carbide (SiC) has been a promising semiconductor for developing next-generation power devices. SiC provides silicon dioxide (SiO<sub>2</sub>) by thermal oxidation as a gate insulator in metal-oxide-semiconductor field-effect-transistors (MOSFETs), which is similar to Si-MOS technology. However, the channel mobility of SiC-MOSFETs ordinarily deteriorates because of several miscellaneous defects in the thermal SiO<sub>2</sub> and at SiO<sub>2</sub>/SiC interfaces notwithstanding the conclusive physical understandings. Some standard procedures were employed to minimize the defect density by passivating electrical defects with particular atomic species, e.g., hydrogen, 3,4 nitrogen, 5-10 and phosphorus. 11 The interface state density (Dit) was markedly reduced below 10<sup>12</sup> cm<sup>-2</sup> eV<sup>-1</sup> near the conduction band edge by using post-oxidation annealing (POA) in reactive nitrogen-containing gases, i.e., nitric oxide (NO),<sup>5</sup> nitrous oxide (N<sub>2</sub>O),<sup>6</sup> and ammonia (NH<sub>3</sub>).<sup>7</sup> The reduction of D<sub>it</sub> is thought to be closely related to the quantity of piled-up nitrogen atoms at the SiO<sub>2</sub>/SiC interfaces. <sup>8–10</sup> Recently, NO has become the main species responsible for interface nitridation of mass-produced SiC-MOSFETs despite its toxicity. The most effective NO-POA is, however, limited to the annealing temperature of 1250°C, because NO molecules may dissociate at temperatures higher than 1300°C.<sup>12</sup>

Other than performing post-oxidation nitridation for SiO<sub>2</sub>/SiC structures, Shirasawa *et al.* proposed a method to passivate bare 6H-SiC surfaces with nitrogen atoms by applying high-temperature annealing in high-purity (N<sub>2</sub>) nitrogen gas.<sup>13</sup> They demonstrated the formation of atomically thin silicon nitride (SiN) layers on SiC surfaces by N<sub>2</sub> annealing at 1350°C for 30 min as the optimal condition. The SiN layers containing high-density nitrogen atoms bonding with Si atoms on the SiC surfaces were well recognized based on physical analyses done using scanning tunneling microscopy (STM),<sup>13</sup> low-energy electron diffraction (LEED),<sup>13</sup> x-ray diffraction (XRD),<sup>14</sup> and photoemission spectroscopy (PES).<sup>15,16</sup> It is suggested that the nitrided SiC surfaces may be suitable for making SiC-MOSFETs with deposition of gate insulators.<sup>17</sup> However, the interface quality

<sup>&</sup>lt;sup>a</sup>E-mail: chanthaphan@asf.mls.eng.osaka-u.ac.jp

<sup>&</sup>lt;sup>b</sup>E-mail: hosoi@mls.eng.osaka-u.ac.jp

improvement in MOS devices with SiO<sub>2</sub> deposited on the nitride surface is not sufficient compared with the NO-treated devices, probably because of unintentional reactions between the atomically thin nitride layers and the growing SiO<sub>2</sub> film.

In this study, we systematically investigated the interface nitridation by POA in pure  $N_2$  ambient for 4H-SiC substrates containing thermally grown oxides (SiO<sub>2</sub>/SiC). The incorporation of nitrogen atoms into SiO<sub>2</sub>/SiC interfaces was demonstrated by physically characterizing the interfaces using x-ray photoelectron spectroscopy (XPS). We report the threshold requirements including the proper oxide thicknesses and annealing temperatures that facilitate interface nitridation by  $N_2$ -POA. Next, the electrical properties of MOS devices were connected to reveal the correlation between the amount of nitrogen and the defect states at SiO<sub>2</sub>/SiC interfaces.

The samples used in this study were fabricated on 4°-off-axis 4H-SiC(0001) Si-face substrates with epitaxially grown *n*-type layers ( $N_d = 1 \times 10^{16} \text{ cm}^{-3}$ ). Piranha ( $H_2SO_4 + H_2O_2$ ) and standard RCA cleanings were done to prepare non-contaminated wafers before the high-temperature processes. Then, sacrificial oxides were formed on the SiC wafers by dry oxidation at 1100°C for 1 h inside a quartz furnace tube. The sacrificial oxide layers were subsequently removed by dipping into 5% HF solution. Next, the samples were oxidized using the same furnace tube at 1150°C to obtain thin and thick thermal SiO<sub>2</sub> layers ranging from approximately 3 to 40 nm by changing the oxidation time. SiO<sub>2</sub>/SiC samples were then subjected to identical POA at 1350°C for 30 min in N<sub>2</sub> ambient, in reference to the typical nitridation conditions for 6H-SiC surfaces using pure N<sub>2</sub> gas. 13-16 Note that vacuum pumping was conducted to remove the ambient gas inside the annealing furnace before introducing high-purity  $N_2$  gas (99.9999%). The oxide thicknesses were then confirmed using ellipsometry. The SiO<sub>2</sub>/SiC structures after N<sub>2</sub>-POA were analyzed by using XPS. In order to observe the chemical states near/at the SiO<sub>2</sub>/SiC interfaces, the SiO<sub>2</sub> layers were thinned down by wet etching in diluted HF (1%) solution prior to XPS measurement. The monochromatic Al K $\alpha$  line (1486.6 eV) was used to acquire core-level spectra of Si 2p and N 1s. The photoelectron take-off angle (TOA) was normal to the sample surfaces (90°).

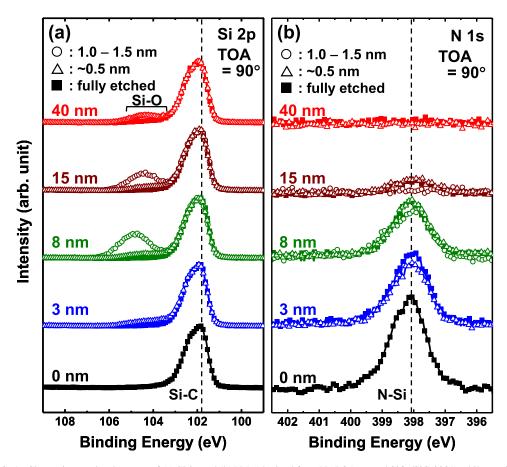

Figure 1 shows the Si 2p and N 1s core-level spectra taken from N<sub>2</sub>-POA treated SiO<sub>2</sub>/SiC samples with varying oxide thicknesses (3–40 nm). After performing identical N<sub>2</sub>-POA at 1350°C for 30 min, the oxide layers were partially (thinner than 1.5 nm) or fully etched back before XPS measurement. To compare the XPS spectra, the spectral intensity was normalized by the peak intensity of Si 2p core-level spectra at a binding energy (BE) of 101.8 eV, which is the Si-C bond (Si<sup>0+</sup>) signal arising from bulk SiC substrates. We observed the chemical shift components in the Si 2p spectra at a higher BE of about 104.5 eV that was attributable to the Si-O bonds (Si<sup>4+</sup>) of the remaining oxides (see Fig. 1(a)). The results from the 4H-SiC wafer without thermal oxide (0 nm) annealed in  $N_2$  gas in the same conditions are also shown in Figs. 1(a) and 1(b). The N 1s peak at 398.1 eV indicates nitridation of the SiC surface. As for the 40-nm-thick SiO<sub>2</sub>/SiC structure, no nitrogen signal was detected from the oxide interface, as shown in Fig. 1(b). This is simply explained by poor reactivity and low diffusivity of N<sub>2</sub> in the SiO<sub>2</sub> network. In contrast, we observed notable nitrogen content when the initial oxide thickness was less than 15 nm. It should be noted that the peak intensity and the BE position of N 1s core-level spectra changed insignificantly following oxide etching, indicating that the Si-N network was formed at SiO2/SiC interfaces by high-temperature N<sub>2</sub>-POA. Moreover, this nitrided interlayer was hard to remove using the HF solution, which is similar to the results in some previous studies on NO-POA.<sup>8,10</sup> These results imply that nitrogen atoms can be incorporated into the SiO<sub>2</sub>/SiC interfaces by conventional N<sub>2</sub>-POA when choosing appropriately thin SiO<sub>2</sub> layers.

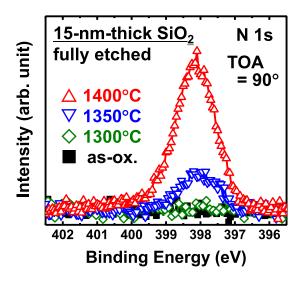

In order to understand the dependence of interface nitridation on the temperature by  $N_2$ -POA, we examined another set of samples subjected to  $N_2$ -POA with different annealing temperatures. Nearly identical 15-nm-thick thermal oxide layers were grown on clean 4H-SiC wafers by dry oxidation at 1150°C for 90 min. After that, the SiO<sub>2</sub>/SiC samples were treated with  $N_2$ -POA at different temperatures ranging from 1300–1400°C for 30 min. The N 1s core-level spectra of the samples after completely removing the SiO<sub>2</sub> layers are shown in Fig. 2. The photoelectron spectra were likewise normalized by the peak signals in Si 2p core-level spectra (data not shown). We found that the  $N_2$ -POA at 1300°C was ineffective to cause interface nitridation, and that, the annealing temperature at 1350°C seems to be the fundamental requirement that facilitates interface nitridation

FIG. 1. Change in core-level spectra of (a) Si 2p and (b) N 1s obtained from  $N_2$ -POA treated SiO<sub>2</sub>/SiC(0001) while varying the initial oxide thickness from 3 to 40 nm. Results from the bare SiC surface without oxide (0 nm) are also shown for comparison. After all samples were annealed in high-purity  $N_2$  at  $1350^{\circ}$ C for 30 min, the oxides were partially etched to a thickness of about 1.0–1.5 nm (open circles) or thinner than 0.5 nm (open triangles), and entirely etched (filled squares) prior to the XPS measurement. The XPS spectra were normalized by the Si 2p component from SiC substrate (Si–C bond).

by pure  $N_2$  annealing. It is probably difficult for stable nitrogen molecules to react at the interfaces under the inadequate annealing temperatures below 1350°C. Moreover, the N 1s peak intensities taken from the samples with  $N_2$ -POA at 1400°C increased considerably.

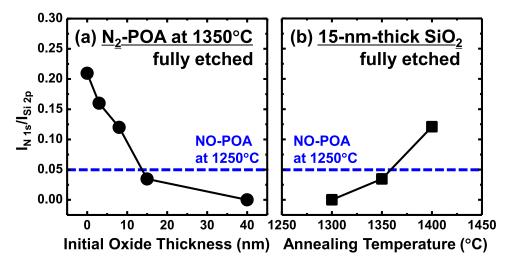

Next, we summarized the amounts of the nitrogen content at the SiO<sub>2</sub>/SiC interfaces in terms of the intensity ratio between the N-Si bond and the SiC bulk signals (I<sub>N 1s</sub>/I<sub>Si 2p</sub>) after completely removing the SiO<sub>2</sub>. Figure 3 plots the I<sub>N 1</sub>/I<sub>Si 2p</sub> ratios as a function of the initial oxide thickness (Fig. 3(a)) and the annealing temperature of  $N_2$ -POA (Fig. 3(b)). We found that the amount of interface nitrogen decreased as the oxide thickness increased. When nitric oxide (NO) is used for POA, interface nitridation can be achieved even for thick oxide samples at 1250°C. A typical nitrogen intensity ratio for the 75-nm-thick SiO<sub>2</sub>/SiC samples treated with the optimized NO-POA conditions (at 1250°C for 90 min)<sup>10</sup> is indicated by the dashed line in Fig. 3. It is clear that despite the poor reactivity of N<sub>2</sub>, the N<sub>2</sub>-POA allows us to incorporate a larger amount of nitrogen atoms than the NO-POA, particularly for thin oxide samples (< 15 nm). Figure 3(b) illustrates the conclusive results for N<sub>2</sub>-POA when the annealing temperatures were varied for samples with an identical initial oxide thickness of about 15 nm. The annealing temperature below 1350°C could not incorporate any notable amount of nitrogen atoms, as stated previously (see Fig. 2). However, a remarkable amount of nitrogen content was observed for the samples with N<sub>2</sub>-POA at 1350°C, and is close to the amount with NO-POA at 1250°C. Furthermore, compared with the NO-POA, the N<sub>2</sub>-POA at 1400°C was very promising for incorporating approximately twofold amounts of nitrogen atoms at the SiO<sub>2</sub>/SiC interface. It must be remarked for the NO-POA that the nitrogen density

FIG. 2. Change in the N 1s core-level spectra obtained from the  $N_2$ -POA treated SiC samples with 15-nm-thick thermal SiO<sub>2</sub> layers after complete SiO<sub>2</sub> removal. The POA in pure  $N_2$  ambient was done for 30 min at different temperatures, i.e.  $1400^{\circ}$ C (upward red triangles),  $1350^{\circ}$ C (downward blue triangles), and  $1300^{\circ}$ C (green rhombuses). The as-oxidized SiO<sub>2</sub>/SiC sample without post annealing (black filled squares: as-ox.) is also shown for comparison. Peak intensity was normalized by the Si 2p peak intensities (not shown).

at  $SiO_2/4H$ -SiC decreases at annealing temperatures higher than  $1300^{\circ}C$  because NO molecules begin to dissociate into  $N_2$  and  $O_2$ .<sup>12</sup> Active oxidation causing oxide etching should be a concern when a small amount of  $O_2$  mixtures exist in an annealing furnace during NO-POA.<sup>19</sup> In this work, we also observed oxide etching even for  $N_2$ -POA samples with annealing temperatures higher than  $1420^{\circ}C$ , probably due to active oxidation by a very small amount of residual oxygen in an annealing apparatus.

To provide insight into the electrical characteristics of SiC-MOS devices, we fabricated SiC-MOS capacitors by depositing circular Al gate electrodes (200 µm diameter) and back contacts.

FIG. 3. (a) Change in ratios between peak intensities of N 1s and Si 2p spectra ( $I_{N~1s}/I_{Si~2p}$ ) of SiO<sub>2</sub>/SiC samples plotted as a function of the initial oxide thickness ranging from 3 to 40 nm (see Fig. 1). The N<sub>2</sub>-POA was performed at 1350°C for 30 min. (b) Change in  $I_{N~1s}/I_{Si~2p}$  ratios of the 15-nm-thick SiO<sub>2</sub>/SiC samples by varying the annealing temperature in the range from 1300 to 1400°C (see Fig. 2). A typical peak intensity ratio for 75-nm-thick SiO<sub>2</sub>/SiC samples receiving NO-POA at 1250°C, which was optimized from the peak carrier mobility of SiC-MOSFETs,  $^{10}$  is also shown for comparison (blue dashed horizontal line). All samples were subjected to HF etching to completely remove oxide layers before XPS measurement.

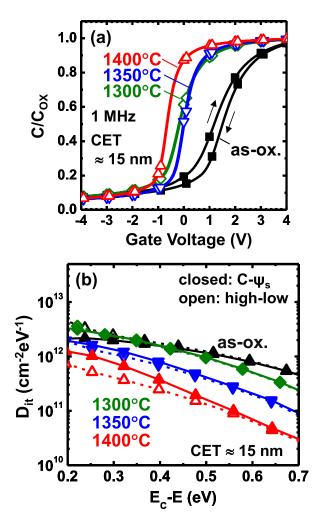

Capacitors with identical 15-nm-thick oxides and subjected to N<sub>2</sub>-POA at 1300, 1350, and 1400°C were chosen in order to characterize their capacitance-voltage (C–V) curves in comparison with the capacitor without nitridation (as-ox.). Figure 4(a) represents bidirectional C-V curves measured at 1 MHz while gate voltages were swept forward from depletion (–5 V) to accumulation (+5 V), and then backward to depletion. The positively shifted flatband voltage (V<sub>FB</sub>) of about 0.69 V in the as-ox. sample compared with the ideal position (V<sub>FB</sub> = 0.43 V) indicates negative fixed charges in the SiO<sub>2</sub>/SiC structure after dry oxidation of SiC substrates. Moreover, the as-ox. sample clearly showed C–V hysteresis with clockwise direction ( $\Delta$ V<sub>FB</sub> = 0.14 V) due to the electron injection from the substrate into defects at as-oxidized SiO<sub>2</sub>/SiC interfaces. It is clear that high-temperature N<sub>2</sub>-POA over 1300°C effectively suppressed the C–V hysteresis. Furthermore, we also found that the C–V curve of the capacitor with N<sub>2</sub>-POA at 1300°C still exhibited a stretched-out shape, which is similar to the earlier report on N<sub>2</sub>-POA at 1110°C.<sup>20</sup> Since N<sub>2</sub>-POA at moderate temperatures does not cause interface nitridation, only a slight improvment in the SiO<sub>2</sub>/SiC interface quality was obtained. In contrast, the capacitors treated at 1350 and 1400°C showed steeper C–V slopes, indicating improved interface quality. It is generally known that unusual slow traps are found at

FIG. 4. (a) Bidirectional high-frequency (1 MHz) C–v curves of SiC-MOS capacitors obtained by biasing gate voltages from depletion (–5 V) to accumulation (+5 V), and vice versa. The capacitors with  $N_2$ -POA at 1300 (green rhombuses), 1350 (downward blue triangles), and 1400°C (upward red triangles); and without POA (black filled squares: as-ox.) were examined. The capacitance values were normalized by the maximum capacitance ( $C_{OX}$ ). The capacitance equivalent thicknesses (CETs) were about 15 nm for all capacitors. (b) Energy distributions of  $D_{it}$  estimated from high-low (open symbols) and the C– $\psi_S$  method (closed symbols).

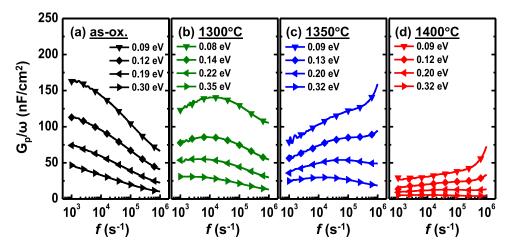

FIG. 5.  $G_P/\omega$  versus f curves obtained from SiC-MOS capacitors (a) without post-annealing (as-ox.) and with N<sub>2</sub>-POA at (b) 1300, (c) 1350, and (d) 1400°C. As indicated in the figures, the energy levels were varied near the conduction band edge (0.08 eV  $\leq$  E<sub>C</sub>-E  $\leq$  0.35 eV). To generate the conductance curves, the probe oscillation was swept from 1 kHz to 1 MHz under constant surface potentials. The measurement was conducted at room temperature.

as-oxidized SiO<sub>2</sub>/SiC interfaces. These slow traps make it difficult to emit carriers from the interfaces that end up with voltage shifts, causing the stretched-out C–V shape. Interface nitridation by NO-POA is the most common approach to passivate the slow traps at SiO<sub>2</sub>/SiC interfaces. <sup>9,10,21,22</sup> It should be noted that similarly to the NO-POA, the well-behaved C–V curves were obtained by incorporating nitrogen with N<sub>2</sub>-POA over 1350°C. Figure 4(b) represents the energy distribution of D<sub>it</sub> for SiO<sub>2</sub>/SiC structures estimated by the conventional high-low method, and the recently proposed C– $\psi$ <sub>S</sub> method<sup>23</sup> that captures entire traps, including fast traps at shallow energy levels. It was found that both methods showed a reduced D<sub>it</sub> with an increase in N<sub>2</sub>-POA temperatures. Interestingly, the D<sub>it</sub> value for N<sub>2</sub>-POA at 1400°C was significantly reduced to below 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> at deep energy levels (E<sub>C</sub> – E > 0.5 eV). However, the magnitude of D<sub>it</sub> reduction at shallow energy levels (E<sub>C</sub> – E < 0.5 eV) estimated using the C– $\psi$ <sub>S</sub> method was not very significant compared with that estimated using the high-low method. On the basis of the D<sub>it</sub> discrepancy between the high-low and C– $\psi$ <sub>S</sub> methods, the results shown in Fig. 4(b) suggest the presence of fast interface traps caused by the high-temperature N<sub>2</sub>-POA.

We further examined conductance characteristics of the same sample set to understand the interface trap behaviors. Figure 5 illustrates conductance  $(G_p/\omega)$  curves plotted as a function of probe oscillation (f) for the shallow energy levels  $(0.08 \text{ eV} \leq E_C\text{-}E \leq 0.35 \text{ eV})$ . The conductance curves acquired at room temperature were normalized by the gate area in order to unbiasedly compare the trap density. As shown in Fig. 5(a), the conductance peaks of the as-ox. sample mainly appear at frequencies less than 1 kHz. This coincides well with the presence of interface states with long time constants demonstrated by the remarkable stretching-out of the C-V curve in Fig. 4(a). As shown in Figs. 5(b)-5(d), the peak intensity of slow traps apparently decreased after N<sub>2</sub>-POA, as expected from the D<sub>it</sub> reduction in Fig. 4(b). The N<sub>2</sub>-POA at 1400°C was the most advantageous to eliminate the conductance signals attributable to the slow traps (Fig. 5(d)), thus improving interface quality. However, we noticed that parts of the conductance signals increased at very high frequencies (f > 1 MHz). We think that these signals are associated with the fast traps at SiO<sub>2</sub>/SiC due to nitridation, similar to previous reports on NO-POA. The fast trap signals began to appear when the annealing temperature was higher than 1350°C (Fig 5(c)), which agrees well with the threshold condition for interface nitridation by N<sub>2</sub>-POA.

In summary, we demonstrated an alternative method to effectively incorporate nitrogen atoms into the  $SiO_2/SiC$  interface by high-temperature POA in pure  $N_2$  ambient. It was revealed that nitridation of the interface is achievable similarly to the case with a bare SiC surface following  $N_2$  annealing at  $1350^{\circ}C$ . These nitrided structures were not chemically reactive to the HF wet etching. We also affirmed that the essential requirements for achieving interface nitridation under

pure  $N_2$  ambient were a suitable initial oxide thickness (less than 15 nm) and a sufficient thermal budget (higher than  $1350^{\circ}$ C). The interface nitridation was likely to be enhanced by increasing the annealing temperature. The electrical properties of the SiC-MOS devices were examined and found to have benefits of  $N_2$ -POA that were analogous to the previous reports on NO-POA. Although a certain amount of fast states were generated at the SiO<sub>2</sub>/SiC interfaces, just as with the conventional NO-POA, the proposed  $N_2$ -POA was found to be beneficial for incorporating a larger amount of nitrogen atoms and passivating dominant slow traps at the interface even under the harmless conditions.

This work was partly supported by Grant-in-Aid for JSPS Fellows (No.14F04359) and Grant-in-Aid for Young Scientists (A) (No.24686008) from the Ministry of Education, Culture, Sports, Science, and Technology of Japan.

- <sup>1</sup> For example, T. Kimoto and J. A. Cooper, Fundamentals of Silicon Carbide Technology (Wiley-IEEE Press, 2014).

- <sup>2</sup> H. Watanabe, T. Hosoi, T. Kirino, Y. Kagei, Y. Uenishi, A. Chanthaphan, A. Yoshigoe, Y. Teraoka, and T. Shimura, Appl. Phys. Lett. **99**, 021907 (2011).

- <sup>3</sup> K. Fukuda, S. Suzuki, T. Tanaka, and K. Arai, Appl. Phys. Lett. **76**, 1585 (2000).

- <sup>4</sup> A. Chanthaphan, T. Hosoi, S. Mitani, Y. Nakano, T. Nakamura, T. Shimura, and H. Watanabe, Appl. Phys. Lett. **100**, 252103 (2012).

- <sup>5</sup> H.-F. Li, S. Dimitrijev, H.B. Harrison, and D. Sweatman, Appl. Phys. Lett. **70**, 2028 (1997).

- <sup>6</sup> T. Kimoto, Y. Kanzaki, M. Noborio, H. Kawano, and H. Matsunami, Jpn. J. Appl. Phys. 44, 1213 (2005).

- <sup>7</sup> J. Senzaki, T. Suzuki, A. Shimozato, K. Fukuda, K. Arai, and H. Okumura, Mater. Sci. Forum **645-648**, 685 (2010).

- <sup>8</sup> R. Kosugi, T. Umeda, and Y. Sakuma, Appl. Phys. Lett. **99**, 182111 (2011).

- <sup>9</sup> H. Yoshioka, T. Nakamura, and T. Kimoto, J. Appl. Phys. **112**, 024520 (2012).

- <sup>10</sup> T. Hosoi, Y. Nanen, T. Kimoto, A. Yoshigoe, Y. Teraoka, T. Shimura, and H. Watanabe, in 10<sup>th</sup> European Conference on Silicon Carbide & Related Materials (ECSCRM-2014), WE-P-LN-10, Grenoble, France, September 21-25 (2014).

- <sup>11</sup> D. Okamoto, H. Yano, K. Hirata, T. Hatayama, and T. Fuyuki, IEEE Electron Device Lett. **31**, 710 (2010).

- <sup>12</sup> A. Gupta, S. Toby, E. P. Gusev, H. C. Lu, Y. Li, M. L. Green, T. Gustafsson, and E. Garfunkel, Prog. Surf. Sci. 59, 103 (1998).

- <sup>13</sup> T. Shirasawa, K. Hayashi, S. Mizuno, S. Tanaka, K. Nakatsuji, F. Komori, and H. Tochihara, Phys. Rev. Lett. 98, 136105 (2007).

- <sup>14</sup> T. Shirasawa, K. Sakamoto, T. Takahashi, and H. Tochihara, Surf. Sci. **605**, 328 (2011).

- <sup>15</sup> T. Shirasawa, K. Hayashi, H. Yoshida, S. Mizuno, S. Tanaka, T. Muro, Y. Tamenori, Y. Harada, T. Tokushima, Y. Horikawa, E. Kobayashi, T. Kinoshita, S. Shin, T. Takahashi, Y. Ando, K. Akagi, S. Tsuneyuki, and H. Tochihara, Phys. Rev. B 79, 241301(R) (2009).

- <sup>16</sup> T. Shirasawa, S. Tanaka, T. Muro, Y. Tamenori, Y. Harada, T. Tokushima, T. Kinoshita, S. Shin, T. Takahashi, and H. Tochihara, Mater. Sci. Forum 675-677, 15 (2011).

- <sup>17</sup> J. Rozen, M. Nagano, and H. Tsuchida, J. Mater. Res. **28**, 1 (2013).

- <sup>18</sup> W. Orellana, A. J. R. da Silva, and A. Fazzio, *Phys. Rev. B* **70**, 125206 (2004).

- <sup>19</sup> N. S. Jacobson and D. L. Myers, Oxid. Met. **75**, 1 (2011).

- <sup>20</sup> S. K. Gupta, A. Azam, and J. Akhtar, Semiconductors **46**, 4 (2012).

- <sup>21</sup> H. Yoshioka, T. Nakamura, and T. Kimoto, J. Appl. Phys. **115**, 014502 (2014).

- <sup>22</sup> S. Nakazawa, T. Okuda, J. Suda, T. Nakamura, and T. Kimoto, IEEE Trans. Electron Devices **62**, 2 (2015).

- <sup>23</sup> H. Yoshioka, T. Nakamura, and T. Kimoto, J. Appl. Phys. **111**, 014502 (2012).