| Title        | Interface and oxide trap states of SiO2/GaN metal-oxide-semiconductor capacitors and their effects on electrical properties evaluated by deep level transient spectroscopy                                                                                       |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Ogawa, Shingo; Mizobata, Hidetoshi; Kobayashi,<br>Takuma et al.                                                                                                                                                                                                  |

| Citation     | Journal of Applied Physics. 2023, 134(9), p. 095704                                                                                                                                                                                                              |

| Version Type | АМ                                                                                                                                                                                                                                                               |

| URL          | https://hdl.handle.net/11094/92520                                                                                                                                                                                                                               |

| rights       | This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. This article appeared in J. Appl. Phys. 7 September 2023; 134 (9): 095704 and may be found at https://doi.org/10.1063/5.0165894. |

| Note         |                                                                                                                                                                                                                                                                  |

### The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

Study on interface and oxide trap states of  $SiO_2/GaN$  metal-oxide-semiconductor capacitors and their effects on electrical properties by deep level transient spectroscopy

Shingo Ogawa,<sup>1, a)</sup> Hidetoshi Mizobata,<sup>2</sup> Takuma Kobayashi,<sup>2</sup> Takayoshi Shimura,<sup>2</sup> and Heiji Watanabe <sup>2</sup>

a) E-mail: shingo.ogawa.s9@trc.toray

The relationship between the electrical properties and the carrier trap properties of the  $SiO_2/GaN$  metal-oxide-semiconductor (MOS) capacitors was investigated using electrical measurements and deep level transient spectroscopy (DLTS). The capacitance-voltage (C-V) measurement showed that the frequency dispersion of the C-V curves became smaller after an 800 °C annealing in  $O_2$  ambient. DLTS revealed that before the annealing, the interface trap states, in a broad energy range above the mid-gap of GaN, were detected with the higher interface state density at around 0.3 and 0.9 eV below the conduction band minimum (Ec) of GaN. Moreover, the oxide trap states were formed at around 0.1 eV below the Ec of GaN, plausibly indicating a slow electron trap with a tunneling process. Although both trap states affect the electrical reliability and insulating property of the  $SiO_2/GaN$  MOS capacitors, they were found to drastically decrease after the annealing, leading to the improvement of the electrical properties.

<sup>&</sup>lt;sup>1</sup> Toray Research Center, Inc., Otsu, Shiga 520-0842, Japan

<sup>&</sup>lt;sup>2</sup> Graduate School of Engineering, Osaka University, Suita, Osaka 565-0871, Japan

### the online version of record will be different from this version once it has been copyedited and typeset. This is the author's peer reviewed, accepted manuscript. However, the online version of record will be diff. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0165894

### 1. Introduction

Gallium nitride (GaN) is one of promising materials for advanced power electronics due to its superior material properties, such as high breakdown electric field and wide band gap, compared to silicon (Si).1-3 While successful developments of GaN-based high electron mobility transistors (HEMTs) using two-dimensional electron gas at the AlGaN/GaN heterostructures have been achieved for high efficiency and high frequency applications, 4-6 there still realize GaN-based issues to metal-oxide-semiconductor (MOS) field-effect transistors (FETs) for high performance power devices with normally-off high voltage and high temperature operations. Although intensive research and progress have been reported regarding the development of GaN MOSFETs, 7-9 the electrical characteristics have not yet been optimized. One of the important issues is the quality of the dielectric/GaN interfaces, leading to a low channel mobility, threshold voltage shift and low reliable operations. Therefore, understanding the origin of the poor interface qualities and formation of the high-quality dielectric/GaN interfaces are indispensable for realization of advanced GaN MOSFETs. As for a dielectric on GaN, gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) is a thermally-grown dielectric on GaN as well as silicon dioxide (SiO<sub>2</sub>) on Si which is well known as a suitable dielectric film for Si-based large scale integrated (LSI) technologies. However, the band gap of Ga<sub>2</sub>O<sub>3</sub> is around 5 eV and thus the barrier height of the Ga<sub>2</sub>O<sub>3</sub>/GaN interface is insufficient, thus causing a high leakage current. Therefore, a wider band gap dielectric, such as aluminum oxide (Al<sub>2</sub>O<sub>3</sub>), <sup>10, 11</sup> silicon nitride (Si<sub>3</sub>N<sub>4</sub>)<sup>8, 12</sup> and SiO<sub>2</sub>, <sup>13-16</sup> should be chosen to design the appropriate band alignment of the dielectric/GaN interface. In addition, Ga<sub>2</sub>O<sub>3</sub> forms large crystal grains on GaN after annealing over 850 °C, <sup>17, 18</sup> leading to an increase in the leakage current and surface roughness. Considering these facts, SiO2 is a possible candidate due to the wide band gap of around 9 eV and stable amorphous structure at higher temperatures. Regarding the SiO<sub>2</sub>/GaN structures,

previous reports revealed that the formation of a suitable thin GaO<sub>x</sub> interlayer between SiO<sub>2</sub> and GaN enhanced the electrical properties of the GaN MOS devices with a low interface state density (Dit) below 10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>. 15, 19 It was also shown that the SiO<sub>2</sub>/GaN interface degraded after a 900 °C annealing due to the interfacial reaction between SiO2 and GaN, leading to the excess oxidation of GaN and the detrimental Ga diffusion into the SiO<sub>2</sub> layer.<sup>20</sup> As a countermeasure, the deposition of the nitrogen (N)-incorporated SiO<sub>2</sub> on GaN was further beneficial for the electrical properties by suppressing the excess oxidation of the GaN surface.<sup>21</sup> These results indicated that appropriate measures must be considered to form high-quality SiO<sub>2</sub>/GaN interfaces. Although several techniques have been proposed for the SiO<sub>2</sub>/GaN structures, further improvement must be achieved for higher performance of the GaN-MOS devices, especially a reduction of the electrically-active defects. Based on this point of view, it was reported that the electrical properties of not only GaN- but also silicon carbide (SiC)-based MOS devices strongly depend on their  $D_{it}$ . Moreover, trap states in the dielectrics, called oxide traps or near interface traps (NITs), also degrade the electrical properties of the power MOSFETs. <sup>23-25</sup> Among the various techniques to investigate the carrier trap properties of MOS devices, deep level transient spectroscopy (DLTS) is one of superior techniques to evaluate the energy and amount of trap states with a higher sensitivity.<sup>26, 27</sup> So far, whereas various intensive DLTS studies have been performed for SiC-MOS devices, 22, 28-30 a few papers have reported on evaluation of GaN-MOS devices using DLTS, for example, Al<sub>2</sub>O<sub>3</sub>/GaN MOS devices, 31, 32 SiN<sub>x</sub>/GaN metal-insulator-semiconductor (MIS) devices<sup>33</sup> and AlGaN/GaN MIS-HEMTs.<sup>34</sup> Technical development to analyze the trap states of the GaN-MOS devices is also required to further enhance the performance of the GaN-MOS devices. Therefore, in this study, we investigated the trap states of the GaN-MOS devices using DLTS. Not only interface traps but also oxide traps were characterized in terms of the relationship

between the electrical properties and trap states.

### 2. Experimental

Free-standing GaN (0001) substrates with 4- $\mu$ m-thick Si-doped n-type GaN epilayers (Si concentration: 2×10<sup>16</sup> cm<sup>-3</sup>) were used as the base substrates in this study. The GaN surface was cleaned using acetone with ultrasonics and a 50 % hydrofluoric acid (HF) solution to remove organic contaminants and the native oxide, respectively. Around 25-nm-thick SiO<sub>2</sub> films were deposited by plasma enhanced chemical vapor deposition (PECVD) using tetraethyl orthosilicate (TEOS) as the Si source. In the early stage of the SiO<sub>2</sub> film deposition (under 5-nm thick), nitrogen gas was introduced into the oxygen gas to dilute the ratio of oxygen and to form the nitrogen (N) incorporated SiO2 layer. A previous study revealed that the N-incorporated SiO<sub>2</sub>/GaN capacitors enhanced the electrical properties by suppressing the excess oxidation of the GaN surface which led to the detrimental Ga diffusion into the SiO<sub>2</sub> films.<sup>21</sup> After the formation of the SiO<sub>2</sub> films, post deposition annealing (PDA) was performed at 800 °C in O2 ambient to improve the interface quality without the interfacial reaction of the SiO<sub>2</sub>/GaN structure.<sup>20</sup> A nickel film was deposited as a gate electrode with diameters of 200 µm and 500  $\mu$ m for the electrical measurements and DLTS measurement, respectively, followed by the deposition of an aluminum film as a back contact.

Capacitance-voltage (*C-V*) and current-voltage (*I-V*) measurements were conducted at room temperature to investigate the electrical properties and the insulating properties of the SiO<sub>2</sub>/GaN MOS capacitors, respectively. Bidirectional *C-V* curves were obtained with measurement frequencies ranging from 10 kHz to 1 MHz. The DLTS measurement was performed to evaluate the electron trap states of the SiO<sub>2</sub>/GaN MOS capacitors. In this study, constant capacitance (CC) DLTS was mainly conducted in which the capacitance was kept constant during the transient process by applying feedback to the

measured voltage. The CC-DLTS enables us to improve the accuracy of the energy of the trap states, because the fermi level of the MOS interface does not change during the electron emission process.<sup>27, 28, 30</sup> The reverse bias was set near the flatband voltage of the MOS capacitors and the pulse bias of |5 V| was applied to accumulate electrons around the SiO<sub>2</sub>/GaN interface. The pulse width ( $T_P$ ) was set at 0.02, 2 and 200 ms to investigate not only the interface traps but also the oxide traps. Generally, electrons are quickly trapped at the interface trap states. Therefore, a shorter  $T_P$  is sufficient to fill the interface trap states and  $D_{it}$  can be calculated from the DLTS spectra with the shorter  $T_P$ .<sup>32, 35</sup> If some electrons infiltrated into the oxide traps from the SiO<sub>2</sub>/GaN interface, the electrons are subject to a tunneling process. This means that the electrons are captured at the oxide traps with a certain time, and as a result, the intensity of the DLTS signal varies with  $T_P$ .<sup>27</sup> Therefore, we also investigated the  $T_P$  dependence of the DLTS signals ranging from  $10^{-5}$  to  $10^0$  s by applying the isothermal CC measurement.

### 3. Results and discussion

The electrical properties of the SiO<sub>2</sub>/GaN MOS capacitors without (as-depo.) and with the 800 °C annealing were evaluated by the bidirectional *C-V* curves, shown in Figs. 1(a) and 1(b). Both curves represented well-behaved *C-V* characteristics of the SiO<sub>2</sub>/*n*-GaN MOS capacitors with a small hysteresis. The capacitance equivalent thicknesses (CET) of the dielectric films, estimated from the maximum of the capacitance, were around 25 nm as expected. The frequency dispersion of the *C-V* curves was found to become smaller after the annealing. These results were consistent with a previous report and indicated the impact of the combination between the N-incorporation into the SiO<sub>2</sub> layer and the 800 °C annealing in O<sub>2</sub> ambient.<sup>21, 36</sup> The frequency dispersion of the *C-V* curves is definitely derived from charge injection from GaN to the SiO<sub>2</sub> layer and/or carrier trap at the SiO<sub>2</sub>/GaN interface caused by the

deterioration of the dielectrics and dielectric/semiconductor interfaces.<sup>15, 37</sup> In addition, we confirmed from the *I-V* measurement that the insulating properties of the SiO<sub>2</sub>/GaN MOS capacitor was also improved by the annealing (data not shown), indicating that the electron injection into the SiO<sub>2</sub> layer were caused by the trap states. Therefore, the investigation of the carrier trap properties not only at the interface, but also in the SiO<sub>2</sub> layer is important for further improvements of the electrical properties of the SiO<sub>2</sub>/GaN MOS capacitors.

To investigate the carrier trap properties of the SiO<sub>2</sub>/GaN MOS capacitors, we performed the CC-DLTS measurement. Figure 2(a) shows the DLTS spectra of the SiO<sub>2</sub>/GaN MOS capacitor without the annealing. Note that the DLTS signal intensity (vertical axis) was calculated by the correlation function analysis applying the sine coefficient to the transient voltages. The higher DLTS signals of the SiO<sub>2</sub>/GaN MOS capacitor without the annealing were observed at around 130 K and 400 K. These results indicated a unique energy distribution of the trap states within the band gap of GaN. In addition, these signals increased with the  $T_P$ , suggesting that electrons were trapped not only at the SiO<sub>2</sub>/GaN interface, but also in the SiO<sub>2</sub> layer. On the other hand, Fig. 2(b) shows that the DLTS signals drastically decreased over one order of magnitude after the annealing compared to those before the annealing. Figure 3 shows the energy distributions of the Dit in the SiO<sub>2</sub>/GaN MOS capacitors, calculated using the DLTS spectra with the  $T_P$  of 0.02 ms. It is noted that the  $D_{it}$  was transformed from the DLTS spectra by assuming that the capture cross section ( $\sigma_c$ ) did not depend on the energy (temperature). <sup>27, 32, 35</sup> The  $\sigma_c$  was estimated to be  $6\times10^{-15}$  cm<sup>2</sup> based on the DLTS spectra at around 0.3 eV for the SiO<sub>2</sub>/GaN MOS capacitor without the annealing using the correlation function method.<sup>30</sup> Though the calculated  $\sigma_c$  contains an error margin to some extent, the value of  $\sigma_c$  is almost comparable to the reported values of several MOS capacitors, such as the Al<sub>2</sub>O<sub>3</sub>/GaN, <sup>31, 32</sup> and the SiO<sub>2</sub>/SiC structures<sup>28-30</sup>. Considering the

$\sigma_c$  of the  $D_{it}$ , the capture time constant ( $\tau_c$ ) is very fast at around  $10^{-10}$  s. Therefore, the  $T_P$  of 0.02 ms is sufficient to fill electrons with the interface states. In Fig. 3, the higher  $D_{ii}$  at around 0.3 eV, labeled  $E_1$ , below the conduction band minimum ( $E_C$ ) of GaN was observed for the SiO<sub>2</sub>/GaN MOS capacitor without the annealing. Previous studies revealed that a similar trap state at around 0.3 eV was detected in the Al<sub>2</sub>O<sub>3</sub>/GaN MOS capacitor, 32, 38 possibly speculated as the nitrogen vacancy related complexes or the bond disorder at the interface. Moreover, the  $D_{it}$  at around 0.9 eV, close to the mid-gap of GaN, was found to slightly increase. Such deep state was observed for the GaN on a sapphire substrate,<sup>39</sup> thin epilayers,<sup>40</sup> and for the GaN after the high-energy electron irradiation,41 indicating to be likely due to dislocation-related defects and/or N interstitials. Theoretical study indicated that the origin of the deep state was plausibly derived from the N interstitials.<sup>42</sup> However, the assignments are still controversial and a deeper understanding is required. On the other hand, the  $D_{it}$  decreased to around  $10^{10}$ cm<sup>-2</sup>eV<sup>-1</sup> in all the measured energy ranges after the annealing. These results clearly indicated the improvement of the interface quality of the SiO<sub>2</sub>/GaN MOS capacitor related to the *C-V* characteristics shown in Fig. 1.

Next, an isothermal CC measurement was performed to distinguish the oxide trap states from the interface trap states. Figure 4 shows the  $T_P$  dependence of the DLTS signals measured at several temperatures. If electrons were captured at the oxide traps with a tunneling process, the DLTS signals ( $\Delta V$ ) follow the equations described below.<sup>27, 30, 35</sup>

$$\Delta V = \frac{qA}{c_{ox}} N_I d_x kT \tag{1}$$

$$d_x = d_0 \ln \left(\frac{T_P}{\tau_c}\right) \tag{2}$$

$$d_x = d_0 \ln \left(\frac{T_P}{\tau_c}\right)$$

$$\tau_c = \frac{1}{\sigma_c \nu_{th} n_0} , \ \tau_e = \frac{1}{\sigma_c \nu_{th} N_c}$$

(2)

where q is the elementary charge, A is the electrode area,  $C_{ox}$  is the capacitance of the  $SiO_2$  layer,  $N_I$  is the density of states in the  $SiO_2$  layer,  $d_x$  is the depth of the trapped layer, k is the boltzmann constant,  $d_0$  is the tunnel constant,  $v_{th}$  is the thermal velocity of the electron,  $n_0$  is the carrier density of the samples,  $\tau_e$  is the emission time constant, and  $N_c$  is the density of states of the conduction band. According to the equation (1) and (2), we can estimate the oxide trap state density  $(N_I d_x)$  and  $\tau_c$  from the linear slope and the intersection in the  $\Delta V$  with the logarithmic (ln)  $T_P$ . Using  $\tau_c$ ,  $\sigma_c$  is obtained by the equation (3) and as a result,  $\tau_e$  is also estimated. It is noted that in this measurement,  $d_x$ can be regarded as the SiO<sub>2</sub> thickness, because the SiO<sub>2</sub> thickness is thin enough to fill carriers after applying the pulse bias. As shown in Fig. 2(a), the DLTS signals without the annealing at around 130 K and 400 K clearly increased with the  $T_P$ , expecting that the T<sub>P</sub> dependence of the DLTS signals is observed. Surely, the DLTS signals without the annealing at 130 K and 400 K, shown in Fig. 4(a), exhibited a linear increase with the  $\ln T_P$  of around  $10^{-4}$  to  $10^{-2}$  s, indicating that the electrons were captured at the oxide traps with a tunneling process. Whereas the DLTS signals at 80 K also showed a linear increase with the ln T<sub>P</sub>, no linear increase was observed at 200 K and 300 K due to being close to the detection limit of the measurement, as expected in the results of the temperature dependence of the DLTS signals shown in Fig. 2(a). Also, the DLTS signals after the annealing, measured at 300 K and 400 K, showed a linear increase with the ln  $T_P$  of around  $10^{-4}$  to  $10^{-2}$  s, shown in Fig. 4(b). It is also noted that the reduction of the DLTS signals in the saturated (Filled) region was observed at the several temperatures in Fig. 4. The reason of the reduction is still unclear but probably due to another process besides the simple electron capture process in the saturated region. One possible reason is a hole injection from the electrode into the  $SiO_2$  layer, when the longer  $T_P$  was applied to the MOS capacitors. However, the influence of the reduction of the DLTS signals in the saturated region seems to be negligible for the evaluation of the oxide trap

states. The energy distributions of the oxide trap state densities and the capture cross sections were calculated using the results of linear ranges in Fig. 4 and shown in Fig. 5. It can be considered that all the active oxide trap states in the SiO<sub>2</sub> layer were filled with electrons, when the DLTS signals were saturated in Fig. 4. At the saturated  $T_P$ , the energy of the trap states at the SiO<sub>2</sub>/GaN interface ( $E_0$ ) and at the  $d_x$  ( $E_P$ ) was calculated using the equations (4) and (5) described below. <sup>27, 30</sup> We defined the averaged value ( $E_{mid}$ ) as the energy of the oxide trap state by the equation (6).

$$E_0(t) = kT \ln \left(\frac{t}{\tau_0}\right) \tag{4}$$

$$E_P = E_0(t) - kT \frac{d_x}{d_0} \tag{5}$$

$$E_{mid} = E_0(t) - \frac{1}{2}kT\frac{d_x}{d_0}$$

(6)

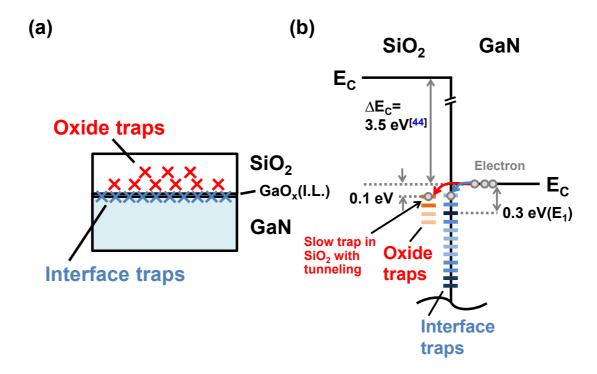

Note that the results of the normal capacitance transient measurement were also plotted in Fig. 5, because it has a higher sensitivity than the CC measurement. The oxide trap state density of around  $1\times10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> at 0.1 eV below the  $E_C$  of GaN was observed without the annealing, while very low oxide trap states were detected after the annealing. The capture cross sections are quite small at around  $10^{-19} \sim 10^{-20}$  cm<sup>2</sup>. This means that the capture time constants are around  $10^{-5} \sim 10^{-4}$  s, which are also seen in the SiN<sub>x</sub>/Si structures.<sup>43</sup> Therefore, the slow charge injection into the shallow states in the SiO<sub>2</sub> layer occurred for the SiO<sub>2</sub>/GaN MOS capacitor without the annealing. It possibly caused the high frequency dispersion of the C-V curves, as shown in Fig. 1, surely leading to a deterioration of the electrical reliability of the SiO<sub>2</sub>/GaN MOS capacitors. Finally, schematic images of the trap states in the SiO<sub>2</sub>/GaN structure are described in Fig. 6. The conduction band offset ( $\Delta E_C$ ) between SiO<sub>2</sub> and GaN was referred for the similar structure of the SiO<sub>2</sub>/n-GaN(0001).<sup>44</sup> The interface trap states were formed in a broad energy range above the mid-gap of GaN. Especially, the higher  $D_{tt}$  values at

around 0.3 eV and 0.9 eV below the  $E_C$  of GaN were observed. The oxide trap states were found at around 0.1 eV below the  $E_C$  of GaN, representing those at around 3.6 eV below the  $E_C$  of SiO<sub>2</sub>. Previous theoretical studies indicated that the states of positively charged oxygen vacancy sites (so-called  $E_I$ ' or  $E_\gamma$ ' center) were formed at around 3-4 eV from the  $E_C$  of SiO<sub>2</sub>. <sup>45, 46</sup> Therefore, the detected oxide trap states likely stem from the oxygen vacancies in the SiO<sub>2</sub> layer, easily capturing electrons. Although these trap states affect the electrical reliability and insulating property of the SiO<sub>2</sub>/GaN MOS capacitors, we confirmed that they were dramatically decreased by the 800 °C annealing in O<sub>2</sub> ambient.

### 4. Summary

In this study, we intensively investigated the carrier trap states of the SiO<sub>2</sub>/GaN MOS capacitors using DLTS and confirmed their effects on the electrical properties. The interface trap states showed a broad energy distribution above the mid-gap of GaN and higher  $D_{it}$  values at around 0.3 eV and 0.9 eV below the Ec of GaN were found for the as-deposited sample. In addition, the oxide trap states were formed at around 0.1 eV below the Ec of GaN, plausibly indicating the slow electron trap with a tunneling process. We confirmed that the interface and the oxide trap states drastically decreased after the annealing at 800 °C in O<sub>2</sub> ambient, leading to the improvement of the electrical reliability and the insulating property of the SiO<sub>2</sub>/GaN MOS capacitors. Although further investigation is required to understand the origin of the carrier trap behaviors in the SiO<sub>2</sub>/GaN MOS capacitors, these results indicate the necessity to evaluate not only the interface traps but also the oxide traps, which surely affect the carrier transport properties and reliability of the GaN-based MOS devices.

### **ACKNOWLEDGMENTS**

This work was partly supported by the MEXT "Program for Creation of Innovative Core Technology for Power Electronics" (Grant No. JPJ009777). The author would like to thank Dr. Okada (Ceramicforum Co., Ltd) for fruitful discussion.

### **AUTHOR DECLARATIONS**

### **Conflict of Interest**

The authors have no conflicts to disclose.

### **Author Contributions**

Shingo Ogawa: Data curation (lead); Formal analysis (lead); Investigation (lead); Writing – original draft (lead); Writing – review and editing (equal). Hidetoshi Mizobata: Data curation (equal); Formal analysis (equal); Investigation (equal). Takuma Kobayashi: Formal analysis (supporting); Investigation (supporting). Takayoshi Shimura: Formal analysis (supporting); Investigation (supporting). Heiji Watanabe: Conceptualization (equal); Formal analysis (supporting); Investigation (supporting); Project administration (lead); Supervision (equal); Writing – review and editing (equal).

### **DATA AVAILABILITY**

The data that support the findings of this study are available from the corresponding author upon reasonable request.

### References

- 1) B. J. Baliga, Semicond. Sci. Technol. **28**, 074011 (2013).

- 2) T. Kachi, Jpn. J. Appl. Phys. 53, 100210 (2014).

- 3) H. Amano et al., J. Phys. D: Appl. Phys. 51, 163001 (2018).

- 4) B. M. Green, K. K. Chu, E. M. Chumbes, J. A. Smart, J. R. Shealy, and L. F. Eastman, IEEE Electron Device Lett. **21**, 268 (2000).

- 5) M. Kuzuhara, T. Asubar, and H. Tokuda, Jpn. J. Appl. Phys. 55, 070101 (2016).

- 6) S. Ozaki, J. Yaita, A. Yamada, Y. Kumazaki, Y. Minoura, T. Ohki, N. Okamoto, N. Nakamura, and J. Kotani, Appl. Phys. Express 14, 041004 (2021).

- 7) H. Otake, K. Chikamatsu, A. Yamaguchi, T. Fujishima, and H. Ohta, Appl. Phys. Express 1, 011105 (2008).

- 8) M. Kodama, M. Sugimoto, E. Hayashi, N. Soejima, O. Ishiguro, M. Kanechika, K. Itoh, H. Ueda, T. Uesugi, and T. Kachi, Appl. Phys. Express 1, 021104 (2008).

- 9) T. Oka, Jpn. J. Appl. Phys. **58**, SB0805 (2019).

- 10) Y. Ando, K. Nagamatsu, M. Deki, N. Taoka, A. Tanaka, S. Nitta, Y. Honda, T. Nakamura, and H. Amano, Appl. Phys. Lett. **117**, 102102 (2020).

- 11) S. Kaneki and T. Hashizume, AIP Advances 11, 015301 (2021).

- 12) T. Hashizume, R. Nakasaki, S. Ootomo, S. Oyama, and H. Hasegawa, IEICE Trans. Electron, **E84-C**, 1455 (2001).

- 13) K. Matocha, V. Tilak, and G. Dunne, Appl. Phys. Lett. 90, 123511 (2007).

- 14) T. Oka, T. Ina, Y. Ueno, and J. Nishii, Appl. Phys. Express 8, 054101 (2015).

- 15) T. Yamada, J. Ito, R. Asahara, K. Watanabe, M. Nozaki, T. Hosoi, T. Shimura, and H. Watanabe, Appl. Phys. Lett. **110**, 261603 (2017).

- 16) K. Aoshima, N. Taoka, M. Horita, and J. Suda, Jpn. J. Appl. Phys. **61**, SC1073 (2022).

- 17) L. M. Lin, Y. Luo, P. T. Lai, and K. M. Lau, Thin Solid Films 515, 2111 (2006).

- 18) T. Yamada, J. Ito, R. Asahara, K. Watanabe, M. Nozaki, S. Nakazawa, Y. Anda, M. Ishida, T. Ueda, A. Yoshigoe, T. Hosoi, T. Shimura, and H. Watanabe, J. Appl. Phys. **121**, 035303 (2017).

- 19) Y. Nakano, T. Kachi, and T. Jimbo, Appl. Phys. Lett. **83**, 4336 (2003).

- 20) T. Yamada, K. Watanabe, M. Nozaki, H. Yamada, T. Takahashi, M. Shimizu, A. Yoshigoe, T. Hosoi, T. Shimura, and H. Watanabe, Appl. Phys. Express 11, 015701 (2018).

- 21) T. Yamada, D. Terashima, M. Nozaki, H. Yamada, T. Takahashi, M. Shimizu, A. Yoshigoe, T. Hosoi, T. Shimura, and H. Watanabe, Jpn. J. Appl. Phys. **58**, SCCD06 (2019).

- 22) J. Hasegawa, M. Noguchi, M. Furuhashi, S. Nakata, T. Iwasaki, T. Kodera, T. Nishimura, and M. Hatano, Extended Abstract of the 2014 International Conference on Solid State Devices and Materials, Tsukuba, 2014, p.386.

- 23) Y. Fujino and K. Kita, J. Appl. Phys. 120, 085710 (2016).

- 24) D. Okamoto, M. Sometani, S. Harada, R. Kosugi, Y. Yonezawa, and H. Yano, Appl. Phys. A 123:133 (2017).

- 25) B. Mikake, T. Kobayashi, H. Mizobata, M. Nozaki, T. Shimura, and H. Watanabe, Appl. Phys. Express **16**, 031004 (2023).

- 26) D. V. Lang J. Appl. Phys. 45, 3023 (1974).

- 27) P. van Staa, H. Rombach, and R. Kassing, J. Appl. Phys. **54**, 4014 (1983).

- 28) T. Hatakeyama, M. Sometani, K. Fukuda, H. Okumura, and T. Kimoto, Jpn. J. Appl. Phys. **54**, 111301 (2015).

- 29) T. Ohashi, Y. Nakabayashi, and R. Iijima, IEEE Trans. Electron Devices 65, 2707 (2018).

- 30) H. Okada, Materials Science Forum 963, 213 (2019).

- 31) C. M. Jackson, A. R. Arehart, T. J. Grassman, B. McSkimming, J. S. Speck, and S. A. Ringel, ECS J. Solid State Sci. Technol. **6**, 489 (2017).

- 32) S. Huang, X. Wang, X. Liu, R. Zhao, W. Shi, Y. Zhang, J. Fan, H. Yin, K. Wei, Y. Zheng, J. Shi, X. Wang, W. Wang, Q. Sun, and K. J. Chen, J. Appl. Phys. **126**, 164505 (2019).

- 33) K. Deng, X. Wang, S. Huang, Q. Jiang, H. Yin, J. Fan, G. Jing, Y. Wang, T. Luan, K. Wei, Y. Zheng, J. Shi, and X. Liu, Appl. Surf. Sci. **607**, 154937 (2023).

- 34) M. El-Khatib, P. Ferrandis, E. Morvan, G. Guillot, and G. Bremond, J. Physics: Conf. Series **1190**, 012013 (2019).

- 35) A. Weiss, "Semiconductor Investigations with the DLTFS (Deep-Level Transient Fourier Spectroscopy) Method" Ph.D. thesis, University of the Country of Hessen, Kassel, 1991, p.10.

- 36) Y. Wada, M. Nozaki, T. Hosoi, T. Shimura, and H. Watanabe, Jpn. J. Appl. Phys. **59**, SMMA03 (2020).

- 37) T. Hosoi, K. Kutsuki, G. Okamoto, M. Saito, T. Shimura, and H. Watanabe, Appl. Phys. Lett. **94**, 202112 (2009).

- 38) T. Hashizume, S. Kaneki, T. Oyobiki, Y. Ando, S. Sasaki, and K. Nishiguchi, Appl. Phys. Express 11, 124102 (2018).

- 39) Y. Tokuda, Y. Matsuoka, H. Ueda, O. Ishiguro, N. Soejima, and T. Kachi, Superlattices and Microstructures **40**, 268 (2006).

- 40) Z. Q. Fang, D. C. Look, and L. Polenta, J. Phys. Condens. Matter 14, 13061 (2002).

- 41) M. Horita, T. Narita, T. Kachi, and J. Suda, Appl. Phys. Lett. **118**, 012106 (2021).

- 42) J. L. Lyons, C. G. Van de Walle, npj Comput. Mater. 3, 12 (2017).

- 43) C. Gong, E. Simoen, N. Posthuma, E. Van Kerschaver, J. Poortmans, and R. Mertens, Appl. Phys. Lett. **96**, 103507 (2010).

- 44) H. Mizobata, K. Tomigahara, M. Nozaki, T. Kobayashi, A. Yoshigoe, T. Hosoi, T. Shimura, and H. Watanabe, Appl. Phys. Lett. **121**, 062104 (2022).

- 45) E. H. Poindexter and W. L. Warren, J. Electrochem. Soc., 142, 2508 (1995).

- 46) P. E. Blöchl, Phys. Rev. B 62, 6158 (2000).

### Figure caption

Fig. 1. Bidirectional *C-V* curves of SiO<sub>2</sub>/GaN MOS capacitors (a) without (as-depo.) and (b) with 800 °C annealing. Multi-frequency measurements ranging from 1 kHz to 1 MHz were carried out at room temperature. Capacitance equivalent thickness (CET) values, estimated from the maximum accumulation capacitance, are shown in the figures.

Fig. 2. DLTS spectra of SiO<sub>2</sub>/GaN MOS capacitors (a) without (as-depo.) and (b) with 800 °C annealing. Pulse bias ( $V_P$ ) was applied at |5 V|. Pulse width ( $T_P$ ) was set at 0.02, 2 and 200 ms with period width ( $T_W$ ) of 512 ms. The schematic image of voltage transient in the measurement is shown in the inset.

Fig. 3. Energy distribution of  $D_{it}$  obtained by the DLTS spectra with the pulse width  $(T_P)$  of 0.02 ms and the period width  $(T_W)$  of 512 ms. Note that the energy axis of the  $D_{it}$  was calculated by assuming capture cross section to be  $6\times10^{-15}$  cm<sup>2</sup>.

Fig. 4. Pulse width  $(T_P)$  dependence of DLTS signals (a) without (as-depo.) and (b) with 800 °C annealing at several temperatures. Pulse bias  $(V_P)$  was applied at |5 V| with period width  $(T_W)$  of 512 ms.

Fig. 5. Energy distribution of oxide trap state density and capture cross section calculated by pulse width  $(T_P)$  dependent measurement. Note that the capture cross section was calculated at each energy. The results of the normal DLTS (capacitance transient measurement) were also shown to confirm the results of the CC-Mode.

Fig. 6. (a) Schematic illustration and (b) energy diagram of interface traps and oxide traps in SiO<sub>2</sub>/GaN structure without 800 °C annealing (as-depo.). The value of the

conduction band offset (AEC) of SiO2/GaN structure was referred for the similar structure of the SiO<sub>2</sub>/n-GaN(0001) [44].

Fig. 1. Bidirectional C-V curves of  $SiO_2$ /GaN MOS capacitors (a) without (as-depo.) and (b) with 800 °C annealing. Multi-frequency measurements ranging from 1 kHz to 1 MHz were carried out at room temperature. Capacitance equivalent thickness (CET) values, estimated from the maximum accumulation capacitance, are shown in the figures.

12

1.2

200 ms

450

400

Fig. 2. DLTS spectra of SiO<sub>2</sub>/GaN MOS capacitors (a) without (as-depo.) and (b) with 800 °C annealing. Pulse bias (V<sub>P</sub>) was applied at |5 V|. Pulse width (T<sub>P</sub>) was set at 0.02, 2 and 200 ms with period width (T<sub>w</sub>) of 512 ms. The schematic image of voltage transient in the measurement is shown in the inset.

Fig. 3. Energy distribution of  $D_{it}$  obtained by the DLTS spectra with the pulse width  $(T_p)$  of 0.02 ms and the period width  $(T_w)$  of 512 ms. Note that the energy axis of the  $D_{it}$  was calculated by assuming capture cross section to be  $6\times10^{-15}$  cm<sup>2</sup>.

Fig. 4. Pulse width  $(T_P)$  dependence of DLTS signals (a) without (as-depo.) and (b) with 800 °C annealing at several temperatures. Pulse bias  $(V_P)$  was applied at  $|5\ V|$  with period width  $(T_W)$  of 512 ms.

Fig. 5. Energy distribution of oxide trap state density and capture cross section calculated by pulse width  $(T_P)$  dependent measurement. Note that the capture cross section was Calculated at each energy. The results of the normal DLTS (capacitance transient measurement) were also shown to confirm the results of the CC-Mode.

Fig. 6. (a) Schematic illustration and (b) energy diagram of interface traps and oxide traps in  $SiO_2/GaN$  structure without 800 °C annealing (as-depo.). The value of the conduction band offset ( $\Delta E_c$ ) of  $SiO_2/GaN$  structure was referred for the similar structure of the  $SiO_2/n$ -GaN(0001) [44].