| Title        | Passivation of hole traps in SiO <sub>2</sub> /GaN metal-<br>oxide-semiconductor devices by high-density<br>magnesium doping                                             |

|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Mizobata, Hidetoshi; Nozaki, Mikito; Kobayashi,<br>Takuma et al.                                                                                                         |

| Citation     | Applied Physics Express. 2023, 16(10), p. 105501                                                                                                                         |

| Version Type | АМ                                                                                                                                                                       |

| URL          | https://hdl.handle.net/11094/92711                                                                                                                                       |

| rights       | This Accepted Manuscript is available for reuse under a CC BY-NC-ND licence after the 12 month embargo period provided that all the terms of the licence are adhered to. |

| Note         |                                                                                                                                                                          |

### The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

#### **ACCEPTED MANUSCRIPT**

**@**⊕\$≘

## Passivation of hole traps in SiO<sub>2</sub>/GaN metal-oxide-semiconductor devices by high-density magnesium doping

To cite this article before publication: Hidetoshi Mizobata et al 2023 Appl. Phys. Express in press https://doi.org/10.35848/1882-0786/acfc95

### Manuscript version: Accepted Manuscript

Accepted Manuscript is "the version of the article accepted for publication including all changes made as a result of the peer review process, and which may also include the addition to the article by IOP Publishing of a header, an article ID, a cover sheet and/or an 'Accepted Manuscript' watermark, but excluding any other editing, typesetting or other changes made by IOP Publishing and/or its licensors"

This Accepted Manuscript is © 2023 The Japan Society of Applied Physics.

During the embargo period (the 12 month period from the publication of the Version of Record of this article), the Accepted Manuscript is fully protected by copyright and cannot be reused or reposted elsewhere.

As the Version of Record of this article is going to be / has been published on a subscription basis, this Accepted Manuscript will be available for reuse under a CC BY-NC-ND 3.0 licence after the 12 month embargo period.

After the embargo period, everyone is permitted to use copy and redistribute this article for non-commercial purposes only, provided that they adhere to all the terms of the licence <a href="https://creativecommons.org/licences/by-nc-nd/3.0">https://creativecommons.org/licences/by-nc-nd/3.0</a>

Although reasonable endeavours have been taken to obtain all necessary permissions from third parties to include their copyrighted content within this article, their full citation and copyright line may not be present in this Accepted Manuscript version. Before using any content from this article, please refer to the Version of Record on IOPscience once published for full citation and copyright details, as permissions may be required. All third party content is fully copyright protected, unless specifically stated otherwise in the figure caption in the Version of Record.

View the article online for updates and enhancements.

# Passivation of hole traps in SiO<sub>2</sub>/GaN metal-oxide-semiconductor devices by high-density magnesium doping

Hidetoshi Mizobata<sup>1\*</sup>, Mikito Nozaki<sup>1</sup>, Takuma Kobayashi<sup>1</sup>, Takayoshi Shimura<sup>1</sup>, and Heiji Watanabe<sup>1\*</sup>

<sup>1</sup>Graduate School of Engineering, Osaka University, 2-1 Yamadaoka, Suita, Osaka 565-0871, Japan

E-mail: mizobata@prec.eng.osaka-u.ac.jp, watanabe@prec.eng.osaka-u.ac.jp

A major challenge in GaN-based metal-oxide-semiconductor (MOS) devices is significant hole trapping near the oxide/GaN interface. In this study, we show that the density and energy level of the hole traps depend crucially on the concentration of magnesium (Mg) dopants in GaN layers. Although the surface potential of a conventional SiO<sub>2</sub>/p-GaN MOS device is severely pinned by hole trapping, hole accumulation and very low interface state densities below 10<sup>11</sup> cm<sup>-2</sup> eV<sup>-1</sup> are demonstrated for MOS capacitors on heavily Mg-doped GaN epilayers regardless of the degree of dopant activation. These findings indicate the decisive role of Mg atoms in defect passivation.

Gallium nitride (GaN) is a promising material for next-generation power devices because it is a wide-bandgap semiconductor that exhibits electrical properties superior to those of silicon (Si), such as a high breakdown electric field and high electron saturation velocity. Among the various GaN-based electronic devices, metal-oxide-semiconductor field-effect transistors (MOSFETs) are one of the most important and fundamental devices. Since advances in GaN growth techniques have made it possible to fabricate high-quality freestanding substrates and epitaxial layers, vertical GaN MOSFETs, such as trench MOSFETs and double-diffused MOSFETs capable of high-current operation, have been intensively investigated. To realize the inherently high level of performance of GaN-based MOSFETs, it is essential to form high-quality MOS structures with low defect densities.

Considering the wide energy bandgap of GaN, gate dielectrics for MOS devices should be oxide insulators with a sufficiently wider bandgap than that of GaN and a large band offset relative to GaN. There are a limited number of oxides with the above properties, and, previously, GaN MOS devices with silicon dioxide (SiO<sub>2</sub>), alumina (Al<sub>2</sub>O<sub>3</sub>), aluminum silicate (AlSiO) dielectrics were investigated.<sup>8–16</sup> However, most of those studies investigated n-type GaN MOS capacitors and evaluated electrical defects near the conduction band edge located near the oxide/GaN interface. We fabricated GaN MOS capacitors with SiO<sub>2</sub> gate dielectrics formed by plasma-enhanced chemical vapor deposition (PECVD).<sup>17,18</sup> Interface engineering was conducted by means of thin Ga-oxide (GaO<sub>x</sub>) interlayers between the SiO<sub>2</sub> dielectrics and GaN substrates and the subsequent post-deposition annealing (PDA). As a result, very low interface state density (*D*<sub>it</sub>) values below 10<sup>14</sup> cm<sup>-2</sup> eV<sup>-1</sup> and a high dielectric breakdown electric field above 8 MV cm<sup>-1</sup> were demonstrated for n-type GaN MOS capacitors.<sup>17,18</sup>

In contrast, there are few reports on p-type GaN MOS capacitors that had well-behaved capacitance-voltage (*C-V*) characteristics. <sup>19–24</sup> Because of the significant number of hole traps located near the oxide/GaN interfaces, a large C-V hysteresis is usually observed for p-type MOS capacitors.<sup>25</sup> Even worse, the surface potential of GaN is pinned and an ideal amount of hole accumulation at the MOS interface hardly occurs regardless of the gate dielectric materials used. Although GaO<sub>x</sub> layers at the oxide/GaN interface and/or disordered Mg-segregation layers at the GaN surface might be origins of the hole traps, 20,21,25,26 the details of the hole trapping mechanism remain unclear. Recently, we demonstrated good C-V characteristics for SiO<sub>2</sub>/p-GaN MOS capacitors fabricated by high-dose Mg-implantation and dopant activation by means of ultra-high-pressure annealing (UHPA) at 1400°C.<sup>27</sup> The fabricated MOS capacitors exhibited mostly ideal C-V characteristics, for which there were negligible hysteresis and a reasonable amount of hole accumulation. The acceptor concentration  $(N_A)$  estimated from the C-V curves was about  $2 \times 10^{18}$  cm<sup>-3</sup>, which agrees with the concentration of implanted Mg atoms and showed the superiority of UHPA for activation of implanted dopants. However, at present, we have no clear explanation why hole trapping centers are passivated in the case of the highly doped GaN substrate and what the decisive factor is in defect passivation. Additionally, the threshold voltage  $(V_{TH})$  of the n-channel MOSFETs is controlled in accordance with the Fermi level of the p-type regions, and hole trapping near the oxide/p-GaN interface needs to be suppressed to improve the  $V_{\rm TH}$  stability that determines the long-term reliability of MOSFETs. Therefore, in this study, we investigated the impact of varying the Mg concentration in epitaxially grown (not ion-implanted) GaN substrates on the electrical properties of the oxide/GaN interfaces to seek clues to designing highquality dielectric/p-GaN interfaces.

We used p-type GaN epilayers with various Mg concentrations grown by metalorganic vapor-phase epitaxy (MOVPE) on n-type GaN(0001) freestanding wafers. The Mg concentration in the epilayers was varied from about  $7 \times 10^{16}$  to  $2 \times 10^{19}$  cm<sup>-3</sup>. After wetcleaning with acetone ultrasonication and a 50% hydrofluoric (HF) acid solution, the substrates were annealed in a nitrogen atmosphere at 800°C for 20 minutes to activate the Mg dopants by dehydrogenation. Then, about 5-nm-thick SiON layers serving as a Ga diffusion barrier were deposited directly on the cleaned GaN surface and 15-nm-thick SiO<sub>2</sub> films were subsequently deposited by PECVD using tetraethyl orthosilicate (TEOS)/O<sub>2</sub>/N<sub>2</sub> and TEOS/O<sub>2</sub> gas mixtures. The details of the film deposition conditions and impact of the thin SiON interlayer on the reliability of GaN MOS devices are described elsewhere. 17,18 The dielectric films were patterned by conventional photolithography to form top contacts for electrical measurements. Palladium (Pd) was deposited by vacuum evaporation, and Pd/p-GaN top contacts and gate electrodes with a diameter of 100 µm on the SiO<sub>2</sub> layers were formed by photolithography and subsequent wet etching. We also fabricated MOS capacitors without activation (dehydrogenation) annealing of Mg-doped GaN layers. Moreover, an n-type GaN MOS capacitor was fabricated in the same manner as the p-type capacitors for comparison, in which nickel (Ni) gate electrodes and aluminum (Al) back contacts were formed by vacuum evaporation. The fabricated p-type and n-type GaN MOS capacitors were examined by making bidirectional multi-frequency C-V measurements to evaluate the electrical properties of the oxide/GaN interfaces.

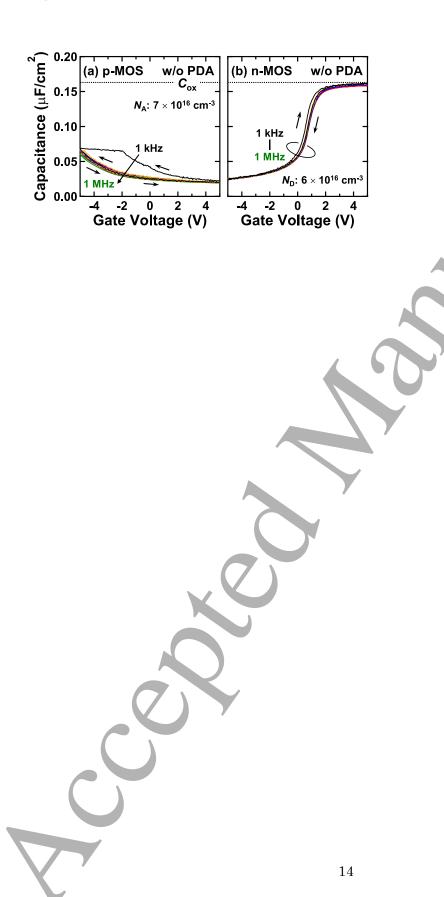

Figures 1(a) and 1(b) show typical C-V curves obtained from SiO<sub>2</sub>/GaN MOS capacitors fabricated on p-type and n-type epilayers, respectively. Bidirectional C-V curves were acquired at a frequency of 1 kHz by sweeping the gate bias from positive

(negative) to negative (positive) and vice versa for the p-type (n-type) capacitor, as indicated by the black lines and arrows. Then, multi-frequency measurements were conducted at frequencies ranging from 1 kHz to 1 MHz. As for the n-type capacitor (Fig. 1(b)), while a small C-V hysteresis was observed for the first bidirectional scan at 1 kHz, well-behaved C-V characteristics with negligible hysteresis and frequency dispersion were achieved even without any post annealing treatment. The capacitance-equivalent thickness (CET = 21 nm) estimated from the maximum oxide capacitance ( $C_{ox}$ ) coincided with the gate oxide thickness (~21 nm) estimated from spectroscopic ellipsometry, as indicated by the horizontal dotted line. This implies an ideal electron accumulation at the  $SiO_2/n$ -GaN interface, as previously reported. <sup>17,18</sup> The donor concentration ( $N_D$ ) determined from the relationship between  $1/C^2$  and gate voltage ( $V_g$ ) was  $6 \times 10^{16}$  cm<sup>-3</sup>. On the other hand, the C-V characteristics of the p-type capacitor were severely degraded by hole trapping, as shown in Fig. 1(a). Significant hysteresis was observed in the first scan, in which the maximum capacitance was far below the expected  $C_{ox}$  value. The acceptor concentration extracted from the  $1/C^2$  versus  $V_{\rm g}$  plots for the depletion region  $(N_A = 7 \times 10^{16} \text{ cm}^{-3})$  agreed well with the concentration of Mg atoms (about  $7 \times 10^{16} \text{ cm}^{-3}$ <sup>3</sup>), suggesting activation of Mg dopants. These results imply hard pinning of the surface potential of the p-type capacitor owing to hole trapping at the SiO<sub>2</sub>/p-GaN interface. Furthermore, subsequently obtained C-V curves completely overlapped with the backward sweep of the first scan regardless of the measurement frequency, meaning that the trapped holes were hard to de-trap even when a positive gate bias was applied and that they acted as fixed charges in the MOS structure.

Next, we investigated the effect of varying the Mg concentration on the C-V characteristics of p-type GaN MOS capacitors. Figure 2 shows the change in the

bidirectional 1-kHz C-V curves of the p-type MOS capacitors depending on the Mg concentration of the GaN epilayers. The  $N_A$  values determined from  $1/C^2$  versus  $V_g$  plots are indicated in the figures. It should be noted that the hole trapping phenomena are crucially dependent on N<sub>A</sub> of the p-GaN substrates. Although the maximum capacitance for the low and medium  $N_A$  samples was far below the  $C_{ox}$  value indicated by the horizontal dotted lines (Figs. 2(a) and 2(b)), a reasonable number of holes accumulated in the high  $N_A$  sample (Fig. 2(c)). In addition, no C-V hysteresis was observed in the high N<sub>A</sub> sample. These results imply a significant reduction in hole traps near the SiO<sub>2</sub>/GaN interface only for the highly Mg-doped sample. The ideal C-V curves depending on the  $N_{\rm A}$  of p-GaN layers are plotted as dashed red lines in the figures, where the flatband voltage  $(V_{\rm FB})$  is shifted to fit the C-V curves in the depletion regions. The ideal curve for the high  $N_A$  sample in Fig. 2(c) appears to be flat because the high  $N_A$  of the p-GaN substrate resulted in the increased minimum capacitance, but the ideal curve overlapped with the experimental one. On the other hand, as for the forward sweeps of the low and medium samples, both the maximum capacitance and the gate voltage showed a discrepancy between the experimental and ideal values that became pronounced depending on the doping conditions, suggesting a change in the density and energy distribution of hole traps near the interface. On the basis of these findings and previous reports, <sup>19-26</sup> it can be concluded that, rather than the UHPA process, <sup>27</sup> the concentration of Mg atoms and/or the Fermi level of the p-GaN substrate play a decisive role in the passivation of hole traps.

To discriminate which of the above causes plays the dominant role in defect passivation, we fabricated MOS capacitors on a heavily Mg-doped GaN epilayer ( $2 \times 10^{19}$  cm<sup>-3</sup>) without intentional dopant activation, where SiO<sub>2</sub> dielectrics were deposited on the GaN

epilayer without activation annealing, except for sintering at 550°C to reduce the contact resistance of the top Pd/p-GaN interface for the C-V measurements. As previously reported, Mg atoms exist in the form of Mg-H complexes in as-deposited GaN epilayers, so high-temperature dehydrogenation annealing over 700°C is needed to electrically activate the Mg dopants as acceptors. 28-32 Figure 3(a) shows bidirectional C-V curves of the GaN MOS capacitor taken at a measurement frequency of 1 kHz. The  $N_A$  value (2 ×  $10^{17}$  cm<sup>-3</sup>) in this case was much lower than the Mg concentration (2 ×  $10^{19}$  cm<sup>-3</sup>), indicating partial activation (ionization) of Mg dopants, as expected. Note that, whereas the MOS capacitor fabricated without activation exhibited a mostly identical  $N_A$  value to that of the medium sample in Fig. 2(b), the C-V characteristics in Fig. 3(a) are wellbehaved. As shown by the horizontal dotted line, ideal hole accumulation corresponding to de-pinning of surface potential at the SiO<sub>2</sub>/p-GaN interface occurred in the highly Mgdoped sample without activation. These results clearly demonstrate that the concentration of Mg atoms (and/or Mg-H complexes), not the N<sub>A</sub> values or the Fermi level of the GaN layers, plays the decisive role in passivation of hole traps near the SiO<sub>2</sub>/GaN interface. The passivation of hole traps is presumably caused by the interaction of highly doped Mg atoms with defects responsible for hole trapping, such as oxygen vacancies in gallium oxide interlayers. However, theoretical studies based on first-principles calculations are essential to understand detailed mechanisms, and those are issues to be addressed in the future.

Finally, the defect density at the p-type MOS interface formed on the highly Mg-doped epilayer without activation annealing was examined in two ways. Figure 3(b) represents the frequency dispersion of the forward *C-V* curves taken from the p-type GaN MOS capacitor studied in Fig. 3(a). As mentioned above, a reasonable amount of hole

accumulation was observed at low frequencies below 1 kHz, but the maximum capacitance gradually decreased as the measurement frequency increased. This is probably due to the high contact resistance at the top Pd/p-GaN interface. This means that the sintering treatment at 550°C is insufficient for obtaining a top contact with Ohmic characteristics, which makes it difficult to conduct the conventional high-low-method evaluation of the defect density. Therefore, as indicated by the solid red curve in Fig. 3(c), the measured 100-kHz *C-V* curve (dashed red curve) was corrected by taking the series resistance into account.<sup>33</sup> Note that the corrected 100-kHz *C-V* curve completely overlapped the measured quasi-static (QS) curve, indicating that the defect density was very low in the lower half of the bandgap of GaN.

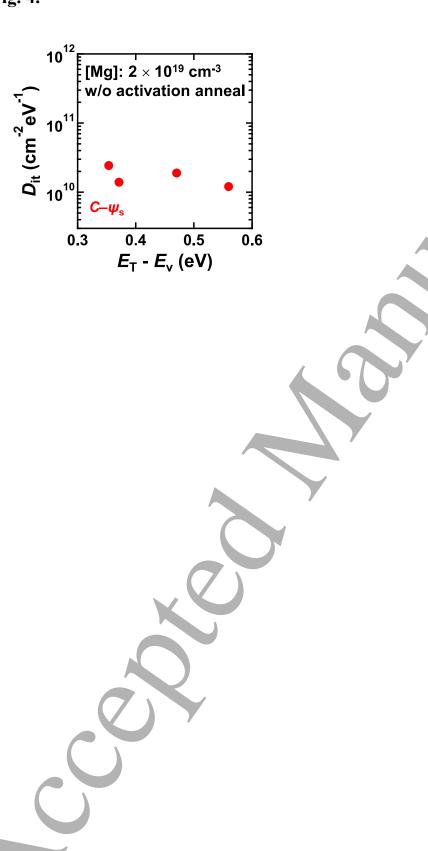

Furthermore, we used the C- $\psi_s$  method proposed by Yoshioka et~al. to evaluate  $D_{it}$ . This method utilizes the theoretical capacitance (the theoretical C-V curve) instead of high-frequency measurements and provides reasonable  $D_{it}$  values for silicon carbide (SiC) MOS devices. The red circles in Fig. 4 represent the  $D_{it}$  distribution for a p-type GaN MOS capacitor fabricated on the highly Mg-doped GaN epilayer without activation annealing. Although this method has difficulty in determining an accurate surface potential in the MOS structure, extremely low  $D_{it}$  values close to the detection limit of our electrical measurement system were obtained. Considering the hard pinning of the surface potential in conventional p-type GaN MOS devices, this is an unprecedented achievement to the best of our knowledge. Although we have no detailed model of the Mg-related defect passivation mechanism at present, the findings described above provide a valuable clue to designing high-quality MOS structures for future GaN-based devices.

In conclusion, we systematically investigated hole trapping phenomena in p-type GaN

MOS devices depending on the concentration of Mg dopants and their degree of activation. We found that, in contrast to n-type MOS devices, p-type devices are severely degraded by hole trapping near the SiO<sub>2</sub>/GaN interface. When conventional p-type GaN substrates with low and moderate  $N_A$  of around  $10^{17}$  cm<sup>-3</sup> or less are used, the surface potential of the p-type MOS structure is severely pinned due to hole trapping and ideal hole accumulation at the MOS interface is hardly observed. However, the devices formed on highly Mg-doped GaN epilayers had ideal hole accumulation regardless of  $N_A$  i.e., the Fermi level of the GaN layers, indicating the decisive role of Mg atoms in passivation of hole traps. Consequently, an extremely low  $D_{it}$  below  $10^{11}$  cm<sup>-2</sup> eV<sup>-1</sup> was demonstrated for p-type GaN MOS devices.

### **Acknowledgments**

This work was supported by the MEXT-Program for Creation of Innovative Core Technology for Power Electronics (Grant No. JPJ009777) and JSPS KAKENHI (Grant No. 23K13367).

### References

- 1) S. J. Pearton, J. C. Zolper, R. J. Shul, and F. Ren, J. Appl. Phys. 86, 1 (1999).

- 2) B. J. Baliga, Semicond. Sci. Technol. 28, 074011 (2013).

- 3) T. Kachi, Jpn. J. Appl. Phys. 53, 100210 (2014).

- 4) M. Kodama, M. Sugimoto, E. Hayashi, N. Soejima, O. Ishiguro, M. Kanechika, K. Itoh, H. Ueda, T. Uesugi, and T. Kachi, Appl. Phys. Express 1, 021104 (2008).

- 5) H. Otake, K. Chikamatsu, A. Yamaguchi, T. Fujishima, and H. Ohta, Appl. Phys. Express 1, 011105 (2008).

- 6) T. Oka, Y. Ueno, T. Ina, and K. Hasegawa, Appl. Phys. Express 7, 021002 (2014).

- 7) S. Takashima, K. Ueno, H. Matsuyama, T. Inamoto, M. Edo, T. Takahashi, M. Shimizu, and K. Nakagawa, Appl. Phys. Express 10, 121004 (2017).

- 8) K. Yamaji, M. Noborio, J. Suda and T. Kimoto, Jpn. J. Appl. Phys. 47, 7784 (2008).

- 9) E. Kim, N. Soejima, Y. Watanabe, M. Ishiko and T. Kachi, Jpn. J. Appl. Phys. 49, 04DF08 (2010).

- 10) S. Takashima, Z. Li and T. P. Chow, Jpn. J. Appl. Phys. 52, 08JN24 (2013).

- 11) K. Aoshima, N. Taoka, M. Horita and J. Suda, Jpn. J. Appl. Phys. 61, SC1073 (2022).

- 12) P. D. Ye, B. Yang, K. K. Ng, J. Bude, G. D. Wilk, S. Halder and J. C. M. Hwang, Appl. Phys. Lett. **86**, 063501 (2005).

- 13) S. Huang, S. Yang, J. Roberts and K. J. Chen, Jpn. J. Appl. Phys. 50, 110202 (2011).

- 14) S. Kaneki, J. Ohira, S. Toiya, Z. Yatabe, J. T. Asubar and T. Hashizume, Appl. Phys. Lett. 109, 162104 (2016).

- 15) D. Kikuta, K. Itoh, T. Narita and T. Mori, J. Vac. Sci. Technol. A 35, 01B122 (2017).

- 16) D. Kikuta, K. Ito, T. Narita and T. Kachi, Appl. Phys. Express 13, 026504 (2020).

- 17) T. Yamada, K. Watanabe, M. Nozaki, H. Yamada, T. Takahashi, M. Shimizu, A.

- Yoshigoe, T. Hosoi, T. Shimura and H. Watanabe, Appl. Phys. Express 11, 015701 (2018).

- 18) T. Yamada, D. Terashima, M. Nozaki, H. Yamada, T. Takahashi, M. Shimizu, A.

- Yoshigoe, T. Hosoi, T. Shimura and H. Watanabe, Jpn. J. Appl. Phys. 58, SCCD06 (2019).

- 19) Y. Nakano, T. Kachi and T. Jimbo, J. Vac. Sci. Technol. B 21, 2220 (2003).

- 20) K. Zhang, M. Liao, M. Imura, T. Nabatame, A. Ohi, M. Sumiya, Y. Koide and L. Sang, Appl. Phys. Express 9, 121002 (2016).

- 21) L. Sang, B. Ren, M. Liao, Y. Koide and M. Sumiya, J. Appl. Phys. 123, 161423 (2018).

- 22) B. Ren, M. Liao, M. Sumiya, J. Su, X. Liu, Y. Koide and L. Sang, J. Phys. D 52, 085105 (2019).

- 23) K. Kim, J. Kim, J. Gong, D. Liu and Z. Ma, Jpn. J. Appl. Phys. 59, 030908 (2020).

- 24) L. Sang, B. Ren, T. Nabatame, M. Sumiya and M. Liao, J. Alloy Compd. **853**, 157356 (2021).

- 25) M. Akazawa, Y. Tamamura, T. Nukariya, K. Kubo, T. Sato, T. Narita and T. Kachi, J. Appl. Phys. **132**, 195302 (2022).

- 26) T. Hashizume, J. Appl. Phys. 94, 431 (2003).

- 27) Y. Wada, H. Mizobata, M. Nozaki, T. Kobayashi, T. Hosoi, T. Kachi, T. Shimura and H. Watanabe, Appl. Phys. Lett. **120**, 082103 (2022).

- 28) H. Amano, M. Kito, K. Hiramatsu and I. Akasaki, Jpn. J. Appl. Phys. 28, L2112 (1989).

- 29) S. Nakamura, N. Iwasa, M. Senoh and T. Mukai, Jpn. J. Appl. Phys. 31, 1258 (1992).

- 30) T. Narita, H. Yoshida, K. Tomita, K. Kataoka, H. Sakurai, M. Horita, M. Bockowski,

- N. Ikarashi, J. Suda, T. Kachi and Y. Tokuda, J. Appl. Phys. 128, 090901 (2020).

- 31) S. Nakamura, T. Mukai, M. Senoh and N. Iwasa, Jpn. J. Appl. Phys. 31, L139 (1992).

- 32) D. H. Youn, M. Lachab, M. Hao, T. Sugahara, H. Takenaka, Y. Naoi and S. Sakai, Jpn.

- J. Appl. Phys. 38, 631 (1999).

- 33) D. K. Schroder, *Semiconductor Material and Device Characterization* (Wiley, New York, 2006) 3rd ed.

- 34) H. Yoshioka, T. Nakamura and T. Kimoto, J. Appl. Phys. 111, 014502 (2012).

### **Figure Captions**

**Fig. 1.** Bidirectional C-V curves of SiO<sub>2</sub>/GaN MOS capacitors fabricated on (a) p-type and (b) n-type GaN epilayers. Multi-frequency measurements ranging from 1 kHz to 1 MHz were carried out. The horizontal dotted black lines indicate (expected) oxide capacitance ( $C_{ox}$ ).

Fig. 2. Bidirectional C-V curves of SiO<sub>2</sub>/p-GaN MOS capacitors with various Mg concentrations. The measurement frequency was 1 kHz. The  $N_A$  values estimated from  $1/C^2$  versus V plots were (a)  $7 \times 10^{16}$  cm<sup>-3</sup> (Low  $N_A$ ), (b)  $1 \times 10^{17}$  cm<sup>-3</sup> (Medium  $N_A$ ), and (c)  $1 \times 10^{19}$  cm<sup>-3</sup> (High  $N_A$ ). The dashed red lines and horizontal dotted lines represent ideal C-V curves and expected  $C_{ox}$  values, respectively. The ideal C-V curves are shifted to fit those of the depletion regions.

**Fig. 3.** Typical C-V characteristics of GaN MOS capacitor fabricated on the heavily Mg-doped GaN epilayer. No intentional activation annealing was conducted: (a) 1-kHz bidirectional C-V curves, (b) multi-frequency forward C-V curves taken at frequencies ranging from 1 kHz to 1 MHz, (c) comparison of QS (black) and 100-kHz C-V (red) curves. The N<sub>A</sub> value shown in (a) corresponds to partial activation of Mg dopants. The dashed and solid red lines in (c) respectively represent the measured C-V curve and that corrected by taking the series resistance into account.

**Fig. 4.** Energy distribution of  $D_{it}$  for the SiO<sub>2</sub>/p-GaN MOS capacitor fabricated on highly Mg-doped epilayer without dopant activation. The C- $\psi_s$  method was used in the  $D_{it}$  evaluation.

Fig. 1.

**Fig. 2.**

Fig. 3.

Fig. 4.