| Title        | 電子顕微鏡による半導体デバイスの解析技術に関する<br>研究   |

|--------------|----------------------------------|

| Author(s)    | 朝山, 匡一郎                          |

| Citation     | 大阪大学, 2007, 博士論文                 |

| Version Type | VoR                              |

| URL          | https://hdl.handle.net/11094/949 |

| rights       |                                  |

| Note         |                                  |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

# 電子顕微鏡による半導体デバイスの 解析技術に関する研究

2007年 9月

朝山匡一郎

# 目 次

| 第1章  | 序論・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・                     | 1          |

|------|------------------------------------------------------------|------------|

| 1. 1 | 半導体技術の進展と解析技術                                              | 1          |

| 1. 2 | 半導体解析技術における電子顕微鏡技術の発展                                      | 6          |

| 1. 3 | 半導体解析の基本的操作                                                | 7          |

| 1. 4 | 本研究の目的と内容                                                  | 8          |

| 第2章  | 本研究で対象とし改良を加えた主な不良解析技術の概要・・・・・・・・                          | 10         |

| 2.1  | TEM-EELS の概要と位置分解型 TEM-EELS の開発                            | 10         |

| 2.2  | 3次元観察電子顕微鏡法(3D CT-TEM)                                     | 28         |

| 2.3  | 電子回折による応力評価(CBED, nano-Diffraction)                        | 32         |

| 2. 4 | 集束イオンビームによる試料作製技術                                          | 39         |

| 2.5  | 微細デバイスの直接評価技術(ナノ・プローバ)                                     | <b>5</b> 3 |

| 2.6  | 半導体不良解析技術における球面収差補正電子顕微鏡への期待                               | 56         |

| 2. 7 | 厚い試料の観察技術                                                  | 65         |

| 第3章  | シリコン基板に関する不良解析・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・         | 74         |

| 3. 1 | 結晶欠陥の生成とその観察                                               | 74         |

| 3. 2 | シリコン基板の応力評価と不良解析例                                          | 78         |

| 3. 3 | 静電保護素子と静電破壊                                                | 83         |

| 第4章  | MOS トランジスタのデバイス構造の不良解析・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 88         |

| 4. 1 | MOS トランジスタのゲート酸化膜破壊解析                                      | 88         |

| 4.2  | MOSトランジスタの不純物元素に起因する不良                                     | 93         |

| 4. 3 | ゲート酸化膜の結合状態                                                | 99         |

| 4.4  | シリサイド材料の結合状態解析                                             | 103        |

| 4. 5 | ゲート酸化膜の不安定性に関する解析                                          | 116        |

| 第5草 コンタクトホール及び配線層の不良解析・・・・・・・・・・・・・        | 122  |

|--------------------------------------------|------|

| 5.1 コンタクトホールの不良解析                          | 122  |

| 5.1.1 高抵抗コンタクトホールのバリアメタルの TEM-EELS 評価      | 124  |

| 5.1.2 コンタクトホールの電流リーク不良解析                   | 133  |

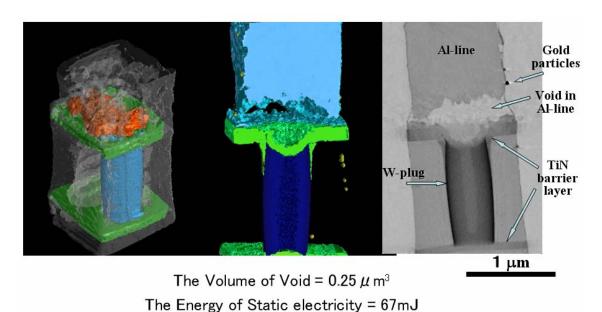

| 5.1.3 静電破壊によるコンタクトホール破壊箇所の3次元的評価           | 137  |

| 5.2 配線層の不良解析                               | 139  |

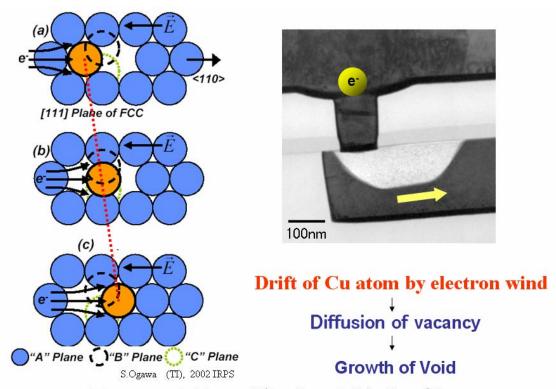

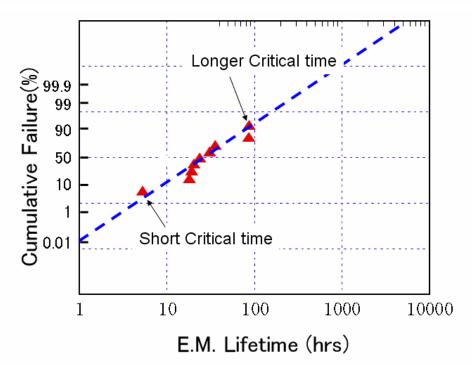

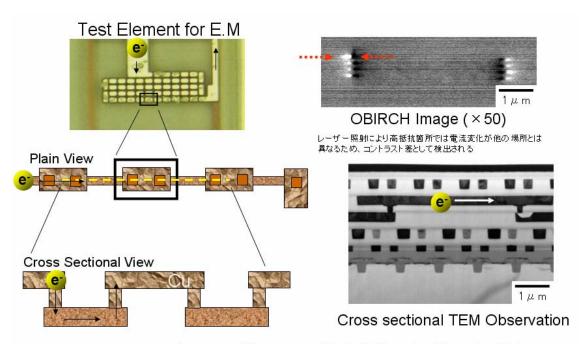

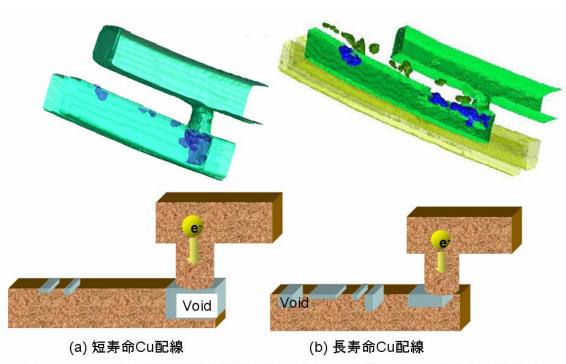

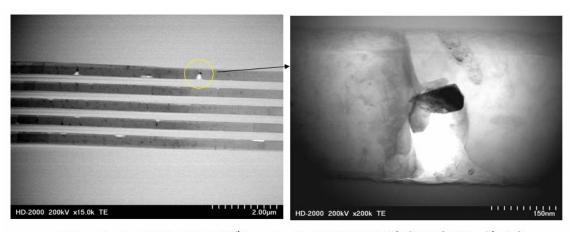

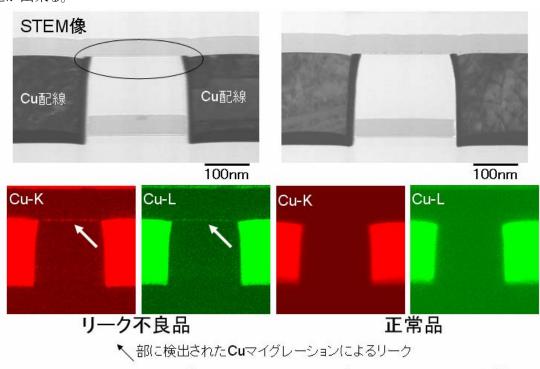

| 5.2.1 マイグレーションによる配線層信頼性解析                  | 139  |

| 5.2.2 配線間電流リーク不良の解析                        | 145  |

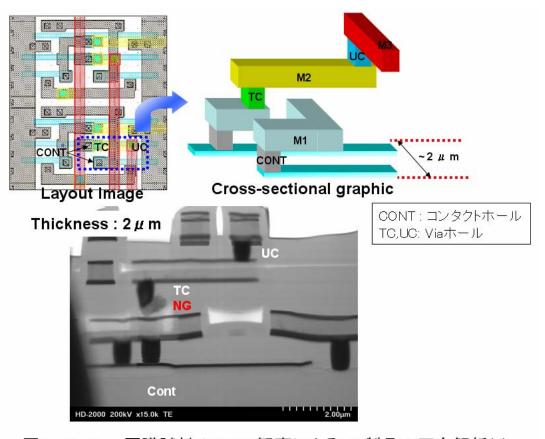

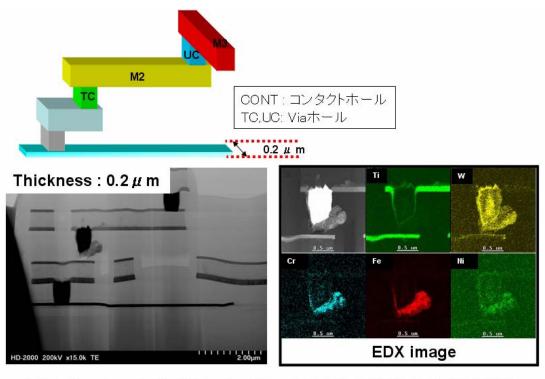

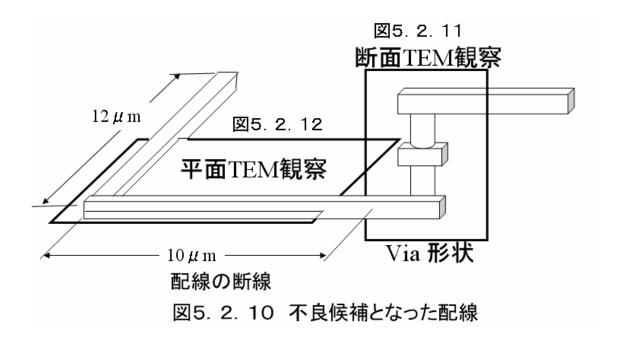

| 5.2.3 広範囲配線層の断線不良解析例                       | 146  |

| 第 6 章.その他の半導体デバイス・材料の解析・・・・・・・・・・・・・・      | 151  |

| 6.1 化合物半導体(GaAs)の結晶基板の異常成長の解析              | 151  |

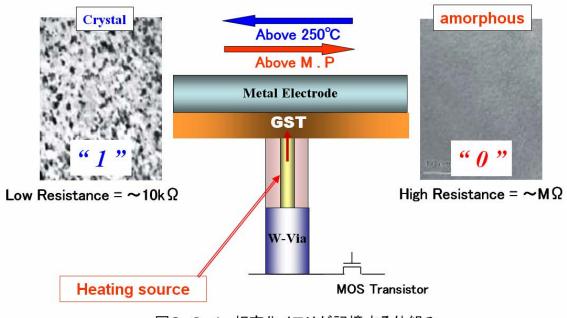

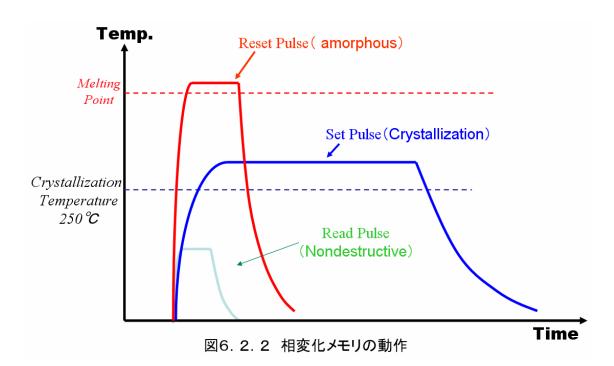

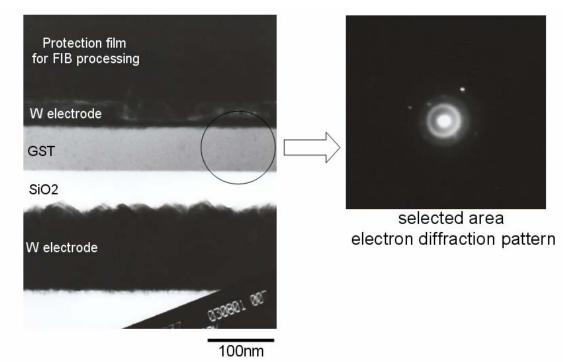

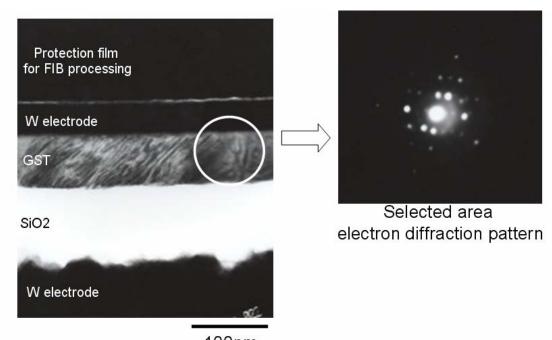

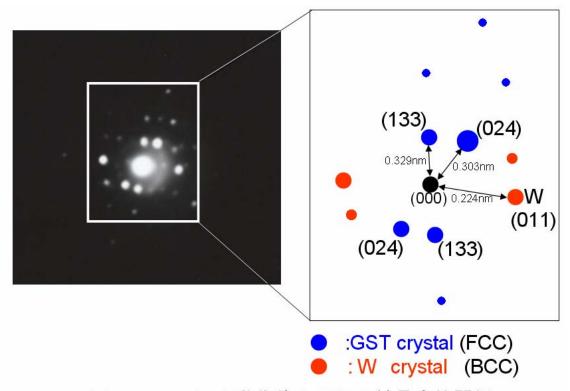

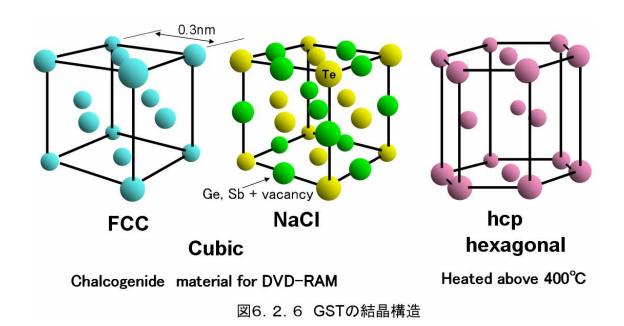

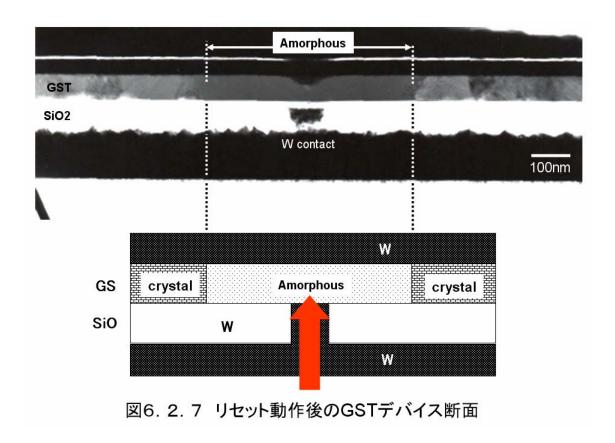

| 6.2 相変化メモリの記録状態に応じた相変化の評価                  | 153  |

|                                            | 1 20 |

| 第7章 結言・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・・ | 159  |

| 謝辞                                         | 161  |

|                                            |      |

| 本研究に関する研究発表                                | 162  |

# 第1章 序 論

#### 1.1 半導体技術の進展と解析技術

インターネットを基盤とした情報化社会の到来は、一方においてはコンピュータ・通信、 マルチメディアの融合を促し、また他方においては情報機器とシステムの統合化を加速 する。情報機器とシステムの統合は、システムの高付加価値と引き換えにシステムをよ り複雑なものとする。この複雑なシステムに対する回答が、半導体チップ上にシステム の中枢を組み込んだ「システム LSI」である。SoC(System on Chip)は、SiP(System in a Package) とともにシステム LSI を実現するための手法であり「システムの中枢機能を 1 チップのうえに集積したもの」と言える。一方、SoC を作るには①異種機能、異種技 術の混載、混合の実現、②ソフトウエアとの協調を図りソフトウエアの一部も組み込む、 ③システム設計と LSI 設計の融合、などが必要となる。また SoC の用途、要求性能も、 ①ビデオゲームやデジタルエンターテイメント機器向けの高性能、高機能な P-SoC(performance-driven SoC)、②携帯電話に代表される移動体端末機器向けの低消 費電力な Low Power SoC、そして③情報家電向けの低価格、短納期の C-SoC(Cost-driven SoC)と多様である。したがって SoC を発展させるにはこのような複雑で多様な要求に対 応できる経済的設計手法とデバイス・プロセス技術が求められる。ところが経済性、消 費電力、スケーリング則の限界がデバイス・プロセス技術の発展を妨げる危機要因とし て指摘されている。スケーリング則はこれまでの「デバイス・プロセス技術開発の指導 原理」であり、LSI の高集積化、高速化、低消費電力を推進する支柱であった。しかし このスケーリング手法はトランジスタ、多層配線、微細加工において支障をきたし始め ている。それはサイズのスケーリングに対して電源電圧のスケーリングが進まなかった ためであるが、この定電圧的なスケーリングが過去数世代続いてきた。この時代はゲー ト酸化膜にかかる電界の高電界化、別の言葉で言うと信頼性マージンを減らしながら電 流駆動能力を高めてきた時代と言える。この障害を超えるために、単純なスケーリング 則(パターン寸法や絶縁膜厚などの比例縮小)から等価的なスケーリングへの転換が必 要とされている。言い換えると、今後のスケーリングは電源電圧の低電圧化、即ち定電 界スケーリングが必要となる。この転換には高誘電率ゲート酸化膜や低誘電率層間絶縁 膜、配線用の金属材料の低抵抗化、金属間化合物材料の変更など、従来のプロセス材料 に代わる新しい材料の導入を意味しており、次世代の半導体プロセス・デバイスの開発 には「マテリアル科学の参加」が必要とされる由縁である(1)(2)。

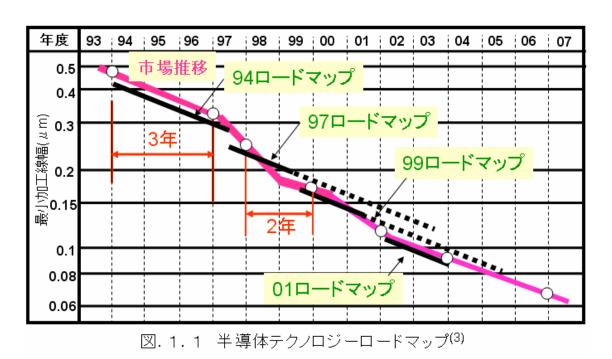

次に SoC に代表される半導体デバイスの開発スピードに関して見てみる。半導体に関係する技術ロードマップとして ITRS(<u>International Technology Roadmap</u> for Semiconductors)がある。ITRS 更新の度にトランジスタゲート長の微細化は前倒しされ

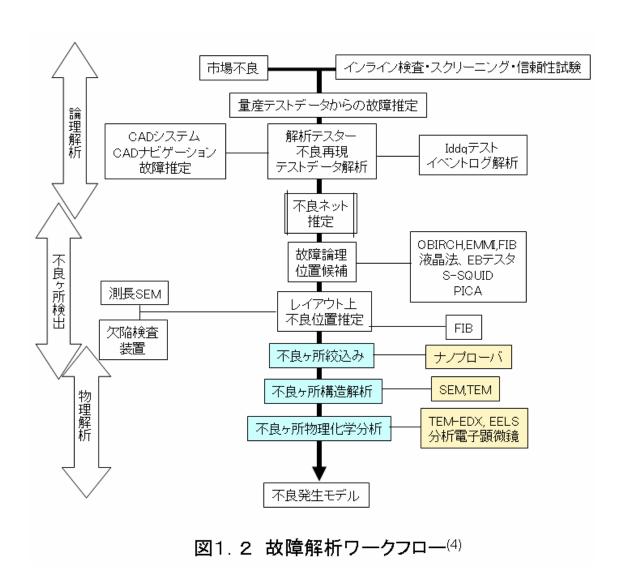

る方向にある。**図1.1**に開発スピードが加速している様子を示す<sup>(3)</sup>。1995年頃におい ては  $0.35 \mu m$  プロセスの開発に約 3 年を費やしていたのに対して、1998 年頃の  $0.18 \mu m$ プロセスの開発期間は約2年となっており、年々その傾向が強まっている。一方で最小 加工線幅が90nmより微細なULSI製造技術に関しては、欠陥検査・検出技術、測長技術、 故障解析技術等における物理的な検出限界が迫っており、製造した物が設計通りにでき ているかの確認が益々困難になると考えられる。また ULSI の性能が設計通りに出なか ったとき、どこに原因があるのかを短時間で抽出することが困難になっている。即ち、 論理設計、回路設計、デバイス開発・設計、プロセス開発、製造技術の全てにわたる故 障解析の技術が、短期間の製品開発、量産における品質向上のために重要になると考え られる。図1.2に大まかな故障解析ワークフローを示す。数億~数十億個に及ぶトラ ンジスタを実装するシステム LSI ではその論理回路や配線の複雑さのため、故障論理 を追い(論理解析)、故障箇所を同定(不良箇所検出)する手法に多大の労力、時間、費用 を費やしている。しかしながら、最終的に「なぜ故障が起きたのか」を物理モデルとし て説明するためには、故障箇所の物理解析なくしては答えられない。またこの答えなく しては製造プロセスの開発はもとより、量産歩留まりや信頼性の向上といった、産業と して最も基本的な技術を確立することさえ不可能である。図1.1にも示したように 年々加速する開発速度とともに、デバイス・プロセスの微細化は、より高い空間分解能 と検出感度を持つ物理解析技術を要求している。表1.1にデバイスの最小加工寸法(テ クノロジーノード)と要求されている分析精度を示す。本報告で多く取り上げる 65~ 100nm 近傍のテクノローノードでは、微細構造の観察に必要な空間分解能は 1nm 以下 であり、数 nm 領域のドーパントプロファイルの評価が要求されている(4)。

| 製品の出荷開始年         | 年                                   | 1999   | 2002   | 2005   | 2008   | 2011   | 2014   |  |  |

|------------------|-------------------------------------|--------|--------|--------|--------|--------|--------|--|--|

| テクノロジーノード        | nm                                  | 180    | 130    | 90     | 65     | 45     | 32     |  |  |

|                  |                                     |        |        |        |        |        |        |  |  |

| 微細形状の観察<br>分解能   | nm                                  | 1.4    | 1.0    | 0.7    | 0.5    | 0.4    | 0.3    |  |  |

| ホール底部観察<br>分解能   | nm                                  | 2.8    | 2.0    | 1.4    | 1.0    | 0.7    | 0.5    |  |  |

| パターン寸法の測定        | nm                                  | 3.6    | 2.6    | 2.0    | 1.4    | 1.0    | 0.7    |  |  |

| 再現性              | nm                                  | 2.8    | 2.0    | 1.4    | 1.1    | 0.8    | 0.6    |  |  |

| (緻密/孤立/穴)        | nm                                  | 4.0    | 3.0    | 2.6    | 1.6    | 1.0    | 0.8    |  |  |

| 微粒子の検出感度         | nm $\phi$                           | 90     | 65     | 45     | 32     | 22     | 16     |  |  |

| 金属の検出感度          | 10 <sup>9</sup> at/cm <sup>2</sup>  | 9.4    | 4.5    | 3.0    | 2.0    | 1.5    | 1.1    |  |  |

| 有機物の検出感度         | 10 <sup>10</sup> at/cm <sup>2</sup> | 20.0   | 14.0   | 9.8    | 6.8    | 4.8    | 3.4    |  |  |

| ゲート絶縁膜 膜厚 測定精度   | nm                                  | 0.0076 | 0.0060 | 0.0077 | 0.0210 | 0.0150 | 0.0130 |  |  |

| 容量絶縁膜 膜厚<br>測定精度 | nm                                  | 0.046  | 0.049  | 0.110  | 0.110  | 0.092  | 0.066  |  |  |

| ドーパントプロファイル      | 2D/nm                               | 10     | 7      | 5      | 4      | 3      | 2.0    |  |  |

| 空間分解能            | 3D/nm                               | -      | 15     | 10     | 7      | 5      | 3.5    |  |  |

表1.1 半導体デバイス技術で到達が期待される分析レベル(2)

| 年代    | 技術                                  | 応用                                                               |

|-------|-------------------------------------|------------------------------------------------------------------|

| 1970年 | 超高圧電子顕微鏡                            | 厚い試料の観察                                                          |

| 1980年 | Cold - FEG<br>冷陰極電界放射型電子銃           | コヒーレント電子線による高分解能観察<br>高いエネルギー分解能による高感度分析<br>位相情報の可視化(電子線ホログラフィー) |

| 1985年 | FIBによる試料作製技術<br>Focused Ga ion beam | 不良箇所そのものの断面試料作製<br>試料作製の自動化                                      |

| 1995年 | 電子顕微鏡のデジタル化<br>ネットワーク化              | 観察結果・分析データの電子化                                                   |

| 2000年 | 観察技術の多様化                            | 3次元トモグラフィー・電位コントラストの観察                                           |

| 2005年 | 球面収差補正技術                            | 高分解能観察・不純物原子の可視化                                                 |

表1.2 半導体解析技術のBreak Through

# 不良解析装置(不良位置特定)の解説

| 装置    | 発光解析装置<br>(EMMI)                                                                         | OBIRCH解析装置<br>(OBIRCH)                                                                    | 電子ビームテスタ<br>(EBT)                                                                  | 電子ピーム電流注入解析装置<br>(EBAC)                                                  |

|-------|------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------|--------------------------------------------------------------------------|

| 励起源   | 入力電圧                                                                                     | レーザービーム                                                                                   | 入力信号+電子ビーム                                                                         | 電子ビーム                                                                    |

| 検出器   | 冷却CCD力メラ/MCP                                                                             | 電流アンブ                                                                                     | 2次電子検出器                                                                            | 電流アンプ                                                                    |

| 検出信号  | ホットエレクトロン発光                                                                              | 電流変化                                                                                      | 2次電子量変化                                                                            | 注入電流変化                                                                   |

| 解析状態  | スタンバイ状態<br>(近年、動作状態の観察報告有)                                                               | スタンバイ状態                                                                                   | 動作状態                                                                               | 首 <b>9</b> 6勺状態                                                          |

| 物理現象  | ・ショート/オーブンによる<br>ゲートでの中間電位発生<br>または<br>ゲートからの電流注入<br>→ホットエレクトロン発生<br>→制動輻射<br>/電子・ホール再結合 | <ul><li>加熱による電流経路の<br/>抵抗変化→電流変化</li></ul>                                                | ・配線への印加電位による<br>2次電子放出能変化                                                          | ・高抵抗箇所での電流分流に<br>よる流入電子電流量変化                                             |

| 入手情報  | 発光座標                                                                                     | 配線系路/発熱反応座標                                                                               | LSI内部波形/<br>電位コントラスト像                                                              | 注入電流分流座標                                                                 |

| 検出不良  | ・中間電位配線部<br>(不良箇所と直接対応しない。)<br>・ゲート破壊箇所                                                  | ・ショート箇所<br>・高抵抗箇所(<10E6Ω)<br>・ゲート破壊/異常箇所                                                  | <ul><li>・タイミング不良トランジスタ</li><li>・配線異常箇所</li></ul>                                   | ・オーブン箇所<br>・高抵抗箇所(>10E6Ω)                                                |

| 装置メーカ | 浜松ホトニクス                                                                                  | 浜松ホトニクス                                                                                   | アドバンテスト                                                                            | (中研) +(半) + 装置メーカ                                                        |

| メリット  | ・簡便な操作で発光簡所観察可<br>・フルオートブローバを装備した<br>発光ウェハマッブ解析装置で<br>ウェハ内のAUF解析可                        | ・簡便な操作で反応箇所観察可<br>・低電圧の場合も電流経路が<br>存在すれば反応検出可                                             | ・Tr.の動作タイミングを<br>検出する現存する唯一の手段<br>(裏面レーザ波形観測は<br>装置完成度不足で当面静頓)                     | <ul><li>・オーブン/高抵抗接続<br/>箇所の観察可</li><li>・比較的低抵抗の不良<br/>箇所までの検出可</li></ul> |

| デメリット | ・配線系不良の場合、反応<br>箇所と不良位置との不一致有<br>・低電圧動作のLSIの場合、<br>発光が発生してくくなり、<br>検出困難                  | ・配線系不良の場合、反応<br>箇所と不良位置との不一致有<br>・微少電流を検出するため、<br>静状態への設定が不可欠で<br>ノイズに敏感<br>・発光解析よりも振動に敏感 | ・下層にある信号ラインから<br>波形取得が困難<br>→スケルトン加工併用要<br>・フリップチップの場合、<br>上層に電源ラインを配した<br>場合、解析困難 | ・製品サンブルに対しての解析<br>手法が不透明(今後の課題)<br>・左記と同様、多層化、フリップ<br>チップ化への対応が困難        |

EMMI=EMission MIcroscope

EBT=Electron Beam Tester

EBAC=Electron Beam Absorbed Current

表1.3 主な故障位置特定手法

#### 1. 2 半導体解析技術における電子顕微鏡技術の発展

電子顕微鏡はその登場以来、主としてマテリアル科学と形態観察を中心とする医学・生物学の分野において発展してきた。表1.2に示すように半導体分野に限って見ると、その解析技術における飛躍的な進展は過去20年間に4度あったと考えられる。1回目は冷陰極型の電子銃の開発により干渉性の良い電子線が得られるようになり、現在の高分解能な観察と高感度の元素分析の基礎が築かれた。2回目は1980年代後半から始まったTEM 試料作製用 FIB 装置の普及、3回目は1995年の MicroSoft 社の Windows95®の発表と期を一にした電子顕微鏡のデジタルネットワーク化、4回目は2000年代前半から始まった3次元観察を中心とする観察技術の多様化、そして5回目として期待されているのが球面収差補正技術である。

FIB の導入は TEM 試料の作製技術に根本的な変革をもたらした。従来は平面的な観察 で Si 基板の結晶欠陥を観察するのが主たる用途であった TEM に、場所が特定された 半導体デバイスの不良箇所の断面構造そのものを観察するという画期的な試料作製手 段を提供した。これをきっかけに TEM は不良箇所の「直接観察と分析」という、解析 の主役に躍り出る。さらにマイクロサンプリング技術などの周辺技術の開発により、平 面 TEM で観察した試料から直接断面試料を抽出すると言う「離れ業」までが可能とな り、開発から20年経た現在では数々の自動化機構やウエハサイズの試料ステージ、座 標リンケージ機能などを伴って、「TEM 解析の量産化」すら可能とならしめている。電 子顕微鏡データのデジタル化、ネットワーク化はある意味では必然であった。高性能の CCD カメラは TEM 観察を暗室作業から開放し、ネットワーク化は配信作業を不要と することによって TAT(Tarn Around Time: 解析依頼の開始から解析結果の出力まで の時間)の劇的な改善をもたらした。これによって製品サイクルの短い半導体製品の歩 留まり垂直立ち上げにも寄与出来るようになった。これまで TEM の薄膜試料の内部構 造には3次元的な構造は想定されていなかった。デバイスサイズの縮小とともに100nm の試料膜厚にもデバイスの立体構造が含まれるようになると、この仮定は成り立たなく なり、3次元構造の2次元投影像を解釈する必要が生じる。当初、生物系試料を中心に 一定の成功を収めた 3D トモグラフィー法が材料分野へも進出し 3 次元的に観察する顕 微手段が開発された。

このように電子顕微鏡技術の大きな特徴は高い空間分解能に加えて、非常に広範囲な周辺技術と試料作製技術を伴っている「総合的な評価手段」ということができる。例えば、電子線と材料原子の相互作用による X 線の発生や、エネルギーを失った電子線の分光機能、つまり元素分析技術を併せ持つことによって、形態観察と元素分析を nm 領域で成し遂げられる有力な手段である。加えて、電子線ホログラフィーによる試料内部のポテンシャル評価や、画像処理技術を用いた 3 次元的な観察評価も可能になっている。電子顕微鏡開発当初からの球面収差を補正する装置が実用化されてからは、さらにその観

察限界を拡張しようとしている。半導体デバイス・プロセス技術においても、その特徴は遺憾なく発揮され測長 SEM(Critical Dimension SEM)は半導体デバイス構造のあらゆる寸法測定に不可欠の検査装置となっている。また欠陥検査装置や特性評価装置にも電子顕微鏡の原理を用いたものが数多くある。しかしながら、表1.1で示したように、電子顕微鏡の特徴である nm 領域の観察と分析を最大限活用するのは透過型電子顕微鏡(TEM: Transmission Electron Microscope) を用いた物理的な不良解析技術である。当初はシリコン基板に発生した結晶欠陥の観察が主体であったが、故障箇所特定技術の精度向上と収束イオンビーム加工装置 (FIB: Focused Ion Beam) による故障箇所そのものの加工観察技術の進展により、故障が起こった箇所を他の健全な箇所と比較観察や分析することが可能になり元素の結合状態までも評価可能になった。このため不良原因物質の特定のみならず、原因物質が生成した不良発現までのプロセスを再現し、工程の特定と異常の原因を指摘することでプロセス・デバイスの開発に大きく寄与している(506)。

#### 1.3 半導体解析の基本的操作(ソフト解析~故障位置特定と物理解析)

図1.2に示した半導体製品の不良解析ワークフローにしたがって半導体解析の基本的な操作を説明する。半導体製品の故障が「故障」として認識されるのは市場だけではない。製造工程や信頼性試験、また製造工程における様々な検査工程など製品に至る前の段階で見つかることも多い。一般的な故障解析手順は「故障」をテスター上で再現させるところから始まる。テスター上では故障に関わる数多くのデータが収集されており、これらを用いて論理的に最も故障が疑われる回路ネット(ある回路の単位)を特定する。実際に推定される「故障」を回路上に導入し回路や論理的なシミュレーションによって故障現象の推定も試みられている(の。これを「論理解析」という。もちろん故障から推定されるネットは一通りではない。よって数多くの故障候補からトランジスタや配線のレイアウト上での不良箇所を特定する。この操作に用いられる装置は表1.3に示すように光、熱、電磁波と半導体不良箇所との相互作用を用いた実に多様な方式が実用化されている(の。この操作を「不良箇所検出」という。

次に特定した不良箇所を物理化学的な手段を使ってプロセス・デバイス上で解析するのが物理解析である。この解析には主として電子顕微鏡が用いられる他、AES(Auger Electron Spectroscopy)や SIMS(Secondary Ion Mass Spectroscopy)、XPS(X-ray Photoelectron Spectroscopy)などの分光的解析手段が用いられる。

#### 1.4 本研究の目的と内容

本研究は電子顕微鏡を用いた物理解析的な評価技術をより発展させるために工夫と改良を加えた手法と、その応用例を主題とする。

本論文の第 2 章では本研究で対象とし改良を加えた電子顕微鏡による主な不良解析手法について述べる。主な内容は、分析電子顕微鏡法として、電子線損失エネルギー分光法(EELS:Electron Energy Loss Spectroscopy)を発展させた位置分解型 TEM-EELS法及び分析の目的に特化した FIB による試料作製技術、電子回折法として、収束電子回折(CBED:Convergent Beam Electron Diffraction)による微小領域の応力評価方法及びそのシミュレーションの高速化、3次元電子顕微鏡法(3D-CT TEM: 3D-Computer Tomography TEM)と、それを半導体デバイスに応用する上での試料作製方法などについて述べる。また電子顕微鏡を観察手段としたプロービング法によるデバイス特性評価技術についても言及する。

第3章から第6章は第2章で検討した解析技術を実際の半導体デバイスに適用した事例を紹介し、電子顕微鏡が半導体デバイス・プロセス開発に果たす役割について考察する。第3章は主としてシリコン基板、第4章はトランジスタに関わる内容を扱い、デバイス・プロセス技術上では Front End Process といわれる部分である。また第5章は主として配線層とコンタクト、および配線材料に関わる内容を扱い、Back End Process と呼ばれる。また第6章はシリコン半導体以外の材料や新規な方式のメモリに適用した応用例を報告する。いずれの技術も半導体デバイスの初期不良から信頼性不良まで幅広い分野に適用されている。第7章で本論文のまとめを述べる。

## 参考文献

- (1)(社)電子情報技術産業協会:ナノ構造観測分析技術調査研究報告書 I,(2001)

- (2) (社)電子情報技術産業協会:ナノ構造観測分析技術調査研究報告書Ⅱ,(2002)

- (3) (社)電子情報技術産業協会: 半導体技術ロードマップ専門委員会(STRJ) 2006 年度 ワークショップ(第8回)

- (4) 半導体産業研究所 故障解析技術検討 WG: LSI 故障解析技術開発強化の提言(2003)

- (5) 電子顕微鏡研究開発·利用推進檢討会:電子顕微鏡研究開発·利用推進檢討会報告書(2006)

- (6) (社)電子情報技術産業協会: 半導体技術ロードマップ委員会(STRJ) 2006 年度ワークショップ講演資料集

- (7) 中前:ソフトウエアによる故障診断技術、第63回日本顕微鏡学会学術講演会予稿集、 p157

- (8) K. Nikawa et. al, . International Reliability Physics Symposium. IEEE, (1996) 346. Dallas, Texas, USA

# 第2章 本研究で対象とし改良を加えた主な不良解析技術の概要

## 2.1 TEM-EELS の概要と位置分解型 TEM-EELS の開発

## 2.1.1 化学結合状態評価の必要性

デバイス・プロセスの開発や量産においては微細化や新材料、新プロセスの採用により解決 困難な不良が数多く発生している。また、開発、量産立上げ後も、各種の検査をくぐりぬけ、顧 客先で不良が発現するケースも増加している。これら不良の原因を突き止め、根本的に解決 し、信頼性の高いプロセスを構築することが強く求められている。

半導体デバイスの不良解析では FIB による試料作製技術の普及以来、TEM (Transmission Electron Microscope) が主な解析手段として使われ、その微細構造の観察結果を元に不良の解析や対策がなされてきた。しかし、プロセス・デバイスの複雑化により構造の観察だけでは多様化し複雑化する不良を克服できない状況となっている。不良の克服にはその直接原因、すなわち、プロセス想定外の反応生成物が何であるかを明らかにし、その発生メカニズムを解明し、確実な対策を施さなければならない。そのためには、例えば『高抵抗を示す特定のコンタクト底の数原子層』といった不良部そのものについて、どのような反応が起きたのか化学結合状態を含めた解析を行なう必要がある。

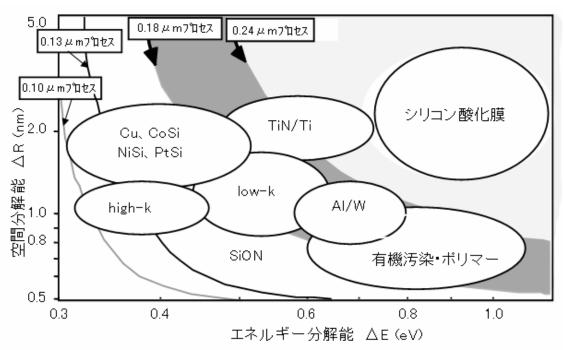

このような極微小部の化学結合状態解析が可能なのは唯一、TEM-EELS 法(TEM with Electron Energy Loss Spectroscopy)  $^{(1)(2)(3)}$ である。TEM-EELS の化学結合状態解析の性能は「空間分解能(nm)」と「エネルギー分解能(eV)」によって決まるが、これらはお互いにトレードオフの関係にある(図 2.1.1)。本節では 100nm 以下のデバイス開発で必要となる不良解析技術として 300kV 位置分解型 TEM-EELS の開発について述べる。

図2.1.1 化学結合状態解析の性能とニーズ

| アプローチ               | 具体的手段                    | 問題点                       |

|---------------------|--------------------------|---------------------------|

| (1)測定系全体のエネルギー分解能向上 | 新電子源開発<br>(エネルキー拡がり低減)   | 材料基礎研究<br>(ex超伝導材料)       |

|                     | エネルキ゛ーフィルタ<br>エネルギー分解能向上 | 透過率低下                     |

| (2)EELSスペクトルのS/N向上  | エネルキデーフィルタ<br>透過率向上      | 新原理フィルタリング<br>(exサイクロトロン) |

|                     | 長時間積算                    | 高精度<br>試料位置ドリフトサル御        |

表2.1.1 TEM-EELS化学結合識別能向上の方策

## 2.1.2 TEM-EELS 高性能化の方法

リフレッシュ不良、高抵抗不良をはじめ、各種の不良は、界面や側壁での局所的な異常が原因となることが多く、不良解析における分析領域は数原子層程度に絞る必要がある。微細化はさらに進むことがロードマップ上からも明らかであり、低電力デバイスではデバイス特性が界面等の境界領域の状態に敏感に影響するため、今後は1から2原子層の分析領域を実現していかなければならない。さらに、今後のデバイス開発ではCu配線、low-k材料、high-k材料などの新材料・新プロセスの開発が重要な課題となっている。これらの開発では未知の化学反応や多元素が関与した化学反応とその反応生成物質を制御していく必要があり、化学結合状態の解析はますます重要度を増し、さらに高いエネルギー分解能が要求される。

これらの傾向から、TEM-EELS に求められる性能は「空間分解能(nm)」「エネルギー分解能 (eV)」ともに厳しくなることが容易に予想される。ただし、TEM-EELS は TEM がベースの評価法 であるため、本質的に空間分解能は TEM と同等である。そのため、性能向上は「エネルギー分解能をいかに向上させるか」に集約される。エネルギー分解能は狭義には入射電子線のエネルギー広がりと分光系のエネルギー分解能で決まるが、ここではこのようなハードウエアで決る最高性能としてのエネルギー分解能ではなく、実効的に得られる EELS スペクトルのエネルギー軸の精度(=信頼性)と広義に定義する。

エネルギー分解能を向上させるために、まず、**表2.1.1**に上げる2つのアプローチについて 考察した。

- (1)測定系(入射電子線と分光系)のエネルギー分解能向上

- (2) スペクトルの S/N 向上

- (1)では図示したように近接した2つのピークが分離して認識できるようになり、スペクトル解析で重要な各々のピーク位置と強度を決定することができる。(2)の場合には S/N の改善によりスペクトル形状が明確になり、ピーク分離を行なうことで個々のピーク位置や強度を明らかにすることが可能となる。これらを実現する具体的手段として、

- (1)については

- (a)新電子源開発によるエネルギー拡がり低減

- (b)エネルギーフィルタのエネルギー分解能向上

が挙げられる。(a)の電子源については、数多くの研究がなされており、TEM搭載の電界放射型電子銃のエネルギー幅約 0.4eV に対して 0.2eV の線源も開発されたが、TEL-EELS 用電子源としては輝度が足りず現実的でない<sup>(4)</sup>。 (b)に関してはスリットを狭めることでエネルギー分解能を向上できるが、同時に信号量が減り、スペクトルの S/N が著しく低下するため、やはり本開発に用いることはできない。

- 一方、(2)についての実現手段としては

- (c)エネルギーフィルタの透過率向上

#### (d)データの長時間積算

が挙げられる。(c)についてはエネルギー分解能を維持して透過率を向上させるためには新しいフィルタリングの原理から基礎検討する必要があり、ここ数世代のデバイス評価に適用するのは不可能である。(d)についてはデータを長時間積算することは可能であるが、この時に生じる試料ドリフトにより実効的な分析領域が拡大してしまう、という問題が生じる。

このように何れのアプローチをとっても困難な問題が生じるが、この中で現実的に解決できる 見込みがあるのは(d)であると判断した。ただし、空間分解能がニーズを満たすためには長時 間測定時の試料位置ドリフトを1から2原子分に抑える、という難しい課題をクリアする必要があ る。

以下、長時間のデータ積算により EELS スペクトルの S/N を改善し、EELS 性能を向上させることを目標に、目標仕様(データ積算時間、許容ドリフト量)について検討した内容を述べる。また、これを実現させる試料位置ドリフト制御技術については次項で述べる。

#### 2.1.3 長時間積算方式における目標仕様

S/N を改善させるためにはデータをより長い時間積算することが望ましいが、観察時間や試料 ダメージの観点からは最低限に抑えたい。この項では実際の不良解析の場で TEM-EELS の エネルギー分解能向上のためにどの程度の積算が必要か、また、可能かを検討し、目標仕様を決定する。まず、S/N 改善によりエネルギー分解能がどのように向上するか、その関係を定量的に関連付けるための検討を行なった。

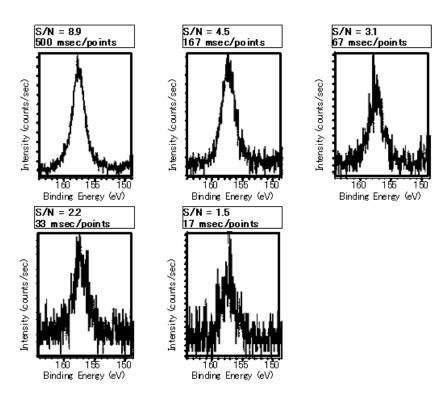

図2. 1. 2は光電子分光装置(XPS)を用いてMg-K  $\alpha$ 線により励起した Si2s 軌道からの光電子を半球型エネルギー分析器で分析したスペクトルである。ピークの半値幅やスペクトル測定時のエネルギー間隔は EELS 測定とほぼ同じ条件であるが、スペクトルの積算時間を 0.05eV当たり 0.017 秒から 0.5 秒と変えて、S/N=1.5 から 9.3 に変化させた。同一ピークであるにもかかわらず、S/N 比によってピーク位置、半値幅が異なって見えるが、この傾向をまとめたものが図2. 1. 3である。各 S/N 比の条件下で同一ピークを数回から 10 数回測定し、各スペクトルのピーク位置と半値幅を求め、それらの S/N 比依存性をプロットしたものである。図2. 1. 3(1)はピーク位置の S/N 依存性、図2. 1. 3(2)はピーク半値幅の S/N 依存性である。どちらの場合もS/N 比が増えるにしたがって、値が真値に収束する傾向が明らかである。これらの結果より、EELS において十分に信頼性のあるスペクトル解析を行なう為には、すなわち、化学結合状態を判断するコアロスエッジエネルギー位置やコアロススペクトル形状の測定精度が±0.1eV 以下となるためには、S/N 比が少なくとも8程度は必要であると考えた。

一方、通常の EELS スペクトルは 20 秒測定で S/N 比は4から7程度である。今回の性能改善においては、現在評価実績のある Si や Ti に比べて一桁感度の低い元素についても S/N 比8 を確保したいため積算時間目標は S/N 比で20倍向上と設定した。スペクトル積算時間は現状20秒であるため、その20<sup>2</sup>倍、約10<sup>4</sup>秒を目標仕様とする。

図2. 1. 2 S/N比が異なるSi<sub>2S</sub>スペクトルの例 XPS測定の結果

図2.1.3(1)ピーク位置のS/N依存性 図2.1.3(2)ピーク半値幅のS/N依存性

10

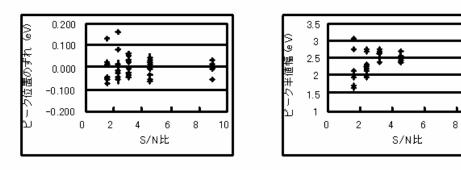

図2.1.4 長時間データ積算の効果

200KV TEM-EELSでSrのコアロススペクトルを評価した例 Srはセラミックス材料として広い面積の試料を得られ、かつEELS感度が低い。 位置補正なしのデータ積算効果を検証する材料として適している。 積算時間 10<sup>4</sup> 秒の効果は**図2. 1. 4**で確認することができる。**図2. 1. 4**は 200kV TEM-EELS で強誘電体 BST 中のストロンチウム(Sr)を測定したスペクトルである。現装置では長時間のデータ積算は不可能であるため、均質な試料を用意し、大面積を測定することで試料ドリフトの影響を無視した長時間積算と同様の効果を得た。Sr は EELS での感度が低く、通常の条件 (積算 20 秒)でピークは認識されない。100~1000 秒相当でようやくピークの存在が確認でき、2000 秒相当でピークが2つ存在することが確認できる。目標の 10<sup>4</sup> 秒では2つのピークの位置、形状が明確になると予想される。これらの結果より、10<sup>4</sup> 秒の積算は実際の不良解析の場で解析程度を高めるために有効であると判断した。

#### 2.1.4 長時間測定時の試料位置ドリフト量

次に、この10<sup>4</sup>秒の積算で最大の問題となるビーム・試料相対位置ドリフトが実際にどの程度になるかを調べた。相対位置ドリフトには電子銃の安定性、レンズ系高電圧の安定性、真空度、高真空化のための液体窒素トラップへの液体窒素補給等が影響するが、いくつかの予備検討の結果、液体窒素トラップへの液体窒素補給にともなう試料位置ドリフトが実測定に最も影響を与えることが判明した。そこで、液体窒素補給後、試料位置がどのようにドリフトしていくか、200kV TEM-EELS を用いて精密な測定を行なった結果、以下の結果を得た<sup>(5)</sup>。

液体窒素補給直後のドリフト量 0.5nm/sec

補給2時間後以降のドリフト量 0.015nm/sec 以下

この結果から、最もドリフトの少ない条件でも 0.02nm/sec 程度の試料位置ドリフトは避けられないことがわかる。この条件で 10<sup>4</sup> 秒測定を継続すると最終的に 200nm のドリフトを生じるため半導体デバイスの特定箇所といったピンポイント的な分析は不可能であり、ドリフト補正の必要性が再確認された。ドリフト補正を行い、高分解能長時間測定(10<sup>4</sup> 秒)を実現させるための方策を次の項で述べる。

#### 2.1.5 長時間測定を可能にするシステム構築

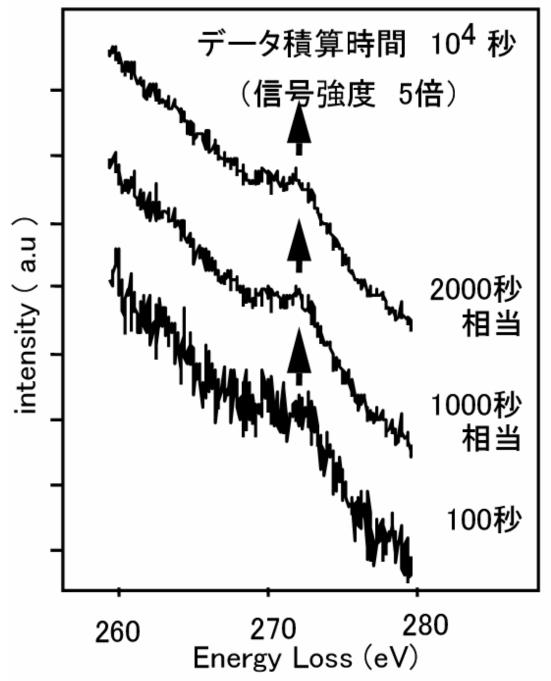

試料位置ドリフトを補正するために、以下の測定方式を採用した<sup>©</sup>。

- [1]測定はドリフト量が十分に小さくなるような短時間測定に分割する。

- [2] 長時間測定の間に注目している領域が測定視野から外れないよう、ピエゾ素子による高精度試料微動ホルダーを作製し、測定視野を保つ(ハードウエアによる粗補正)。

- [3] 長時間測定実現のため、[1]の結果をドリフト補正しながら積算する(ソフトウエアによる詳細補正)。

[4]長時間測定時には、電子線照射により試料温度が上昇して試料がダメージを受けることが予想されるため、電子線シャッターによる電子線断続照射を実施し、電子線照射による昇温

#### を抑える。

[5]上記[1]~[4]を自動測定で実施できる制御システムを構築する。

この方法により、ドリフトが測定結果に与える影響は[1]の一回の測定内で生じるドリフト量と [3]のソフトウエアによるドリフト補正の誤差を重畳したものとなる。 具体的には 1 測定を 20 秒 (ドリフトは 0.02nm/秒 x20 秒=0.4 nm)、位置合わせ精度を 0.4nm 以下と目標を定めるとドリフト による分解能の低下は 0.8nm 以下となる。また、測定視野を確保するためにピエゾ素子による 粗補正の精度は 2nm 以下とする。これらによる自動測定を最.大 $10^4$ 秒(約 3 時間)実施することで、原子番号 56 (Ba) 以下の位置分解スペクトルをS/N=8以上で取得し、空間分解能 0.8nm でのエネルギー分解能 0.4eV 以下を実現することを目標とした。

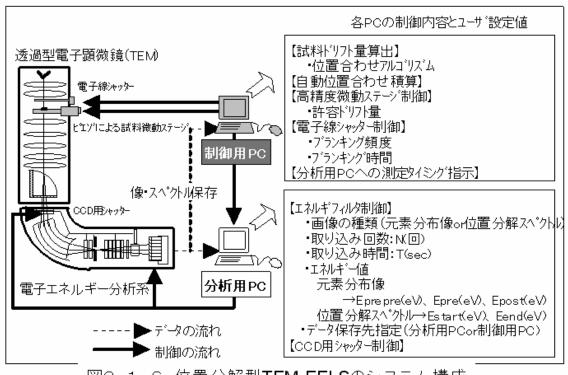

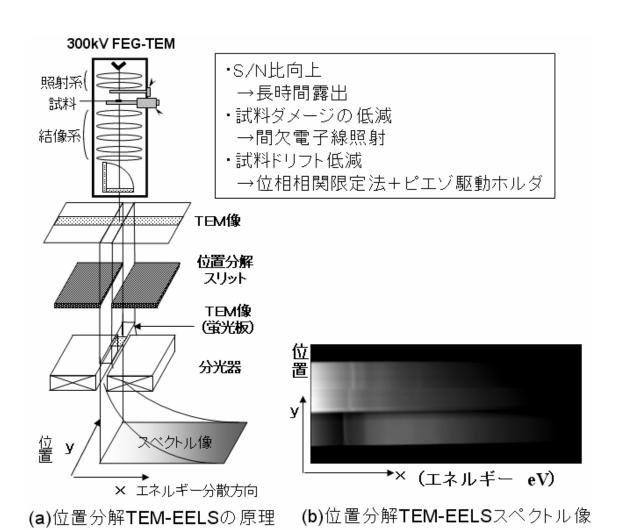

表2. 1. 2に開発の内容と目標をまとめ、図2. 1. 5に装置構成図を示す。これらを用いた長時間測定は TEM-EELS 測定の制御を行なっているGatan社製のソフトウエア「デジタルマイクログラフ」を部分的に外部から制御することで、全て自動で行なえるようにする。詳細な EELS 測定条件は「デジタルマイクログラフ」搭載の分析用 PC を用いて入力し、測定結果におけるドリフト量の算出や位置合せ積算、ピエゾホルダーの制御、電子線シャッターの制御は制御用 PC が行う。システム構成図を図2. 1. 6に示した。

| 開発項目                 | 技術課題                            | 技術的ポイント                         | 目標                 |                               |

|----------------------|---------------------------------|---------------------------------|--------------------|-------------------------------|

| 100nm<br>領域の<br>化学結合 | ハードウエアによ<br>る<br>分析位置補正         | ビエゾを用いた<br>高精度試料微動ホ<br>ルダ       | 位置精度<br>2nm以下      | 空間分解能<br>0.8nmの場合<br>•S/N=8以上 |

| 評価技術                 | ソフトウエアによる<br>分析位置補正             | 正規化相関法を用<br>いた<br>自動位置合わせ積<br>算 | 合わせ精度<br>0.4nm以下   | •エネルギー分<br>解能<br>0.4eV以下      |

|                      | 長時間データ積算<br>時の<br>試料損傷・変質防<br>止 | シャッターによる<br>電子線の間欠照射            | 最大データ積<br>算<br>3時間 |                               |

表2.1.2 開発の目標と内容

図2.1.5 位置分解型**TEM-EELS**の構成図

図2.1.6 位置分解型**TEM-EELS**のシステム構成

## 2.1.6 高精度試料微動ホルダーによるドリフト補正システム

高精度試料微動ホルダーは長時間測定時に機械的、電気的ドリフトにより分析している領域が視野から逃げてしまうことを防ぐために用いる。長時間測定中には随時試料ドリフト量をチェックし、その値が一定値を越えた場合にこの高精度試料微動ホルダーを用いて試料を元の位置に戻す。その値は測定領域の大きさによって異なるため、各測定時に設定するが、最低5 nm を想定した。そのため、制御精度は 2nm 以下が必要であり、ピエゾ素子を用いて駆動する。

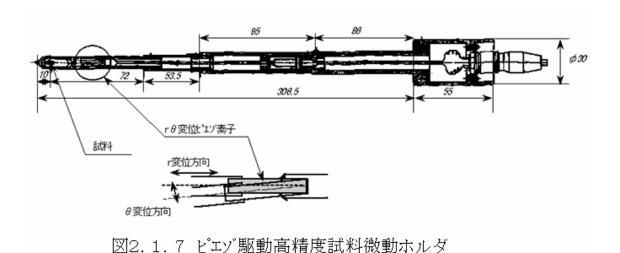

ホルダーの概略図を図2. 1. 7に示す。ピエゾ素子は試料保持部とホルダーの軸との間を繋いでおり、1つのピエゾ素子がr方向の変位、2つのピエゾ素子が  $\theta$  方向の変位を与える。ただし、操作性のため、測定側からはxとyの 2 軸で変位量の設定を行い、これをrと  $\theta$  変位に変換して制御する。ピエゾの素子特性には個体差があるため、実際の印加電圧と変位量の関係を実験的に求め、これより設定値(x,y)に対する $(r,\theta)$ ピエゾへの印加電圧 $(V_r,V_\theta)$ を決定し、試料の高精度移動を行う。

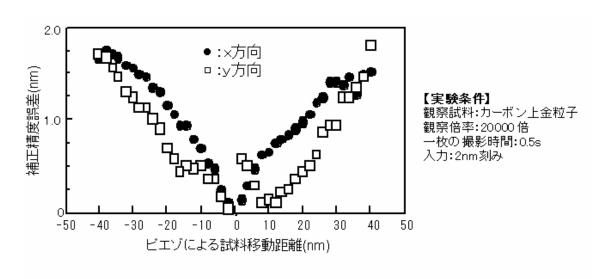

実際に作製した高精度試料微動ホルダーの評価結果を図2. 1. 8に示す。この実験では独立に与えた入力 $(x_0,0)(0,y_0)$ に対して、実際に動いた(x,y)を TEM 像より求めた。 $(x_0,0)$ 又は $(0,y_0)$ と(x,y)の差がこの高精度試料微動ホルダーの制御精度であると定義すると、本ホルダーの制御精度は目標 2nm に対し、移動距離 40nm 以下では 1.8nm 以下、移動距離 10nm 以下では 0.7nm 以下、と、目標値をクリアし、試料の高精度移動が行えることを確認した。

図2.1.8 ピエゾ駆動高精度試料微動ホルダの制御精度評価結果 (制御精度は(入力変位値-実際の変位量)で定義した)

- 23 -

#### 2.1.7 画像位置合せ積算によるドリフト補正システム

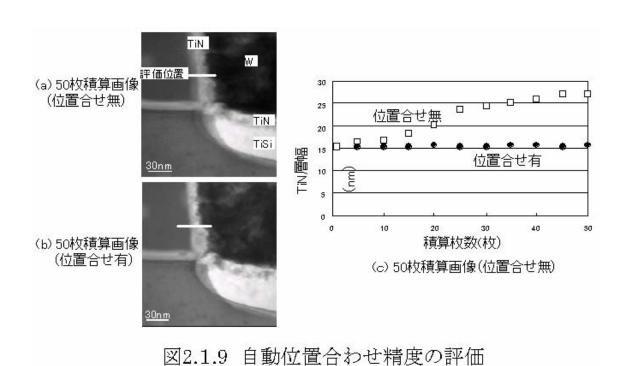

2. 1. 6で述べた高精度試料微動ホルダーにより TEM-EELS 長時間測定時に機械的、電気的ドリフトが生じても分析領域を視野内に保つことが可能となったが、多数の短時間(数~数10 秒)測定画像データ間にはドリフトによる数 nm 程度の位置ずれが残っている。これを正規化相関法 7) を用いた画像同士の比較により補正して積算する。自動位置合せ積算システムの精度を評価した結果を図2. 1. 9に示す。(a)(b)はコンタクト底の断面 TEM 画像を 50 枚積算したもので、(a)は位置合せ無、(b)は位置合せ有の場合である。(a)の場合、TEM 像中の TiN 層はドリフトによりぼけて見えるのに対し、(b)では明瞭に観察される。このぼけを定量的に評価したのが(c)のグラフである。位置合せ無しでの積算の場合、評価位置における TiN 層幅は積算枚数とともに増加するが、位置合せ有りでの場合約 15nm とほぼ一定の値を示す。1枚のTEM 像における TiN 層幅と複数枚積算を行った像における TiN 層幅の差は積算枚数によらず、1 ピクセル(=0.38nm)以下となった。

これらの結果より、短時間(数~数10秒)測定画像データを複数枚、位置ずれを補正して 積算することが可能となり、像の空間分解能を劣化させることなく長時間測定が行えることが確 認できた。長時間測定により元素像や位置分解スペクトルの高 S/N 化が実現し、微小部の詳 細な元素分布評価や化学結合状態評価が可能となる。

#### 2.1.8 電子線シャッターによる測定試料の電子線損傷低減

長時間測定時には電子線照射による試料の変質・損傷が予想される。この変質・損傷は電子のドーズそのものによるものと、電子線照射による試料の昇温によるものが考えられるが、後者の場合、電子線の間欠照射によりある程度緩和することができる。本検討ではシャッターによる電子線間欠照射機構を設け、さらに、測定毎に電子線のOn/Offのタイミングを調整できるようにすることで、試料や EELS の測定条件によってシャッター使用のタイミングを最適化して使えるようにした。

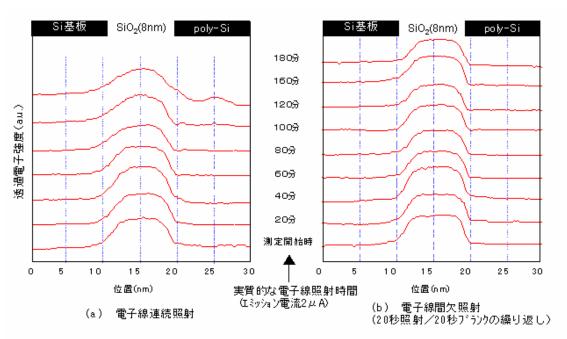

シャッター使用による電子線間欠照射の効果の一例を図2.1.10にまとめた。これは poly-Si/SiO<sub>2</sub>(8nm) /Si 基板の断面試料をTEM観察した結果からコントラストのみをグラフに したものである。SiO<sub>2</sub>層ではSi層に比べて平均質量数が小さいため透過電子強度が強まり、T EM像では明るく見える。電子線を連続照射した(a)の場合には約80分で SiO<sub>2</sub>とSiの境界が 不明瞭になり始め、電子線照射により試料が変質していることがわかる。一方、(b)の電子線間 欠照射の場合180分の電子線照射後も SiO<sub>2</sub>とSiの境界ははっきりしており、電子線による損傷は(a)の場合よりも抑えられていることがわかる。この結果より電子線シャッターによる間欠照射が試料損傷の抑制に一定の効果があることが確認された。この効果は照射条件、試料の材

質、加工厚さ等に依存する(図2.1.10は20秒照射/20秒非照射の繰り返し観察、試料構造は poly-Si/SiO<sub>2</sub>(8nm)/Si 基板、試料厚さ 70nm の場合)が、各条件を最適化することで、電子線照射時に試料が昇温しても非照射時に放熱することができ、実質的な測定時間は延長されるものの、従来不可能であった試料でも長時間測定できる可能性がある。

ただし、電子線間欠照射は試料温度の上昇を緩和させる効果があるのみで、電子のドーズで引き起こされる損傷には効果がない。わずかな化学結合状態の違いを評価する場合には慎重な検討が必要である。

図2.1.10 電子線シャッタによる試料損傷低減効果

## 2.1.9 TEM-EELS の性能評価

# (1)元素分布、位置分解スペクトル測定結果

この開発により電子線エネルギー損失分光法による評価性能が向上したことを確認するため に、従来法と本法による測定結果の比較を行った。

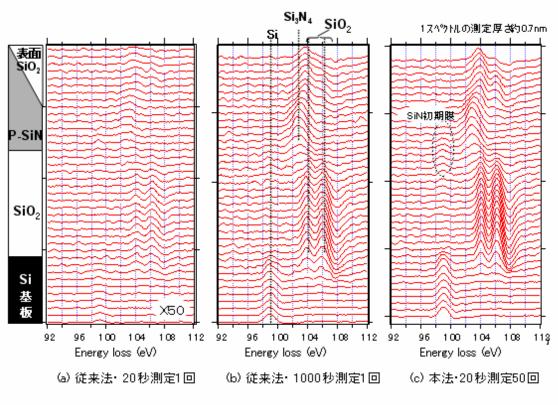

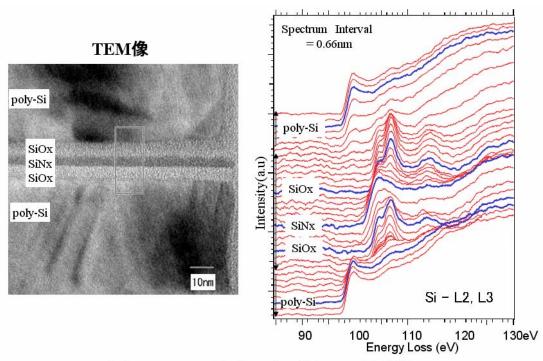

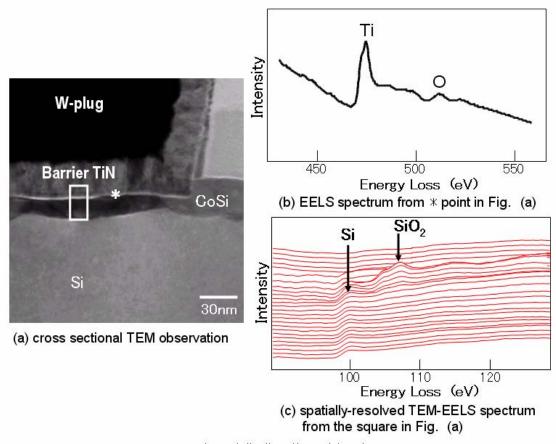

図2. 1. 11は位置分解スペクトル測定の結果である。試料はプラズマ SiN/SiO₂/Si 基板である (表面は酸化)。スペクトルは 0.7nm 毎に測定したもので、コアロスエッジの変化を明瞭にする ため微分形で示した。(a)は従来法で 20 秒測定の結果、(b) も従来法で 1000 秒連続測定の 結果、(c) は本法によるもので 20 秒測定を 50 回実施し、ドリフト補正後積算したものである。 Si コアロススペクトルは純 Si(Si 基板)では約 99eV に、SiO₂では 104 と 106eV 付近に、SiN で は約 103eV にピークを持つ。従来法(a)(b)では、Si 基板と SiO₂、SiN の存在は確認できるが、表面の SiO₂は不明瞭である。本法による結果では表面の SiO₂ 起因の2つのピークが明瞭に認識される他、SiN 初期膜(SiN/SiO₂ 界面付近)では窒化していない Si が存在していることが確認される。この絶縁膜中(SiN/SiO₂)ではリークが認められたが、これはプラズマ SiN 初期に形成された Si によるものと判明した。この評価事例では 0.7nm 毎に光電子分光(XPS)並みの化学結合状態を示すスペクトルが示され、元素分布評価、位置分解スペクトル測定ともに本法では高 S/N な元素像、スペクトルが得られ、元素の分布や化学結合状態評価時の空間分解能が向上していることを確認した。

図2.1.11 位置分解スペクトル測定結果

## (2)エネルギー分解能評価結果

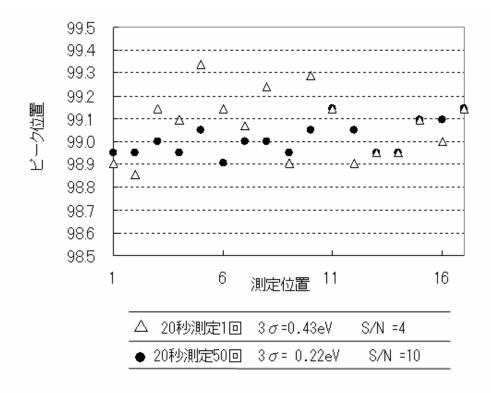

エネルギー分解能 ( $\Delta$ E)の向上については Si 基板の EELS スペクトルを測定し、微分スペクトルにおけるピーク位置のばらつき ( $3\sigma$ ) により評価した。結果を**図2. 1. 12**に示す。 $\Delta$ は従来 法で 20 秒測定を行ない 0.7nm 毎に17点測定した結果である。本来真値で直線に並ぶべきものであるが、スペクトルの S/N は 4 で 0.43eV にわたってばらつきがある。  $\blacksquare$  は 20 秒 50 回測定の結果で、S/N は10、ばらつきは 0.22eV に減少している。これらの S/N やピーク位置のばらつきは元素種とその濃度によって異なるが、これらの結果は本法により EELS スペクトルにおけるコアロスエッジ位置や形状の評価精度が向上したことを示している。感度や濃度により信号量が1桁~1. 5桁程度低い場合にも積算時間を最大  $10^4$  秒 (約 3 時間)まで延ばすことで、同様の評価精度が達成できる見通しであり、当初の目標(空間分解能 0.8nm 以下で S/N=8 以上、エネルギー分解能 0.4eV 以下)を達成した。

なお、本検討結果とは別に Zero loss ピークの形状を基にしたデコンボリューションによってエネルギー分解能を向上する取り組みも成されている<sup>(7)</sup>。 Zero loss は TEM の電子光学系の歪やノイズを反映しており、デコンボリューションによってソフト的にエネルギー分解能を向上させることが出来る。

図2.1.12 位置分解スペクトルにおけるエネルギー分解能の比較

#### (3) 位置分解型スリットによる評価

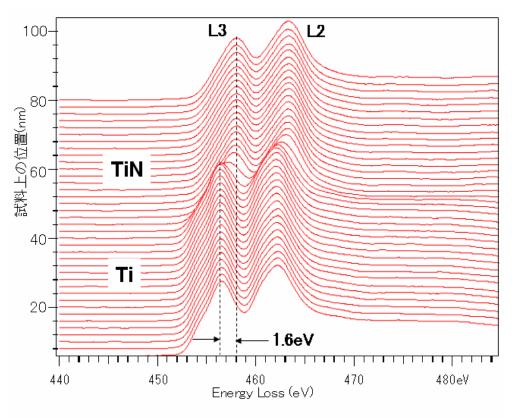

位置分解型 TEM-EELS の概要を図2. 1. 13に示す。この方式は像面(蛍光板)上に置かれた 位置分解スリットが特徴である。このスリットにより制限された電子顕微鏡像が分光器に導かれると、制限された TEM 像の EELS スペクトルが同時に取得される。ここで重要なことはスリットの 長手方向、即ち試料の Y 方向とスペクトルの Y 軸方向が一致していることである。図2. 1. 14 に Ti と TiN の積層膜を位置分解 TEM-EELS で取得した例を示す。TiN 層の EELS スペクトルは Ti 層の EELS スペクトルと同時に取得される。したがって、例え上記のような EELS スペクトルの再現性に問題があっても、測定したい物質のスペクトル(ここでは TiN)と、基準となる純物質(ここでは Ti)のスペクトルと同時に取り込んでいることになり、常に安定したスペクトルの比較が可能になる。図2. 1. 15には位置分解型 TEM-EELS 装置の外観写真を示す。

図2. 1. 13 位置分解型TEM-EELSのしくみ

図2. 1. 14 位置分解TEM-EELSのスペクトル例 (TiとTINの積層膜)

図2. 1. 15 位置分解型TEM-EELS装置の外観

#### 2. 1. 10 まとめ

以上の開発によって得られた結果をまとめると次のようになる。

100nm プロセスノードの開発および量産では、ナノレベル、サブナノレベルの構造および元素 分布・結合状態を制御する必要がある。これを可能とする元素分布・化学結合状態解析ツー ルとして高性能な位置分解型 TEM-EELS を開発した。

- (1) 元素分布、スペクトルの高 S/N 化のため、位置分解型EELSによる元素分布・二次元スペクトル等の画像データを時分割で取り込み積算する機構を開発した。

- (2) 上記の機構に電子顕微鏡の機械的・電気的ドリフトを補正し、サブナノレベルの空間分解能を保持させる機能を付加した。

- (3) 高 S/N 化、ドリフト補正の結果、TEM-EELSの空間分解能、エネルギー分解能の向上を達成した。一例として、

- 空間分解能 0.7nm での Si コアロススペクトル(Si 基板中)のエネルギー分解能 0.22eV (1000 秒測定)を実現した(従来 0.43eV(20 秒測定))。

- (4)(3) の空間分解能、エネルギー分解能は元素種や測定試料厚さに依存するが、感度や濃度により信号量が一桁程度低い場合にも積算時間を最大 10<sup>4</sup>秒(約 3 時間)まで延ばすことで、同様の性能が達成できる見込みを得た。

#### 2. 2 3次元観察電子顕微鏡法(3D CT-TEM)

#### 2.2.1 半導体デバイスの3次元観察における意義

半導体デバイスは最近のシステム LSI に代表されるように多機能・高集積化が進み、配線層の多 層化とトランジスタの微細化によってその性能を実現している。その解析には超高圧電子顕微鏡 (Ultra High Voltage Electron Microscope :UHVEM)が必要な数 μ m³の空間的に広がった配線や Via の構造、欠陥の分布を把握しなければならない。その一方では、透過型電子顕微鏡 (Transmission Electron Microscope: TEM)の薄膜試料(100~150nm 厚)内にコンタクトホールや MOS トランジスタと言ったデバイスの構成要素が全て含まれるまでになっている。 従来は 2 次元平 面で近似して差し支えなかった TEM 試料が、デバイスの3次元構造の2次元平面投影として観察 されることになり、否応なしに「2次元観察像の3次元的な解釈」を強いられている。このように半導 体デバイス分野における 3 次元観察の動機と目的は異なる観察技術と手段を要求している。これ に対して配線構造のような厚い試料でも観察できる UHVEM やトランジスタの微細構造を観察でき る 300kV クラスの 3 次元観察機能を備えた電子顕微鏡にも 3 次元的観察機能の開発が進んでお り®、FIB やマイクロサンプリング法を始めとする試料作製技術の進展、さらには電子顕微鏡内で試 料を360°回転して全方位から観察ができる試料ホルダーの開発など、幅広い周辺技術の発展に 負うところが大きい<sup>(9)</sup>。また近年のパソコン性能の向上や画像処理技術の進展がこれを後押しして いる(10)。本報告では、半導体分野における構造解析や不良解析における可能性を、配線構造とト ランジスタの 3 次元 TEM 観察評価例を元に考察する。

#### 2.2.2 デバイス試料観察の概要

3 次元再構成画像処理に関しては数多くの報告がなされている<sup>(11)-(16)</sup>が、半導体デバイスの観察を 念頭に置くと下記のようになる。

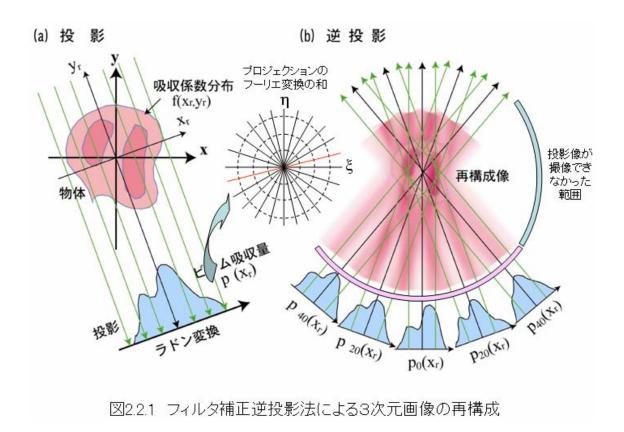

図 2.2.1 にフィルタ補正逆投影法による 3 次元画像の再構成方法を示す。一般的な 3 次元 TEM 像の再構成は「透過波の強度の減少が電子線の入射方向への投影試料密度に比例する」ことを 前提としている。この条件下で、試料に電子線をある角度で入射させた試料内部の密度分布をラドン変換によりビーム吸収量に変換する。これを  $\xi$  と $\eta$  で表わされるフーリエ空間に投影する。この 作業を繰り返し、各角度からプロジェクションしたもののフーリエ変換の和を得る。得られたフーリエ変換の和を逆変換することによって、再構成像を得ることができる。これは医療機器として知られる X 線 CT(Computer Tomography)の手法と同じである。3 次元 TEM 観察が CT-TEM 法と呼ばれる のもこれに由来している。

次に画像の位置合わせの問題について議論する。試料を 60° ~180° 回転させて多数枚の TEM 写真を撮影する間に、試料位置のずれが起こりそのまま再構成してもぼやけた 3 次元像となってしまう。

これは次のようなパラメータが考えられている。

- ・ X,Y 方向のずれ (回転軸と試料中心のズレ)

- ・ 角度のずれ (観察箇所が回転軸に対して歳差運動する場合)

- ・ ローテーション (試料軸と電子線軸の傾きによる)

- ・ 試料の伸び縮み (電子線ダメージによる試料の収縮)

- 倍率誤差 (電子顕微鏡の安定性)

- ・ 試料ドリフト (試料台の機械的誤差、チャージアップなど)

これらの画像の合わせずれを防止するため、生物試料の場合は特徴的な構造を目標にできるが、 半導体デバイスの場合、試料位置合わせの目標に適した構造がない。よって金(Au)のコロイド粒子を試料表面に付着させ、それを目標に画像の位置を合わせる。目標の個数は多いほど正確に位置合わせ出来るが、概ねパラメータの個数以上(8~10ヶ)が良いとされている。また Au コロイド粒子にもいくつかの直径のものがあり、UHVEMなどの加速電圧の高い電子顕微鏡では20~40nm かを用い、300kV 以下の TEM では 10~20nm かが適当とされている。

#### 2.2.3 デバイス観察の問題点と対策

この手法を半導体デバイスの 3 次元観察に適用する上で予想される問題点を列挙すると次のようになる<sup>(17)</sup>。

- ① 全方位の透過像が撮影できない場合の情報欠落領域

- ② 結晶材料からの Bragg 反射の処理

- ③ 試料厚さによる動力学的回折効果

- ④ 画像再構成時の偽像の問題

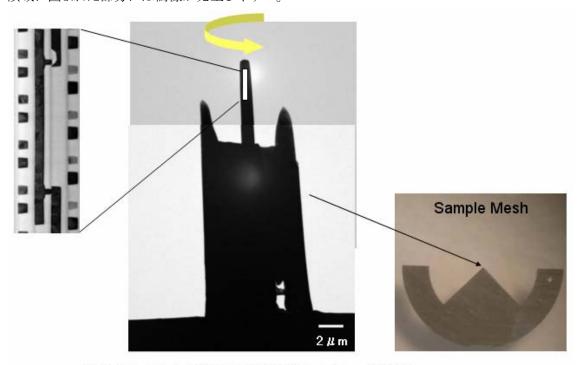

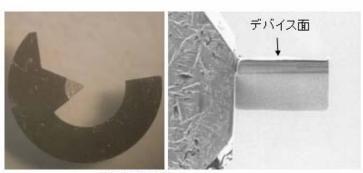

このうち①は、図 2.2.2 に示すように、柱状に加工した試料を TEM 内で 180 度回転させて観察する ことにより解消できる。FIB 加工によって試料をピラー状に作製し V 型メッシュの頂上部分に固定する。またメッシュ自体も試料の観察位置にかかる部分を切除することによって、完全な全方位からの 観察が可能になる。この試料は超高圧電子顕微鏡を用いた 3 次元観察に適用した。

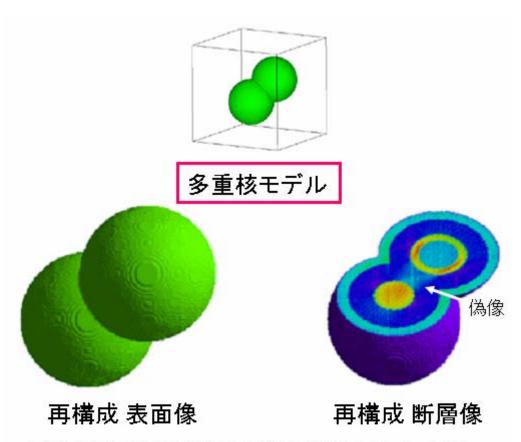

また②と③は多数の観察像を再構成する中で平均化され、実用的な半導体の不良解析では、大きな問題とならないことが確認できた<sup>(18)</sup>。④は暗視野 STEM 法を用いる方法もあるが、解析用途によっては再構成像の注意深い解釈を必要とする。図 2.2.3 に偽像の例を示す。これは2つのコアをもった球体を組み合わせた形状をしたものを仮定し、これを3次元再構成したときの結果を示す。コアとコアの間に存在しないコントラストが再生されている。このように比較的電子線透過能の低い領域に囲まれた部分には偽像が発生しやすい。

図2.2.2 3次元観察試料と試料メッシュの形状

図2.2.3 偽像の例(中心核を持った球の再構成シミュレーション像)

#### 2. 3 電子回折による応力評価

## 2. 3. 1 電子回折による結晶中の応力評価方法

結晶に加わっている応力を評価する方法には、ラマン散乱を用いる方法が知られている。しかしレーザー光によるプローブ径が 500nm 程度あり、半導体デバイス中の応力評価には決定的に分解能が不足している。そこで電子顕微鏡を用いた応力評価が候補として考えられるが、基本的には電子回折によって格子常数を求める手法に他ならない(19)-(24)。ここでは主に CBED(Convergent Beam Electron Diffraction)について、基本的な手法とシミュレーション速度の向上についての工夫を述べる。

## (1) nano-diffraction 法

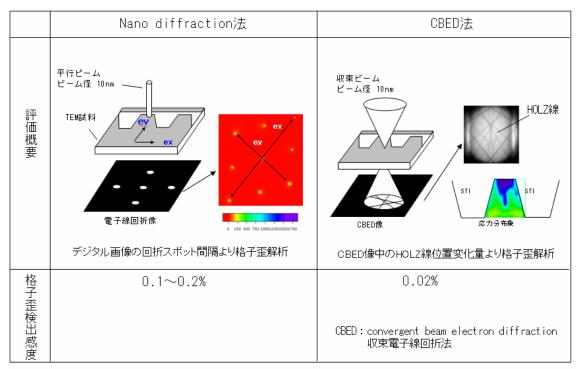

図2.3.1に電子回折による応力評価方法について示す。

一つは Nano-diffraction 法であり、もう一つは CBED 法である。Nano-diffraction 法は電界放射型電子銃(FEG: Field Emission Gun)から出るコヒーレントな電子線を、電子レンズによって  $5\sim10$ nm  $\phi$  程度の平行ビーム(nano beam)とし、微細領域の電子回折図形を得るものである。制限視野電子回折と違って、絞りの直径に依存せず非常に細い平行ビームが作れるので、材料科学分野では微小析出物などの結晶構造を評価する用途に用いられてきた。応力評価の原理は、応力による結晶格子の伸び縮みを電子回折図形に現れた回折斑点の間の距離を測って求め、格子面間隔の変位として読み取るものである。電子回折図形に現れる逆格子点と原点(000)との距離は、実空間における面間隔に相当するため、特定の面間隔に対応する逆格子点までの距離を測って、格子常数を求め格子の伸び縮みを評価する事ができる。近年の画像処理技術の進歩により回折スポットをデジタル的に処理して回折斑点間距離を正確に再現性良く求める事ができる。この手法は電子回折図形をとるだけの単純な方法であるが面間隔を直接評価するために格子歪の検出感度、つまり応力の感度が低いと言う欠点がある。格子歪量としては 0.1%程度の歪量が検出限界とされている。

逆に高応力下における CBED 法では HOLZ 線がスプリット(1 本の HOLZ 線が 2 本に分かれる)する現象が現れ、通常のフィッティング計算では格子定数を求めることが出来ない。スプリットした HOLZ 線から格子の「曲がり」を評価する試みも成されている $^{(25)}$ が、このような場合は nano-diffraction 法を用いて応力評価できる場合もある。

図2.3.1 半導体デバイス中における応力評価方法

- 36 -

#### (2) CBED 法

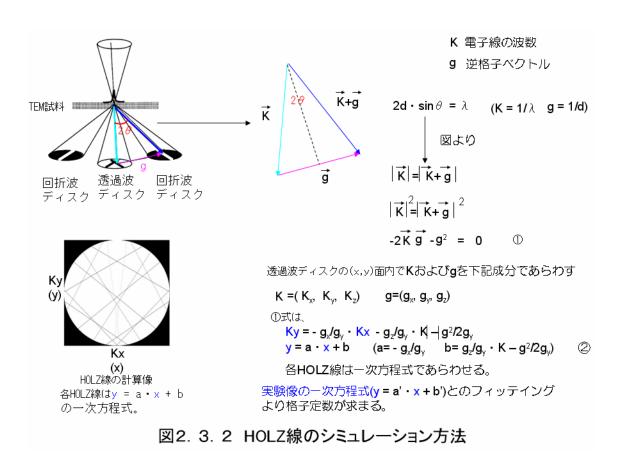

CBED 法は電子線を高角度(数 mrad)の照射角で試料に入射させたときに現れる透過波ディスク中の HOLZ(High order Laue Zone)線が、結晶の格子常数に敏感である事を利用している。収束させた 電子線を試料に入射させると、透過波ディスクと回折波ディスクが現れる。透過波ディスクと回折波ディスクの HOLZ線には Bragg の式より図2.3.2 の①式に示す関係があり、透過波ディスクの(x,y)面内で k(電子線の波数ベクトル)と g(逆格子ベクトル)を、それぞれ x,y,z の成分であらわすと②式が得られる。これより透過波ディスクの HOLZ線は 1 次方程式で表されることになり、実験像の HOLZ線の 1 次方程式と格子定数(a,b,c,)と格子角度 $(\alpha)$ から計算される計算像とのフィッティングによって格子常数を求める事が出来る(26)。

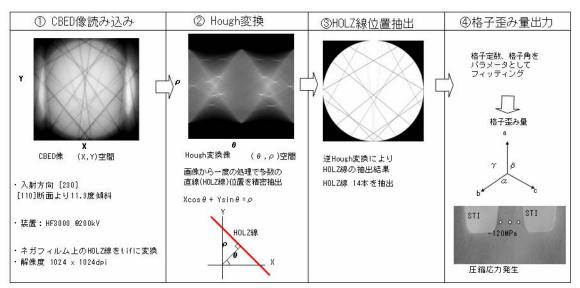

図2. 3. 3に CBED 法による実際の応力評価方法の手順を示す。透過波ディスクの HOLZ 線を読み込み、1 次方程式に変換する。この際、Hough 変換と言う一種の画像 処理を用いて HOLZ 線を抽出するが、HOLZ 線のコントラストによってはソフトによる自動抽出に誤差が生じる場合がある。Hough 空間内では HOLZ 線はコントラストの 最大値として求まり、図の例では 14 本の HOLZ 線が抽出されている。抽出した HOLZ 線の 1 次式をシミュレーション値とフィッティング計算することによって、格子定数を 求め格子歪が得られる(27)(28)(29)。

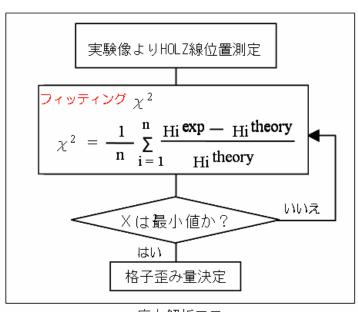

図2.3.4にフィッティング計算の精度評価について示す。実験像から得られた HOLZ 線の 1 次方程式と理論的にシミュレーションした HOLZ 線の 1 次方程式のフィッティングパラメータを  $\chi^2$  として図のように定義する。この  $\chi^2$  が最小になるようにフィッティング計算を繰り返すが、通常 4 0 回程度の繰り返し回数を必要とし計算時間が長くなる原因となっている。

ステップ1 CBED像よりHOLZ線位置を抽出。(一次方程式に変換)

ステップ2 HOLZ線をシミュレーションし実験像の一次方程式とのフィッティングより格子歪が求まる。

図2.3.3 CBEDによる応力評価方法

応力解析フロー

図2. 3. 4 CBEDによる応力評価方法 (シミュレーション)

## 2. 3. 2 パラメータ設計手法による CBED 計算手法の改良

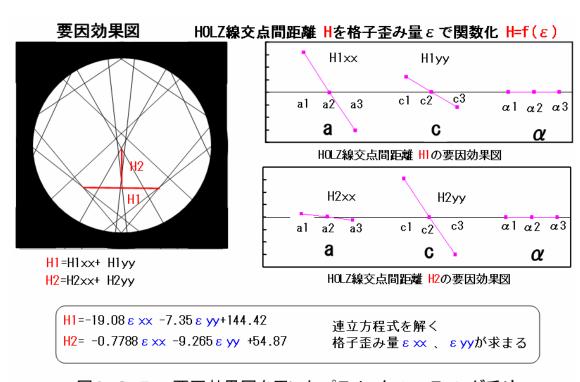

実際の CBED のフィッティング計算では、Hough 変換によって抽出された HOLZ 線 の交点座標を用いて交点間距離をフィッティングしている。図2.3.3の例では14 本の HOLZ 線が抽出され、100 点以上の交点が求められている。従来はこれらすべて の交点間距離をフィッティング計算していたため、計算時間が長くなっていた。この欠 点をパラメータ設計手法を用いて解決する方法を示す。パラメータ設計手法とは実験計 画法や品質管理で使われる多変量解析の一種で、多くの実験条件の中から最も結果に大 きく影響を及ぼしているパラメータを見つけ出す手法で、そのツールとして直交表や要 因効果図が用いられる。図2.3.5に要因効果図を用いてパラメータフィッテングす る方法を示す。この手法ではまず交点間距離 H を格子歪 ε で関数化する。すべての交 点間距離は  $H_n = \epsilon_{xx} + \epsilon_{yy} + a$  として表される。格子歪  $\epsilon$  はこれらの連立方程式を解くこ とによって求められる。図2.3.5に示す要因効果図の例では交点間距離 H1 は a 軸 の格子常数には敏感であるが、c軸への寄与は小さい。また $\alpha$ には殆ど関与していない 事がわかる。また H2 の交点間距離は c 軸にのみ寄与し、a 軸にも  $\alpha$  にも殆ど関与して いない。よって関与の度合いの大きい交点間距離のみを用いてフィッティングすること によって計算回数を大幅に減らす事が出来る。基本的に格子定数の a と c、格子角の α の3つを未知数として求めるのであれば、方程式も3つあれば良い。

図2. 3. 5 要因効果図を用いたパラメータフィッティング手法

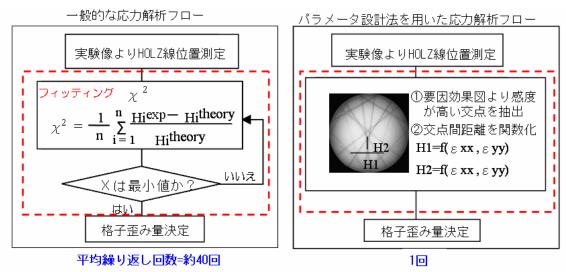

図2.3.6にパラメータ設計手法を用いたシミュレーション方法と一般的なシミュレーション方法の比較を示す。要因効果図を用いて格子歪に感度の高い交点間距離を抽出し、その交点間距離と歪を関数化する事によって大幅に計算時間を短縮(約 1/80 と推定)できた。また両方の方法でも同じ歪測定精度が得られる事が確認されている。

図2.3.6 パラメータ設計手法によるCBEDシミュレーションの改良効果

### 2. 3. 3 応力評価と試料膜厚の関係

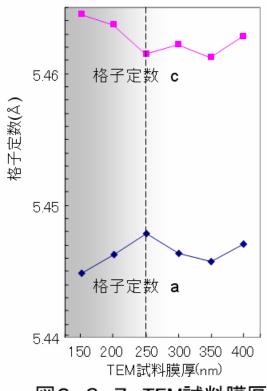

CBED 法で応力を評価する場合は、試料を電子線が透過できる程度の薄膜に加工しなければならない。試料膜厚が薄くなるに従い、応力分布がバルク中と異なり薄膜化するに連れて応力が開放され正確な評価が出来なくなってくると考えられる。実効的にデバイス中の応力評価が可能な膜厚を調べた例を図2.3.7に示す。これは Si 基板をいくつかの膜厚に薄膜加工し CBED 法で格子定数を求めたものである。試料膜厚が250nm 以下になると a 軸の格子定数は大きくなり、c 軸は小さくなる。これは試料表面からの応力の開放によって Si の結晶格子がバルク中とは異なった形に変化している事を示している。したがって、Si 基板中の応力を CBED 法で評価するには 250nm 以上の膜厚が必要と推定できる。

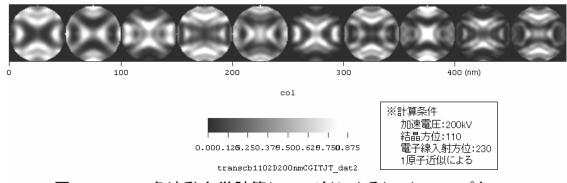

なお、この評価に用いた試料膜厚は CBED のパターン形状を比較する事によって求めた。FIB による試料加工中の観察結果からおおよその膜厚を知る事が出来るが、評価点の膜厚を正確に評価するには CBED パターンを評価するのが良い。CBED パターンの形状は試料膜厚の変化に敏感なため、試料膜厚によって変化する CBED パターンをあらかじめ多波動力学シミュレーション(30)によって求めておき、これと実際の試料を観察して得られた CBED パターンとを比較する事によって求める事が出来る。図2.3.8に多波動力学計算(Bethe 法)によって得られた(110)面の CBED パターンを示す。

図2. 3. 7 TEM試料膜厚と 格子定数の推移

試料膜厚が250nm以上あると 格子常数の変化は少ない

図2. 3. 8 多波動力学計算(Bethe法)による(110)CBEDパターン CBED評価前にパターンを取得しBethe法のシミュレーション結果と見比べて膜厚を推定する

#### 2.4 集束イオンビーム(FIB)装置による試料作製技術

#### 2.4.1 はじめに

半導体デバイス・プロセスの高集積化限界が論じられて久しいが、半導体製品はまだ当分の間はシリコンを主たる材料として微細化を続けていくものと思われる(31)。最小加工寸法が100nm以下のデバイスが出現するに及んでトランジスタや配線の微細構造観察は、SEMからTEMへと移行しつつある。但し全ての解析がTEMに置き換わることは無く、今後もSEMによる解析数はTEMを上回ると予想される。しかしながらHigh-K, Low-K膜に代表されるように新材料や新プロセス技術が導入されることがSiデバイスの延命条件を握っていることも事実である。新材料、新プロセスの導入は半導体製品の信頼度の裏づけとなる寿命予測方法に根本的な見直しを迫るものであり、例えば長年半導体製品の配線材料として使われてきたAI配線とコンタクトホールにおける許容電流と信頼度の関係は、配線材料がCuに置き換わることによって変更が迫られている(32)。Cu配線独自の信頼度メカニズムを確立するには数多くの解析事例と信頼度データを積み上げる必要があり、新材料・新プロセス導入による解析技術の役割は重要である。

また高集積化と共に半導体製品の高機能化も進展している。System on Chip(SOC)と呼ばれる高機能チップはこのような先端デバイス・プロセスのプラットフォーム上に成り立っている。SOCの多くはBuilt in Self Test(BIST)と呼ばれるチップテスト技術を実装しているため、チップ外部からのアクセスにより故障箇所の同定が困難になっている。このためメモリ部分をテストするFail bit Map(FBM)以外の方法による故障箇所同定技術が求められており、様々な内部波形のトレース技術や発光解析技術が用いられている(33)(34)。

以上のように Si 半導体は、微細化、新材料、高機能化をキーワードにして、今後とも進化し続けると予想されるが、その基礎を担う解析は TEM を主体とした技術が重要になっている。 TEM 技術は材料内部の構造が観察できるだけでなく、nm 単位の分析機能により半導体デバイスの故障メカニズムを明らかにできる。 最近では分析機能を強化し短時間で微細領域の観察と分析が出来る STEM 装置も開発されており、半導体デバイス・プロセスの開発における分析電子顕微鏡の役割は非常に重要になっている。

しかしながら、解析目的に見合った試料作製技術が伴わなければ、いかに高性能な電子顕微鏡といえども満足な解析結果を出すことは出来ない。半導体不良解析のための TEM 試料作製には現在では FIB が一般的に用いられるようになっている。これは従来の研磨・イオンミリングによる薄膜化技術と比較して短時間で精密加工できることに加え、ビット単位で不良箇所の摘出が可能であり、これまでに進展してきた故障箇所同定技術との相性に優れているためである。さらにマイクロサンプリング( $\mu$  サンプリング)技術により平面 TEM から断面 TEM 試料を抽出したり、広範囲な特定配線層を平面試料としたりできる(35)。最近ではマイクロピラー( $\mu$ ピラー)作製技術により特定箇所の3次元立体観察試料の作製も可能になる(36)(37)など、FIB 技術は従来の試料作製技術では想像も付かない解析試料の作製を可能にしている(38)(39)。

本節では、主として FIB を用いた試料作製技術のうち、高性能な分析電子顕微鏡を十分に活用するための試料作製方法や半導体デバイスの故障箇所同定技術から物理解析へと導く試料作製技術の検討結果を報告する。

## 2.4.2 FIB による平面→断面試料作製技術

電流のリーク不良を解析するために平面 TEM 観察により多数の結晶欠陥が観察された場合、どの欠陥が致命であったかを判別するためには同一欠陥の断面情報が必要となる。従来の研磨・イオンミリング方法では既に薄膜化された TEM 試料からの再加工は事実上不可能であった(40)

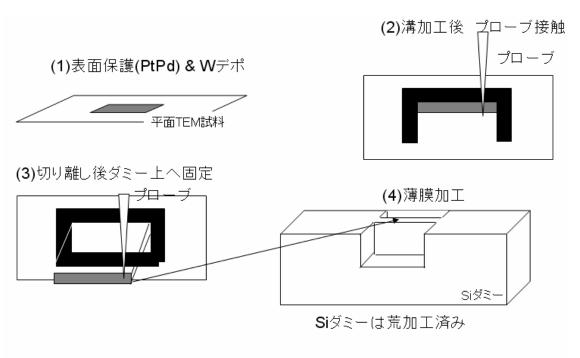

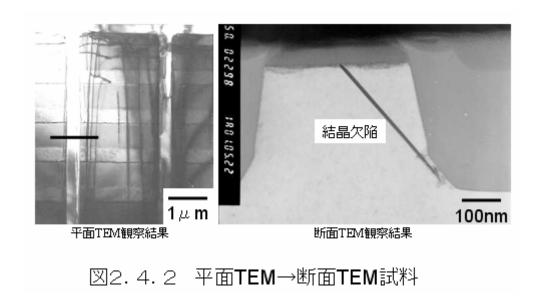

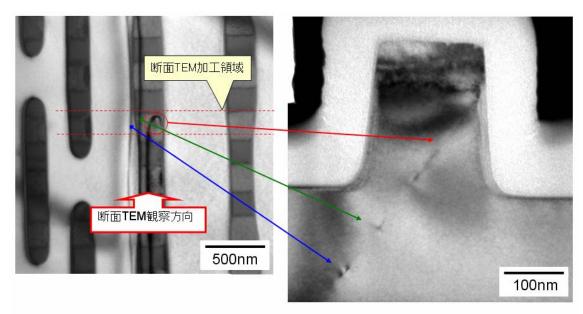

$\mu$  サンプリングによる平面→断面 TEM 試料の作製は、一般的な  $\mu$  サンプリング法とほぼ同じである。但し、既に 100nm 程度に薄膜化された試料を FIB の SIM 像で観察すると、FIB の Ga イオンダメージで結晶情報が失われてしまう。このため、結晶欠陥のような材料の内部情報を取り出すためには、欠陥の方向、深さ、発生点と終端点を TEM 写真を参照しながら決定しなければならない。図2. 4. 1に平面 TEM 試料から断面 TEM 試料を作製する手順を示す。平面 TEM 観察結果からおおよその場所を決めた試料表面に Ar スパッタにより薄い金属保護膜(PtPd)やプラズマ重合カーボン膜などをデポし、その上に FIB 中で W 保護膜をデポする。次に断面観察したいところの周囲をイオンビームで切り取る。切り取った薄片を事前に加工しておいた Si ダミー上に固定する。図2. 4. 2に平面 TEM 観察結果と FIB で作製した同じ個所の断面 TEM 観察結果を示す。結晶欠陥の発生点、深さなどが理解でき不良解析に役立たせることが出来る。

図2.4.1 平面TEM試料から断面TEM試料の作製

- 44 -

## 2.4.3 μピラー試料の作製と観察例

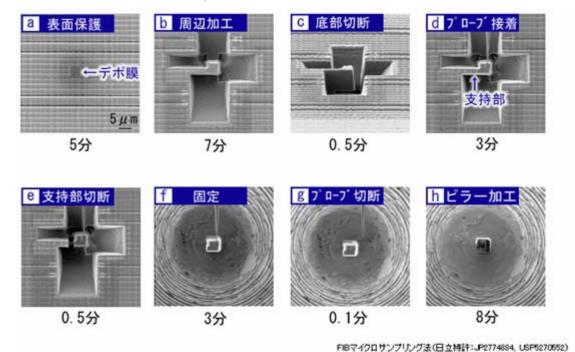

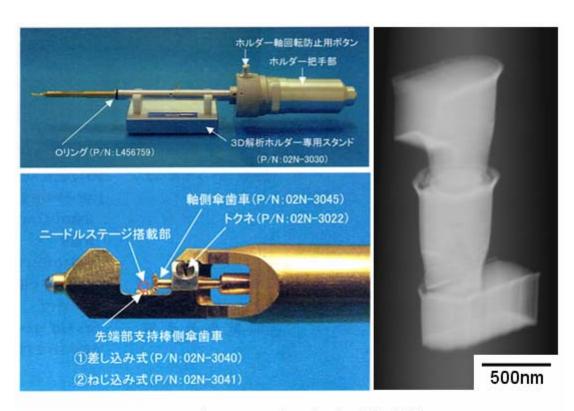

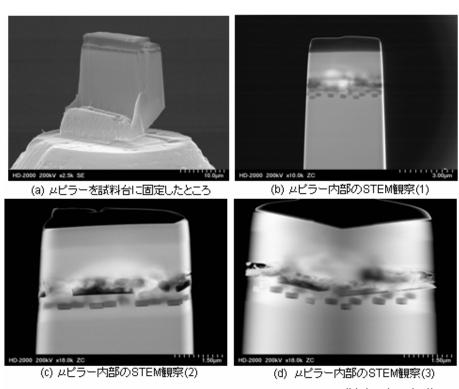

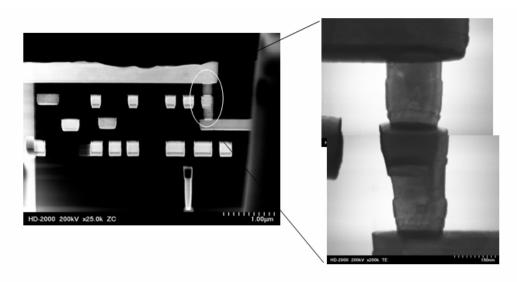

иピラーはSTEM内で回転する特殊な試料ホルダーを用いた3次元TEM(STEM)観察手法で ある(36)。試料台は2ヶの傘歯歯車を用い回転可能な試料ホルダーに柱状のサンプルを固定し、 360°全方向から観察する<sup>(37)</sup>。μピラー試料の作製方法を**図2. 4. 3(1)**に示す。

Viaホールの3次元観察試料作製 図2. 4. 3(1) (マイクロサンブリングによるビラー試料作成:日立ハイテク資料より)

- ① 観察箇所に W 保護膜を形成し、FIB による平面試料作製方法のように観察したい領域を 含むブロックをピックアップする。

- ② ブロックの周囲をFIBで電子線が透過する程度まで細く加工する。但しSTEMは色収差や 回折コントラストが少ないため、1~2 um の試料厚さでも観察対象の形状程度は確認する ことが出来る。

- ③ 図2.4.3(2)に示すように回転ホルダーの先端にWデポ機能によって試料を固定する。 この観察で重要なことは材料内部の微細構造よりも、不良箇所の大まかなイメージが立体的に 把握できることである。特に配線のマイグレーション、パッシベーションや層間膜にできた CVD プロセスの巣、ショート断線個所の全体像を理解するために有効である。また配線やキャパシ タ、コンタクトなどのデバイス構造物の影になって平面的、断面的には把握できないような不良 の発見に役立つことも期待できる。

図2. 4. 3(2) Viaホールの3次元観察試料作製 (マイクロサンプリングによるビラー試料作成:日立ハイテク資料より)

図2. 4. 4 マイクロ(μ)ピラー**STEM**試料と観察像

図2. 4. 4に $\mu$ ピラーの例と STEM 観察結果の一部を示す。試料は Cu 配線のマイグレーションにより隣接配線とショートした箇所の破壊状況を観察したものである。ショートにより配線間に流れた大電流が発生させた高温による物理的な破壊が配線の他、周囲の SiO<sub>2</sub> 膜等デバイス構造全体に及んでいることが分かる。

### 2. 4. 4 FIB による平面 TEM 試料作製手法

FIB による試料作製は一般的に断面 TEM 試料を前提にしている。それは不良位置の特定は主としてレイアウト上からの平面情報によってもたらされる事が多く、また半導体の多層構造的な特質から、断面情報が重要という事情がある。本章以降でも主として断面 TEM 観察や断面からの分析評価が主体となる。しかしながら、断面観察に踏み切るには不良位置の同定がデバイス要素のレベルまで確定している必要がある。これが成し得なかった場合には、考えられる不良候補箇所の全てを含む膜厚を同時に観察する超高圧電子顕微鏡法によって 3 次元観察などの手法が必要となる。また場合によっては不良箇所の特定が、ある配線の層までしか特定されない場合も出てくる。この場合は一定の範囲の配線層を広範囲に見る必要が生じる。但し、通常の研磨→ミリングによる試料作製技術では、シリコン基板以外で特定の配線層に限定した平面 TEM 試料作製は非常に困難で、ここでも FIB の微細加工技術に頼ることになる。従来の試料作製技術では平面 TEM 試料の多くは Si 基板の観察であって、特定の配線層のみを平面 TEM 観察する試料は非常に作製困難で歩留まりも悪いとされていた。しかし FIB の μ サンプリング機能を用いると上記のような試料作製も可能である。

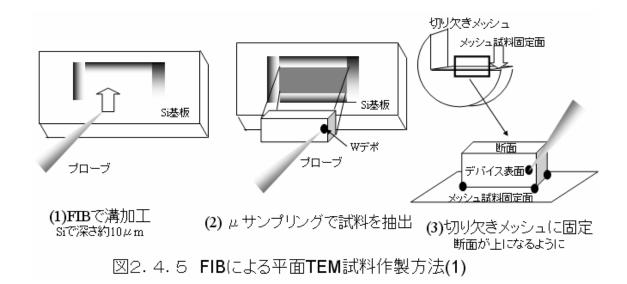

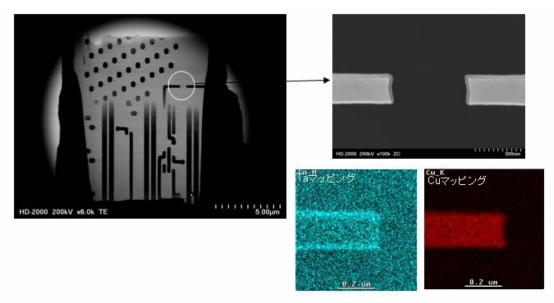

図2. 4. 5に FIB による平面 TEM 試料作製手法を示す。①まず  $\mu$  サンプリング法により所望の 平面を含む領域全体をブロックとしてサンプリングする。②③次にこのブロックを切り欠きメッシュ上に横倒し(実際はメッシュを 90°回転させる)にして W デポで固定する。④メッシュを直立させるとデバイスの断面が SIM 像により観察できるので、平面 TEM 試料として抜き出したい層が 残るように、所定の膜厚(150nm 程度)まで FIB で加工する。

注意すべき点は、②の工程でメッシュに対してブロックを完全に正立させるのが困難であるため、③で抜き出したい層が薄膜中に平行に残るように加工しなければならない点である。特に長い配線の全体や特定箇所を確実に試料とするためには、STEM 観察と FIB 加工を往復することによって位置決めを正確にする必要がある。図2. 4. 5(5)に完成した平面 TEM 試料の全体像を示す。

#D-2000 200kV x2 0k SE #D-2000 200kV x2 0k

2.4.5 試料ダメージの除去方法

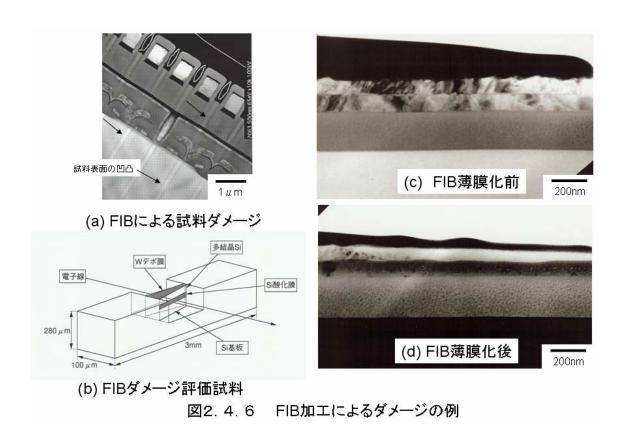

FIB による試料加工が Ga イオンのスパッタリングを利用している以上、イオン衝撃による試料表面へのダメージは避けられない<sup>(41)(42)(43)</sup>。このダメージは試料表面のアモルファス層、Ga による試料汚染が主であり、いずれも高分解能観察や分析、特に界面の評価には深刻な影響を及ぼす。本項では FIB による試料ダメージの評価とデバイス解析への影響、およびダメージ除去の方法について述べる。

## (1) FIB 加工にともなう試料ダメージ

図2. 4. 6(a)に一般的な FIB 加工にともなう半導体デバイスのダメージの例を示す。半導体デバイスの構造にはシリコン系や金属材料などスパッタリングレートの異なる材料が多く使われている。よって試料上面から FIB で薄膜加工するとスパッタリングレートの違いによって、シリコン基板に矢印で示すような凹凸が発生する。さらにデバイス表面のパッシベーション膜の凹凸や配線間を埋めている酸化膜の空洞(巣)なども加工速度に違いを生じさせ、凹凸が生じるの原因となる(44)。一方、試料表面全体を覆うダメージ層は一定の厚みを持っている。試料厚さが薄い場合は Ga イオンダメージによるアモルファス層が試料厚さの大部分を占めるようになり、結晶材料であっても回折コントラストが消失する。図2. 4. 6(b)に示すように膜厚が連続して変化するクサビ形の多結晶シリコンの試料を作製し、FIB で薄膜化した。その結果、膜厚の薄い側(紙面右側)から回折コントラストが消失している。これは材料の結晶部分が無くなったためと考えられる。

半導体デバイスの信頼性を左右する要素として、今後は薄膜界面における結合状態評価が重要になると考えられる。薄膜界面における元素の結合状態は、コンタクトホールの接触面での電気抵抗のみならず、ゲート絶縁膜界面における界面準位の増大がトランジスタの性能や信頼性低下に直接結びつくため、nm 以下の空間分解能での化学結合状態

評価が求められる。また MOS のゲート酸化膜と PolySi 電極の界面などでは高い分解能の格子像観察を必要とする。近年のシステム LSI(SOC)ではゲート酸化膜厚が 1.5~2nm 程度になっており、ゲート酸化膜厚の正確な測定には格子像の面間隔を基準に取る必要がある。試料表面に Ga イオンミリングによるアモルファス層からの電子の散乱により、格子像コントラストが低下する。よって明瞭な格子像観察のためには表面ダメージの少ない試料作製技術が必要である。

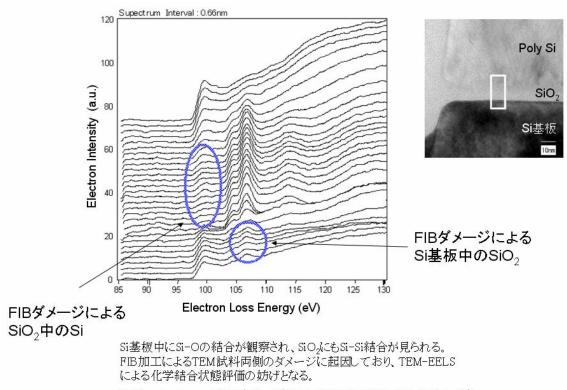

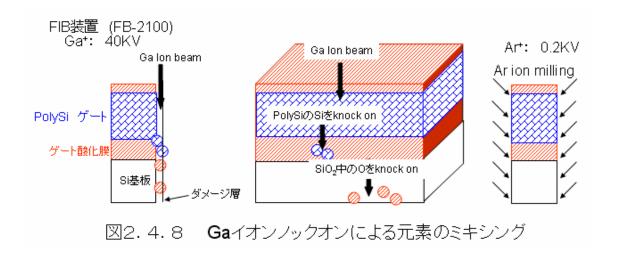

## (2)界面評価に必要な試料作製技術

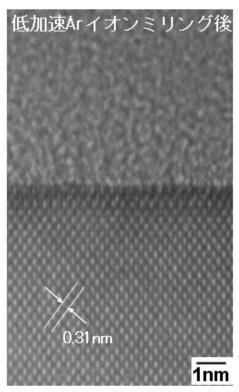

半導体デバイスの解析試料は特定箇所を観察分析する必要性から、また多種類の材料が 積層された構造であることから、電解研磨やウエットエッチングによる手法は採用でき ない。従って FIB による試料作製は必須であるが、その加工原理はガリウム(Ga)イオ ンを数十 keV に加速した物理的衝撃である以上、スパッタリングによる試料ダメージ は免れない $^{(41)}$ 。低加速 $^{(4)}$ と $^{(41)}$ の $^{(41)}$ ないのののののののである。 の縮小など FIB 装置にもダメージを減らす改良が加えられているが、Ga 汚染やダメー ジを伴わない加工が期待される GPFIB(Gas Phase Ion Source FIB)の実現は、観察用 途にはいくつかの試みが報告されているが、直近では難しいとされている。そこで FIB 加工にともなう一定のダメージは許容しつつ、TEM 観察や分析の前処理として極低加 速(100-200V)のイオンミリングを用いたダメージ除去技術が取り入れられている<sup>(42)(43)</sup>。 **図2.4.7**は MOS トランジスタの PolySi ゲート電極/SiO<sub>2</sub> ゲート絶縁膜/Si 基板の 部分を FIB で TEM 試料作製し、位置分解 TEM-EELS を用いて Si のコアロススペク トルを取得したものである。この図からはゲート酸化膜中に Si-Si の結合スペクトルが 見られ、逆に Si 基板中には Si-O 結合の EELS スペクトルが観察される。これは明ら かにデバイス構造と矛盾している。薄膜界面を FIB で TEM 試料に加工した直後は、 Ga イオンのスパッタリングによって界面付近はミキシングやノックオン原子を含むダ メージ層が形成されている。この現象を図示すると図2.4.8にようになる。断面加 工時に Ga イオンによって試料上層部の原子が材料界面を越えて、下層部に押し出され る(ノックオン)ことによって生ずると考えられる。

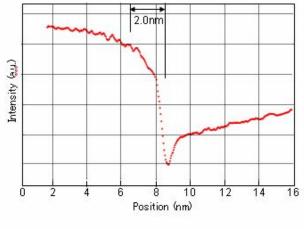

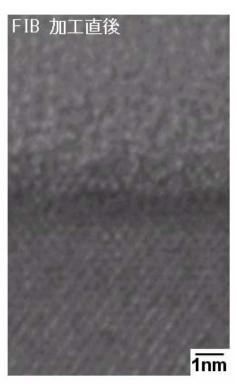

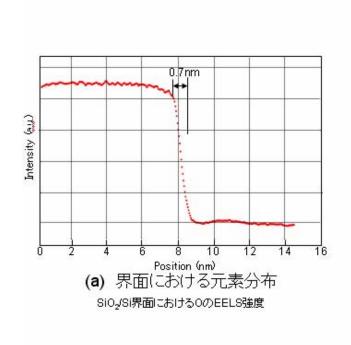

このダメージは、TEM 像のコントラスト異常としても現れる。FIB 加工直後に撮影した断面 TEM 写真の SiO<sub>2</sub> / Si 界面部分のコントラスト強度をプロットしたものを図2.4.9 に示す。界面が不鮮明になり膜中のコントラストにも不均一が生じている。また SiO<sub>2</sub> / Si 界面における O のスペクトル強度変化の半値幅も 2nm 程度に広がっている。これを低加速のイオンミリング装置を用いて FIB 加工によるダメージを除去した結果を図2.4.10 (a)と(b)に示す。イオン種は Ar、加速電圧は 0.2kV である。SiO<sub>2</sub> / Si 界面における O のスペクトル強度変化の半値幅は 0.7nm に減少し、コントラストの不均一も減少して SiO<sub>2</sub> 中や Si 中のコントラストが均一化されている。更に格子像も鮮明に観察できる事が分かった (45)。図2.4.11 に本実験で用いた低加速 Ar イオンミリ

ング装置の外観を示す(Linda 社製 Gentle Mill)。このように界面を詳細に解析する為には試料作製時に導入される元素のミキシングやダメージを出来るだけ減らす工夫が必要である。

図2. 4. 7 FIBダメージによる結合状態のミキシング

(a) 界面における元素分布 SiO<sub>g</sub>Si界面におけるOのEELS強度

図2.4.9 Gaイオンダメージの影響 (b) \*\*

(b) 格子像の劣化

(b) 格子像の改善

図2. 4. 10 ダメージ除去(低加速Arイオンミリング)の効果

GentleMill (Linda社のカタログより)

# 《装置の特長》

- ・低エネルギーイオンビーム (100eV~2keV)

- ・高シニングレート(イオン化効率向上) ⇒ミリング時間の短縮化

- イオン源のパラメータコントロール

- ・試料位置/微動コントロール

- ·OCDカメラによるTEM試料観察

- ・両面ミリング

図2. 4. 11 低加速Arイオンミリング装置

(a) 変形切り欠けメッシュ

図2. 4. 12 リデポジション抑制のための試料メッシュと試料台

## (3)その他のダメージ低減手法

FIB 加工によるダメージは Ga イオンが試料に直接及ぼす影響だけではない。FIB 加工時に、TEM 試料に衝突せず、試料表面や周囲を通り過ぎた Ga イオンはメッシュ表面で反射しメッシュ材料をスパッタリングする。このリデポジションによって試料表面が汚染される場合がある。この汚染を防ぐには Ga イオンが試料メッシュ上で反射しない配置に試料を固定する必要がある。図2. 4. 12(a)に示すメッシュは試料を「片持ち」構造で固定することが可能で、試料を加工した後の Ga イオンは全て通り抜けるためリデポジションによる試料汚染は起きない。また試料ホルダーを回転できる構造にすることによって、同じホルダーで FIB 加工(b)と TEM 観察(c)が可能になる。

## 2.4.6 今後の不良解析 FIB 装置

本稿で述べた FIB 装置は電子顕微鏡による不良解析試料作製を目的としているが、半導体応用全般という視点では配線修正、故障箇所特定(Voltage Contrast 法)、断面 SEM 観察など幅広い用途に展開されている。配線修正の目的は、配線層マスク修正の確認や試作サンプル出荷のための限られた数量の生産であり、FIB の主機能である加工に加え、金属膜のデポジション、反応性イオンエッチング、CAD ナビゲーション機能などを備えている。また故障箇所特定のために FIB 装置内にプローブを備え電圧印加やチャージの引き抜き機能を持つものもある。半導体解析用途としての特徴は、試料作製~TEM 観察分析までが短時間で結果が出せるような工夫がなされていること、加工時間が短く自動化が進んでいること、 $\mu$  サンプリングなど高度 FIB 技術の利用が可能なアプリケーションが用意されていることが重要である。高分解能 SEM を備え加工から観察まで 1 台の装置で完了させる All in One タイプも、ルーチン化できる解析対象には向いていると考えられる(46)-(49)。

さらには半導体開発評価全体の TAT 改善を考えたとき、オートプローバによる電気的なデバイスパラメータ取得と電子顕微鏡によるデバイスの微細構造解析が並行して評価が進むことが必要である。このため大口径ウエハがそのまま投入できる TEM 試料のピックアップ専用機も開発されている。

また将来的に32nmルールのデバイス解析には、更に高い加工精度と分解能が必要とされる。 Ga イオンによる汚染がなく1nm に加工精度を目標にGas Phase Ion Source やAr イオンプラ ズマ、イオン光学系の収差補正技術などが開発検討されている。

## 2.4.7 まとめ

FIB は TEM 試料の作製に従来技術にはない可能性を広げ、その結果が半導体の不良解析に広く適用されている。観察したい領域を思い通りの方向から、色々な手段で観察できる試料作製技術は、多層で微細な構造が用いられる半導体解析技術として最適である(50)(51)(52)。

今後は、オプションやユーザーインターフェイスの改良を通じて使いやすく、短 TAT な試料作製が可能になると共に、高分解能 SEM や大口径ウエハの適用など総合的な不良解析装置として発展してゆくものと考えられる。

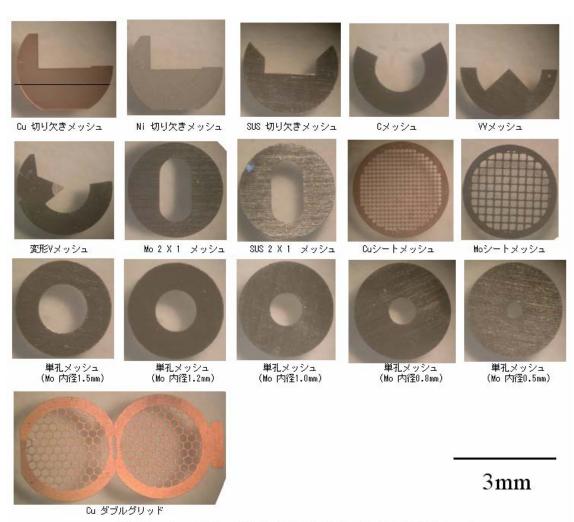

なお本節に記載した試料作製に用いたメッシュを**図2.4.13**に示す。TEM の試料作製用には様々な形状のメッシュが工夫されており、平面 TEM 観察から断面、特殊な試料作製用途にも適用されている。

図2. 4. 13 様々な形状のTEM試料メッシュ

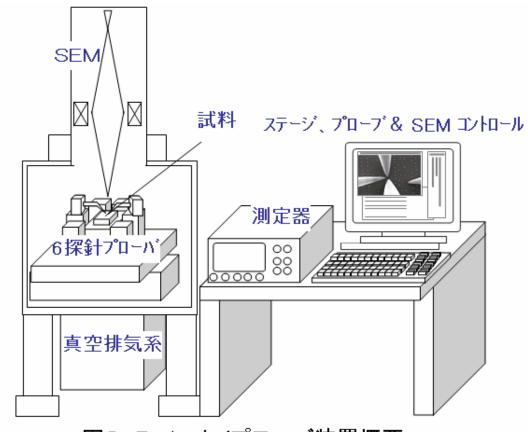

#### 2.5 微細デバイスの直接評価技術(ナノ・プローバ)

#### 2. 5. 1 はじめに

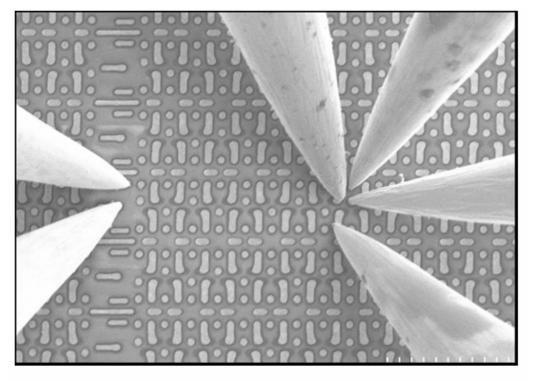

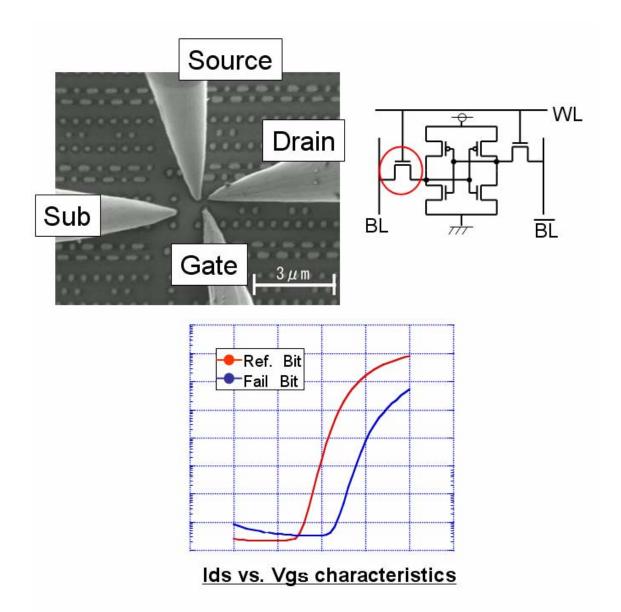

ナノ・プローバは実回路内単体デバイス評価装置である<sup>(53)(54)</sup>。図2.5.1に示すように、デバイスに直接接触可能な6探針プローブを配置し、プローブ及び測定試料の顕微手段としての SEM、及び半導体パラメータアナライザで構成されている。図2.5.2に示すように、デバイス表面を研磨しデバイスからの引き上げ電極や、配線、FIBにより形成された電極等に、先端径 100nm 程度の針を直接針当てし、電気特性を測定する。特に TEM との組み合わせによる不良解析を実施すると、その不良のバックグラウンド、電気特性結果、詳細構造等から、確実な不良メカニズムを構築することが出来、高効率なプロセスへのフィードバックが可能となる。

最近、顕微手段として AFM(Atomic Force Microscope)を使用するタイプも発表されている (55)(56)。SEM を顕微手段とする場合には電子線ダメージによるデバイスの特性劣化を考慮する必要があり、低加速化と高分解能化の両立が検討されている (57)(58)。

## 2. 5. 2 ナノ・プローバによる評価方法

ナノ・プローバによるデバイス解析技術の開発により、従来では困難であった実回路内単体デバイスの特性評価を可能にしてきた。これにより従来では不良現象の把握が困難であった不純物に起因する不良についても明らかとなってきている。しかしながら様々な解析を実施して行く中で、ナノ・プローバで得た電気特性結果のみでは不良位置の特定出来ない事例がみられる様になってきた。特に保護素子等で使用される大サイズ MOS では、例えば拡散層に電気的に欠陥が指摘されても、TEM 等の外観解析が可能な範囲までの絞り込みが困難であり、大きな技術課題であった。

本報告では、この問題を解決するために、発光解析装置とナノ・プローバを併用する事により解析が可能となった事例を第4章第2節において紹介する。

図2.5.1 ナノプローバ装置概要

図2.5.2 測定中のSEM写真(6探針)

SEMを顕微手段としコンタクトプラグ(W)に直接針(プローブ)を当てる。 上記の例は、SRAM中の特定のセルやトランジスタ単体を測定して故障原因を解明できることを示す。

図2. 5. 3 SRAMのセルを測定中のSEM写真

## 2.6 半導体不良解析技術における球面収差補正電子顕微鏡への期待

本節では、序論でも述べたように過去にもたらされた電子顕微鏡技術の break through(表1.2)と比較しながら、デバイス解析技術に対する「球面収差補正電子顕微鏡技術」への期待を考える。

## 2.6.1 球面収差補正技術とは

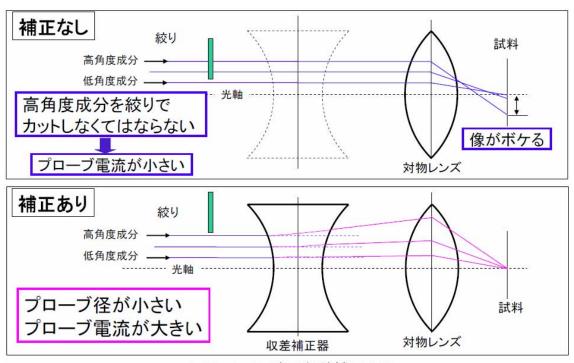

光学レンズにはレンズ表面の歪や曲率のバラつきに起因する球面収差が存在する。よって光学顕微鏡や写真カメラなどの光学系は凸レンズと凹レンズの組み合わせによって、球面収差を打ち消し回折限界にせまる分解能を実現している。しかしながら電子顕微鏡の光学系を構成する電子レンズは原理的に凸レンズしか作る事が出来ない。よってこれまでは球面収差を補正する手段が無く、電子波の波長よりはるかに劣る分解能に留まってきた。

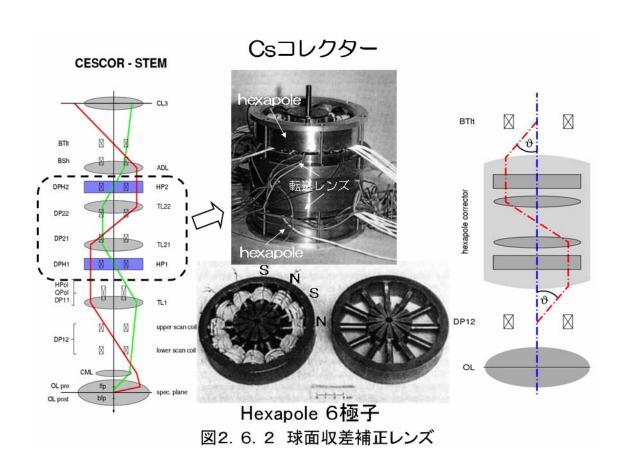

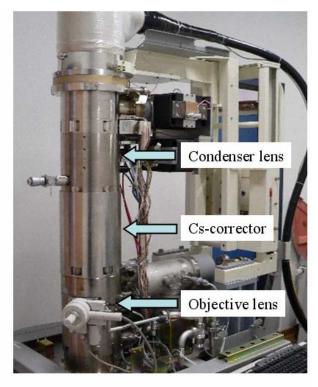

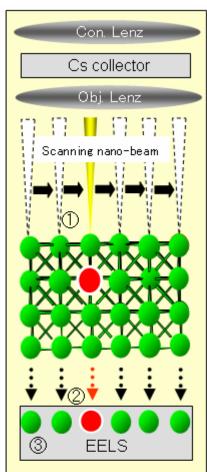

電子レンズの球面収差を補正する手段として登場したのが「球面収差補正装置(Cs collector)」である<sup>(59)-(63)</sup>。図2. 6. 1に示すように球面収差補正が無い場合、高角度成分は球面収差のため一点に集束せず像がボケたりプローブが広がる。球面収差補正装置を用いると、見かけ上、負の球面収差を発生させる6極子レンズによって球面収差を補正するため、像のボケが著しく小さくなる。またレンズの周囲を通る電子線も利用できるため、電子線量の多い明るい像が得られる。図2. 6. 2に Cs コレクターの内部構造とレンズ光学系を示す。この技術は歪やボケの無い高分解能な観察と同時に、分析感度を 10 倍以上向上させられることになり、像観察と分析の両方に効果が期待される。Cs collector による球面収差の除去作業はコンピュータコントロールにより半自動化されており、電子顕微鏡メーカによると観察毎に調整の必要は無いとされている<sup>(64)(65)(66)</sup>。図2. 6. 3に Cs collector を付けた STEM 装置の写真を示す。Cs collector は約 25cm の高さがあるため、鏡筒全体も高くなる。

#### 2.6.2 球面収差補正による効果と可能性

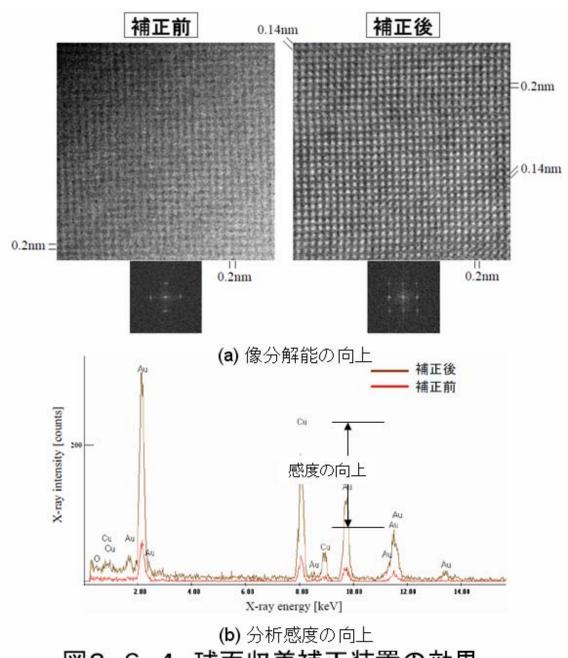

図2. 6. 4(a)に球面収差補正装置による STEM の像質の向上効果を示す。照射系の球面収差改善によって像質や分解能が向上している。またフーリエ回折図形にも、より高次の回折斑点が記録されており、Information limit が向上している。Au-Cu 合金を EDX 分析した結果を図2. 6. 4(b)示す。X 線のカウント数が5倍程度増加しており、分析感度が向上していることがわかる。

図2.6.1 球面収差補正とは

図2. 6. 3 球面収差補正器を取り付けた走査型透過電子顕微鏡 球面収差補正装置をコンデンサーレンズと対物レンズの間に取り付けた試作機(HD-2300)の外観。 ドイツ ハイデルベルグのCEOS社で撮影

前述のように表1.2に過去20年間における半導体解析分野での電子顕微鏡技術の Break Through を示した。1980年頃の Cold Emitter 電子銃はコヒーレント性の高い電子線を実現し、解像度や分析感度の向上に大きく寄与した。また高い干渉性の電子線を利用して試料薄膜中のポテンシャルを可視化する電子線ホログラフィー技術を可能にした。その後、FIB による試料作製技術や3次元観察技術、電子線回折による応力評価などが開発されてきたが、いずれも電子顕微鏡そのものの性能向上ではなく周辺技術の進展に負うところが大きい。ところが球面収差補正技術は電子レンズの球面収差という電子顕微鏡が抱えてきた本質的な分解能限界を克服するのみならず、解像度と分析感度を飛躍的に高めた電子顕微鏡技術の Break Through であることは間違いない。この顕微鏡技術の飛躍が実用材料、特に半導体の解析分野にも同様の Break Through をもたらすのかを考える(67)(68)。

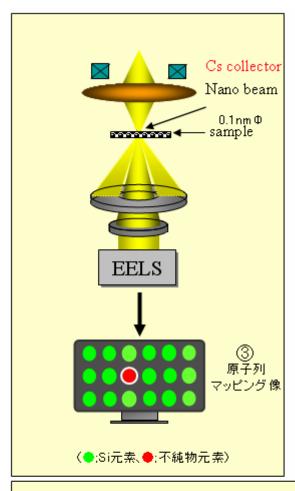

図2. 6. 4 球面収差補正装置の効果

図2. 6. 5に球面収差補正された電子レンズを通った電子線が試料上、または試料内部でどのような相互作用するかを示す。ここでは球面収差補正装置は STEM 照射系に適用したものとする。対物レンズの球面収差がほぼゼロと仮定すると、電子ビームは試料表面で非常に細く(0.1nm φ)絞ることができる。このプローブは波束(wave packet)の形をとり試料中では原子列に沿って伝播する。よってこの電子線が試料を出射する時には、ある特定の原子列の情報だけを持っていることになる<sup>(69)</sup>。この現象は試料中で電子波がブロッホ定在波を形成している限り可能であり、シリコン基板などでは 50nm 程度と見積もられている。このことよりある特定の原子

列の観察と分析が可能であることが分かる。例えば、EELS(Electron Energy Loss Spectroscopy)では特定の原子列に含まれる原子の Core Loss スペクトルを選んで測定することができる。シリコン基板で 50nm の膜厚に含まれる原子のカラムには約 100 ヶの Si 原子が含まれており、仮にこの中に 1 ヶの不純物原子が含まれていれば、その原子列は約 1%の不純物 濃度を持つことになる。1%の分析感度を持つ EELS は現実に存在しており、原子列分解能の観察と分析が同時にできることになる。

- ① 0.1 nm®の電子ビームは原子列に収束して伝播

- ② 特定の原子列情報だけを持って、結像またはEELS分析

- ③ 原子列毎の観察と分析

図2. 6. 5 球面収差補正効果への期待 観察と分析によるドーパント可視化

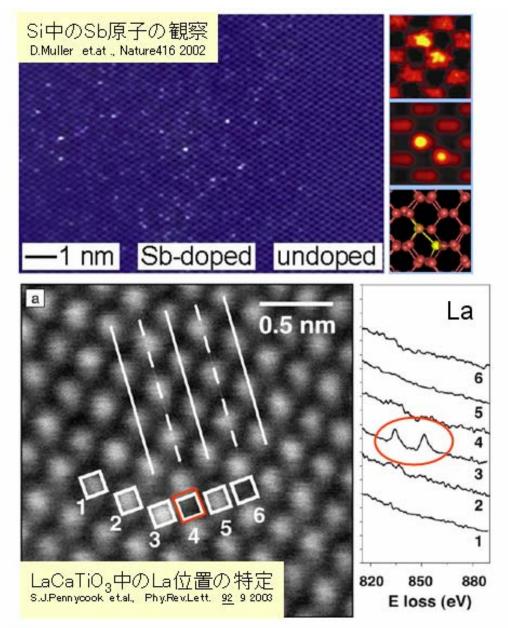

これらの可能性を示す報告を**図2.6.6**に示す。LaCaTiO<sub>3</sub>を原子列毎に EELS 分析した結果、特定の原子列のみに La の EELS Edge を観測した結果である<sup>(70)</sup>。また Si 基板中に含まれる Sb 原子の位置を Zコントラスト像として観察した報告を示す。Sb の面内分布がインプラ領域によって分かれていることが確認できる<sup>(71)</sup>。

図2.6.6 球面収差補正によるドーパント可視化例

また従来は高分解能像を得るには高加速電圧を必要としてきた。これは電子線の波長の短縮にともなう分解能の向上と電子線の色収差の低減によるものである。しかしながら、球面収差補正によっては比較的低加速(80kV 程度)でも高分解能像が得られることが分かっており、Low-K 膜などの電子線ダメージに弱い材料の評価にも適した手段と考えられる。

このように電子レンズの球面収差補正技術は原子列分解能の分析電子顕微鏡として、空間分解能と微量不純物の定量を同時に実現する可能性があり、ドーパント可視化も含む半導体解析技術の Break Through となり得る。

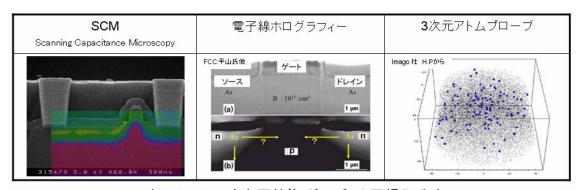

ドーパント可視化を中心に球面収差補正電子顕微鏡への期待を整理すると表2.6.1のようになる。現在、ドーパント可視化技術として有力視されている技術には表2.6.2に示すような3種類の手法がある。3次元アトムプローブを除くSCM(Scanning Capacitance Microscope)と電子線ホログラフィーは、何れもドーパントが作る「電位のポテンシャル」を観測する技術であり、ドーパントの間接的な可視化技術と考えられる。3次元アトムプローブと球面収差補正電子顕微鏡法は原子そのものの観察技術であるところが異なっている。ただし3次元アトムプローブは完全な破壊検査であり試料の再評価やシリコン基板以外でのデバイス形状の測定などには適さない。球面収差補正電子顕微鏡法は後述するように現在の電子顕微鏡技術の延長線上にあり、現行技術との親和性も高く有力な候補と考えられる。

## 収差補正電子顕微鏡技術の特徴

| 収差補正の特徴             | 電子顕微鏡的な効果       | 半導体解析への期待                       |

|---------------------|-----------------|---------------------------------|

| 原子直視性               | 原子列分解能像とEELS 情報 | ドーパント可視化                        |

| 電子線量の向上             | 分析感度の向上、短時間評価   | 高効率な評価                          |

| 低加速(80kV)で<br>高分解能像 | 試料ダメージの低減       | Low-Kなどの低ダメージ観察分析<br>分析中のダメージ低減 |

#### 調館

- 1. 試料作成技術: ダメージレスで50nm以下, FIB加工ダメージの除去手法

- 2. 鏡体の最適化: 照射系、結像系/ TEM-STEM, STEMの選択

- 3. 像シミュレーション技術:プローブファンクションによる像修正、多重回折コントラスト

表2.6.1 球面収差補正電子顕微鏡の特徴と課題

表2.6.2 主な不純物・ドーパント可視化手法

## 2.6.3 ドーパント可視化の課題

これまで報告されている結果は比較的高濃度に含まれる元素の位置の特定や Si に比べて重い元素の同定が主であるが、半導体に含まれる不純物元素にはリン(P)やボロン(B)などの軽元素が多い。またデバイスの信頼性や抵抗に関係する元素には窒素(N)や酸素(O)、またはフッ素(F)などのハロゲン、さらに炭素(C)なども汚染源として考えられる。軽元素の検出にはEELS 分光器の高感度化が必要であるが、収差補正によって照射電子線量も飛躍的に高まっているので検出できる可能性は高い。また散乱角に依存した電子線を使って結像する暗視野(HAADF)法も高分解能像が得られるだけでなく、元素識別能にも優れている。EELS では重い元素中の軽い元素の検出は難しいとされているが、HAADF 法は元素のクーロンポテンシャルによるラザフォード散乱に依存した1次的な現象(Z-contrast)を捉えるので、シリコンより軽い元素を検出できる可能性は高い。但しドーパントとしての Si 中のリン(P)に限っては、母相の Si と原子番号が一つしか違わないため、コントラストとして観察することは困難と予想される。

次に問題となるのは試料作製技術である。原子列分解能の観察を可能にするには膜厚 50nm 以下で、表面裏面ともダメージレスの試料が必要である。半導体デバイスの試料作製には FIB が一般的であり、また必須である。FIB は加速した Ga イオンによるスパッタリング加工である以上、試料表面へのダメージは避けられない。しかしながら、2. 4節でも述べたように、近年非常に低加速の Ar イオンビームを用いて Ga イオンダメージを除去する技術が開発され、装置も市販されている。さらに試料ホルダーやメッシュ等の工夫と改良によってデバイスの構成材料に影響されない平滑な試料表面を得ることもできるようになっている。

本節では収差補正は電子線の照射系に適用した場合を想定してきたが、結像系にも適用することができ非常に高い分解能が得られている。また照射、結像の両方に適用し分析と観察の両方を高分解能化することも可能である。このように一口に「収差補正電子顕微鏡」と言っても様々な方式があり、評価対象や試料の状態、得たい情報などによって選択されるべきである。また高分解能像では原子直視性に優れた STEM 方式でも照射角度の増大により多重散乱による偽コントラストの発生が懸念されており、像シミュレーション技術による結果の裏づけも必要である。

## 2.6.4 まとめ

収差補正電子顕微鏡の特徴と半導体解析技術に与えるインパクトをまとめたが、もっとも効果的な評価技術はドーパント可視化と考えられる。真のドーパント可視化には原子そのものを可視化する技術が必要となる。その点、収差補正電子顕微鏡技術は3次元アトムプローブと並んで最短距離に位置している。電子顕微鏡が他の分析手段より優れるのは観察と分析の同時性と高い汎用性、周辺技術の充実である。今後、試料作製や分光器を含む鏡体技術、シミュレーション技術などの進展によって、半導体デバイスの動作が故障解析、信頼度解析を問わず物理分析レベルで解明できるという「Break Through」が実現できると期待される。

#### 2. 7 厚い試料の観察技術

半導体の加工ルールが微細化しTEM 試料の膜厚に複数のデバイス要素が含まれるようになると、3 次元観察などの用途を除いて試料作製技術は薄膜化、ダメージレス化の一途を辿って行くように思われる。しかし半導体製品の解析技術、とりわけ実際的な故障解析結果を引き継いで実施される物理解析では、厚い試料を観察する必要に迫られる。これは主として配線系の故障解析に関わる分野において、故障位置が特定のデバイス要素に限定できなかった場合の物理解析手段として必要になっている。解析例については第5章第2節に記すが、ここでは厚い試料の観察技術について検討した結果を示す。

## 2. 7. 1 電子線の透過能と色収差

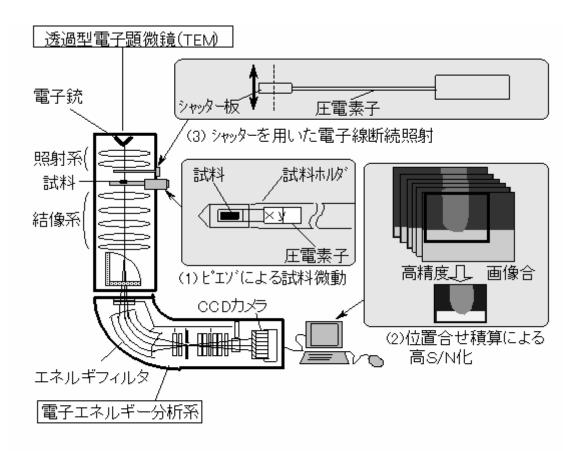

電子顕微鏡の透過能は粗い近似のもとでは加速電圧の平方根に比例して向上すること が知られているが、色収差の低減も加速電圧を高めることによってもたらされる大きな メリットである。一般に試料厚さが厚くなると透過する電子線量が減少し、像が暗くな って観察できなくなることは容易に想像ができる。従来は電子線フィルムの感度が低か ったため、厚い試料の場合は長時間の露光を要したが、観察中の試料ドリフトの問題も あって、それにも限度があった。現在では高感度の CCD カメラとデジタル的な画像処 理方法によって、まったく電子線が透過できない膜厚でなければ観察できるようになっ た。そこで、最近では色収差の増大による像質の劣化の方が、より深刻な問題になって きている。電子線が厚い試料中を進むと多数の原子と非弾性散乱を起こすことによって、 非常に幅広い(broad)エネルギー分布をもつ電子線で像観察される。これは非常に多く の波長の電子線で結像していることになり、フォーカスが一点に結ばないことによる像 質の劣化(ボケ)が著しい。この色収差を回避する方法は2つある。厚い試料を観察する ことによる色収差は $\Delta E / E$  で表される。E は電子顕微鏡の加速電圧で、 $\Delta E$  は試料中 の非弾性散乱による電子線エネルギーの広がりである。色収差を低減するにはこの式の 分母を大きくするか、分子を小さくすれば良い。分母(E)を大きくする方法が超高圧電 子顕微鏡で、分子( $\Delta E$ )を小さくする方法がエネルギーフィルタ TEM である。

また STEM も TEM に比べて色収差が少なく、半導体の厚膜試料の観察ができる。 なお STEM の観察例については第5章2節で検討する。

## 2. 7. 2 エネルギーフィルタ TEM と UHVEM

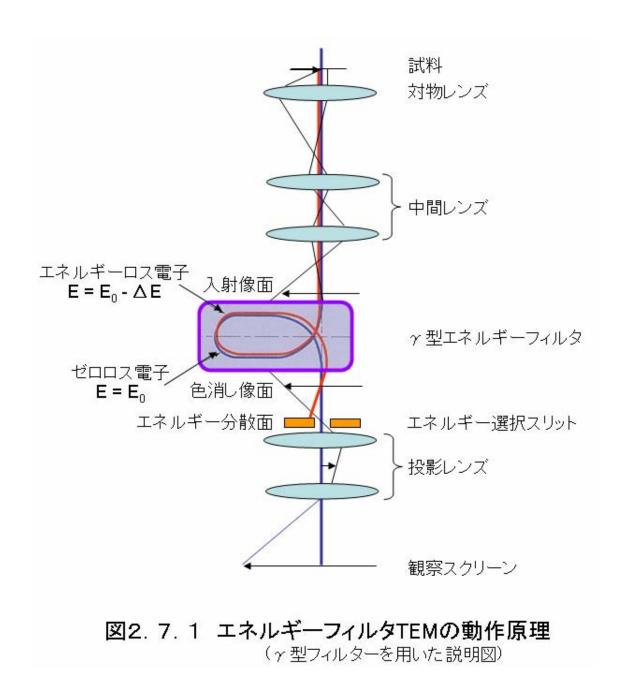

エネルギーフィルタ TEM の動作原理を図2.7.1に示す。試料を透過した電子線は対物レンズや中間レンズによって拡大された後、クロスオーバーを持ち、エネルギーフィルタの手前の入射像面に結像する。エネルギーフィルタ内では電子は、試料で失ったエネルギーの差によって異なる軌道を通るが、フィルタを出た後、全てのエネルギーの電子が色消し像面で再結像する。さらにエネルギー選択スリットの位置で空間的に収束しながらエネルギー的に分散し、エネルギー分散面にはエネルギースペクトルが形成さ

れる。エネルギー選択スリットにより特定のエネルギーの電子のみが選択され、投影レ ンズで観察スクリーンに拡大結像する(72)。

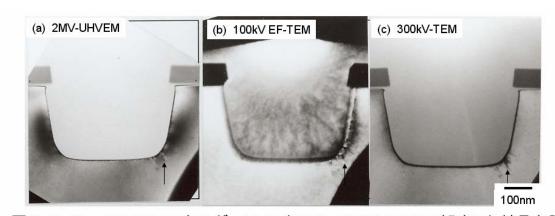

UHVEM は 1~3MV の加速電圧によって非常に大きな透過能を有する。加速電圧が 300kV-TEM と比べて 10 倍になると透過能は約 3 倍になる。300kV-TEM では通常 200nm 程度の試料膜厚を用いて観察するため、600nm 以上の膜厚でも同等のコントラ ストで観察できることになる。さらに色収差の低減効果もあり実用上、1μm 程度は問 題なく観察できている(73)。

図2. 7. 2にエネルギーフィルタ TEM と UHVEM の外観を示す。

100kV エネルギーフィルタTEM

図2. 7. 2 エネルギーフィルタTEM(EF-1000) と超高圧電子顕微鏡(H-3000)の外観

## 2. 7. 3 色収差低減の効果

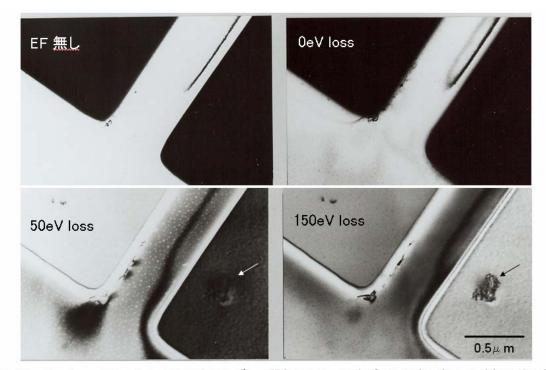

図2. 7. 3に STI(shallow trench isolation)のコーナー部に発生した結晶欠陥を通常の 300kV 電子顕微鏡、100kV のエネルギーフィルタ TEM、2MV の UHVEM で観察した例を示す。試料膜厚は約  $1.0\,\mu$  m である。結晶欠陥は STI コーナー部に Si 基板の (111)面上に発生している。通常型の 300kV-TEM では不明瞭なコントラストとしてしか観察でないが、2MV-UHVEM では明瞭な回折コントラストを伴った結晶欠陥像として観察できる。またエネルギーフィルタ TEM は僅か 100kV の加速電圧ながら、結晶欠陥の回折コントラストはもとより素子分離部分の酸化膜の粗密コントラストまで観察できている。

エネルギーフィルタ TEM はエネルギー選択スリットによって任意のエネルギーロスした電子線で結像させることが出来る。図2.7.4に Si 基板中の結晶欠陥をエネルギーフィルタ TEM で平面観察した例を示す。結晶欠陥は STI 構造の活性化領域部(トランジスタが形成される領域)に発生しており、その領域の試料膜厚は 0.8  $\mu$  m である。(a)はフィルタ無し(全ての電子線で結像)のため STI の縁がぼやけており不明瞭な像となっている。エネルギーロス値を 0eV(弾性散乱電子のみ)にすると、膜厚の厚い領域はコントラストを失い観察できない。50eV では活性化領域が観察できるようになり、150eVのエネルギーロス値で目的の結晶欠陥が観察できた。これは厚い試料部分を透過した電子線はエネルギーロスも大きく、その領域の情報も大きなエネルギーロスを選択することによって観察可能になることを示している。このことよりエネルギーフィルタ TEMを用いてエネルギーロス値を選ぶことによって、膜厚の厚さのため通常の TEM では観察できないような微細構造や欠陥も明瞭に観察できることが分かった(74)。

図2. 7. 3 UHVEM、エネルギーフィルタTEM、300KV-TEMで観察した結晶欠陥

図2.7.4 EF-TEMのエネルギー選択スリットを変えて観察した結晶欠陥

### 参考文献

- (1) R.F.Egerton: Electron Energy-Loss Spectroscopy in the Electron Microscope 2<sup>nd</sup>-Edition: PLENUM Publishing Co. New York (1998) p346

- (2) F.Ernst, M.Ruhle: *High-Resolution Imaging and Spectrometry of Materials* Springer-Verlag. Berlin (2002) p119

- (3) D.C.Joy, A.D.Romig and J.I.Goldstein, *Principles of analytical electron microscopy*Plenum Press, New York (1986) p155

- (4) 西山、大島、品田:ショットキー電子源から放出される電子ビームの狭エネルギー幅 化 応用物理 第71巻 第4号(2002)

- (5) Terada S, Aoyama T, Yano F, Mitsui Y(2001) Time-resolved acquisiton for elemental mapping by energy-filtering TEM. J.Electron Microsc., 50, 83-87.

- (6) Terada S, Aoyama T, Yano F, Mitsui Y(2002) Time-resolved acquisition technique for spatially-resolved electron energy-loss spectroscopy by energy-filtering TEM. J.Electron Microsc., 51,291-296.

- (7) Ishizuka K, Kimoto K and Bando Y (2003)Improving Energy Resolution of EELS Spectra by Deconvolution using Maximum-Entropy and Richardson-Lucy Algorithms. Proc. Micros. Microanal., San Antonio, 832–833

- (8) 鷹岡:三次元電子顕微鏡の開発と特徴 **39**(2004) 「顕微鏡」p11

- (9) 朝山、加藤: LSI 特定個所の断面 TEM 試料作製技術 **32** (1997)「電子顕微鏡」 p44

- (10) 馬場:電子線トモグラフィー再構成の原理 **39** (2004) 「顕微鏡」p4

- (11) DeRosier, D.J. and Klug.A: Nature, 217,130(1968)

- (12) Hoppe.W. et.al.: Hoppe-Seyler's Z.Physiol.Chem., **355**,1483 (1974)

- (13) Zhang.H and Takaoka.A.:Rev.Sci.Instru., **69**,4008 (1998)

- (14) Grunewald.K et.al.: Science, **302**,1396 (2003)

- (15) Midgley.P.A. and Weyland.M.: Ultramicroscopy, 96,413 (2003)

- (16) Yamaguchi.K et.al., Micromolecules, 36, 6962 (2003)

- (17) 田中: 材料・デバイス系試料の電子線トモグラフィー 39 (2004)「顕微鏡」p26

- (18) 朝山、鷹岡:透過電子顕微鏡による半導体デバイスの三次元的解析「応用物理」 76 (2007) 掲載予定

- (19) 友清、奥山:収東電子回折による結晶の歪場計測 **39**(2004)「顕微鏡」p42

- (20) Hirsch, P.B., Howie, A., Nicholson, R.B., Pashley, D.W. and Whelan, M.J.: *Electron microscopy of thin crystals*, Robert E, Krieger, New York, (1977), p195

- (21) Reimer, L.: Transmission Electron Microscopy, 4<sup>th</sup>-Edition,, Springer-Verlag, Berlin (1997) p250

- (22) Tomokiyo, Y., Matsumura, S., Kuwano, N., Kominami, M., Okuyama, T. And Oki, K.:

- J.Electron Microsc., 35 359 (1986)

- (23) Okuyama, T., Matsumura, S., Kuwano, N. and Tomokiyo, Y.: Ultramicroscopy, 31, 309(1989)

- (24) Tomokiyo, Y.: J. Electron Microsc., 41 403 (1992)

- (25) 山崎:収東電子線回折法を用いた微小歪測定法の開発とその問題点、第 63 回日本顕 微鏡学会学術講演会予稿集 p166

- (26) 志村: 半導体シリコン結晶工学、丸善東京、(1993) p355

- (27) Zuo, J.M., Gjonnes, K. and Spence, J.C.H.,: J. Electr. Micros. Tech., 12, 29 (1989)

- (28) Zuo, J.M.: Ultramicroscopy 41, 211, (1992)

- (29) 安田、斎藤、田中:HOLZ 線図形の Hough 空間フィッティングによる格子歪精密測定、 第63回日本顕微鏡学会学術講演会予稿集 p165

- (30) Kraemer, S. and Mayer, J.: J. Microsc, 194, 2, (1999)

- (31) ITRS:International Technology Roadmap for Semiconductors, 2002 Edition

- (32) B.Li et.al:Line Depletion Electromigration Characteristics of Cu Interconnects pp140 IRPS(2003)

- (33) 久慈憲夫: 故障診断手法とその動向、LSI テスティングシンポジウム、pp.64-69 (2000)

- (34) 二川 清: LSI の故障解析技術の最新の動向、REAL 誌、日本信頼性学会、25, p139-147(2003)

- (35) 朝山、荒川: LSI 特定個所の断面 TEM 試料作製技術 「電子顕微鏡」 **32** p44 (1997)

- (36) 矢口他: FIB-STEM 共用 3D 解析ホルダーの開発(1)、日本顕微鏡学会第 59 回学術 講演会要旨集 pp106(2003)

- (37) 今野他: FIB-STEM 共用 3D 解析ホルダーの開発(2)、日本顕微鏡学会第 59 回学術 講演会要旨集 pp107(2003)

- (38)「LSI 故障解析技術開発強化の提言」p28 半導体産業研究所故障解析 WG 編(2003)

- (39) 黒田:FIB 加工による電顕試料作製の現状と課題 「電子顕微鏡」 **37**, p154 (2002)

- (40) 薮内: 半導体デバイス観察への FIB の適用 「電子顕微鏡」 37, p159 (2002)

- (41) Saito, M., Aoyama, T., Hashimoto, T. and Isakozawa. S.: J. Jpn. Appl. Phys., 37,355 (1998)

- (42) Yabuuchi, Y., Proc. Of the 12<sup>th</sup> European Congress of Electron Microscope, p565 (2000)

- (43) 加藤: FIB で作製した半導体 TEM 試料のダメージ: 「顕微鏡」 41, p45 (2006)

- (44) 朝倉健太郎、平坂雅男、為我井晴子:失敗から学ぶ電子顕微鏡試料作製技法 Q&A、アグネ承風社 (2006) p113

- (45) 寺田、橋川、朝山:半導体デバイスの低ダメージ TEM-EELS 試料作製技術、第 63 回日本顕微鏡学会学術講演会予稿集 p161

- (46) 矢口、鈴木、今野、上野、稲田、東、朝山:微細化・高集積化デバイス対応3D 構造解析技術、第63回日本顕微鏡学会学術講演会予稿集 p159

- (47) T.Kamino, et.al.: J.Electron Microsc., 53, 583 (2004)

- (48) 村田:低加速 FIB を用いた TEM 試料作製、第63回日本顕微鏡学会学術講演会予稿集 p160

- (49) 高橋、中谷、山本、完山、岩崎、大柿、藤井:トリプルビームを用いた TEM 試料作製技術、第63回日本顕微鏡学会学術講演会予稿集 p161

- (50) Kato, N. I.: J. Electron Microsc., 53, 451-463 (2004)

- (51) Sasaki, H. et al.: J. Electron Microsc., 53, 497-500 (2004)

- (52) 朝山匡一郎, 橋川直人, 寺田尚平, 矢野史子:第 61 回学術講演会 予稿集 p48(2005)

- (53) Y. Mitsui, F. Yano, Y. Nakamura, K. Kimoto, T. Hasegawa, S. Kimura and K.Asayama, "Physical and Chemical Analytical Instruments for Failure Analysis in G-bit Devices", Ext. Abst. IEDM, p.329 (1998)

- (54) 柳田、水野、矢野、梅村、三井"ナノプローブ技術を応用した 4 探針プローバ による、単体実デバイスの電気特性評価技術"、LSI テスティングシンポジウム、pp.243-244 (2002)

- (55) C.A.Waggoner, "A New Submicron Probing Technique for Failure Analysis of Integrated Circuits.", ESREF 2002 Proceedings.

- (56) A.N.Erickson, "Gate fault isolation and parametric characterization through the use of atomic force probing", IRPS proceedings, p.617 (2004).

- (57) Takayuki Mizuno, Miho Takahashi, Yoshie Azuma, Hiroshi Yanagita, Kyoichiro Asayama, Koji Nakamae: "Maximum permissible EB acceleration voltage for SEM-based inspection before electrical characterization of advanced MOS" IRPS-2007 (2007)Proc. P618

- (58) 水野、高橋、東、朝山:ナノ・プローバを用いた故障箇所絞込み技術の紹介、 第 63 回日本顕微鏡学会学術講演会予稿集 p158

- (59) Rose H., Ultramicroscopy **78**, 13, (1999)

- (60) Haider M., et.al.,: Nature **392** 768, (1998)

- (61) Haider M, Rose H, Uhlemann S., Schwan E., Kabius B., Urban K.: Ultramicroscopy **75**, 53, (1998)

- (62) Uhlemann S., Haider M.: Ultramicroscopy 72, 109, (1998)

- (63) Zach J., Haider M.: Nucl Instrum Meth Phys Res A363, 316, (1995)

- (64) 沢田、奥西、富田、山本:収差補正 200kVTEM·STEM:「顕微鏡」 41 p11 (2006)

- (65) 中村他: 走査透過電子顕微鏡の球面収差補正とその応用: 「顕微鏡」41 p16 (2006)

- (66) Freitag,B.他: 次世代の電子光学系を有する収差補正電子顕微鏡の開発: 「顕微鏡」 **41** p21 (2006)

- (67) 田中: 収差補正、次の道を見つけよう 「顕微鏡」41 p2 (2006)

- (68) 山崎、田中:球面収差補正 TEM 法の材料研究への応用 「顕微鏡」41 P3 (2006)

- (69) 阿部、S.J.Pennycook: Sub-A STEM による局所構造解析「顕微鏡」41 p7 (2006)

- (70) S.Pennycook et.al.,: Materials Advanes through Aberration Corrected Electron Microscopy, Phy.Rev.Lett. **92** 9 (2003)

- (71) D.Muller et.al.,: Atomic-scale imaging of individual dopant atoms and clusters in highly n-type bulk Si, Nature **416** (2002)

- (72) 朝山匡一郎、加藤好美: エネルギーフィルタ TEM による半導体デバイスの観察、電子顕微鏡 **34**(1999) p22

- (73) 朝山匡一郎、荒川史子: 超高圧電子顕微鏡による MOS トランジスタと拡散層の観察、日本電子顕微鏡学会「LSI への超高圧電子顕微鏡の応用研究部会講演会予稿集(1995)」p12

- (74) 朝山匡一郎:  $\gamma$  型エネルギーフィルタ TEM による半導体デバイスの観察、日本学術振興会、第 132 委員会「第 3 回ナノビーム技術シンポジウム資料」(1998) p33

# 第3章 シリコン基板に関する不良解析

本章ではシリコン基板内部やデバイス界面における主として結晶学的な要因によって起こる不良の解析について述べる。解析方法の詳細は第 2 章に記した通りであるが、必要に応じて本章にも記載する。

### 3.1 結晶欠陥の生成とその観察

半導体デバイスはシリコン半導体基板上に形成される。ウエハは  $100 \, \mu \, \text{m} \sim 700 \, \mu \, \text{m}$  の厚さがあって、その大半はトランジスタや配線などデバイス構造物を支える基台である。しかしながらシリコン基板の最上層部分( $\sim 2.0 \, \mu \, \text{m}$ )はデバイスの動作に重要な役割を果たしている。

例えば MOS トランジスタはゲート電極に印加した電圧(Vg)がゲート酸化膜を介して MOS のチャネル部分に反転層を生じさせ、そこを電流経路として MOS のソース・ドレイン間に電流を流れるようにする、いわば「スイッチ」のような素子である。シリコン基板と MOS のゲート酸化膜界面に生じた異常は MOS 動作の原理に直接影響する。このためシリコン基板の結晶欠陥によって、様々な不良が発生する。結晶欠陥生成のメカニズムはプロセスにともなう汚染や加工形状にともなう応力、イオン注入ダメージによるアモルファス化とアニールによる再結晶化、また素子分離領域でも埋め込み酸化膜とシリコン基板の間に大きな応力が発生し、これが原因となる結晶欠陥が発生する。ここでは結晶欠陥の観察とデバイスの不良について述べ、結晶欠陥生成の原因となる応力評価については後述する。

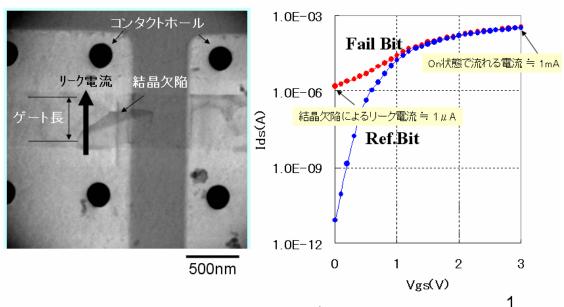

図3. 1. 1に 150nm 相当のプロセスで作製した SRAM の結晶欠陥を平面で観察し、同じ領域の断面を観察した例を示す。平面観察ではトランジスタの活性化(アクティブ)領域に分布している結晶欠陥が、断面観察することによって Si の(111)面上に分布していることが分かる。これはダイアモンド型結晶構造を持つシリコンの最稠密面であり、もっとも滑りやすい面上に欠陥が分布している(1)(2)。このような欠陥が実際にトランジスタのリーク原因となった例を示す。

図3. 1. 2の平面観察からはトランジスタのソース・ドレイン間に結晶欠陥が観察される。ナノ・プローバによる電気的な評価の結果によると、この MOS トランジスタはゲート電圧(Vg)=0V の時でも約  $1\mu$  A の電流がソース・ドレイン間に流れており、これは MOS の動作電流(約 1mA)の 0.1%に相当する。この結晶欠陥を図2. 4. 1に示す試料作製方法により断面 TEM 観察した結果を図3. 1. 3に示す。MOS トランジスタの活性化領域のゲート酸化膜直下に結晶欠陥が達しており、この部分の Si 基板/ゲート酸化膜界面に高さ約 1nm の段差が生じていた。この MOS トランジスタのゲート幅は  $1.2\mu$  であり、観察された結晶欠陥の大きさはゲート幅の約 0.1%である。この結晶欠陥を寄生的な MOS によるリークパスとみなすと、電気的なリーク電流量と図3. 1. 3に示す結晶欠陥による段差大きさは一致している。

図3.1.1 SRAMに生じた結晶欠陥の平面と同じ箇所の断面TEM観察

結晶欠陥によるリーク電流(1 $\mu$ A)はMOSトランジスタのOn電流(1mA)の  $\frac{1}{1000}$

図3. 1. 2 MOSゲート酸化膜直下に発生した結晶欠陥とリーク電流

ゲート幅= $1.2\,\mu$  mのMOSの  $\frac{1}{1000}$  (1.2nm)のMOSが出来ている

図3. 1. 3 結晶欠陥によりActive上に現れた段差

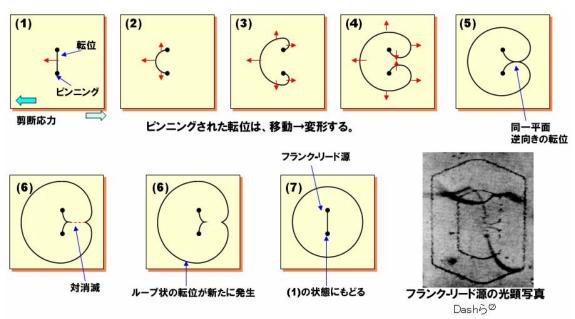

図3.1.4 結晶欠陥の増殖モデル候補のフランク・リード源

図3.1.5 デバイス構造における結晶欠陥の増殖モデル

このような結晶欠陥が増殖する理由は、古くから知られているフランク・リードのモデル<sup>(3)(4)</sup>を仮定すると一定の説明が得られる。図3. 1. 4に示すようにピンニングされた転位に外部から応力が加わると転位線がループ状に広がり、すべり面である(111)面上を移動・増殖してゆく。応力源としては素子分離領域(STI)に働く応力や、プロセス温度による熱応力、シリコン基板自体の変形による応力などが(111)面上で分解剪断応力として働いていると考えられる。このモデルから考えられる転位分布を図3. 1. 5に示すと、概ね予想される転位分布を再現できることが分かる。但しこのモデルの証明は、800℃程度におけるプロセス温度、実際の応力下における転位の拡張を観察する必要があり、in-situ実験も含めた検証が必要である。

### 3.2 シリコン基板の応力評価と不良解析例

### (1) CBED による応力評価とシミュレーション

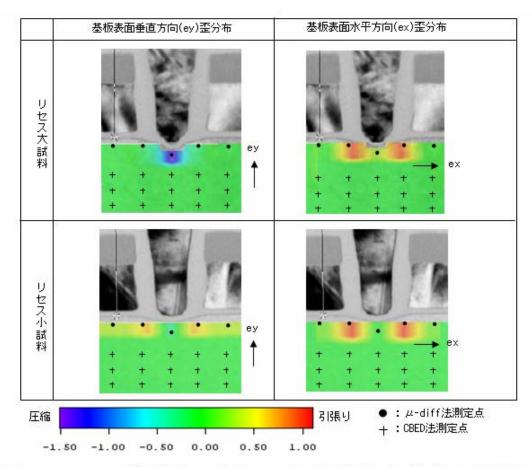

第2章3節でも述べたようにCBEDやnano-diffractionによる応力評価では、一定以上(250nm)の試料膜厚がないと、薄膜化による応力の開放により正確な値が得られない(5)。一方、デバイスの微細化によってMOSトランジスタの最小加工線幅が65nm以下になるに及んでは、250nmの試料膜厚中には複数のデバイス要素が含まれてしまう。よって得られる結果は必然的に複雑な応力構造を積算した試料での計測となり、不良現象や結晶欠陥の発生モデルを説明するための評価結果を得るには、単純なパターンによりモデル化された構造を測定する必要がある。

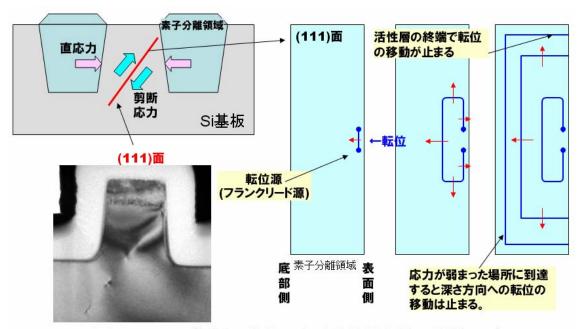

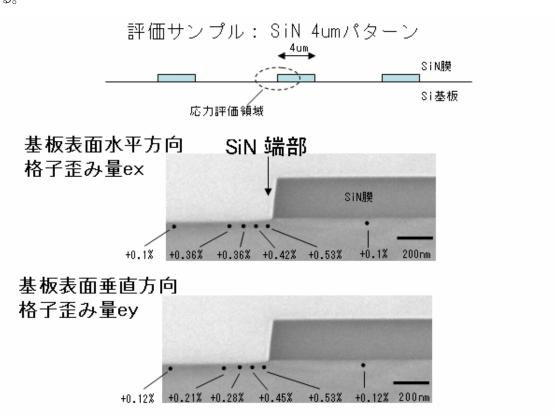

図3. 2. 1 単純なSiNパターンによる応力の評価

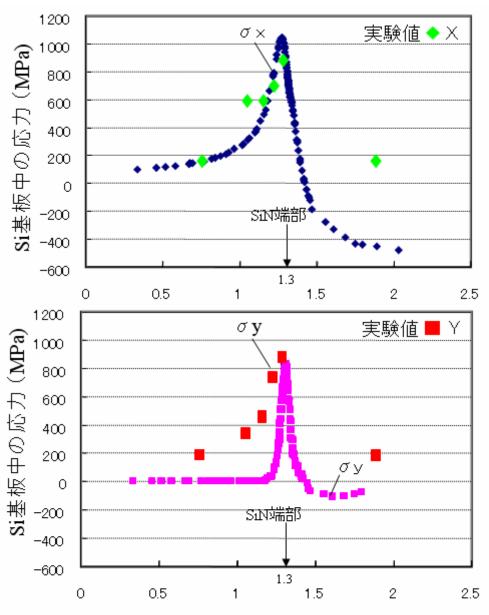

ここでは、まず CBED や nano-diffraction による応力評価の妥当性を実験的に評価した。図3. 2. 1に示すような単純な SiN パターンが作り出す応力について評価した。膜厚 250nm の SiN を Si 基板上にデポし、ホトリソグラフィーにより  $4\mu$  m 幅のパターンを得る。これを FIB により膜厚 350nm の断面 TEM 試料に加工し、Si 基板表面の直下 20nm のところから CBED により応力を評価した。評価点は SiN 端部を中心とした 6 点で基板表面と水平方向 $(e_x)$ と基板表面垂直方向 $(e_y)$ の応力成分について測定した。その結果を図3. 2. 2に実測値6 点とシミュレーション値の比較として示す。SiN パターンの端部を極大値とした応力分布については、X 方向では実

測値とシミュレーション値は比較的良く一致している。また Y 方向でも応力分布の傾向は同じで定性的な評価は可能であることが分かった。これより、CBED や nano-diffraction を用いた応力測定はシミュレーションとも良く一致する事が確かめられた。

図3. 2. 2 CBEDによる応力評価結果と シミュレーションの比較

### (2) 実際のデバイスパターンでの応力評価

実際のデバイスパターンでは 3 次元的な形状をしており、微細デバイスにおいては前後のトランジスタ構造も含まれるため複雑な応力分布となる。試料作製精度も含めて応力の絶対値評価は困難と考えられる。しかしながら、一定の構造の違いが Si 基板中の応力分布に差を生じさせていることは十分に予想され、それが不良原因や信頼性との因果関係を含んでいる事も予測される。

図3. 2. 3 デバイスパターンによる応力分布の評価 (CBED & nano-diffraction)

図3. 2. 3は PolySi プラグ直下の Si 基板にできた窪み(リセス)量の違いによる応力分布を計測した例である。PolySi のプラグの直下は両側のトランジスタゲートに挟まれた構造となっており、しばしばリセス量にばらつきが生じ、これがトランジスタの動作に影響することが懸念されていた。Si 基板の表面付近では強い応力のため HOLZ 線が分裂して応力評価できないため、μーdiffraction 法で、それ以外の箇所では CBED 法で評価した。その結果、基板に垂直方向(y方向)の応力について、リセス量が大きい場合は強い圧縮応力が生じる事が分かった。X 方向についてはリセス部分の両側でリセスの大小に関わらず、同じ程度の引っ張り応力が見出された。これよりゲート加工プロセスによる Si 基板の窪み(リセス)量の違いによって応力の方向と強

さに大きな違いが生じる事が分かった。また応力成分にも明らかな差が生じる事が分かった。 この応力分布、大きさの違いとデバイス動作の不安定性の間に直接の因果関係は明らかでは ないが、実際のデバイスではわずかな形状の違いが応力分布に大きな影響を与えている事が 明らかとなった。

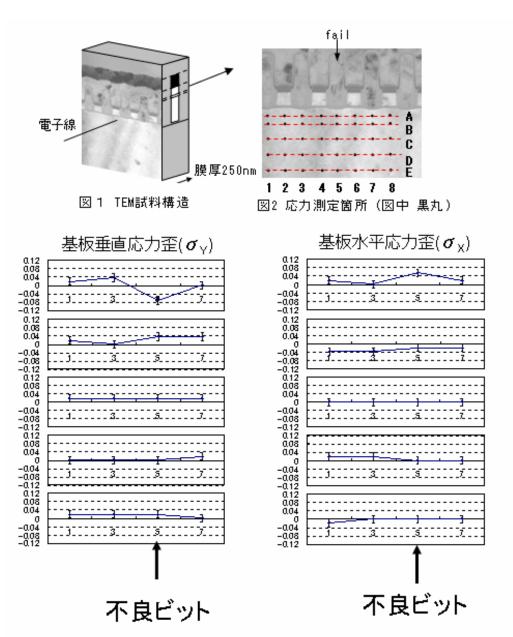

図3.2.4 メモリセルのリーク不良と応力の相関結果

次に実際にメモリセルでディスターブ不良の起こった例について応力分布を評価した。ディスターブ不良とはフラッシュメモリのある特定のメモリセルに書き込み読み出し動作を繰り返すと、動作電圧がその周辺のメモリセルに影響を及ぼし、一定以上の書き換え動作後、メモリの内容が反転する現象を言う。これは特定メモリセルのフローティングゲートに電子を注入する動作において、電子が何らかの原因で流出し、隣接する MOS トランジスタの書き込み情報である Vth シフト量が変動することを指す。原因としては書き込みと消去するトランジスタの電流リークやゲート酸化膜の劣化が考えられている。この例では、不良ビット直下の応力により Si 基板のバンドギャップが狭くなってトランジスタのリーク電流が増えるモデルを仮定した。図3.2.4に実際にディスターブ不良の起こっているビット周辺の応力分布を評価した結果を示す。図中、1、3、5、7の各点は PolySi ゲート直下の応力を表す。これより不良ビット位置の「5」では X 方向(基板水平方向)において引っ張り応力、Y 方向において圧縮応力が周囲の正常ビットと比べて大きい事が分かった。今のところ、その他の状況証拠との関連から、この応力がディスターブ不良の直接の因果関係かどうかは明らかでないが、不良ビットを特定しての応力評価が何らかの差を示す事が明らかになった最初の例として注目される。

### 3.3 静電保護素子と静電破壊

静電気は半導体デバイスの信頼性にとって大きな問題である。人体は静電気の発生源となりやすく、乾燥時のドアノブや自動車のドアでの放電衝撃は知られるところである。半導体デバイスにおいては、特に携帯電話、小型オーディオ等人体の近くで使用される機器は常に静電気の脅威にさらされている。また最近ではクレジットカードや電子マネーカードなどのように、個人情報や課金情報を高度なセキュリティとともに書き込んだマイコンも登場しており、静電破壊に対する対策は益々重要になっている。

静電気に対する対策は主としてパッケージやセット基板でとられることが多いが、半導体チップ側の一般的な対策としては、デバイス側にグランド端子を数多く設けデバイス全体がフローティングになりにくくする方法や、ESD(Electric Static Discharge)デバイス(静電保護素子)を用いる方法がある。これは静電気により不可逆的な MOS のゲート破壊が生じる前に、高濃度の拡散層を用いた P-N 接合に静電気を誘導し、可逆的な破壊が可能なデバイス構造を用いて静電気のエネルギーをシリコン基板(グランド側)に放出させる方法である。しかしこれとて静電エネルギーの度が過ぎると ESD 構造自体の破壊を伴って不良に至ることがある。

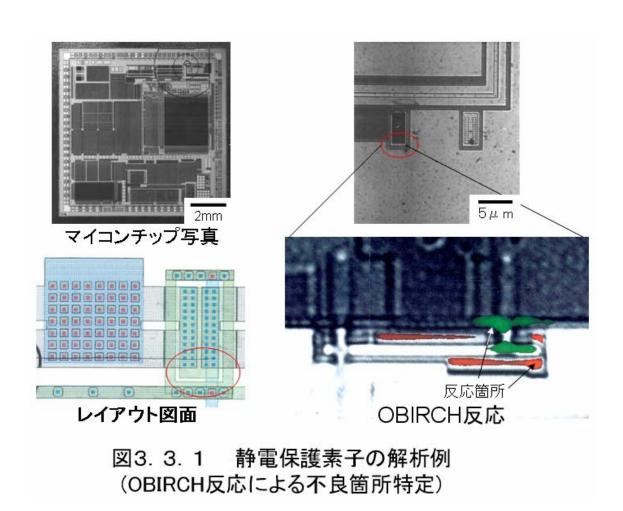

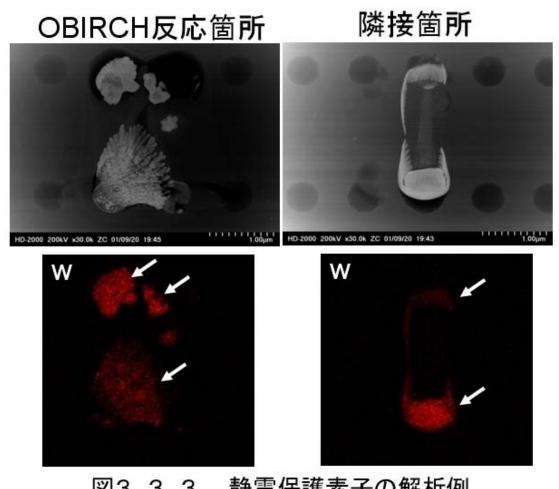

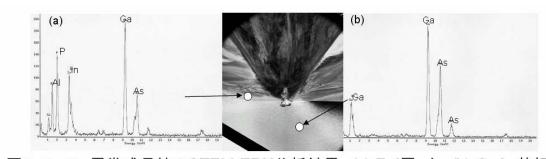

その例を図3. 3. 1に示す。携帯電話用の32bitマイコンにおいて静電破壊試験中に基板リーク不良が発生した。現象としては静電破壊により保護素子が破壊され入力端子の信号がシリコン基板に抜け出している不良である。不良箇所の特定にはOBIRCH(Optical Beam Induced Resistivity Change)を用いた。これは赤外域のレーザーを照射しながら、不良が予想される端子間の電流量を観測し、電流の増減が大きかったところを不良箇所として表示するものである(表1.3参照)。微小領域の赤外加熱を利用して局所的な抵抗変化を捉えることができ、特に配線やトランジスタのショートに有効な手段として知られている。その結果、レイアウト上から静電保護素子が並列して配置されている部分の一箇所でOBIRCH反応が得られシリコン基板へのリークと判明した。図3. 3. 2にこの領域を平面 TEM 観察した結果を示す。静電保護素子のコンタクト間に金属組織と思われるコントラストと多数の結晶欠陥が観察された。

OBIRCH反応箇所

隣接箇所

図3.3.2 静電保護素子の解析例 (OBIRCH反応箇所の平面TEM観察)

また図3.3.3に STEM-EDX による元素マッピングの結果を示す。基板から観察された金属のコントラストはタングステン(W)であることが分かった。この W は MOS トランジスタと第一層目のメタル配線を接続しているコンタクトホールに埋め込まれている CVD-W と推定される。静電試験中の静電エネルギーによりコンタクトホール中の W が溶融しシリコン基板側に突入したものと考えられた。

図3.3.3 静電保護素子の解析例 (OBIRCH反応箇所のSTEM-EDX分析)

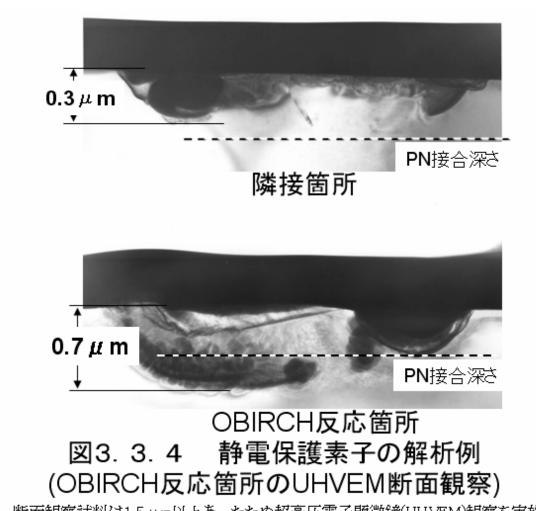

しかしながら OBIRCH 反応は一箇所であったにもかかわらず、静電保護素子の破壊跡は隣接する 2 箇所で観察された。この原因を調べるため、平面 TEM 試料から断面 TEM 試料を FIB で作製し、再度 TEM 観察した。但し静電破壊箇所は数  $\mu$  m の領域に達しており、実際に P-N 接合部を貫通した箇所を特定することは通常の TEM 試料膜厚では不可能である。よって試料膜厚  $1.5\,\mu$  m とし UHVEM を用いて、加速電圧 2MV で断面観察した。その結果を図3. 3. 4 に示す。 UHVEM 観察の結果、OBIRCH 反応が生じていた静電保護素子では W の突入深さが  $0.7\,\mu$  m に達しており、この箇所の P-N 接合深さと推定される、 $0.4\,\mu$  m を超えていた。

しかし OBIRCH 反応が現れなかった静電保護素子では W の突入深さが 0.3 μm に留まって おり、シリコン基板に信号電流がリークしなかったことが判明した<sup>60</sup>。このように、FIB による不良 箇所の平面→断面試料作製手法を用い、TEMと分析 STEM、さらに UHVEM の観察によれば、 電気的な不良現象と、不良箇所を検出する光学的手法による知見を矛盾なく説明することが でき、不良メカニズムの特定が可能となる。

断面観察試料は1.5μm以上あったため超高圧電子顕微鏡(UHVEM)観察を実施

### 参考文献

- (1) 上田: 実験物理学講座23「電子顕微鏡」、共立、p251 (1982)

- (2) 辛島:「転位論」日本金属学会、丸善(1977), p627

- (3) F.C.Frank and W.T.Read: Phys.Rev, 79(1950),p722

- (4) 鈴木: 金属物理、4(1958), p109

- (5) 友清、奥山:収束電子回折による結晶の歪場計測 39 (2004)「顕微鏡」p42

- (6) 朝山匡一郎、荒川史子: 半導体デバイスの信頼度不良解析 「文部科学省ナノテク支援 総合プロジェクト実績報告書」 大阪大学超高圧電子顕微鏡センター p18 (2002)

## 第4章 MOSトランジスタのデバイス構造の不良解析

この章では半導体デバイスの単位素子である MOS トランジスタに関する不良解析と解析技術を扱う。 MOS トランジスタはシリコン基板や配線層と密接に関係しているが、特にトランジスタを構成しているゲート多結晶シリコン材料(Poly Si)、ゲート酸化膜または酸窒化膜に関する解析結果を含む。またシリサイドやトランジスタ不純物元素はシリコン基板中に形成されるデバイス要素であるが、トランジスタ動作の基本的な部分であるため本章で扱う。

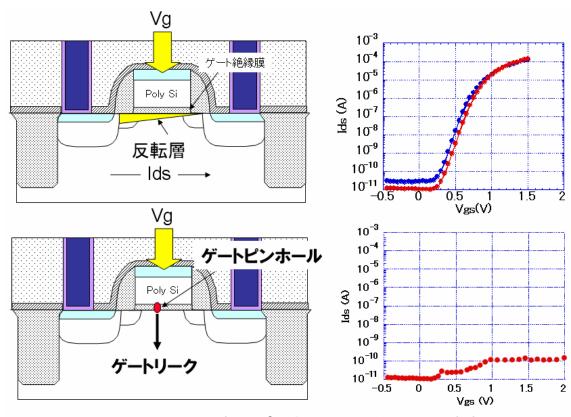

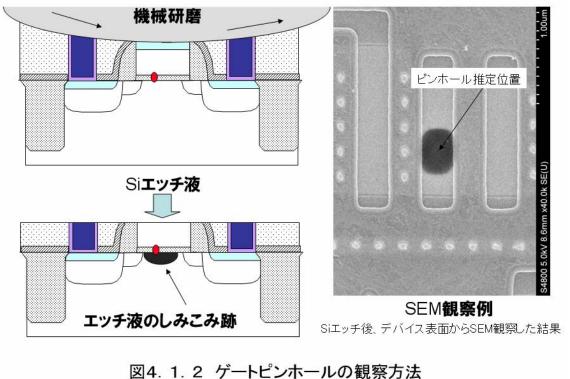

### 4.1 MOSトランジスタのゲート酸化膜破壊解析

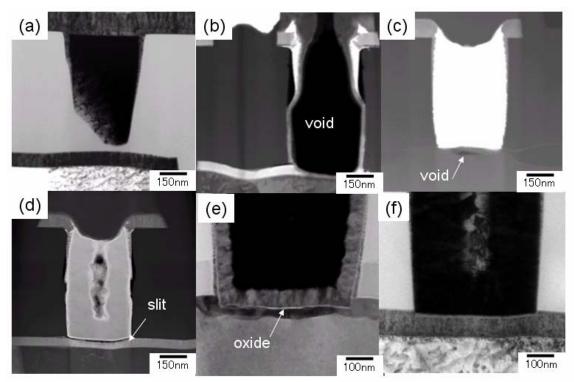

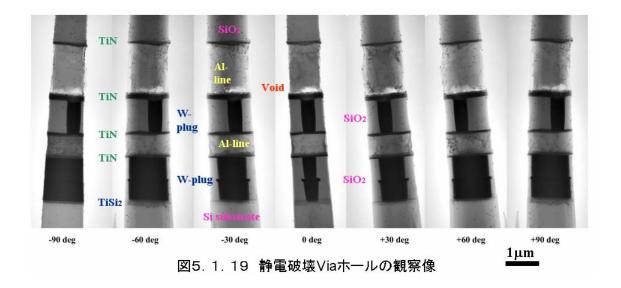

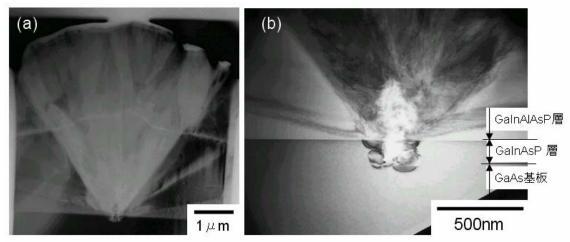

半導体デバイスの単位素子である MOS トランジスタは、ゲート電極に加わる電圧によってチ ャネル部にできる反転層を介してソース・ドレイン間の信号電流を制御する、一種のスイッチ素 子である。最も重要なデバイス要素は「ゲート酸化膜」と呼ばれる厚さ数 nm のシリコン酸化 (SiO<sub>2</sub>)膜である。この SiO<sub>2</sub> 膜の特性は下地の凹凸や汚染、膜質の劣化に極めて敏感で、しば しばゲート電圧で信号電流を制御できない「ゲート破壊」と呼ばれる不良が発生する。図4. 1.1 にゲート破壊の推定構造とトランジスタ特性を示す。ゲート酸化膜に出来た欠陥によりゲー ト電圧がシリコン基板側に直接伝わるため、チャネル部分に反転層が形成されず、ソース・ドレ イン間に電流が流れない。従来、不良解析的にはゲート酸化膜の破壊箇所を貫いて Si 基板 に浸み込んだエッチング液(フッ硝酸系)の「浸み跡」を SEM 観察し、その結果をゲートピンホ ールと称してきた。 **図4.1.2**にその手法とゲートピンホールの SEM 観察結果を示す。「ゲート ピンホール」はこれまで TEM による微細構造の評価が困難であった。それは非晶質のゲート 酸化膜にあいた微小な穴であること、Si 酸化膜と Si 基板、多結晶 Si の材料に囲まれた領域に あるため TEM 像で十分なコントラストが得られないこと、トランジスタのゲート酸化膜上における 位置特定ができないことなどが原因である。超高圧電子顕微鏡を用いた観察例でも Si 基板に 過電流が流れ込んだことによる結晶欠陥や歪コントラストが観察されたのみで、ゲートピンホー ルの実態は観察されていない<sup>(1)</sup>。ここでは300kV級の3DCT-TEMによる詳細観察を試みた<sup>(2)</sup>。 3次元観察手法については第2章2節を参照(3)(4)。

ゲートピンホールによるMOSの破壊 図4.1.1

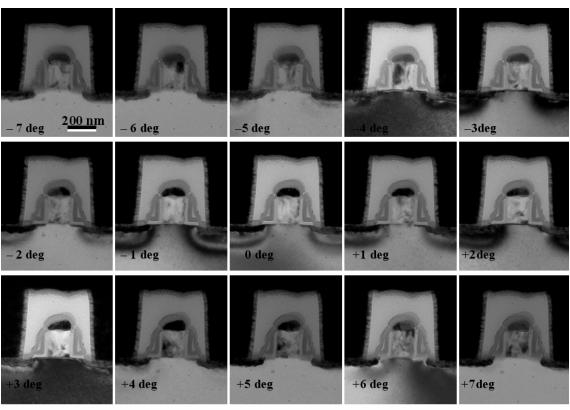

ゲート耐圧不良を起こしたトランジスタを 300nm の薄膜に FIB 加工し、V メッシュに固定したものを試料とした。この薄膜の方線はゲート酸化膜に平行方向と一致させた。この試料を 3 次元 TEM(日立 H-9500SD)によって $-60^\circ$  ~ $+60^\circ$  まで  $1^\circ$  毎に TEM 像を撮影し、3次元像に再構成した。UHVEMと同様、像再構成の位置合わせには 20nm  $\phi$  の金コロイド粒子を用いている。

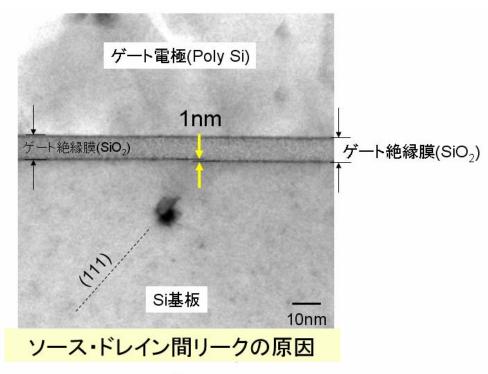

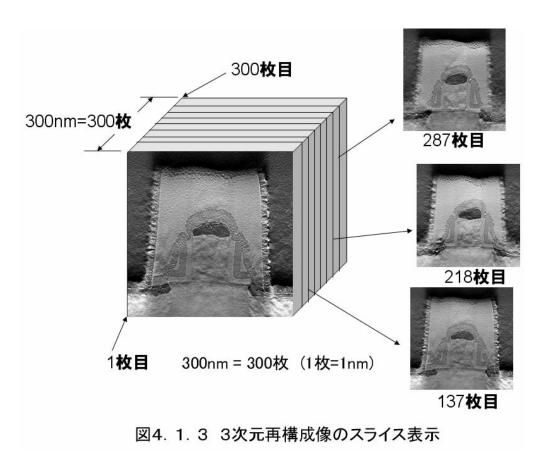

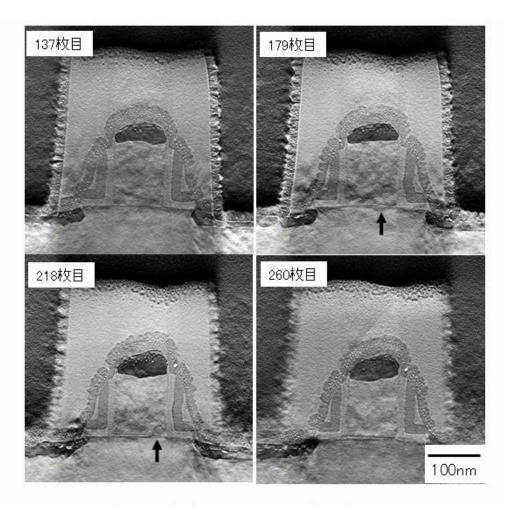

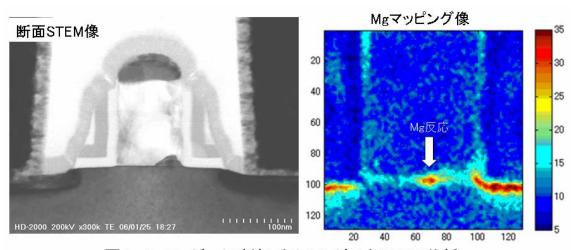

図4.1.3に示すように3次元再構成した画像は断面スライス像としてコンピュータ上にデー タを保持しているため、特定の断面像(断層像)を選んで表示することが出来る。ここでは 300nm の膜厚の MOS トランジスタの試料を 300 枚の断面像として表示する。よって断面像 1 枚あたりの厚さ方向への空間分解能は約1nmで、これは膜厚1nmの試料を非破壊でTEM観 察していることになる。また図4.1.4は試料の傾きによるシリコン基板と多結晶シリコンのゲー ト電極に現れる回折コントラストの違いを示す。 結晶材料の 3 次元観察の場合、回折コントラス トが再構成像に与える影響が懸念されていたが、多数の写真を再構成する過程で回折コント ラストは平均化され、不良解析の実用上、大きな問題とはならなかった。**図4.1.5**に MOS トラ ンジスタの 137、179、218、260 番目の断面を示す。ここで「137 番目」とは試料表面から 137nm 目の断面像で、他の写真も同様である。 試料表面から 137nm 目の写真ではゲート酸化膜と Si 基板界面は平滑であり酸化膜自体にも異常は認められない。ところが 218 番目の断面ではゲ ート酸化膜を貫通してSi 基板からゲート電極に向かって楔(くさび)形のSi 結晶が成長している。 この部分がゲートピンホールとなってゲートリークを起こしていたと推定される。また「楔形の Si 結晶」は 78 枚分の断面像に写っていることより、その大きさは 78nm φ であることが分かる<sup>(5)</sup>。 さ らに不良箇所の「楔形の Si 結晶」の領域を STEM-EDX で分析した結果、図4.1.6に示すよう にマグネシウム(Mg)の特性 X 線(Mg-K α)を検出した。Mg は半導体製造装置の部材に合金元 素として広く使われている。装置から発生した異物による汚染が原因と特定された®。このよう に不良箇所の微視的な3次元的な形態評価と元素分析を組み合わせることによって、不良原 因をより多角的に解析できる。

図4.1.4 角度を変えたときのゲート電極のコントラスト変化

図4. 1. 5 ゲート破壊したトランジスタの断面スライス像 楔形のSi結晶成長領域=87nm Φ

図4. 1. 6 ゲート破壊したトランジスタのEDX分析

### 4.2 MOSトランジスタの不純物元素に起因する不良

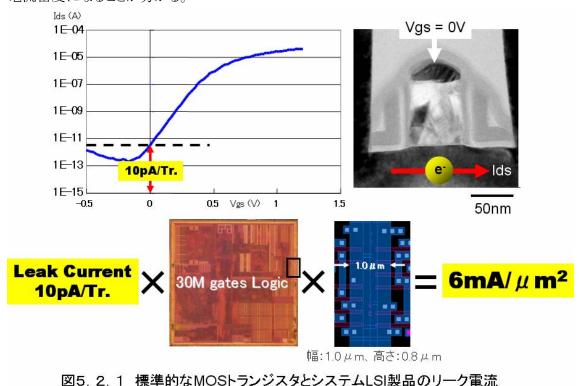

MOSトランジスタの動作不良は前節のゲート酸化膜以外にも、拡散層における不純物元素の 濃度や分布が原因となりうる。しかしながら分析電子顕微鏡の分析感度は 0.1%前後で 1×10<sup>17</sup> 個/cm³ 程度の不純物元素を分析電子顕微鏡的に解析するのは不可能である。しかし不良原因によっては不純物分布そのものが観察できなくとも、不純物の導入工程に関わるデバイスの 微細形状から原因を推定することが出来る。また高濃度な不純物領域であれば通常の STEM-EDX でも評価できる場合もある。本節ではナノ・プローバによる MOS の電流測定と TEMの高分解能観察、及びSTEM-EDXによる元素分析を用いた解析例を示す。ナノ・プローバの詳細は第 2 章 5 節を参照。

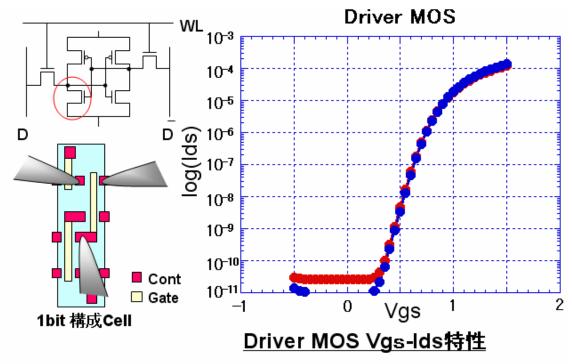

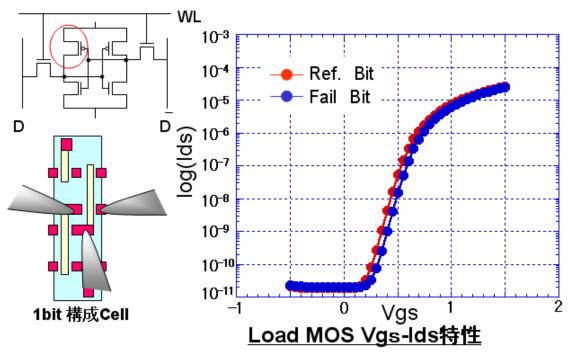

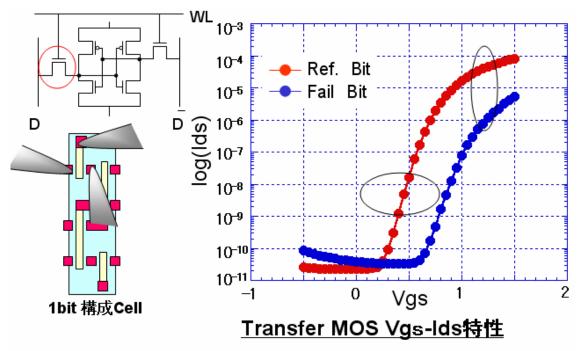

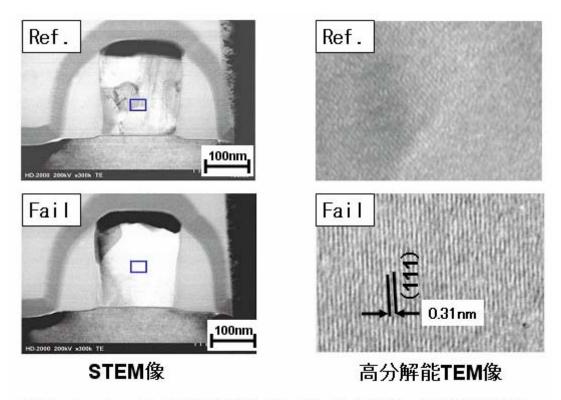

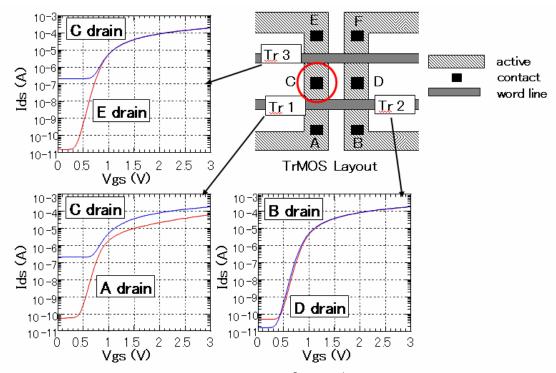

本不良はメモリのシングルビット不良と呼ばれる「1 ビット分が単独で動作しない」現象で、 SRAM のビットを構成する 6 つの MOS トランジスタのいずれかが動作不良となっていることが 推定される。不良現象はメモリテスタと呼ばれる専用のテスタで評価され不良箇所の位置がチ ップ上で特定されるが、該当メモリ部には通常のプローバで測定できる端子がないため、 SRAM を構成する MOS トランジスタのコンタクトホールに直接針当てができるナノ・プローバを 用いた。**図4.2.1**から**図4.2.3**に SRAM のレイアウトとメモリセルを構成するトランジスタをナ ノ・プローバで測定した結果を示す。SRAM にはドライバー、ロード、トランスファーの 3 種類の MOS トランジスタがあるが、この内、トランスファーMOS において顕著な Vth(MOS トランジスタ に電流が流れ始めるゲート電圧)の上昇が確認された。またメモリセル動作電圧の範囲で電流 (Ids)も一桁小さい事を確認した。この原因としては①ゲート酸化膜厚増大、②ゲートの加工寸 法異常、③不純物濃度の異常などが考えられる。この内、①と②は断面 TEM 観察によって容 易に原因を特定できるが、③の場合は低濃度の不純物元素を分析する必要があり、電子顕微 鏡的な解析は困難である。ここでは原因を①または②と推定して、不良箇所のトランジスタと正 常ビットのトランジスタを断面 TEM 観察した。その結果を図4.2.4に示す。不良箇所はゲート 垂直方向の観察よりゲートを構成する多結晶 Si がほぼ単結晶化していること、単結晶化した PolySi の格子像観察結果から Si の最稠密面である(111)面がシリコン基板にほぼ垂直であるこ と、さらにはゲート平行方向からの観察より PolySi 粒界も基板に対してほぼ垂直であることが判 明した。なおゲート酸化膜厚、及びゲート長に差異は確認されなかった。MOS トランジスタの Vth を調整するために、ボロン(B)をゲート電極形成後にインプラしている。この不良原因はゲ ート電極が単結晶化した上に(111)面がシリコン基板に垂直であったためインプラ時に B がチ ャネリングを起こし基板へBが漏れためと推定される。対策としてゲート電極のアニール条件に より結晶粒を微細化したところ不良率が改善された。

図4.2.1 SRAMの不良セルのナノ・プローバ測定結果

図4.2.2 SRAMの不良セルのナノ・プローバ測定結果

図4. 2. 3 SRAMの不良セルのナノ・プローバ測定結果

図4.2.4 SRAMの不良トランジスタの断面TEM観察結果

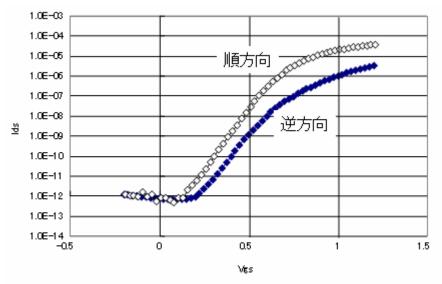

次に電流量が非対称な特性を示す MOSトランジスタの解析結果を示す。MOSトランジスタは 断面形状が左右対称の形状をしているが、その電流特性も本来は対称でなければならない。 しかしながら何らかの原因でソースまたはドレイン側に抵抗が付加されると、ソース→ドレイン 方向の電流とドレイン→ソース方向の電流量が異なってくる。これは MOS の非対称特性と呼 ばれ、信頼性やメモリセル動作の不安定性などの問題が生じる。図4.2.5に非対称特性を示 す MOSトランジスタの評価結果を示す。ゲート電圧(Vgs)=1.2V の時、ソース・ドレイン間電流 (Ids)は順方向の電流が 50 μ A であるのに対して、逆方向では 6 μ A と約一桁低くなっている。 例えばソースに抵抗が付加された場合、ゲート・ソース間にかかる電圧、即ちゲート電圧がこの 抵抗により分配され、チャネルに加わる実効的なゲート電圧が低くなる。このため、見かけのゲート電圧より低い電圧でしか MOS が駆動されないため、ソース・ドレイン間電流が減少してしま う。逆に反対方向に電圧印加する場合のゲート電圧はドレイン・ゲート間の電圧になるため、こ のような現象は起こらない。MOSのソースやドレイン抵抗が高くなる原因としては、

- ① シリサイド形成不良による拡散層表面の抵抗上昇

- ② 上部配線層からのコンタクト抵抗大

- ③ インプラ工程、LDD(Lightly Doped Drain)\*形状起因の不純物導入不足 (\*)MOS トランジスタのゲート電極端部での電界強度緩和のため、ソース・ドレイン拡散層 部分より、低濃度の不純物を導入した領域。

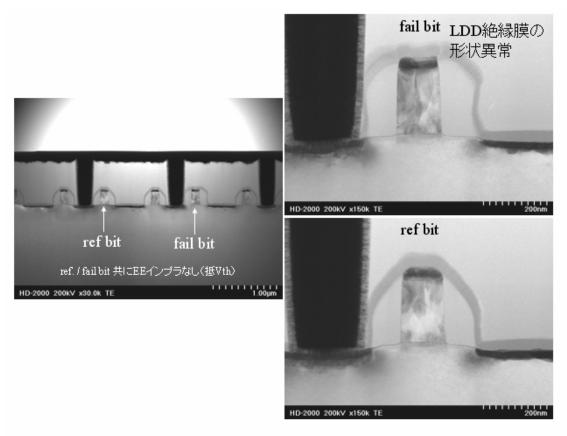

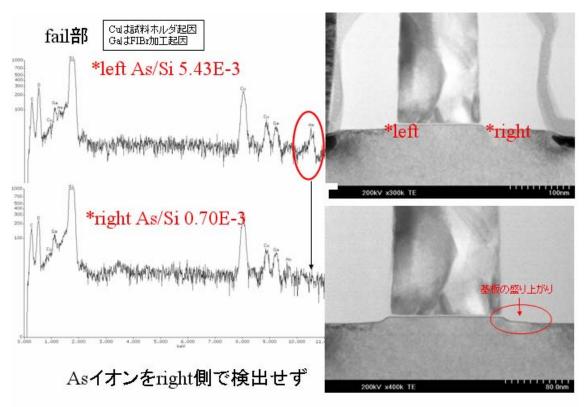

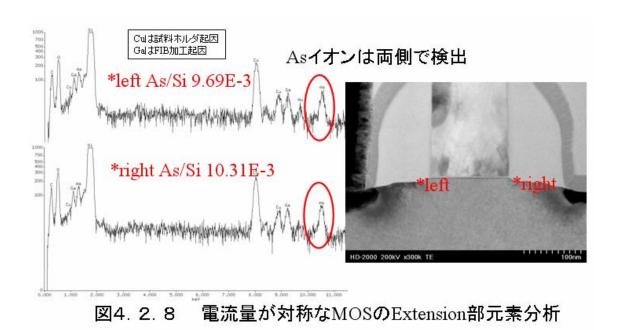

などが予想される。 ①はデバイスの断面 TEM 観察から容易に確認できる。 また②の場合もコン タクトの断面観察に加え、第 5 章で詳述する分析電子顕微鏡等を用いたコンタクト底部の詳細 解析で原因が判明する場合が多い。③の場合は数十~数百 nm の範囲における不純物元素 の分析を必要とし、現状の分析電子顕微鏡では検出感度的に困難な場合が多い。この MOS におけるゲート電圧の非対称性降下は 0.5V 程度と推定され、この高抵抗を生成する原因とし ては上記の予想原因の①と②が仮定される。断面 TEM 観察した結果を**図4.2.6**に示す。こ れよりソース、ドレイン部分及びゲート表面の Co シリサイドの形状・膜厚ともに異常がなく、また コンタクト部にも高抵抗を伺わせる結果は見当たらない。LDD の酸化膜形状に異常が見られ るが、この形は MOS の電流特性には直接関与していない。②が原因とすれば、拡散層の不 純物濃度低下は数桁以上が予想され通常の EDX 分析でも判別が予想された。不良 MOS の Extension 部分とリファレンスの同じ箇所を STEM-EDX で元素分析した結果を**図4.2.7**と**図4.** 2. 8に示す。リファレンスの MOSトランジスタの Extension 部分では明らかなヒ素(As)の EDX ス ペクトルピークが確認できるが、不良 MOSトランジスタの Extension 部分では片側のみ As のス ペクトルが確認できるのみで、もう片側には As のスペクトルが現れていない。 また As が確認さ れなかった拡散層部分はMOSの電流非対称方向とも一致していた。よってMOSのExtension 部分における不純物元素(As)の濃度不足による高抵抗がMOSの電流非対称性の原因である ことが確認された。この不純物元素の導入不足に至った原因は、LDD シリコン酸化膜の形状 異常も非対称的であることを考慮すると、MOS の Extension 部にイオンが導入される時にこの 非対称性が原因となっていることが考えられる。

図4.2.5 電流量が非対称なMOS特性

図4.2.6 電流量が非対称なMOSの外観TEM観察

図4.2.7 電流量が非対称なMOSのExtension部元素分析

#### 4.3 ゲート酸化膜の結合状態

### (1)位置分解型 TEM-EELS の概要

ゲート酸化膜は本章第1節でも述べたように、MOSトランジスタの特性と信頼性を決定付ける最も基本的な構成要素であり、また膜厚も1~数 nm 程度の最もデリケートな膜である。ゲートピンホールのように MOSトランジスタ特性を根本的に損なってしまう不良現象は、破壊箇所の形態的な把握と分析が重要である。一方、信頼性や電気的な特性、または「マージン性の不良」と呼ばれるハード的な不良には至らないまでも、特定の使用条件でデバイスのスペックを割り込む現象などの解明には、膜を構成している元素の結合状態までさかのぼらなければならない。これらの現象を解明する手段として筆者等は「位置分解型 TEM-EELS」を開発し、元素の結合状態を電子顕微鏡的分解能で評価する手段を開発した(詳細は第2章第1節)<sup>(7)</sup>。本節では位置分解型 TEM-EELS を用いたゲート酸化膜、フラッシュメモリのトンネル酸化膜の膜質評価について検討した結果を記す。

### (2)薄膜組成の同定

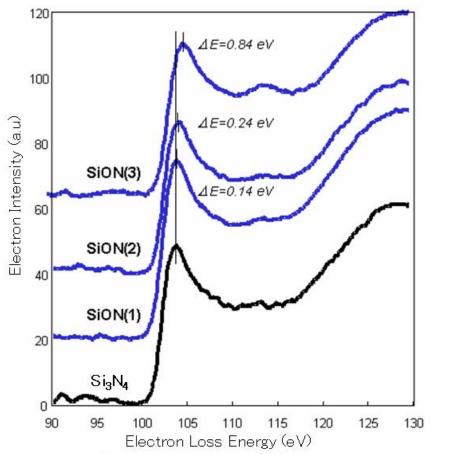

最近の高速画像処理や音声処理技術を支えるのは高速度フラッシュメモリである。多く のフラッシュメモリのゲート絶縁膜にはシリコン酸化膜と窒化膜の積層膜(ONO 膜)が 連続的なプロセスで形成される。図4.3.1はフラッシュメモリのコントロールゲー ト電極とフローティングデート電極の間に形成されている ONO 膜を位置分解型 TEM-EELSで、それぞれの結合状態を評価したものである。各層の EELS スペクトル をみると、Si(poly-Si)、SiO2、SiN、SiO2に特徴的なプロファイルを示している。また  $SiO_2$ や SiN 膜の境界付近ではシリコン酸窒化膜( $SiO_xN_y$ )に近い組成を持っていると考 えられている。さらにゲート絶縁膜には信頼性の観点からも SiON 膜が多く採用されて いるが、製造プロセスによっては、図4.3.2に示すように少しずつ異なるケミカル シフト、即ち異なる組成比を持った膜ができる。フラッシュメモリは記憶単位となるト ランジスタに厚さ数 nm の絶縁膜を介して電子を出し入れしてトランジスタ特性(Vth) を変化させることによって読み書きするもので、このゲート絶縁膜の膜質や組成がメモ リの動作特性や信頼性に大きな影響を及ぼす。従来、薄膜の組成を特定する手段として は、標準試料を用いて校正された XPS(X-ray Photoelectron Spectroscopy)や RBS(Ratherford backscattering Spectroscopy)が一般的であったが、何れも 100  $\mu$  m<sup>2</sup> ~数 mm<sup>2</sup>の試料サイズを必要とし ULSI のデバイス上では計測できなかった<sup>(8)</sup>。位置 分解型 TEM-EELS の高い空間分解能とエネルギー分解能を用いてゲート絶縁膜の組 成同定を試みた。

図4. 3. 1 フラッシュメモリのONO酸化膜

図4.3.2 プロセスによるSiON膜のケミカルシフトの違い

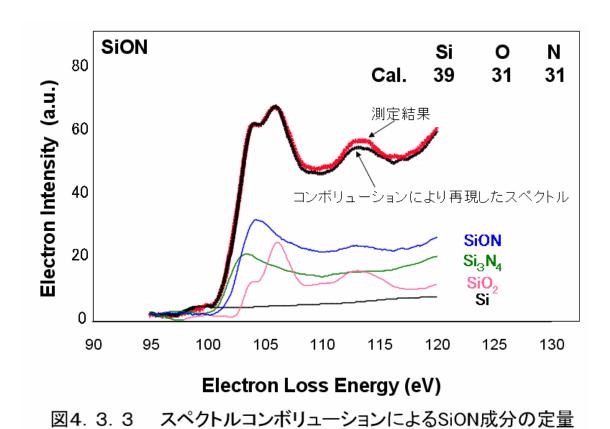

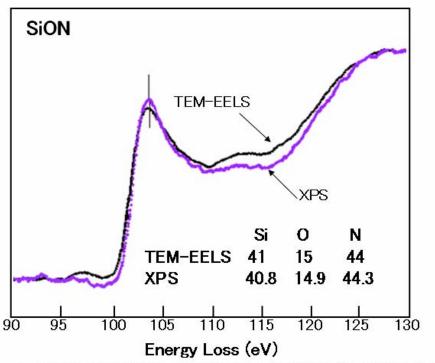

同定方法は以下の通りである。TEM-EELSで予め組成が同定されている薄膜を用いて 基準となるスペクトルを取得しておく。ここでは $\mathbf{Z4.3.3}$ に示す  $\mathbf{Si}$ 、 $\mathbf{SiO}_2$ 、 $\mathbf{SiON}$ 、 Si<sub>3</sub>N<sub>4</sub>膜のスペクトルを用いた。次にこれらの基準スペクトルを一定の割合で加減する スペクトルコンボリューションの手法を用いて、組成が未知の薄膜から取得した EELS スペクトルの形状を再現する。スペクトルコンボリューションは XPS のスペクトル解 析で用いられる手法で、用いた「Casa XPS」と呼ばれるソフトウエアも XPS 用に開発 されたものである。コンボリューションした基準スペクトルの割合から未知の薄膜組成 比を求めることが出来る $^{(9)}$ 。図4.3.3の例ではSiとOとNの比が、約4:3:3 と求められた。次に結合状態の同定手法として一般的な XPS と比較した例を図4.3. 4に示す。TEM-EELS のスペクトルをコンボリューションして求めた組成は、XPS 法 の結果とよく一致している。この例では Si と O と N の比が 3:1:3 になっている。 この SiON 膜は  $Si_3N_4$ の窒素のうちの一つが酸素に置き換わった  $Si_3ON_3$ のような構造 をとっていると考えられる。この手法は純然たる「指紋照合法(finger printing method)」であり、ELNES のプロファイルから詳細な結合状態を評価する手段として は、必ずしも最適とはいえない(10)(11)(12)。しかしながら半導体デバイスサイズにおける 薄膜組成の同定方法としては有効と考えられる。

- 104 -

図4.3.4 TEM-EELS法とXPS法による膜組成同定精度の比較

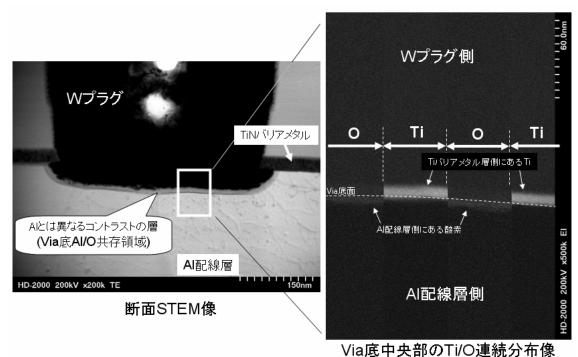

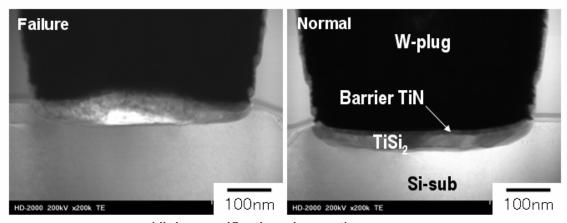

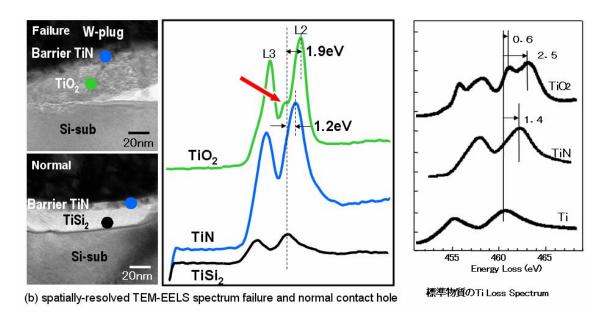

### 4.4 シリサイド材料の結合状態解析

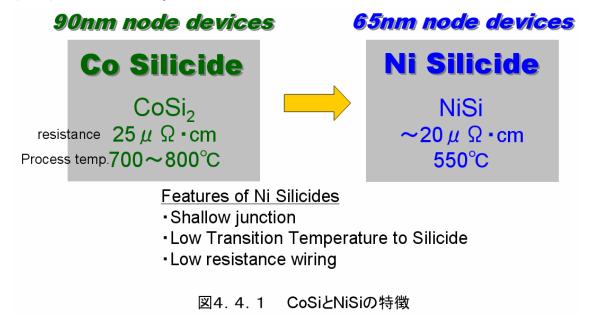

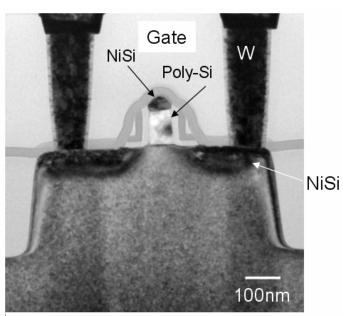

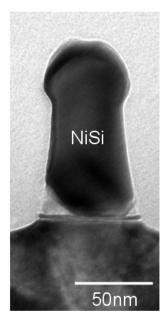

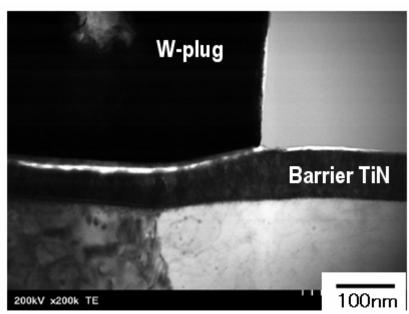

### (1)MOS トランジスタにおけるシリサイド材料

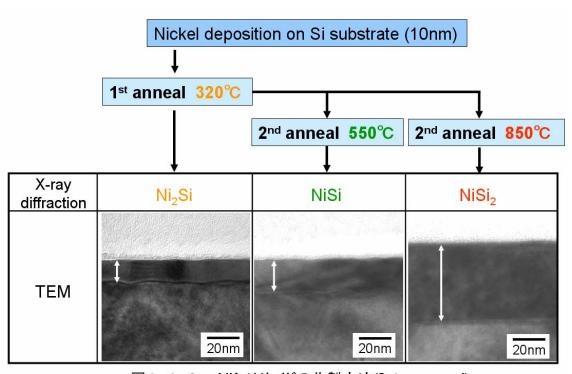

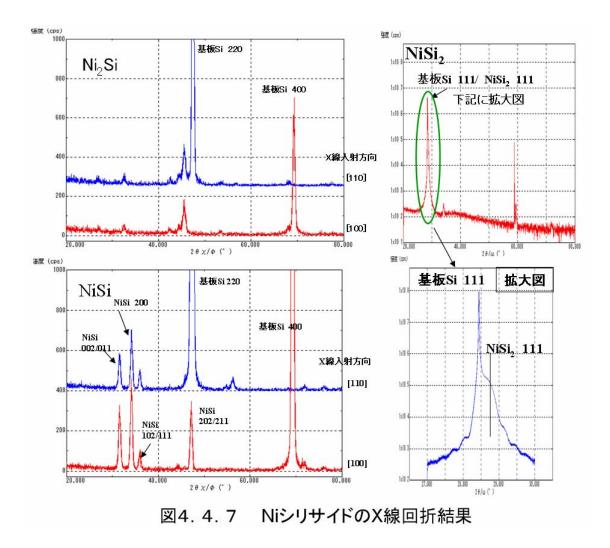

半導体デバイスの微細化に伴い拡散層抵抗の低抵抗化が必須となっている。本章2節でも述 べたように拡散層抵抗の増大は MOSトランジスタの駆動力を低下させ、主として電流で駆動さ れる論理回路やアナログ回路、またメモリの書き込み読み出し回路など、マイクロコンピュータ の性能に大きな影響を及ぼす。また MOS トランジスタのゲート寸法の微細化によってゲートそ のものが持つ細線抵抗も増大している。そこで、これらのデバイス要素の抵抗を下げるために、 配線層から拡散層へのコンタクト部分(実際には MOS の拡散層領域の表面)とゲート電極の表 面をシリコンと遷移金属の金属間化合物(シリサイド)によって被覆するデバイス構造が採用さ れるようになっている<sup>(13)</sup>。 デバイスとしては 500nm プロセスノードのチタンシリサイド(TiSi)に始ま り、200nmプロセスノードのコバルトシリサイド(CoSi)を経て、65nmプロセスノードからはニッケル シリサイド(NiSi)が採用されている<sup>(14)-(17)</sup>。 **図4. 4. 1**に CoSi と NiSi の特徴を示す。 NiSi は CoSi に比べて、低抵抗であるばかりでなくシリサイド化温度も低く、またシリコンとの反応量が少ない ため拡散層の消費が少なく、浅接合でもジャンクションリークを起こすことが少ないとされている (18)-(20)。このように Ni シリサイドは 65nm ノード以下のプロセスの要求仕様に合致しており、**図4.** 4. 2に示すようなデバイス要素に使われている。しかしながら図4. 4. 3に示すように Ni シリサ イドは 3 種類の相を持っている<sup>(15)</sup>。デバイス的には最も低抵抗である Ni モノシリサイド(NiSi)を 形成したいが、プロセス的にはシリサイド化温度だけでなく、薄膜化の影響や周辺の応力、レ イアウト、下地となるシリコン基板やゲートポリシリコンの不純物濃度などによって、所望の相以 外が出現することもある。よって不良解析的には Ni シリサイドの相をデバイス構造の中で評価 する要求が強まっていた。

Ni Fully-Silicided Gate

図4.4.2 Niシリサイドが用いられるデバイス要素

|                    | resistivity<br>(μΩ·cm) | transfer Temp.<br>(℃) | Crystal system |

|--------------------|------------------------|-----------------------|----------------|

| Ni <sub>2</sub> Si | 24                     | 320                   | orthorhombic   |

| NiSi               | 20                     | 550                   | orthorhombic   |

| NiSi <sub>2</sub>  | 35 - 60                | 850                   | cubic          |

図4.4.3 Niシリサイドの3種類の相と性質

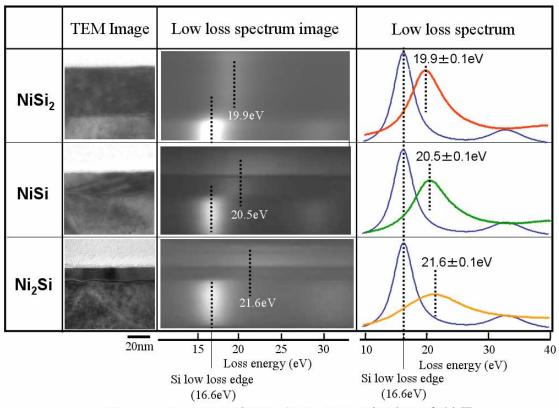

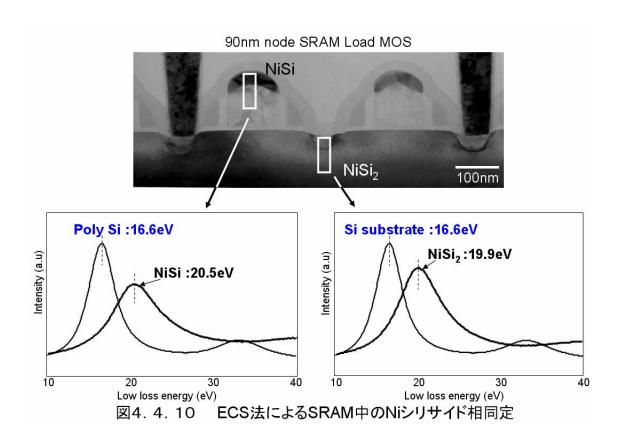

## (2)電子顕微鏡による Ni シリサイドの相同定方法

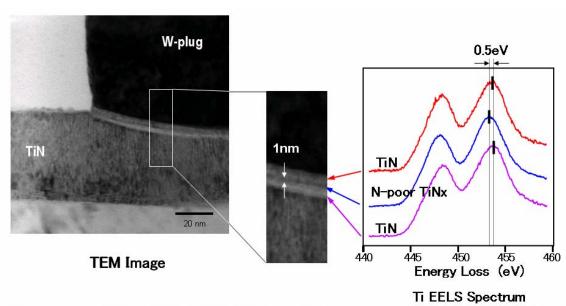

# - Energy Calibration by Standards (ECS)法の開発ー(21)

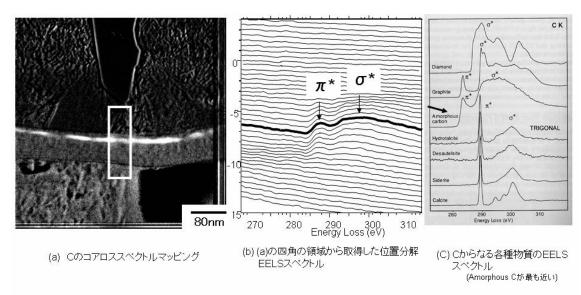

通常の Ni シリサイドの相同定は X 線回折や RBS(Rutherford Back Scattering)、XPS(X-ray Photoelectron Spectroscopy)などで調べられることが多いが、いずれも数~数百  $\mu$  m² 以上の試料サイズを必要とし、デバイスサイズでの相同定は出来なかった。そこで第 2 章第 1 節で述べた位置分解型 TEM-EELS 法 $^{(22)-(26)}$ を用いて電子顕微鏡的な空間分解能で相同定する方法を開発した。

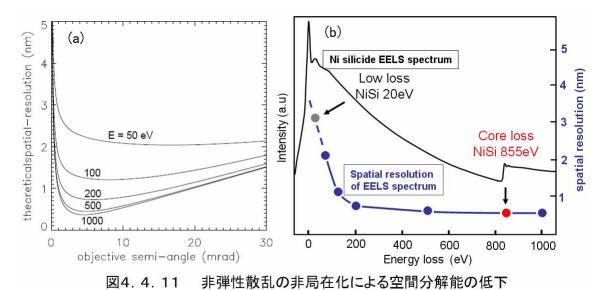

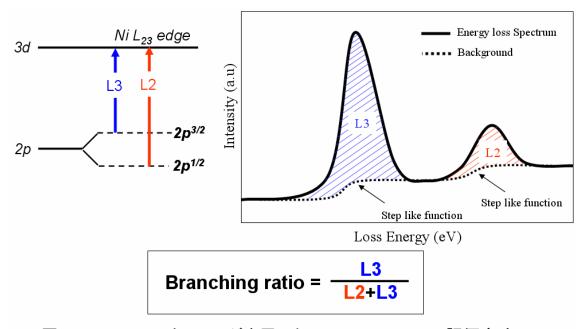

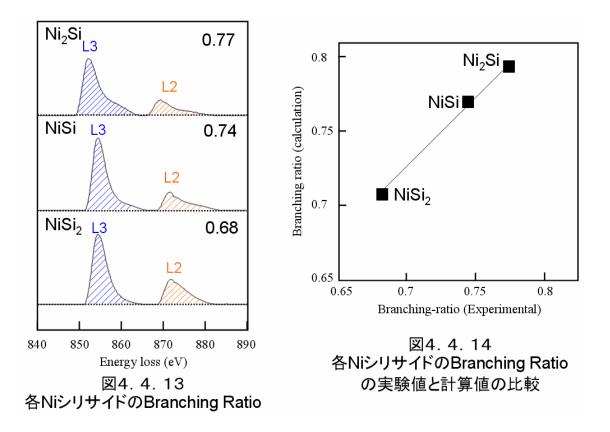

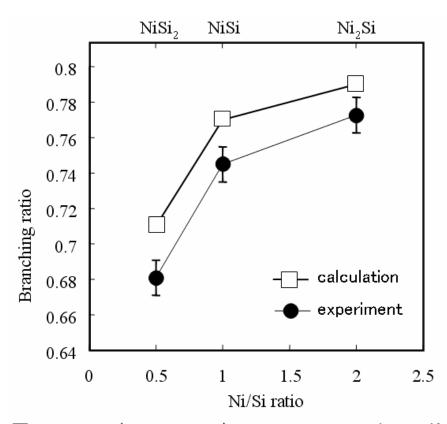

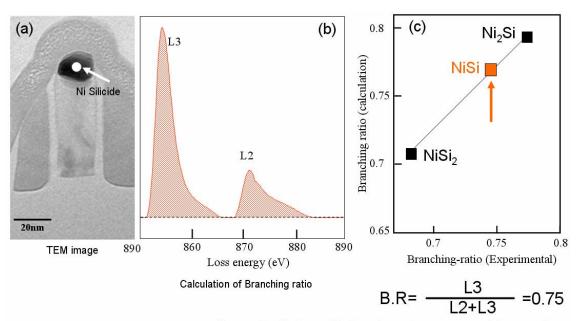

原理的には EELS スペクトルのエッジのケミカルシフトが Ni シリサイドの各相によって異なっていることを利用すれば(27)(28)各相を同定できるが、実験的には下記のような問題点がある(29)。

- ① EELS スペクトル測定上の不安定性

- ②非弾性散乱の非局在化による空間分解能低下の問題

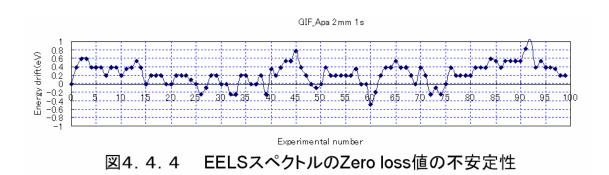

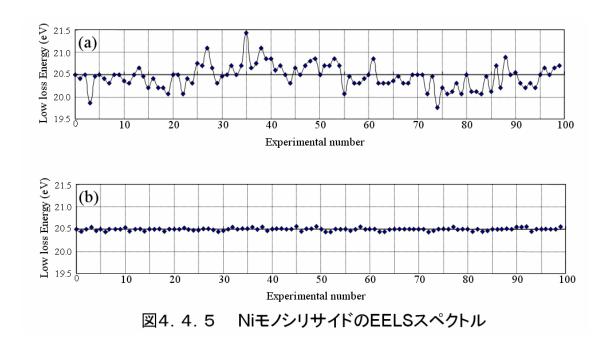

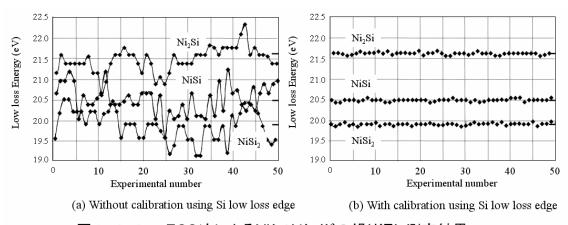

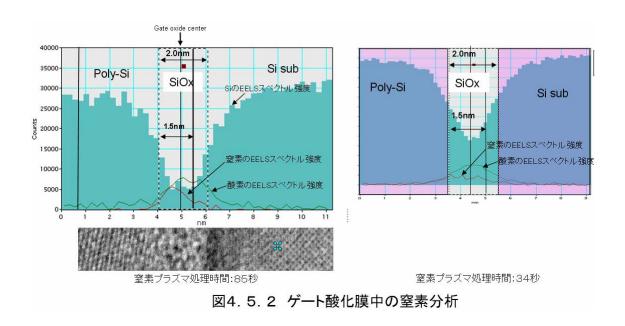

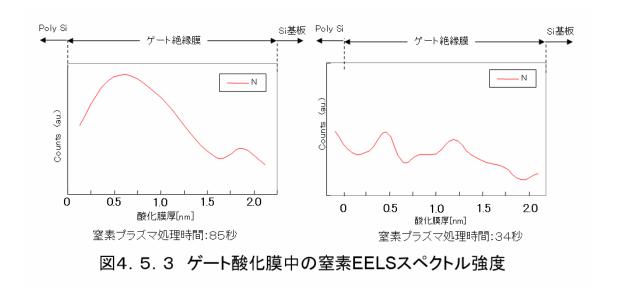

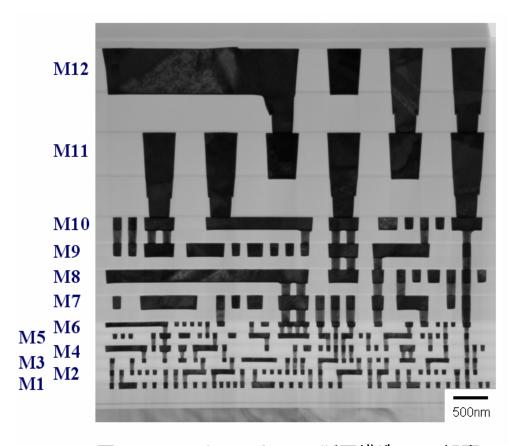

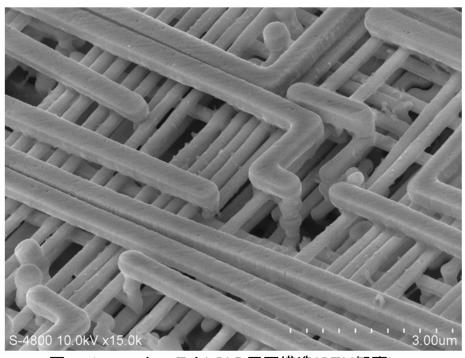

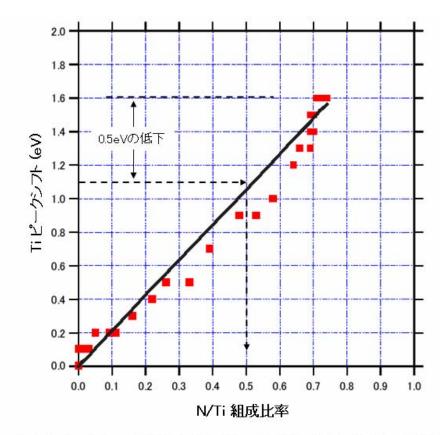

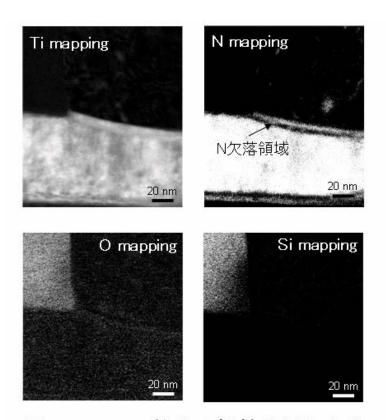

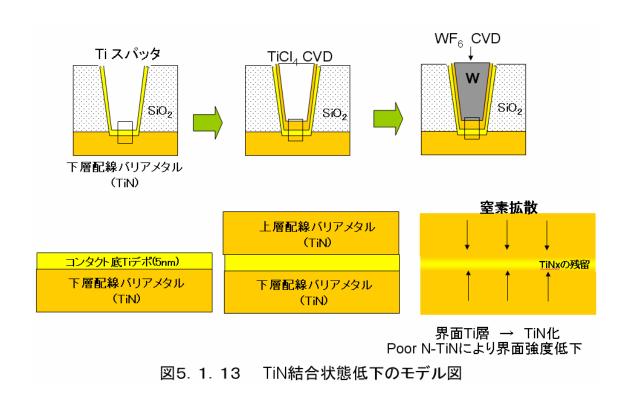

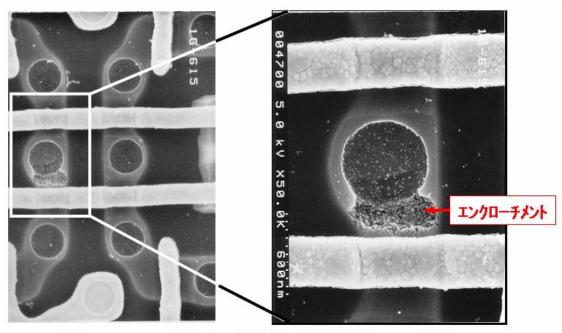

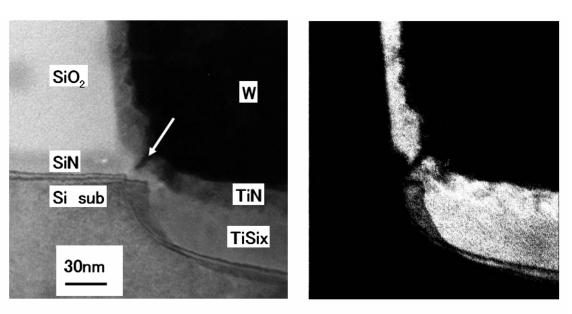

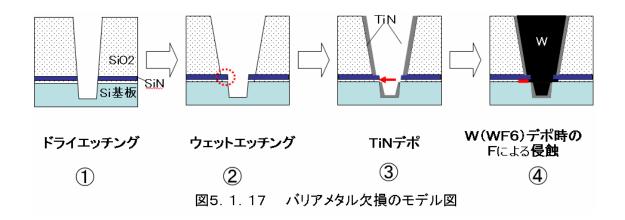

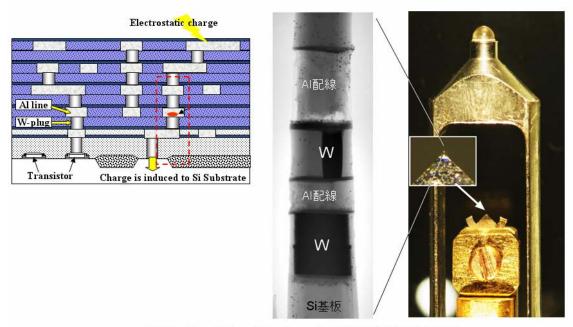

TEM-EELSのスペクトルは機械的振動、加速電圧の不安定性、分光器の精度、外来雑音などにより常に不安定である<sup>(30)</sup>。その様子を Zero loss の不安定性を用いて評価した結果を**図4.4.4**に示す。横軸は測定回数、縦軸は EELS の loss energy である。100 回の測定中に $\pm 1.0 \,\mathrm{eV}$  近いドリフトが観測されている。Zero loss の変動は Ni シリサイドの測定値に直接影響するため、Ni シリサイドの energy loss 値も同様に変動している。この変動をキャリブレーションする手法として位置分解型 TEM-EELS が有効である。**図2.1.13(a)**にも示すように、蛍光板上に設けた視野制限スリットによって被測定物質(ここでは Ni シリサイド)と基準物質(ここではシリコン基板またはポリシリコンの Si)を同時に EELS 分光器に導くことが出来る。 EELS 分光器内の Y 軸が試料位置の Y 方向に一致しているため、シリコン基板と Ni シリサイド層のスペクトルが同時に取得できる。これは Si のスペクトルという物理常数を用いて Ni シリサイドの測定値が校正できることになり、EELS スペクトルの不安定性を解決することが出来る。