| Title        | 0.36 µW/channel capacitively-coupled chopper instrumentation amplifier in EEG recording wearable devices for compressed sensing framework |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Mii, Kenji; Kanemoto, Daisuke; Hirose, Tetsuya                                                                                            |

| Citation     | Japanese Journal of Applied Physics. 2024, 63(3), p. 03SP54                                                                               |

| Version Type | VoR                                                                                                                                       |

| URL          | https://hdl.handle.net/11094/97766                                                                                                        |

| rights       | This article is licensed under a Creative Commons Attribution 4.0 International License.                                                  |

| Note         |                                                                                                                                           |

### Osaka University Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

Osaka University

#### **REGULAR PAPER • OPEN ACCESS**

# 0.36 µW/channel capacitively-coupled chopper instrumentation amplifier in EEG recording wearable devices for compressed sensing framework

To cite this article: Kenji Mii et al 2024 Jpn. J. Appl. Phys. 63 03SP54

View the article online for updates and enhancements.

#### You may also like

- <u>COEVAL INTERMEDIATE-MASS STAR</u> <u>FORMATION IN N4W</u> Zhiwei Chen, Shaobo Zhang, Miaomiao Zhang et al.

- <u>Ultra-low power signal conditioning system</u> for effective biopotential signal recording

Diksha Thakur, Kulbhushan Sharma,

Sonal Kapila et al.

- The NANOGrav 12.5 yr Data Set: A Computationally Efficient Eccentric Binary Search Pipeline and Constraints on an Eccentric Supermassive Binary Candidate in 3C 66B Cabriella Agazia, Zayan Azzumanian

Gabriella Agazie, Zaven Arzoumanian, Paul T. Baker et al.

https://doi.org/10.35848/1347-4065/ad264f

# $0.36\,\mu\text{W/channel}$ capacitively-coupled chopper instrumentation amplifier in EEG recording wearable devices for compressed sensing framework

Kenji Mii, Daisuke Kanemoto\*, and Tetsuya Hirose

Graduate School of Engineering, Osaka University, 2-1, Yamadaoka, Suita 565-0871, Japan

\*E-mail: dkanemoto@eei.eng.osaka-u.ac.jp

Received October 18, 2023; revised January 1, 2024; accepted February 4, 2024; published online February 23, 2024

We evaluated the effectiveness of a low-current-consumption amplifier for a compressed-sensing (CS) framework in wearable electroencephalography (EEG) recording devices. The amplifier uses a capacitively coupled chopper instrumentation amplifier (CCIA) architecture which is often used for low-noise amplifier (LNA) to achieve low consumption and low-noise characteristics. According to measurements of the designed CCIA, the power consumption was 0.36  $\mu$ W/channel, and the input referred noise (IRN) was 4.47  $\mu$ Vrms. The measured IRN and simulations were used to confirm the effect of CCIA noise on the CS-based EEG measurement framework. The difference in the normalized mean squared error at CR = 4 to the uncompressed conditions could be reduced to 0.008. The findings show that even with the LNA specialized for low power consumption, a slight signal degradation is observed when the compression ratio is increased up to 4 in the CS framework by utilizing the sparsity of EEG in the frequency domain. © 2024 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

#### 1. Introduction

In recent years, the application of electroencephalography (EEG) has not been limited to healthcare, and new technologies such as brain-computer interfaces have been developed. Wireless EEG recording devices have also attracted attention, and these devices must be wearable and lightweight to reduce the user burden and regulate user activities. However, extending the operating time of wearable devices typically involves increasing their battery size and weight. Therefore, research has recently been undertaken to reduce the power consumption of wearable devices via compressed sensing (CS)<sup>1)</sup> with the aim of reducing the amount of data to be transmitted. For example, several reports have been made on integrated circuit implementations and low-power dissipation measurements for electrocardiographs, electromyographs, and ultrasound echo devices.<sup>2-4)</sup> Additionally, research is underway to incorporate CS into EEG. For example, CS is vulnerable to artifact contamination.<sup>5)</sup> However, in recent years, an EEG measurement framework using CS that is resistant to blink artifact contamination<sup>6–8)</sup> was proposed, and its practical applicability has been enhanced. Examples are also present on low-consumption EEG measurement frameworks running on thermoelectric generation that have been implemented and confirmed to consume less power as a system.<sup>9)</sup> Moreover, research on integrated circuits for wireless EEG recording devices is ongoing. 10)

Capacitively coupled amplifiers <sup>11–13)</sup> with a high input impedance are used in instrumentation amplifiers for EEG measurements because of their connection electrodes. <sup>14)</sup> The capacitively coupled chopper instrumentation amplifier (CCIA) architecture, which adds a chopping technique to the above configuration, has been extensively used as a lownoise amplifier (LNA) for EEG measurement. <sup>15–23)</sup> In general, a tradeoff is present between the input referred noise (IRN) and the power consumption of an LNA. Research has been conducted to optimize this tradeoff, and the application of CS is considered one of the solutions. For example, in CS, the EEG signal is assumed to be sparse when mapped on a certain basis. Various bases are known<sup>24–27)</sup>; for example, in the case of frequency-domain-based transforms, <sup>28)</sup> flicker noise, which has strong frequency dependence, reportedly

has significant effect on the reconstruction accuracy, while thermal noise, which has power over a wide bandwidth, has a weak effect on the transform.<sup>29)</sup> Because the EEG signal is distributed mainly in the frequency band below 100 Hz, 30) reducing flicker noise is essential for improving the signal-tonoise ratio. In addition, the low power consumption of the LNA is important for the realization of wearable EEG recording devices. Considering a system using bluetooth low energy (BLE), the power consumption of the RF circuit increases only during communication, 31) and the majority of the current consumption is accounted for by the RF circuit. 32,33) Outside of communication, most of the power consumption is determined by the circuits contributing to sensing. The power consumption of the LNA, which is in constant operation, is one of the circuits that consume power on the sensing circuit. In previous studies, the power consumption of the LNA comprised a large proportion of the total system power consumption, including the analog front end. 34-36) Therefore, a lower power consumption of the LNA leads to smaller and lighter batteries, and thus, lowconsumption AFE ICs and AFE ICs with RF circuits have been developed, although LNAs still account for a large proportion of power consumption in some cases. 37,38) When considering 10-to-20-channel EEG-recording devices, <sup>39)</sup> we set a power consumption target of 0.5  $\mu$ W for one LNA channel to maintain the total power consumption of LNAs below the majority of the above IC<sup>38)</sup> even at a large number of LNAs. As described above, in the CS framework, the LNA characteristic that critically affects signal compression and reconstruction is not thermal noise but flicker noise, which mitigates the tradeoff between thermal noise and power consumption in the characteristics of LNAs. In this study, we design an LNA that is specialized for flicker noise suppression and thermal noise with some magnitude using the CCIA architecture. We aim to demonstrate that signal degradation can be mitigated within a CS framework, even when employing a low-power LNA with significant noise in the system.

In this study, we extend the research presented in our international conference paper.<sup>40)</sup> We present the measurement results for the designed LNA and the results of signal processing using CS framework, which utilizes random

© 2024 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

03SP54-1

undersampling<sup>41)</sup> based on the measured LNA data. The remainder of this paper is organized as follows. Section 2 presents the circuit configuration and features of the designed CCIA. Section 3 presents the CCIA measurement results. Section 4 presents the simulation results for signal processing using the proposed framework based on the measurement results in Sect. 3. Section 5 concludes the paper.

#### 2. Designed CCIA

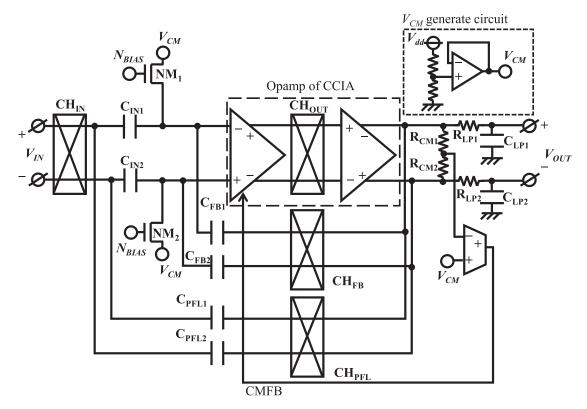

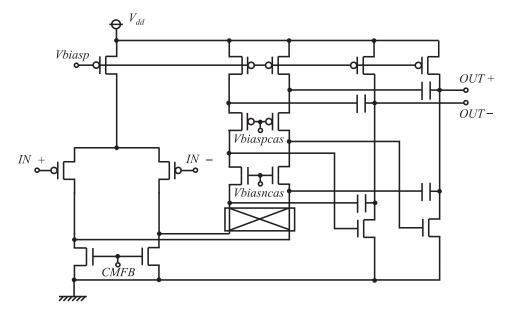

As described in the Introduction, when reconstructing using frequency domain sparsity in the CS framework, flicker noise is susceptible to reconstruction while thermal noise is not. Considering this characteristic, the use of a low-power LNA with suppressed flicker noise and high thermal noise can contribute to reducing the overall AFE power consumption while minimizing signal degradation. This section describes the design of an LNA to realize the aforementioned system. Figure 1 illustrates the CCIA designed for this study. A 180  $\mu$ m CMOS process was used for the design. Because the impedance of the electrode is high in EEG measurements, 42) a capacitor for positive feedback loop was employed to increase the input impedance. 43) Although the signal characteristic of the input node of the CCIA operational amplifier is AC, it requires an appropriate DC bias to ensure proper amplification. <sup>44)</sup> In Fig. 1, as in previous studies, <sup>43,44)</sup> a high resistance is generated and used with NM<sub>1</sub> and NM<sub>2</sub> to ensure the stability of the capacitively coupled nodes. The  $N_{\rm BIAS}$  node is supplied from outside the chip. Figure 2 shows the circuit diagram of the amplifier used in Fig. 1. As in a previous study, a folded cascode is used to achieve lowsupply voltage operation and high gain. 16) Indirect phase compensation technology is used for phase compensation to generate zeros at high frequencies, even when the node impedance increases. 45,46) In addition, a common-mode feedback (CMFB) circuit based on the output voltage of the CCIA is used, and the signal is amplified around  $V_{\rm CM}$ , which is half of  $V_{\rm DD}$ . The CCIA operates with  $V_{\rm DD}=1.8~\rm V$ .

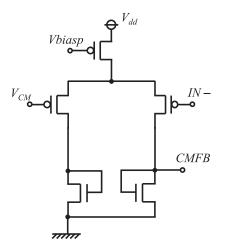

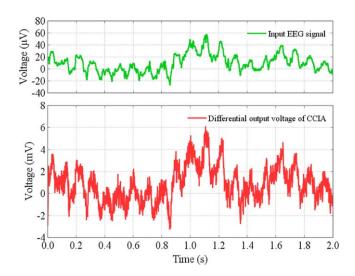

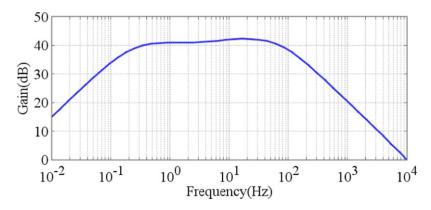

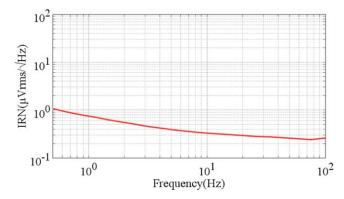

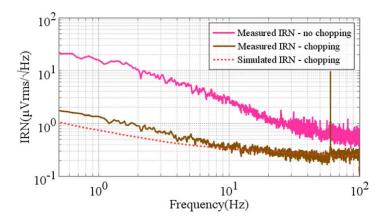

$R_{\rm CM1}$  and  $R_{\rm CM2}$  are used for the CMFB and feedback the center of the output voltage. The operational transconductance amplifier (OTA) used for CMFB is shown in Fig. 3. The circuit configuration of the CMFB circuit, including  $R_{\text{CM1}}$  and  $R_{\text{CM2}}$ , is general. <sup>47,48)</sup> In addition to the 4-channel CCIA,  $V_{CM}$  generate circuit and CMFB circuits were designed in this study, and the simulation results indicate that the current consumption of the entire chip is 828 nA and the current consumption per channel is 207 nA. This result implies a power consumption of  $0.373 \,\mu\text{W}$  per channel, a performance that meets the target indicated above. The chopping frequency was set at 5 kHz because of the narrow bandwidth of the amplifier resulting from its low power consumption. To reduce the spike voltage due to chopping, low pass filters (LPFs) consisting of  $R_{LPF1}$ ,  $R_{LPF2}$ ,  $C_{LPF1}$ , and  $C_{\rm LPF2}$  are implemented in the chip. The LPFs are first-order filters with a cutoff frequency of 24.5 kHz and are designed with a high cutoff frequency to allow fine tuning with offchip anti-aliasing filters. Figure 4 shows the AC simulation results for the CCIA without chopping. Figure 4 shows that the gain from 0.5 to 100 Hz is greater than 37 dB, indicating that sufficient amplification is achieved considering the frequency of the EEG signal.<sup>30)</sup> Figure 5 shows the input EEG signal and output differential voltage waveform of the CCIA during chopping. The amplification ratio is identical to that in Fig. 4, indicating that the amplitude of the EEG signal, which was on the  $\mu V$  order, is amplified to the mV order as expected. Figure 6 shows the IRN spectrum of the CCIA during chopping. The maximum value at frequencies above  $0.5 \,\mathrm{Hz}$  is  $1.04 \,\mu\mathrm{Vrms}/\sqrt{\mathrm{Hz}}$ . The integrated value of the input equivalent noise calculated from Fig. 6 is  $2.9 \mu Vrms$ .

Fig. 1. Configuration of designed CCIA.

Fig. 2. Schematic of the operational amplifier of the CCIA.

Fig. 3. Schematic of the OTA of CMFB.

**Fig. 5.** Simulated input EEG signal and differential output voltage of the CCIA.

#### 3. Measurement results for designed CCIA

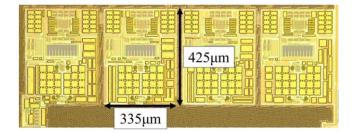

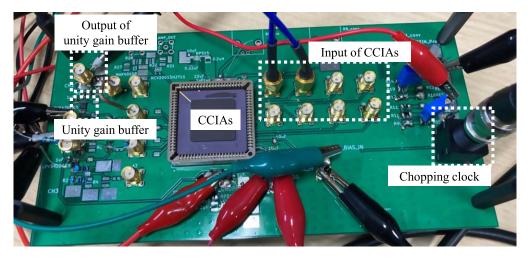

Figure 7 shows a photograph of the fabricated chip. The area of each CCIA channel was 0.142 mm<sup>2</sup>. Figure 8 shows a photograph of the printed circuit board (PCB) used for the measurements. The PCB was a general two-layer board, and an 84-PLCC was used for the chip package. Figure 9 shows

the configuration of the measurement circuit, and Table I presents the conditions and equipment used for the measurement. The total measured quiescent current of the chip was 800 nA, which was approximately equal to that in the simulation, and the current consumption per channel was

Fig. 4. Simulated gain frequency characteristic of the CCIA in the no-chopping state.

Fig. 6. Simulated noise spectral density of the designed CCIA.

Fig. 7. Chip microphotograph of each CCIA.

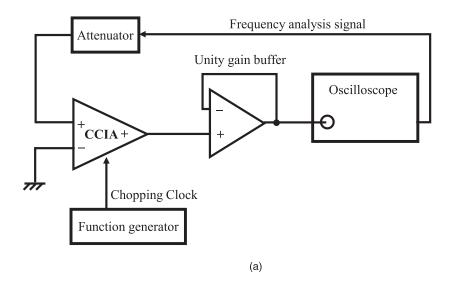

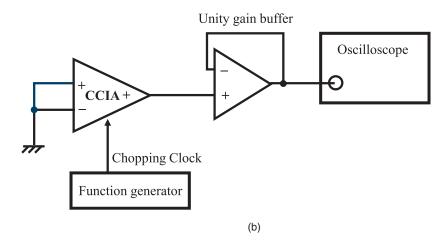

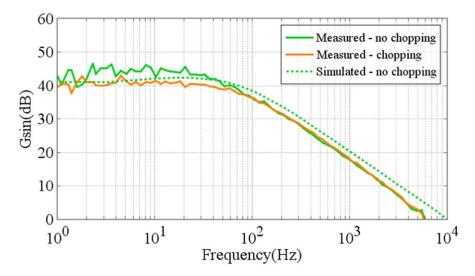

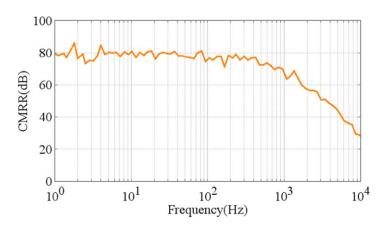

200 nA. This result implies a power consumption of 0.36  $\mu W$ per channel, achieving the target value, which agrees with the simulation result. Because the designed CCIA had low quiescent current, connecting the measurement probes directly to the output pins was impossible; therefore, measurements were performed using LPV542 (Texas Instruments) as a unity gain buffer. The LPV542 had sufficiently low noise and an adequately high cutoff frequency for the designed CCIA; therefore, it did not affect the measurement. In addition, as shown in Fig. 9(a), the oscilloscope output signal was input to the CCIA via an attenuator to prevent clipping of the CCIA output voltage in the gain frequency response measurement. Figure 9(b) shows circuit configuration for measuring the noise spectral density. Figure 10 shows the measured gain frequency response, which match the simulation results, confirming that amplification is possible in the EEG frequency bands. Figure 11 shows the common mode rejection ratio (CMRR) measurements during chopping. Figure 11 shows that the CMRR remains at 80 dB up to 100 Hz, which is sufficient because it is above the 60 dB target set in a previous study.<sup>34)</sup> Figure 12 presents the IRN measurement results; the peak at 60 Hz is due to a hum in the power supply and is not due to chip characteristics. As shown, the IRN was significantly lower during chopping compared with the condition without chopping. The results obtained during chopping were generally similar to those of the simulation, with a maximum IRN of 1.78  $\mu$ Vrms/ $\sqrt{\text{Hz}}$ 0.5 Hz. The integrated IRN during chopping, which was calculated from the measurements presented in Fig. 12, is 4.47  $\mu$ Vrms. In the next section, according to the measurement results, we confirm the effect of LNA noise on EEG signal reconstruction by applying the designed CCIA to the CS signal-processing framework with random undersam-

## 4. Evaluation results for proposed framework with designed CCIA

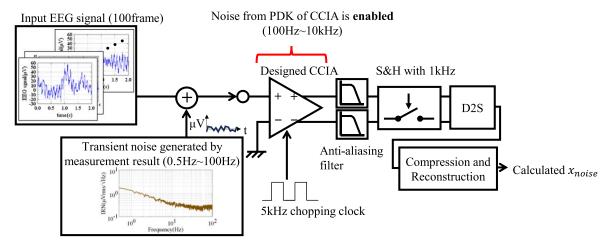

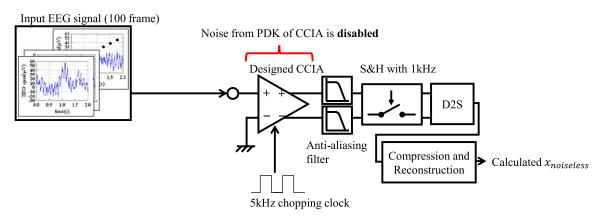

In this section, we confirm the implementation of the designed CCIA via a simulation of the CS framework based on the IRN measurement results obtained in the previous section. To confirm the influence of CCIA noise on the reconstruction of EEG signals, a comparison of the LNA noise with a noise-free ideal state is desirable. In this study, the measurement results were reflected in the simulation and compared with ideal conditions. Figure 13 shows the signal processing performed in this study. As shown in Fig. 13(a), the hum caused by the 60 Hz power supply was removed from the measured IRN shown in Fig. 12 and input to the noise-source model. This converted the IRN resulting from the AC measurement into a transient noise waveform that was overlaid on the input of the CCIA. For noise in the frequency band below 100 Hz, which is the critical frequency band of the EEG, the IRN measurement results were used in the simulation as described above. For noise at frequencies above 100 Hz, where the CCIA gain decreased, the simulator generated flicker noise and thermal noise from 100 Hz to 10 kHz based on the process design kit information. Figure 13(b) shows the ideal state in which no noise was generated at all, which was used for reference. In the cases of both Figs. 13(a) and 13(b), the output voltage of the CCIA

Fig. 8. Part of the PCB used for the measurement.

Fig. 9. Circuit configuration for measurement of the designed CCIA. (a) Circuit configuration for measuring the gain frequency characteristics. (b) Circuit configuration for measuring the noise spectral density.

Table I. Measurement parameters and components used.

| Parameters and components                              | Value and model |  |

|--------------------------------------------------------|-----------------|--|

| $V_{ m dd}$                                            | 1.8 V           |  |

| Total chip $I_{\rm O}$                                 | 800 nA          |  |

| Chopping frequency                                     | 5 kHz           |  |

| Attenuator                                             | 8495B           |  |

| Function generator                                     | SG-4115         |  |

| Oscilloscope with frequency response analysis function | MSO44           |  |

| Unity gain buffer                                      | LPV542          |  |

was input to an anti-aliasing filter with a cutoff frequency of 0.54 kHz; then, the signal was sampled at 1 kHz. After sampling, it was converted into a single-phase voltage using a differential-to-single circuit. The single-phase signal was used as the input signal for the CS compression and reconstruction algorithm in the simulations. The amplified signal was compressed via random undersampling. In this evaluation, a block-sparse Bayesian learning algorithm was used for the signal reconstruction. In addition, a discrete cosine transfer basis was used for frequency-domain sparse representation in this study.  $x_{\text{noiseless}}$  denotes the result obtained without considering noise in the compression and reconstruction of the EEG signal during the CS process, and  $x_{\text{noise}}$  denotes the result obtained with consideration of noise.

The relationship between  $x_{\text{noiseless}}$  and  $x_{\text{noise}}$  was evaluated using the normalized mean squared error (NMSE<sub>comp</sub>) as follows:

$$NMSE_{comp} = \frac{||x_{noiseless} - x_{noise}||_2^2}{||x_{noiseless}||_2^2}$$

(1)

Using NMSE<sub>comp</sub> for the results obtained with different compression ratio (CR), the effects of noise and compression can be examined simultaneously. CR can be expressed by the following equation, where N and M represent the numbers of sample points before and after compression, respectively.

$$CR = \frac{N}{M}.$$

(2)

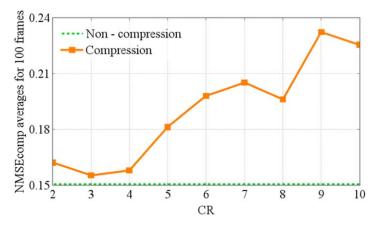

A total of 100 frames of EEG signals, such as the waveform shown in Fig. 5, were processed, with 1.5 s as one frame. Figure 14 shows the average NMSE $_{\rm comp}$  for 100 frames. The uncompressed NMSE $_{\rm comp}$  was 0.15, which is reasonable considering previous studies. <sup>28,39)</sup> Although some fluctuations were present in the reconstruction due to reconstruction errors, the results in Fig. 14 indicate that for CR = 4, NMSE $_{\rm comp}$  was 0.158, which was almost the same as that in the uncompressed case. This indicates that the CRs

Fig. 10. Measured gain frequency characteristics of the CCIA.

Fig. 11. Measured CMRR characteristics of the CCIA in the chopping state.

Fig. 12. Measured noise spectral density of the designed CCIA.

from 2 to 4 were reconstructed to the same quality as the uncompressed results, regardless of the presence or absence of noise from the CCIA. This suggests that the proposed CCIA, which was designed with priority for flicker noise reduction and low power consumption, can be used even with CR = 4 in the proposed framework. In this case,  $NMSE_{comp}$  increases with CR larger than 5, but  $NMSE_{comp}$  generally decreases as CR increases in CS because less information is used for reconstructing. The optimized CR used for CS depends on the type of reconstruction algorithm that is used. In this case, when the algorithm shown above is used, the

degradation of  $NMSE_{comp}$  due to compression is suppressed up to CR = 4.

Table II compares the CCIA designed in this study with previous studies on LNAs for similar applications. Table II shows that the CCIA designed in this study has lower power consumption than the LNAs in previous studies. Table II also shows that the NEF of the CCIA designed in this study is not notably low. Table II and the results of Fig. 14 verify our assertion that the CS framework can reduce signal degradation even when employing a low-power LNA with significant thermal noise in the system. Therefore, the CS framework

#### (a) Settings for calculating $x_{\text{noise}}$ .

#### (b) Settings for calculating $x_{\text{noiseless}}$ .

Fig. 13. Signal processing performed in this study. (a) Settings for calculating  $x_{\text{noise}}$ . (b) Settings for calculating  $x_{\text{noiseless}}$ .

**Fig. 14.** NMSE<sub>comp</sub> calculation results.

can achieve a smaller battery size for wireless EEG recorders due to the availability of LNAs with low power consumption.

#### 5. Conclusions

We designed a CCIA specialized for low-power consumption and measured its characteristics. Using the IRN measurement results for the simulation, we employed the normalized mean squared error to evaluate the reconstruction effect of the noise generated by the CCIA in a CS-based EEG measurement framework. The measurement results indicated that the power consumption was low which is  $0.36\,\mu\mathrm{W}$  per channel, and the IRN was  $4.47\,\mu\mathrm{Vrms}$ . In simulations using the measured IRNs, the normalized mean squared error was computed for 100 EEG frames, and the result obtained at  $\mathrm{CR}=4$  and the uncompressed result were almost equal. This finding proves that the degradation that occurs during signal compression and reconstruction in the CS framework can be suppressed while using an LNA specialized for flicker noise suppression and low power consumption. Although the NEF of the designed CCIA is not significantly low, the simulation results

**Table II.** Performance comparison of the designed LNA and previously reported LNAs.

|                                | 49       | 50      | 51      | This<br>work |

|--------------------------------|----------|---------|---------|--------------|

| Application                    | EEG      | EEG     | ECG/    | EEG          |

|                                |          |         | EEG     |              |

| $I_{\rm Q}$ ( $\mu$ A/channel) | 2.3      | 0.57    | 7.06    | 0.2          |

| $V_{\rm dd}$ (V)               | 1        | 1.5     | 1.8     | 1.8          |

| Power consumption              | 2.3      | 0.855   | 12.7    | 0.36         |

| (µW/channel)                   |          |         |         |              |

| Gain (dB)                      | 55       | 47.6    | 40      | 40           |

| CMRR (dB)                      | 120-95   | 105.6   | 120     | 80           |

| Bandwidth (Hz)                 | 1100     | 500     | 170     | 100          |

| Input referred noise           | 2.18     | 1.22    | 3.8     | 4.47         |

| $(\mu Vrms)$                   | (0.1 -   | (0.5-   | (0.45-  | (0.5-        |

|                                | 1.1 kHz) | 100 Hz) | 100 Hz) | 100 Hz)      |

| NEF                            | 3.8      | 2.91    | 39      | 7.69         |

| Chip area of LNA               | _        | 0.065   | 0.074   | 0.142        |

| $(mm^2)$                       |          |         |         |              |

prove that compression may be achieved in the CS framework by using frequency domain sparsity, and the developed wearable EEG recording devices can operate for a long time by reducing power consumption and communication data volume during EEG sensing.

#### **Acknowledgments**

This work was supported by JSPS KAKENHI Grant No. JP21H03410 and JP23K18463. This work was supported by JKA and its promotion funds from AUTO RACE.

- D. Donoho, "Compressed sensing," IEEE Trans. Inf. Theory 52, 1289 (2006).

- F. Pareschi, P. Albertini, G. Frattini, M. Mangia, R. Rovatti, and G. Setti, "Hardware-algorithms Co-design and implementation of an analog-toinformation converter for biosignals based on compressed sensing," IEEE Trans. Biomed. Circuits Syst. 10, 149 (2016).

- T. S. Chen, H. C. Kuo, and A. Y. Wu, "A 232-to-1996KS/s robust compressive-sensing reconstruction engine for real-time physiological signals monitoring," 2018 IEEE Int. Solid - State Circuits Conf.—(ISSCC), Febr., 2018, 10.1109/ISSCC.2018.8310266.

- D. Kanemoto, J. Spaulding, and B. Murmann, "Single-chip mixer-based subarray beamformer for sub-Nyquist sampling in ultrasound imaging," Jpn. J. Appl. Phys. 60, SBBL08 (2021).

- X. Zou, L. Feng, and H. Sun, "Robust compressive sensing of multichannel EEG signals in the presence of impulsive noise," Inf. Sci. 429, 120 (2018).

- D. Kanemoto, S. Katsumata, M. Aihara, and M. Ohki, "Compressed sensing framework applying independent component analysis after undersampling for reconstructing electroencephalogram signals," IEICE Trans. Fundam. Electron. Commun. Comput Sci. E103-A, 1647 (2020).

- S. Katsumata, D. Kanemoto, and M. Ohki, "Applying outlier detection and independent component analysis for compressed sensing EEG measurement framework," 2019 IEEE Biomedical Circuits and Systems Conf. (BioCAS) 2019, 10.1109/BIOCAS.2019.8919117.

- D. Kanemoto, S. Katsumata, M. Aihara, and M. Ohki, "Framework of applying independent component analysis after compressed sensing for electroencephalogram signals," 2018 IEEE Biomedical Circuits and Systems Conf. (BioCAS), 2018, 10.1109/BIOCAS.2018.8584829.

- T. Miyata, D. Kanemoto, and T. Hirose, "Random undersampling wireless EEG measurement device using a small TEG," 2023 IEEE Int. Symp. on Circuits and Systems (ISCAS), 2023, 10.1109/ISCAS46773.2023.10181822.

- 10) T. Moy, L. Huang, W. R. Louis, C. Wu, P. Cuff, S. Wagner, J. C. Sturm, and N. Verma, "An EEG acquisition and biomarker-extraction system using low-noise-amplifier and compressive-sensing circuits based on flexible, thinfilm electronics," IEEE J. Solid-State Circuits 52, 309 (2017).

- 11) H. R. Dehsorkh, N. Ravanshad, R. Lotfi, K. Mafinezhad, and A. M. Sodagar, "Analysis and design of tunable amplifiers for implantable neural recording applications," IEEE J. Emerg. Sel. Top. Curcuits Syst. 1, 546 (2011).

- 12) L. Shen, N. Lu, and N. Sun, "A 1 V 0.25 µW inverter stacking amplifier with 1.07 noise efficiency factor," 2017 Symp. on VLSI Circuits, 2017, 10.1109/JSSC.2017.2786724.

- 13) C. H. Tsai, Z. H. Hsieh, and W. C. Fang, "A low-power low-noise CMOS analog front-end IC for portable brain-heart monitoring applications," 2011 IEEE/NIH Life Science Systems and Applications Workshop (LiSSA), 2011, 10.1109/LISSA.2011.5754151.

- 14) M. Nasserian, A. Peiravi, and F. Moradi, "A 1.62 µW 8-channel ultra-high input impedance eeg amplifier for dry and non-contact biopotential recording applications," 2016 IFIP/IEEE Int. Conf. on Very Large Scale Integration (VLSI-SoC), 2016, 10.1109/VLSI-SoC.2016.7753539.

- 15) C. Chen, L. Chen, X. Wang, and F. Zhang, "A 66 dB SNDR, 8 µW analog front-end for ECG/EEG recording application," 2018 IEEE Int. Symp. on Circuits and Systems (ISCAS), 2018, 10.1109/ISCAS.2018.8351783.

- 16) C. Y. Wu and C. S. Ho, "An 8-channel chopper-stabilized analog front-end amplifier for EEG acquisition in 65 nm CMOS," 2015 IEEE Asian Solid-State Circuits Conf. (A-SSCC), 2015, 10.1109/ASSCC.2015.7387480.

- 17) X. T. Pham, D. N. Duong, N. T. Nguyen, N. V. Truong, and J. W. Lee, "A 4.5 GΩ-input impedance chopper amplifier with embedded DC-servo and ripple reduction loops for impedance boosting to Sub-Hz," IEEE Trans. Circuits Syst. Express Briefs 68, 116 (2021).

- 18) Z. Liang, B. Li, Z. Wu, and Y. Hu, "A high input impedance chopper amplifier using negative impedance convertor for implantable EEG recording," IEICE Electron. Express 17, 20200238 (2020).

- 19) Z. Yan, M. Atef, G. Wang, and Y. Lian, "Low-noise high input impedance 8-channels chopper-stabilized EEG Acquisition system," 2017 30th IEEE Int. System-on-Chip Conf. (SOCC), 2017, 10.1109/SOCC.2017.8226005.

- 20) Y. P. Chen et al., "An injectable 64 nW ECG mixed-signal SoC in 65 nm for arrhythmia monitoring," IEEE J. Solid-State Circuits 50, 375 (2015).

- M. Moradi, M. Dousti, and P. Torkzadeh, "Designing a low-power LNA and filter for portable EEG acquisition applications," IEEE Access 9, 71968 (2021).

- 22) T. Tang, W. L. Goh, L. Yao, and Y. Gao, "A 16-Channel TDM analog front-end with enhanced system cmrr for wearable dry EEG recording," 2017 IEEE Asian Solid-State Circuits Conf. (A-SSCC), 2017, 10.1109/ ASSCC.2017.8240209.

- 23) P. W. Chen, C. W. Huang, and C. Y. Wu, "An 1.97 μW/Ch 65 nm-CMOS 8-channel analog front-end acquisition circuit with fast-settling hybrid DC servo loop for EEG monitoring," 2018 IEEE Int. Symp. on Circuits and Systems (ISCAS), 2018, 10.1109/ISCAS.2018.8351075.

- 24) M. Mohsina and A. Majumdar, "Gabor based analysis prior formulation for EEG signal reconstruction," Biomed. Signal Process. Control 8, 951 (2013).

- L. Lin, Y. Meng, J. P. Chen, and Z. B. Li, "Multichannel EEG com-pression based on ICA and SPIHT," Biomed. Signal Process. Control 20, 45 (2015).

- 26) D. Kanemoto and T. Hirose, "EEG measurements with compressed sensing utilizing EEG signals as the basis matrix," 2023 IEEE Int. Symp. on Circuits and Systems (ISCAS), 2023, 10.1109/ISCAS46773.2023.10181710.

- 27) K. Nagai, D. Kanemoto, and M. Ohki, "Applying K-SVD dictionary learning for EEG compressed sensing framework with outlier detection and independent component analysis," IEICE Trans. Fundam. Electron. Commun. Comput Sci. E104-A, 1375 (2021).

- 28) Z. Zhang, T. P. Jung, S. Makeig, and B. D. Rao, "Compressed sensing of EEG for wireless telemonitoring with low energy consumption and inexpensive hardware," IEEE Trans. Biomed. Eng. 60, 221 (2013).

- D. Gangopadhyay et al., "Compressed sensing analog front-end for biosensor applications," IEEE J. Solid-State Circuits 49, 426 (2014).

- X. Zou, X. Xu, L. Yao, and Y. Lia, "A 1 V 450 nW fully integrated programmable biomedical sensor interface chip," IEEE J. Solid-State Circuits 44, 1067 (2009).

- A. H. Sodhro, S. Pirbhulal, G. H. Sodhro, and A. Gurtov, "A joint transmission power control and duty-cycle approach for smart healthcare system," IEEE Sens. J. 19, 8479 (2019).

- 32) Y. Zhang et al., "A batteryless 19  $\mu$ W MICS/ISM-band energy harvesting body sensor node SoC for ExG applications," IEEE J. Solid-State Circuits 48, 199 (2013).

- 33) K. Y. Yeh, Y. J. Huang, T. C. Chen, L. G. Chen, and S. S. Lu, "A 473 µW Wireless 16-channel neural recording SoC with RF energy harvester," 2018 Int. Symp. on VLSI Design, Automation and Test (VLSI-DAT), April 2018, 10.1109/VLSI-DAT.2018.8373250.

- 34) N. Verma, A. Shoeb, J. Bohorquez, J. Dawson, J. Guttag, and A. P. Chandrakasan, "A micro-power EEG acquisition SoC with integrated feature extraction processor for a chronic seizure detection system," IEEE J. Solid-State Circuits 45, 804 (2010).

- 35) H. Bhamra, J. Lynch, M. Ward, and P. Irazoqui, "A noise-power-area optimized biosensing front end for wireless body sensor nodes and medical implantable devices," IEEE Trans. Very Large Scale Integr. VLSI Syst. 25, 2917 (2017).

- 36) M. Tohidi, J. K. Madsen, and F. Moradi, "Low-power high-input-impedance EEG signal acquisition SoC with fully integrated IA and signal-specific ADC for wearable applications," IEEE Trans. Biomed. Circuits Syst. 13, 1437 (2019).

- 37) C. J. Deepu, X. Zhang, W. S. Liew, D. L. T. Wong, and Y. Lian, "An ECG-on-chip with 535 nW/channel integrated lossless data compressor for wireless sensors," IEEE J. Solid-State Circuits 49, 2435 (2014).

- 38) D. Yeager, F. Zhang, A. Zarrasvand, and B. P. Otis, "A 9.2 μA gen 2 compatible UHF RFID sensing tag with -12 dBm Sensitivity and 1.25 μVrms input-referred noise floor," 2010 IEEE Int. Solid-State Circuits Conf. (ISSCC), Feb. 2010, 10.1109/ISSCC.2010.5434055.

- 39) P. T. Dao, A. Griffin, and X. J. Li, "Compressed sensing of EEG with gabor dictionary: effect of time and frequency resolution," 2018 40th Annual Int. Conf. of the IEEE Engineering in Medicine and Biology Society (EMBC), July 2018, 10.1109/EMBC.2018.8513071.

- 40) K. Mii, D. Kanemoto, and T. Hirose, "Low quiescent current capacitively-coupled chopper instrumentation amplifier in EEG recording wearable devices for compressed sensing framework," Ext. Abstr. Solid State Devices and Materials, Nagoya, 9172023.

- 41) Y. Okabe, D. Kanemoto, O. Maida, and T. Hirose, "Compressed sensing EEG measurement technique with normally distributed sampling series," IEICE Trans. Fundam. Electron. Commun. Comput Sci. E105.A, 1429 (2022).

- E. H. T. Shad, M. Molinas, and T. Ytterdal, "Impedance and noise of passive and active dry EEG electrodes: a review," IEEE Sens. J. 20, 14565 (2020).

- 43) Q. Fan, F. Sebastiano, J. H. Huijsing, and K. A. A. Makinwa, "A 1.8 W 60 nV/ √Hz capacitively-coupled chopper instrumentation amplifier in 65 nm CMOS for wireless sensor nodes," IEEE J. Solid-State Circuits 46, 1534 (2011).

- 44) T. Denison, K. Consoer, W. Santa, A. T. Avestruz, J. Cooley, and A. Kelly, "A 2μW 100nV/rtHz chopper-stabilized instrumentation amplifier for chronic measurement of neural field potentials," IEEE J. Solid-State Circuits 42, 2934 (2007).

- 45) P. J. Hurst, S. H. Lewis, J. P. Keane, F. Aram, and K. C. Dyer, "Miller compensation using current buffers in fully differential CMOS two-stage operational amplifiers," IEEE Trans. Circuits Syst. I 51, 275 (2004).

- R. J. Baker, CMOS: Circuit Design, Layout, and Simulation (Wiley Inter Science, USA, 2005) 2nd ed., 3p. 786.

- Y. K. Cho and B. H. Park, "Loop stability compensation technique for continuous-time common-mode feedback circuits," 2015 Int. SoC Design Conf. (ISOCC), 2015, 10.1109/ISOCC.2015.7401737.

- 48) R. J. Baker, CMOS: Circuit Design, Layout, and Simulation (Wiley Inter Science, USA, 2005) 2nd ed., p. 873.

- C.-J. Lee and J.-I. Song, "A chopper stabilized current-feedback instrumentation amplifier for EEG acquisition applications," IEEE Access 7, 11565 (2019).

- C. Lee and J. Song, "A chopper-stabilized amplifier with a tunable bandwidth for EEG acquisition applications," IEEE Access 7, 73165 (2019).

- 51) Z. Hoseini, M. Nazari, K. S. Lee, and H. Chung, "Current feedback instrumentation amplifier with built-in differential electrode offset cancellation loop for ECG/EEG sensing frontend," IEEE Trans. Instrum. Meas. 70, 2001911 (2020).