| Title        | Low quiescent current LDO with FVF-based PSRR enhanced circuit for EEG recording wearable devices |

|--------------|---------------------------------------------------------------------------------------------------|

| Author(s)    | Mii, Kenji; Kanemoto, Daisuke; Hirose, Tetsuya                                                    |

| Citation     | Japanese Journal of Applied Physics. 2024, 63(3), p. 03SP33                                       |

| Version Type | VoR                                                                                               |

| URL          | https://hdl.handle.net/11094/97767                                                                |

| rights       | This article is licensed under a Creative Commons Attribution 4.0 International License.          |

| Note         |                                                                                                   |

## The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

#### **REGULAR PAPER • OPEN ACCESS**

# Low quiescent current LDO with FVF-based PSRR enhanced circuit for EEG recording wearable devices

To cite this article: Kenji Mii et al 2024 Jpn. J. Appl. Phys. 63 03SP33

View the article online for updates and enhancements.

## You may also like

- Ultra-low power low-dropout linear regulator with a load current tracking bias current generator for loT devices Yosuke Mizuno, Hikaru Sebe, Daisuke Kanemoto et al.

- A comparative study of digital low dropout regulators

Mo Huang, Yan Lu and Rui P. Martins

- A fast transient response and high current efficiency output-capacitorless low dropout regulator for low-power SoC applications Wei-Bin Yang, Yu-Hsin Li, Cheng-Yang Yu et al.

https://doi.org/10.35848/1347-4065/ad1f0e

## Low quiescent current LDO with FVF-based PSRR enhanced circuit for EEG recording wearable devices

Kenji Mii, Daisuke Kanemoto\*, and Tetsuya Hirose

Graduate School of Engineering, Osaka University, 2-1, Yamadaoka, Suita 565-0871, Japan

\*E-mail: dkanemoto@eei.eng.osaka-u.ac.jp

Received October 12, 2023; revised December 8, 2023; accepted January 14, 2024; published online February 16, 2024

This paper presents a low quiescent current low-dropout regulator (LDO) with an auxiliary amplifier, flipped voltage follower (FVF)-based power supply rejection ratio enhanced circuit (FBPEC) for electroencephalogram (EEG) recording devices. The FBPEC comprises a FVF filter, current mirror, and common-source amplifier. The FBPEC exploits the characteristics of FVF filter to reduce the current consumption and increase the gain at specific frequencies. The small-signal equivalent circuit reveals the dominant pole of the FBPEC, which is affected by the output impedance and load capacitance of the common-source amplifier. The proposed LDO is designed using a 0.18  $\mu$ m CMOS process and has improved power supply rejection ratio (PSRR) up to 18 dB at frequencies above 10 kHz compared to the general LDO. The proposed LDO has a low no-load quiescent current 648 nA and a good figure-of-merit score compared to those of previous works, proving that the proposed circuit is an effective solution for use in wearable EEG recording devices. © 2024 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP

Publishing Ltd

## 1. Introduction

The development of wearable devices enables us to easily understand and manage our biometric information. Recent studies on wearable electroencephalogram (EEG) recording devices facilitate health maintenance and support the diagnosis of various diseases. In wearable devices, the battery generally occupies a large portion of the device space, preventing weight reduction. However, a trade-off exists between the battery size and the operating time of the device. Therefore, it is crucial to reduce the overall power consumption of the device to realize small wearable devices capable of operating for sustained periods. Therefore, some studies have proposed sensing frameworks to reduce the overall power consumption of wearable devices with compressed sensing to achieve long operation times using small batteries. 1-4) Research on hardware implementation methods<sup>5,6)</sup> and verification using actual devices have been conducted, 7) and the effectiveness of the proposed framework has been determined.

However, the reduction in power consumption of the circuit is equally important. For example, the power management IC (PMIC), which supplies power to the entire system, is always operating, consuming a significant amount of power in a wearable device even in its sleep state.<sup>8)</sup> Therefore, the demand for low-consumption current PMICs has been increasing. Low-dropout regulators (LDOs) are commonly used as PMICs owing to their ease of use and low-noise performance. LDOs play a crucial role in a wide range of applications, such as driving noise-sensitive analog, RF, mixed-signal, and digital module interfaces. 9-14) In many cases, power supply circuits use LDOs and switch-mode power supplies (SMPSs) connected in series to optimize their efficiency and achieve a low noise output voltage. Therefore, the power supply rejection ratio (PSRR) characteristic of the LDO is crucial to suppress the output voltage ripple of the SMPS.  $^{15-17)}$  Generally, increasing the PSRR bandwidth of an LDO requires an increase in current consumption, which prevents the realization of small-sized wearable devices capable of operating for extended periods. Studies to improve the PSRR are underway, and a typical example involves a circuit configuration using a feedforward capacitor  $(C_{\rm ff})$ . <sup>17–23)</sup> However, a discrepancy exists between the output resistance of the SPICE model and that of the manufactured transistor, rendering the accurate design of circuits for high-impedance nodes challenging. Moreover, as the absolute value of the capacitor used for  $C_{\rm ff}$  is in the order of a few femtofarads, the characteristics vary drastically during manufacturing. Specific problems include difficulty in accurate design, large characteristic variation, and the requirement for a fast amplifier with high current consumption depending on the topology. Compact and long operating time biometric signal recording wearable device such as the one assumed in this study 1-7) suppresses power consumption by using duty-cycled communication.<sup>24)</sup> When a communication method such as Bluetooth low energy is used, tens of milli Amperes of current flows through the RF circuit during wireless communication; however, during other EEG detection, the current in circuits, other than the RF circuit, is less than 1 mA, which is a light load for an LDO. It is particularly difficult to improve the bandwidth of PSRR at light loads, and existing adaptively bias techniques<sup>25–27)</sup> that improve the PSRR by increasing the bias current based on the load current are less effective. A hybrid LDO controlled using an analog loop and a digital loop<sup>28)</sup> has also been proposed, but its large chip size and current consumption make it unsuitable for wearable devices, despite its outstanding PSRR characteristics.

Based on previous studies, realizing an auxiliary control circuit with low power consumption for PSRR is a simple solution. The technique proposed in this study does not increase the current consumption of the operational amplifier to improve the PSRR. Instead, an auxiliary amplifier, which uses a flipped voltage follower (FVF) filter that is characterized by low power consumption and partial gain in the HF band, improves the PSRR at high bandwidths while suppressing the current consumption. In contrast to our previous work,<sup>29)</sup> here we include an analysis using the small-signal equivalent circuit of the FBPEC and LDO measurement results to discuss its circuit behavior in more detail. The remainder of this paper is organized as follows. Sect. 2 describes the overall circuit of the proposed LDO and the ideas referred by us. In Sect. 3, we describe the operation of the FBPEC, an auxiliary amplifier used in the proposed LDO, using small-signal equivalent circuits and simulations. In

© 2024 The Author(s). Published on behalf of The Japan Society of Applied Physics by IOP Publishing Ltd

03SP33-1

Sect. 4, we present the measured results of our prototype chip of the proposed LDO. In Sect. 5, we conclude the paper.

## 2. FVF-based PSRR-enhanced circuit (FBPEC) in proposed LDO

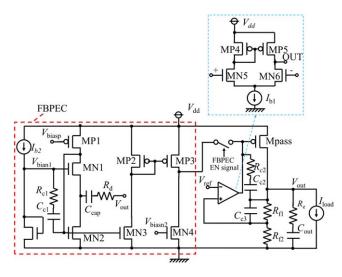

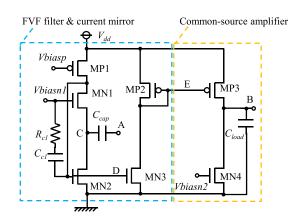

The circuit configuration of the proposed LDO is illustrated in Fig. 1.  $C_{\text{out}}$  and  $R_{\text{e}}$  denote the output capacitance and the parasitic resistance of the LDO, respectively;  $R_{\rm f1}$  and  $R_{\rm f2}$ indicate the voltage divider resistors of the LDO.  $R_{c1}$ ,  $R_{c2}$ ,  $C_{c1}$ ,  $C_{c2}$ , and  $C_{c3}$  are used as phase compensation elements.  $R_{\rm d}$  indicates the damping resistance to ensure stability during transients. The proposed circuit improves the PSRR by using an FVF-based PSRR-enhanced circuit (FBPEC) as an auxiliary amplifier. The circuit illustrated in Fig. 1 is capable of controlling the FBPEC output by using the FBPEC EN signal and a switch. The switch enables us to confirm the differences in the characteristics between the proposed LDO and a general LDO. The configuration of the FBPEC is depicted in Fig. 2. Node A shown in Fig. 2 refers to the input of the FBPEC, node B refers to the output of the FBPEC, and nodes C, D, and E correspond to the internal nodes of the FBPEC. The FBPEC comprises an FVF-filter, a current mirror, and common-source amplifier. The FVF used in the FBPEC has a low impedance at node C, low current consumption, and low-voltage operation. Recently, FVFs have been increasingly utilized to improve the PSRR characteristics of capacitor-less LDOs in systems on a chip. 30-34) In the aforementioned studies, FVFs are used in the main amplifiers for feedback or pass transistors. Specifically, they are used to increase the frequency of the dominant pole. However, previous studies require many amplification circuits, and the low current consumption characteristics for FVFs were not realized. The FVF filter is a circuit configuration that was proposed in a previous study; the filter achieved an unconventional signal amplification when a capacitor  $C_{\text{cap}}$  was added.<sup>35)</sup> In previous studies, the small-signal analysis of the FVF filter has been conducted, 35) and the role of MN1, shown in Fig. 2, in amplifying the signal enables us to achieve HF signal amplification and low quiescent current. However, the FVF filter alone cannot be used as an auxiliary amplifier owing to its low amplifier gain. As shown in Fig. 2, the FBPEC comprises a common-source

Fig. 1. Configuration of the proposed LDO.

Fig. 2. Configuration of the FBPEC.

amplifier using MN4 and MP3 for the FVF filter to improve its gain, such that it can be used as an auxiliary amplifier. However, stability must be considered by adding an amplification stage composed of MP3 and MN4.  $R_{\rm c1}$  and  $C_{\rm c1}$  are used as phase compensation elements. In designing the FBPEC, it is crucial to determine or estimate  $C_{\rm cap}$  and  $C_{\rm load}$ , primarily because the parameters  $C_{\rm cap}$  and  $C_{\rm load}$  affect the frequency characteristics of FBPEC. As a precondition, a capacitor with a large off-chip capacitance value is used for  $C_{\rm cap}$  in the FBPEC design. To express the parasitic capacitance of the pass transistor, a large sized  $C_{\rm load}$  is used. The following section presents a small-signal analysis to determine the dominant pole of the FBPEC.

## 3. FBPEC small signal analysis and simulation results

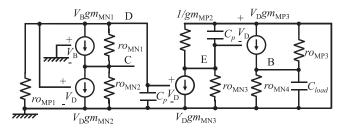

Figure 3 shows the small-signal equivalent circuit of the FBEC. Here,  $C_{\text{cap}}$  is much larger relative to the parasitic capacitance of the transistor, and  $R_d$  is much smaller than the output resistance of the transistor such that it can be neglected in the small-signal analysis, where ro denotes the output resistance of the transistor, gm denotes the output conductance of the transistor, and  $C_p$  denotes the parasitic capacitance of the transistor. As node C is connected to  $C_{load}$  via  $C_{\text{cap}}$ , its parasitic capacitance is relatively small compared to  $C_{\text{load}}$  and can be ignored. If we assume that the transconductances of all the transistors in the small-signal equivalent circuit shown in Fig. 3 are equal to  $gm_{MN1}$ , and the output resistances are equal to  $ro_{MN1}$ , then we can observe that the circuit has poles  $p_D$ ,  $p_E$ , and  $p_B$ , corresponding to the poles that occur at nodes D, E, and B, respectively. The equation showing the poles are as follows:

$$p_{\rm D} \approx \frac{g m_{\rm MN1}}{C_{\rm D}} \tag{1}$$

Fig. 3. Small-signal equivalent circuit of the FBPEC.

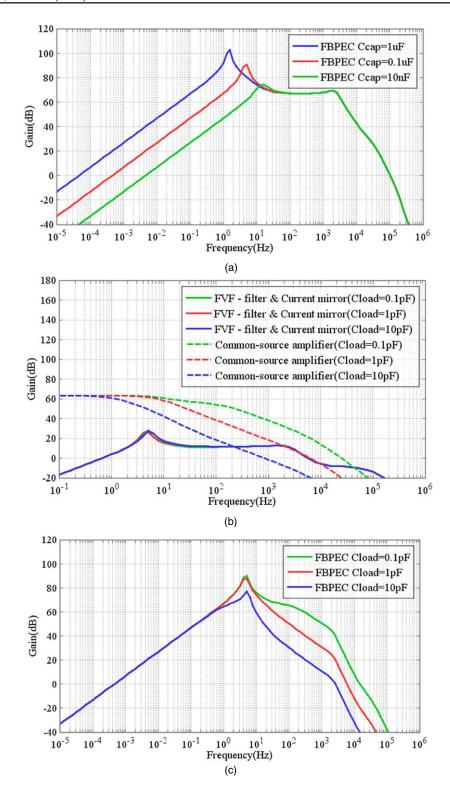

**Fig. 4.** Frequency response of the FBPEC and each component block at  $V_{\rm dd}=2$  V. (a) Effect of  $C_{\rm cap}$  ( $C_{\rm load}=0$  pF). (b) Effect of  $C_{\rm load}$  on the FVF-filter and current mirror and common-source amplifier ( $C_{\rm cap}=0.1~\mu{\rm F}$ ). (c) Effect of  $C_{\rm load}$  ( $C_{\rm cap}=0.1~\mu{\rm F}$ ).

$$p_{\rm E} \approx \frac{g m_{\rm MN1}}{C_{\rm p}} \tag{2}$$

$$p_{\rm B} \approx \frac{2}{ro_{\rm MNI}C_{\rm load}} \tag{3}$$

Since  $C_{\rm load}$  is generally designed to be greater than 100 times  $C_{\rm p}$ , we can observe from Eqs. (1) to (3) that  $p_{\rm B}$  is the dominant pole. In the following, the results of a simulation are used to validate the effects of  $C_{\rm cap}$  and  $C_{\rm load}$  on the FBPEC. The results of the SPICE simulation for the frequency response of

the FBPEC and each component block are presented in Fig. 4. The FBPEC is designed based on a 0.18  $\mu m$  CMOS process. The simulation condition is  $V_{\rm dd}=2$  V and  $I_{\rm Q}$  of the FBPEC is 100 nA. The simulation results of the frequency response with node A as input and node B as output, shown in Fig. 2, are shown in Fig. 4(a), indicating that the FBPEC can be optimized as an auxiliary amplifier by adjusting the frequency range of the gain of the FBPEC based on the  $C_{\rm cap}$  setting. The frequency response characteristics owing to the  $C_{\rm cap}$  sweep are based on the FVF filter and has been analyzed in a previous

Fig. 5. Chip microphotograph of LDO.

study. 35) Based on the results, the characteristics of the FBPEC are similar to those of the FVF filter and can function as a bandpass filter and amplifier. Figure 4(b) illustrates the frequency characteristics of the FVF filter and current mirror and the common-source amplifier stage when  $C_{load}$  sweeps, and the AC signal input/output definitions are identical to those shown in Fig. 4(a). The bandwidth of the commonsource amplifier is reduced owing to the effect of  $C_{load}$ , as shown in Eq. (3). The FVF filter and current mirror are not influenced by  $C_{load}$  because they are the prior stage circuits of the common-source amplifier. As the frequency response of the FBPEC is the product of the FVF filter and current mirror and the common-source amplifier, the unity gain frequency is determined by the value of  $C_{load}$ . In fact, it is evident from the results of the small-signal analysis. The frequency response of the FBPEC when  $C_{\text{load}}$  sweeps is shown in Fig. 4(c). The dominant pole depends on the value of  $C_{load}$  according to the the characteristics of the common-source amplifier shown in Fig. 4(b), the unity gain frequency of the FBPEC with a  $C_{load}$ of 10 pF is approximately 3 kHz, and the dominant pole frequency is 5 Hz. The frequency response of the FBPEC shown in Fig. 4 is characterized by its ability to increase the gain at specific frequencies compared to general operating amplifiers. The PSRR characteristics of the proposed circuit shown in Fig. 1 are determined by the sum of the frequency response characteristics of the conventional LDO and the frequency response characteristics of the FBPEC, which improves the PSRR in a specific bandwidth compared to the conventional circuit.

## 4. Measurement results of the proposed LDO

The proposed LDO, shown in Fig. 1, was designed using a 0.18  $\mu$ m CMOS process. The maximum  $I_{\rm load}$  of the LDO was designed to be 100 mA. The chip microphotograph is displayed in Fig. 5, where the active area is 0.103 mm<sup>2</sup>. The PCB used for the measurement is shown in Fig. 6. The PCB is a general two-layer board. An 84-PLCC package was used as the chip. The measured no-load  $I_{\rm Q}$  of the proposed LDO is

Fig. 6. A part of the PCB used for the measurement.

**Table I.** Measurement parameters and used components.

| Parameters and components                              | Value and model                                   |

|--------------------------------------------------------|---------------------------------------------------|

| $V_{ m dd}$                                            | 2 V                                               |

| I <sub>load</sub> (resistive load)                     | 1 mA                                              |

| $R_{\rm d}$                                            | $5 \text{ k}\Omega$                               |

| C0603C103K2RACTU                                       | 10 nF (for $C_{\text{out}}$ )                     |

| 0603BB104K500NGT                                       | $0.1  \mu \text{F}  (\text{for}  C_{\text{cap}})$ |

| Oscilloscope with frequency response analysis function | MSO44                                             |

| Line injector                                          | J2120A                                            |

648 nA. The measurement parameters and used components are listed in Table I.

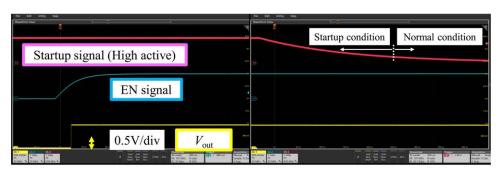

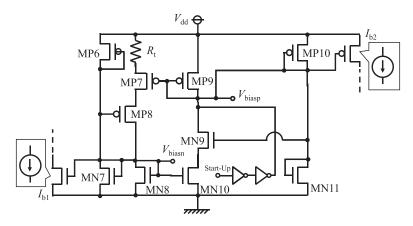

Figure 7 shows the measured start-up waveforms of the LDO by the EN signal and the start-up signal. Setting the startup signal to "H" increases the current consumption of the LDO during startup and setting it to "L" shifts the LDO to normal operation. The details of the role of the startup signal are described below. As indicated in the waveform in Fig. 7, the output voltage of the LDO is 0.938 V. The EN signal controls the ON and OFF of the LDO. The startup signal is used to activate the bias cell of the LDO. In Fig. 7, the EN signal is set to "high" after  $V_{\rm DD}$  is applied, preventing the occurrence of a high-impedance node during startup. Subsequently, by setting the startup signal to "low," the start-up state of the internal bias cell is terminated and the LDO transitions to its normal state. The bias cell of the LDO is depicted in Fig. 8. The cell generates the bias voltages  $V_{\rm biasp}$  and  $V_{\rm biasp}$ . These bias voltages are used as current

Fig. 7. Start-up waveform of the proposed LDO.

**Fig. 8.** Bias cell of the proposed LDO.

Fig. 9. PSRR of the proposed LDO.

mirrors. For instance, as illustrated in Fig. 8, V<sub>biasn</sub> and NMOS realize  $I_{b1}$  shown in Fig. 1, and  $V_{biasp}$  and PMOS realize  $I_{\rm b2}$  in Fig. 1. The bias voltages  $V_{\rm biasn}$  and  $V_{\rm biasp}$  are determined by MN8, MN10, MP7, MP9, and  $R_t$ . The resistor  $R_{\rm t}$  is used to improve the temperature characteristics. MN9 and MP8 are used as a cascode transistors; MN7, MN11, MP6, and MP10 generate the bias for the cascode transistors based on  $V_{\rm biasn}$  and  $V_{\rm biasp}$ . The bias circuit requires a startup circuit for proper operation. 36) In this study, the startup circuit was configured with inverters and an externally applied startup signal. The  $V_{\rm biasp}$  node is pulled down by the startup signal and the inverter, thereby increasing the reference current. In the startup condition, the device is activated by increasing the current in the bias cell. Following its activation, the device operates as a low-consumption LDO in the normal condition.

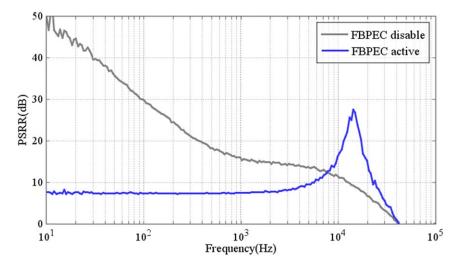

Figure 9 shows the measurement results of PSRR. Figure 9 shows that the HF PSRR characteristic increases when the FBPEC is changed from disabled to active state in the proposed circuit. It can also be observed that the proposed circuit with the FBPEC in active condition improves the PSRR at frequencies above 8 kHz owing to the effect of the FBPEC compared to the general circuit configuration. During EEG sensing of wearable devices, the SMPS is controlled in the pulse frequency modulation (PFM) mode owing to the light load. The control scheme reduces the switching

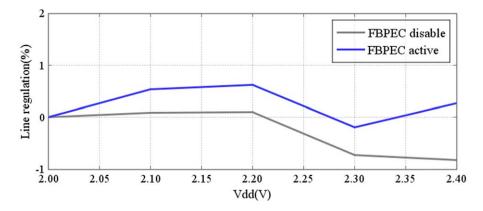

frequency at light loads, and in this study, the proposed LDO is most effective when the switching frequency is assumed to be 15 kHz, which is a reasonable frequency for an SMPS that is regulated by pulse frequency modulation control. The proposed LDO has a PSRR of 27.5 dB at 15 kHz, which is approximately 18 dB higher than that of the general configuration. At frequencies below 8 kHz, the PSRR of the proposed LDO is lower than that of the general configuration; however, it is not a problem because the characteristic below the lowest switching frequency is meaningless. Moreover, there is no problem in the DC characteristics because it is regulated in the loop of the differential amplifier. In PSRR measurements, since low-frequency characteristics could not be shown owing to limitations of the measurement equipment, an alternative measurement is employed via line regulation. Figure 10 presents the line regulation measurement results. In all condition, line regulation is within 1% and is well regulated by the differential amplifier of the conventional circuit. The frequency of the EEG signal is mainly distributed below 100 Hz, which is far from 15 kHz, the frequency of the power supply ripple. However, the analog-to-digital converter (ADC) must operate in a time-division manner to handle multiple channels, so the operating frequency must be 200 Hz multiplied by the number of channels or higher.<sup>5)</sup> It is known that power supply fluctuations, even if it is a power supply ripple at a

**Fig. 10.** Line regulation of the proposed LDO.

[28] [38] [39] This work Process 14 nm 180 nm 250 nm 180 nm Active area (mm<sup>2</sup>) 0.01 0.039 0.108 0.103  $V_{\rm ddMAX}(V)$ 1.2 1.8 3.3 3.3 Load Capacitor (µF)  $C_{\rm out} = 0.004$  $C_{\rm out} = 0.47$  $C_{\rm out} = 1$  $C_{\rm out} = 0.01$  $+ C_{\text{cap}} = 0.1$  $I_{O}$  (nA) 27300 900 1240 648  $I_{\text{loadMAX}}$  (mA) 15 50 150 100 PSRR @15 kHz (voltage ratio) 126 @  $I_{load} = 1.5 \text{ mA}$ 178 @  $I_{load} = 50 \text{ mA}$ 17.8 @  $I_{load} = 150 \text{ mA}$ 23.7 @  $I_{load} = 1 \text{ mA}$ F.O.M. (PSRR @15 kHz/I<sub>O</sub> @no-load) 0.005 0.198 0.014 0.037

Table II. Performance comparison of the proposed LDO with past works.

frequency far from the measurement signal, affect the characteristics of the ADC, such as reducing the dynamic range of the ADC.<sup>37)</sup> In other words, the power supply fluctuation at 15 kHz affects the characteristics of the ADC so that it contributes to the improvement of the system performance.

If the device performs wireless communication, then the load current of the LDO and the SMPS connected in series with the LDO increases, and the switching frequency of the SMPS becomes even higher by PFM control; however, it is allowed to increase the self-consumption current of the LDO in this case. Thus, if the switching frequency of the SMPS increases as the load current increases, it is not a problem either, particularly since the PSRR characteristics can be easily improved by using adaptively bias techniques, <sup>23–25)</sup> as described in the Introduction.

This study and previous studies are compared in Table II. The figure-of-merit (FOM) is defined as the PSRR at 15 kHz divided by the  $I_{\rm O}$  at no-load in a trade-off relationship, with higher values indicating better performance. The good performance of this study is shown in terms of the FOM. The FOM of previous study<sup>38)</sup> is also a higher value. The PSRR result in the previous study<sup>38)</sup> was measured at  $I_{load} = 50 \text{ mA}$ . In previous study, 38) the adaptive bias technique 25-27) has been used, which improves the PSRR at a large  $I_{load}$ , and thus appears to be superior as a FOM. It is not equally comparable in terms of improving the PSRR at light loads, which is the target of the proposed technology. Furthermore,  $I_{loadMAX}$  of this study can handle load currents up to 100 mA, which is considered advantageous as the current is increased during communication in wearable devices. The proposed circuit using FBPEC does not improve the load transient response.

Therefore, it is recommended that the proposed circuit be used in combination with a circuit that improves the load transient response<sup>35)</sup> when a fast response is required.

#### 5. Conclusions

This paper proposed an LDO with improved PSRR characteristics for EEG recording wearable devices. We designed an LDO that improves the PSRR at a specific frequency, as shown in the measurement results shown in Fig. 9 in Sect. 4. The proposed LDO was designed and fabricated using a 0.18  $\mu$ m CMOS process. Compared with the general configuration, the PSRR of the proposed LDO was improved by 18 dB at 15 kHz through measurement results. The measured no-load  $I_Q$  was as low as 648 nA, and the FOM confirmed the improved trade-off with PSRR. The results of the study validated that the proposed LDO could be a solution to address the battery size versus operating time trade-off of EEG recording wearable devices.

## **Acknowledgments**

This work was supported by JSPS KAKENHI Grant No. JP21H03410. This work was supported by JKA and its promotion funds from AUTO RACE.

D. Kanemoto, S. Katsumata, M. Aihara, and M. Ohki, "Compressed sensing framework applying independent component analysis after undersampling for reconstructing electroencephalogram signals," IEICE Trans. Fundam. E103.A, 1647 (2020).

K. Nagai, D. Kanemoto, and M. Ohki, "Applying K-SVD dictionary learning for EEG compressed sensing framework with outlier detection and independent component analysis," IEICE Trans. Fundam. E104.A, 1375 (2021).

- D. Kanemoto, S. Katsumata, M. Aihara, and M. Ohki, "Framework of applying independent component analysis after compressed sensing for electroencephalogram signals," Proc. of IEEE Biomedical Circuits and Systems Conf. (BioCAS) (USA), 2018, 10.1109/BIOCAS.2018.8584829.

- S. Katsumata, D. Kanemoto, and M. Ohki, "Applying outlier detection and independent component analysis for compressed sensing EEG measurement framework," Proc. of IEEE Biomedical Circuits and Systems Conf. (BioCAS) (Japan), 2019, 10.1109/BIOCAS.2019.8919117.

- Y. Okabe, D. Kanemoto, O. Maida, and T. Hirose, "Compressed sensing EEG measurement technique with normally distributed sampling series," IEICE Trans. Fundam. E105.A, 1429 (2022).

- D. Kanemoto and T. Hirose, "EEG measurements with compressed sensing utilizing EEG signals as the basis matrix," Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), 2023, p. 1, 10.1109/ISCAS46773.2023.10181710.

- T. Miyata, D. Kanemoto, and T. Hirose, "Random undersampling wireless EEG measurement device using a small TEG," Proc. IEEE Int. Symp. Circuits Syst. (ISCAS), 2023, p. 1, 10.1109/ISCAS46773.2023.10181822.

- J. Lee, K. Lee, U. Ha, J. Kim, K. Lee, S. Gweon, J. Jang, and H. Yoo, "A 0.8-V 82.9-μW in-ear BCI controller IC with 8.8 PEF EEG instrumentation amplifier and wireless BAN transceiver," IEEE J. Solid-State Circuits 54, 1185 (2019).

- Y. Chen, D. Ma, and P. Georgiou, "A wireless power management unit with a novel self-tuned LDO for system-on-chip sensors," Proc. of IEEE Int. Symp. on Circuits and Systems (ISCAS) (Korea), 2021, 10.1109/ ISCAS51556.2021.9401217.

- C. Zheng and D. Ma, "Design of monolithic CMOS LDO regulator with D2 coupling and adaptive transmission control for adaptive wireless powered bio-implants," IEEE Trans. Circuits Syst. I: Regular Papers 58, 2377 (2011).

- A. Arakali, S. Gondi, and P. K. Hanumolu, "Analysis and design techniques for supply-noise mitigation in phase-locked loops," IEEE Trans. Circuits Syst. I: Regular Papers 57, 2880 (2010).

- 12) M. Nasrollahpour and S. Hamedi-Hagh, "Fast transient response and high PSRR low drop-out voltage regulator," Proc. of IEEE Dallas Circuits and Systems Conf. (DCAS) (USA), 2016, 10.1109/DCAS.2016.7791122.

- 13) S. Gweon, J. Lee, K. Kim, and H. Yoo, "93.8% current efficiency and 0.672 ns transient response reconfigurable LDO for wireless sensor network systems," Proc. of IEEE Int. Symp. on Circuits and Systems (ISCAS) (Japan), 2019, 10.1109/ISCAS.2019.8702435.

- 14) Y. Jiang, D. Wang, and P. Chan, "A quiescent 407-nA output-capacitorless low-dropout regulator with 0–100 mA load current range," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 27, 1093 (2019).

- 15) P. Liao, Y. Chen, and P. Chen, "A single-inductor dual-ouput (SIDO) DC-DC converter for implantable medical devices in 180 nm standard CMOS process," Proc. of 25th IEEE Int. Conf. on Electronics, Circuits and Systems (ICECS) (France), 2018, 10.1109/ICECS.2018.8617929.

- 16) K. Li, X. Xiao, X. Jin, and Y. Zheng, "A 600-mA, fast-transient low-dropout regulator with pseudo-ESR technique in 0.18 μm CMOS process," IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 28, 403 (2020).

- 17) M. El-Nozahi, A. Amer, J. Torres, K. Entesari, and E. Sanchez-Sinencio, "High PSR low drop-out regulator with feed-forward ripple cancellation technique," IEEE J. Solid-State Circuits 45, 565 (2010).

- 18) T. Chien, C. Chen, S. Li, and C. Tsai, "A fast transient flip voltage follower based low dropout regulator with AC-coupled pseudo tri-loop technique without using any output capacitor," Proc. of IEEE Applied Power Electronics Conf. and Exposition (APEC) (USA), 2019, 10.1109/ APEC.2019.8722137.

- M. Huang, H. Feng, and Y. Lu, "A fully integrated FVF-Based low-dropout regulator with wide load capacitance and current ranges," IEEE Trans. Power Electron. 34, 11880 (2019).

- 20) U. Awais and T. W. Barton, "High PSRR low drop-out regulator with isolated replica feedback ripple cancellation technique," Proc. of IEEE Dallas Circuits and Systems Conf. (DCAS) (USA), 2016, 10.1109/ DCAS.2016.7791139.

- 21) S. Ganta, C. Park, D. Gitzel, R. Rivera, and J. Silva-Martinez, "An external capacitor-less low drop-out regulator with superior PSR and fast transient

- response," Proc. of IEEE 56th Int. Midwest Symp. on Circuits and Systems (MWSCAS) (USA), 2013, 10.1109/MWSCAS.2013.6674604.

- 22) Y. Lim, J. Lee, S. Park, and J. Choi, "An external-capacitor-less low-dropout regulator with less than -36 dB PSRR at all frequencies from 10kHz to 1GHz using an adaptive supply-ripple cancellation technique to the body-gate," Proc. of IEEE Custom Integrated Circuits Conf. (CICC), USA), 2017. 10.1109/CICC.2017.7993669.

- 23) B. Yang, B. Drost, S. Rao, and P. K. Hanumolu, "A high-PSR LDO using a feedforward supply-noise cancellation technique," Proc. of IEEE Custom Integrated Circuits Conf. (CICC) (USA), 2011, 10.1109/ CICC.2011.6055409.

- 24) A. H. Sodhro, S. Pirbhulal, G. H. Sodhro, and A. Gurtov, "A joint transmission power control and duty-cycle approach for smart healthcare system," IEEE Sens. J. 19, 8479 (2019).

- 25) D. Mandal, C. Desai, B. Bakkaloglu, and S. Kiaei, "Adaptively biased output cap-less NMOS LDO with 19 ns settling time," IEEE Trans. Circuits Syst. II: Express Briefs 66, 167 (2019).

- 26) A. A. Santra and Q. Khan, "A power efficient output capacitor-less LDO regulator with auto-low power mode and using feed-forward compensation," Proc. of 32nd Int. Conf. on VLSI Design and 2019 18th Int. Conf. on Embedded Systems (VLSID) (India), 2019, 10.1109/VLSID.2019.00025.

- 27) Y. Huang, Y. Lu, F. Maloberti, and R. P. Martins, "Nano-ampere low-dropout regulator designs for IoT devices," IEEE Trans. Circuits Syst. I: Regular Papers 65, 4017 (2018).

- 28) X. Liu, H. K. Krishnamurthy, T. Na, S. Weng, K. Z. Ahmed, C. Schaef, K. Ravichandran, J. W. Tschanz, and V. De, "A universal modular hybrid LDO with fast load transient response and programmable PSRR in 14 nm CMOS featuring dynamic clamp strength tuning," IEEE J. Solid-State Circuits 56, 2402 (2021).

- 29) K. Mii, D. Kanemoto, and T. Hirose, "Low quiescent current LDO with FVF-Based PSRR enhanced circuit for EEG recording wearable devices," Ext. Abstr. Solid State Devices and Materials (Nagoya), 2023, p. 411, 10.7567/SSDM.2023.J-3-04.

- G. Cai, Y. Lu, C. Zhan, and R. P. Martins, "A fully integrated FVF LDO with enhanced full-spectrum power supply rejection," IEEE Trans. Power Electron. 36, 4326 (2021).

- J. Guo and K. N. Leung, "A 6 μW chip-area-efficient output-capacitorless LDO in 90 nm CMOS technology," IEEE J. Solid-State Circuits 45, 1896 (2010).

- 32) V. Shirmohammadli, A. Saberkari, H. Martínez-García, and E. Alarcón-Cot, "An output-capacitorless FVF-based low-dropout regulator for power management applications," Proc. of IEEE 14th Int. Conf. on Industrial Informatics (INDIN) (France), 2016, 10.1109/INDIN.2016.7819169.

- 33) X. L. Tan, K. C. Koay, S. S. Chong, and P. K. Chan, "A FVF LDO regulator with dual-summed miller frequency compensation for wide load capacitance range applications," IEEE Trans. Circuits Syst. I: Regular Papers 61, 1304 (2014).

- 34) A. Saberkari, H. Martinez, and E. Alarcón, "Fast transient response CFA-based LDO regulator," in Proc. of IEEE Int. Symp. on Circuits and Systems (ISCAS) (Korea), 2012, 10.1109/ISCAS.2012.6271990.

- K. Mii, A. Nagahama, and H. Watanabe, "Ultra-low quiescent current LDO with FVF-based load transient enhanced circuit," IEICE Trans. Electron. E103.C, 466 (2020).

- 36) P. E. Allen and D. R. Holberg, *CMOS Analog Circuit Design* (Oxford University Press, New York, 2012) 3rd ed. p. 152.

- L. Bryan, Fundamentals of Precision ADC Noise Analysis (Texas Instruments, Texas, 2020) p. 53.

- 38) A. Maity and A. Patra, "Design and analysis of an adaptively biased low-dropout regulator using enhanced current mirror buffer," IEEE Trans. Power Electron. 31, 2324 (2016).

- 39) R. Magod, B. Bakkaloglu, and S. Manandhar, "A 1.24 μA quiescent current NMOS low dropout regulator with integrated low-power oscillator-driven charge-pump and switched-capacitor pole tracking compensation," IEEE J. Solid State Circuits 53, 2356 (2018).