|              |                                                                                               |

|--------------|-----------------------------------------------------------------------------------------------|

| Title        | Energy-Efficient Architectural Design of High-Dimensional Computing Paradigm for Edge Devices |

| Author(s)    | Liang, Dehua                                                                                  |

| Citation     | 大阪大学, 2024, 博士論文                                                                              |

| Version Type | VoR                                                                                           |

| URL          | <a href="https://doi.org/10.18910/98690">https://doi.org/10.18910/98690</a>                   |

| rights       |                                                                                               |

| Note         |                                                                                               |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

Energy-Efficient Architectural Design of

High-Dimensional Computing Paradigm for Edge Devices

Submitted to

Graduate School of Information Science and Technology

Osaka University

July 2024

Dehua LIANG

# Publications

## Journal Articles (Refereed)

- [J1] Dehua Liang, Jun Shiomi, Noriyuki Miura, Masanori Hashimoto, and Hiromitsu Awano, “A Hardware Efficient Reservoir Computing System Using Cellular Automata and Ensemble Bloom Filter,” *IEICE Transactions on Information and Systems*, Vol. E105-D, No. 7, pp. 1273–1282, July 2022.

- [J2] Dehua Liang, Jun Shiomi, Noriyuki Miura, and Hiromitsu Awano, “StrideHD: A Binary Hyperdimensional Computing System Utilizing Window Striding for Image Classification,” *IEEE Open Journal of Circuits and Systems*, just accepted (May 2024). <https://doi.org/10.1109/ojcas.2024.3401028>

- [J3] Dehua Liang, Hiromitsu Awano, Noriyuki Miura, and Jun Shiomi, “A Robust and Energy Efficient Hyperdimensional Computing System for Voltage-scaled Circuits,” *ACM Transactions on Embedded Computing Systems*, just accepted (September 2023). <https://doi.org/10.1145/3620671>

## International Conference Papers (Refereed)

- [C1] Dehua Liang, Masanori Hashimoto, and Hiromitsu Awano, “BloomCA: A Memory Efficient Reservoir Computing Hardware Implementation Using Cellular Automata and Ensemble Bloom Filter,” in *2021 Design, Automation & Test in Europe Conference & Exhibition (DATE)*, Grenoble, France, 2021, pp. 587-590, doi: 10.23919/DATE51398.2021.9474047.

- [C2] Dehua Liang, Jun Shiomi, Noriyuki Miura, and Hiromitsu Awano, “DistriHD: A Memory Efficient Distributed Binary Hyperdimensional Computing Architecture for Image Classification,” in *Proceedings of the 27th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp. 43-49, Jan. 2022.

- [C3] Dehua Liang, Hiromitsu Awano, Noriyuki Miura, and Jun Shiomi, “DependableHD: A Hyperdimensional Learning Framework for Edge-oriented Voltage-scaled Circuits,” in *Proceedings of the 28th Asia and South Pacific Design Automation Conference (ASP-DAC)*, pp. 416-422, Jan. 2023.

# Summary

With the emergence of the Internet of Things (IoT), devices are generating massive data streams. Running big data processing algorithms, e.g., machine learning, on edge devices poses substantial technical challenges due to limited device resources. Compared to the sophisticated machine learning method, the brain-inspired high-dimensional computing paradigm are considered as promising alternative in terms of energy efficiency and robustness, which is suitable for the resource limited scenario. As a novel computing paradigm, how to reduce the hardware cost while maintaining sufficient accuracy performance on edge devices is still an open problems for circuit designers. The goal of this thesis is thus to provide the strategies to design an energy efficient high-dimensional computing paradigm on edge devices. In this thesis, we provide the solutions for high-dimensional computing from different perspectives: arithmetic operations, memory usage, and robustness, which eventually leading to the pursuit of energy efficiency.

In Chapter 3, we discussed the bottleneck for the reservoir computing (RC) systems in several related papers, which is one of the typical high-dimensional computing paradigms. Suffered from the huge memory usage and expensive arithmetic operations, there was still gap between the RC concept to practical implementation on edge devices. Therefore, this thesis propose a novel RC architecture *EnsembleBloomCA*, which utilizes cellular automata (CA) and an ensemble Bloom filter to organize an RC system. By adopting CA as the reservoir in the RC system, it can be implemented using only binary operations and is thus energy efficient. The rich pattern dynamics created by CA can map the original input into a high-dimensional space and provide more features for the classifier. Applying the ensemble Bloom filters as the classifier, the features provided by the reservoir can be effectively memorized. As the combination of these two techniques, the novel RC architecture successfully eliminates all floating-point calculation and integer multiplication. Our experiment result demonstrated that  $43\times$  and  $8.5\times$  reduction is achieved in terms of memory usage and power consumption, while the accuracy performance is maintained.

Although the extreme energy efficiency is achieved in the first prototype with novel RC architecture, the circuits designer's target changes for variety application scenarios. The high-dimensional computing paradigm are also expected to achieve not only

sufficient but also competitive accuracy performance, which has posed designers problems to balance the trade-off between different key indicators. In Chapter 4, we found the similar issues should be tackled in hyper-dimensional computing (HDC), which are also considered as high-dimensional computing paradigm. To alleviate the huge memory cost during encoding procedure in HDC (i.e., over 95% of the memory capacity is consumed), we propose a novel HDC architecture *StrideHD* that utilizes the window striding in image classification. It encodes data points to distributed binary hypervectors and eliminates the expensive Channel item Memory (CiM) and item Memory (iM) in the encoder, which significantly reduces the required hardware cost for inference. For the improvement of accuracy on edge devices during inference, we provide the iterative learning mode for the proposed HDC architecture. It also enables HDC systems to be trained and tested using binary hypervectors and achieves very competitive accuracy performance. The experiment result shows that the proposed HDC model achieves extreme memory efficiency ( $27.6\times$ ) with acceptable accuracy performance under the single-pass mode, while its iterative mode provides competitive performance (11.33% classification accuracy improvement) and keeping the memory efficiency ( $8.7\times$  improvement) for inference phase. The iterative retraining can be accomplished within fewer iterations compared to the baseline HDC works.

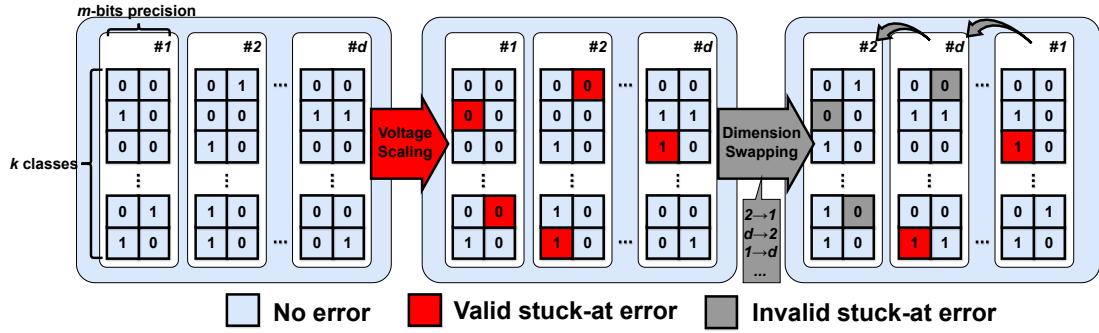

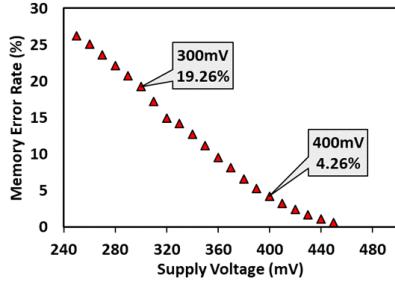

Besides the trade-off between accuracy performance and hardware resource in high-dimensional computing, the robustness issue are also arousing the attention of circuit designers. As we commonly known, scaling down the supply voltage is a promising approach to reduce the energy consumption of the circuits, while the aggressive voltage scaling will pose designers several severe problems such as the performance variation and functional failures. It is a potential solution to tolerate the voltage-scaling induced functional failures by the superior robustness of the brain-inspired high-dimensional computing paradigms. Therefore, we introduces the concept of margin enhancement for model retraining and utilizes noise injection to improve the robustness in the proposed HDC framework *DependableHD*, which is capable of application in most state-of-the-art HDC algorithms. After analyzing the error patterns in voltage-scaled circuits, we come up with a strategy to take fully advantage of the equivalent structure transformation in HDC architecture. We additionally propose the dimension-swapping technique, which aims at handling the stuck-at errors induced by aggressive voltage scaling in the memory cells. The experiment shows that under 8% memory stuck-at error, the proposed method exhibits a 2.42% accuracy loss on average, which achieves a  $14.1\times$  robustness improvement compared to the baseline HDC solution. The work also supports the systems to reduce the supply voltage from 430mV to 340mV for both item Memory and Associative Memory, which provides a 41.8% energy consumption reduction while maintaining competitive accuracy performance.

# Acknowledgments

First of all, I would like to express my deepest gratitude to Associate Professor Jun Shiomori for his invaluable guidance, support, and encouragement throughout my PhD journey at Osaka University. His profound expertise, insightful suggestions, and advanced perspective have led me to these achievements. His mentorship has been a cornerstone of my research career, and I am sincerely appreciative of all the time and effort he has invested in my development.

I would like to express my sincere appreciation to Associate Professor Hiromitsu Awano at Kyoto University for his precious suggestions and enormous help throughout my master's and doctoral research.

I am deeply grateful to Professor Noriyuki Miura at Osaka University for providing me with a precious opportunity and an excellent environment to study as a doctoral student in his laboratory.

I would also like to thank Professor Yasushi Sakurai at Osaka University for his detailed reviews and insightful suggestions.

I extend my appreciation to Professor Masanori Hashimoto at Kyoto University for giving me the chance to study VLSI design in his laboratory during my master's degree.

My sincere appreciation goes to Associate Professor Yoshihiro Midoh at Osaka University, Assistant Professor Ryo Shirai at Kyoto University, and Associate Professor Jaehoon Yu at the Tokyo Institute of Technology for their invaluable suggestions and enormous help.

I am grateful to Dr. Jun Chen, Dr. Tai-Yu Cheng, Miss Yangchao Zhang, Mr. Lukas Nakamura from Osaka University and Dr. Ángel López from Tokyo Institute of Technology for their technical discussions and suggestions. I would also like to thank my colleagues, past and present, from the Intelligent Integrated Systems Laboratory at Osaka University for their daily discussions and support. Special thanks to our laboratory secretary, Mrs. Makiko Arai, for her various support. I appreciate the financial support from the Osaka University fellowship. Additionally, I would like to thank all of my friends for their financial and emotional support.

I would like to extend my heartfelt gratitude to my parents. They have always supported and encouraged me with their best wishes.

# Contents

|          |                                                                          |           |

|----------|--------------------------------------------------------------------------|-----------|

| <b>1</b> | <b>Introduction</b>                                                      | <b>1</b>  |

| 1.1      | Background . . . . .                                                     | 1         |

| 1.2      | Motivation: High-Dimensional Computing . . . . .                         | 5         |

| 1.3      | Challenges toward High-Dimensional Computing . . . . .                   | 8         |

| 1.3.1    | Elimination of Expensive Arithmetic Operations . . . . .                 | 9         |

| 1.3.2    | Memory Efficient High-Dimensional Computing . . . . .                    | 10        |

| 1.3.3    | Model Robustness in the Low Voltage Operation . . . . .                  | 11        |

| 1.4      | Research Goal and Thesis Contribution . . . . .                          | 12        |

| 1.4.1    | Research Target . . . . .                                                | 12        |

| 1.4.2    | Thesis Contribution . . . . .                                            | 13        |

| 1.5      | Thesis Organization . . . . .                                            | 16        |

| <b>2</b> | <b>Literature Review and Preliminaries on High-Dimensional Computing</b> | <b>17</b> |

| 2.1      | Reservoir Computing . . . . .                                            | 17        |

| 2.1.1    | Basics of Reservoir Computing . . . . .                                  | 17        |

| 2.1.2    | Suitable Components for Hardware Implementation . . . . .                | 19        |

| 2.2      | Hyper-Dimensional Computing . . . . .                                    | 20        |

| 2.2.1    | Basic of Hyper-Dimensional Computing . . . . .                           | 20        |

| 2.2.2    | Related Works . . . . .                                                  | 26        |

| 2.3      | Voltage Scaling for Low Power Design . . . . .                           | 30        |

| 2.4      | Summary . . . . .                                                        | 31        |

| <b>3</b> | <b>RC System using CA and Ensemble BF</b>                                | <b>33</b> |

| 3.1      | Introduction . . . . .                                                   | 33        |

| 3.2      | Preliminary . . . . .                                                    | 34        |

| 3.2.1    | Cellular Automata (CA) . . . . .                                         | 34        |

| 3.2.2    | Cellular Automata Applied to Reservoir Computing . . . . .               | 35        |

| 3.2.3    | Application of Bloom Filter . . . . .                                    | 37        |

| 3.3      | Proposed Method . . . . .                                                | 38        |

| 3.3.1    | <i>EnsembleBloomCA</i> . . . . .                                         | 38        |

|          |                                                           |           |

|----------|-----------------------------------------------------------|-----------|

| 3.3.2    | Ensemble Bloom Filter . . . . .                           | 40        |

| 3.4      | Experiment . . . . .                                      | 41        |

| 3.4.1    | Experiment Setup . . . . .                                | 41        |

| 3.4.2    | Optimization of ReCA . . . . .                            | 42        |

| 3.4.3    | Experiment Results . . . . .                              | 43        |

| 3.4.4    | Hardware Implementation . . . . .                         | 44        |

| 3.5      | Conclusion . . . . .                                      | 45        |

| <b>4</b> | <b>Binary HDC System utilizing Window Striding</b>        | <b>47</b> |

| 4.1      | Introduction . . . . .                                    | 47        |

| 4.2      | Proposed Method . . . . .                                 | 49        |

| 4.2.1    | Feature Extraction by Window Striding . . . . .           | 49        |

| 4.2.2    | Encoder . . . . .                                         | 51        |

| 4.2.3    | Single-Pass Training . . . . .                            | 53        |

| 4.2.4    | Inference . . . . .                                       | 54        |

| 4.2.5    | Optimized Model Sparsification . . . . .                  | 54        |

| 4.2.6    | Iterative Retraining . . . . .                            | 55        |

| 4.3      | Hardware Implementation of Inference . . . . .            | 56        |

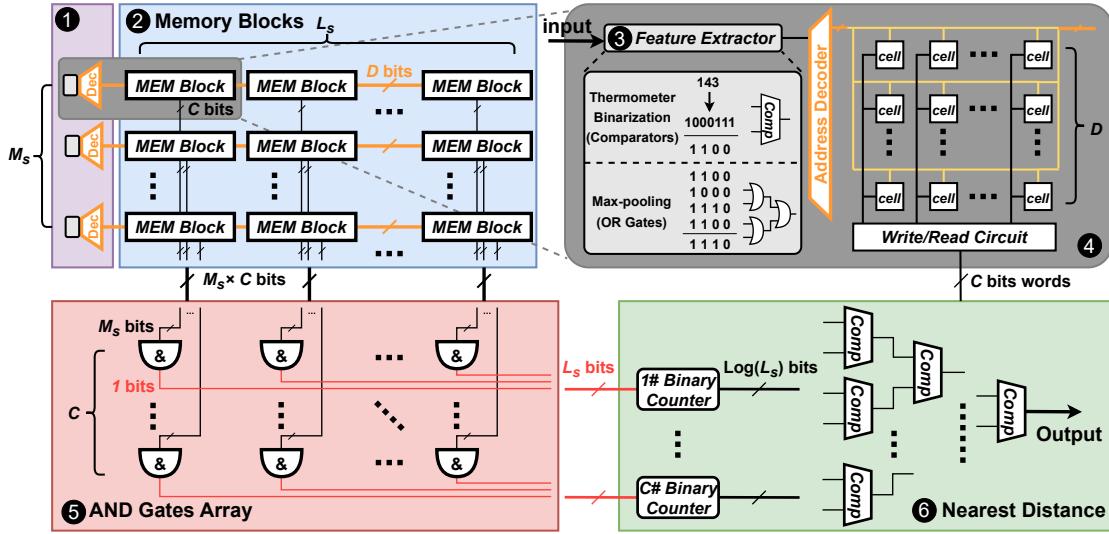

| 4.3.1    | Encoding Blocks . . . . .                                 | 56        |

| 4.3.2    | Associative Memory (AM) Blocks . . . . .                  | 57        |

| 4.3.3    | AND Gates Array . . . . .                                 | 57        |

| 4.3.4    | Nearest Distance Searching . . . . .                      | 58        |

| 4.4      | Experiment . . . . .                                      | 58        |

| 4.4.1    | Experimental Setup . . . . .                              | 58        |

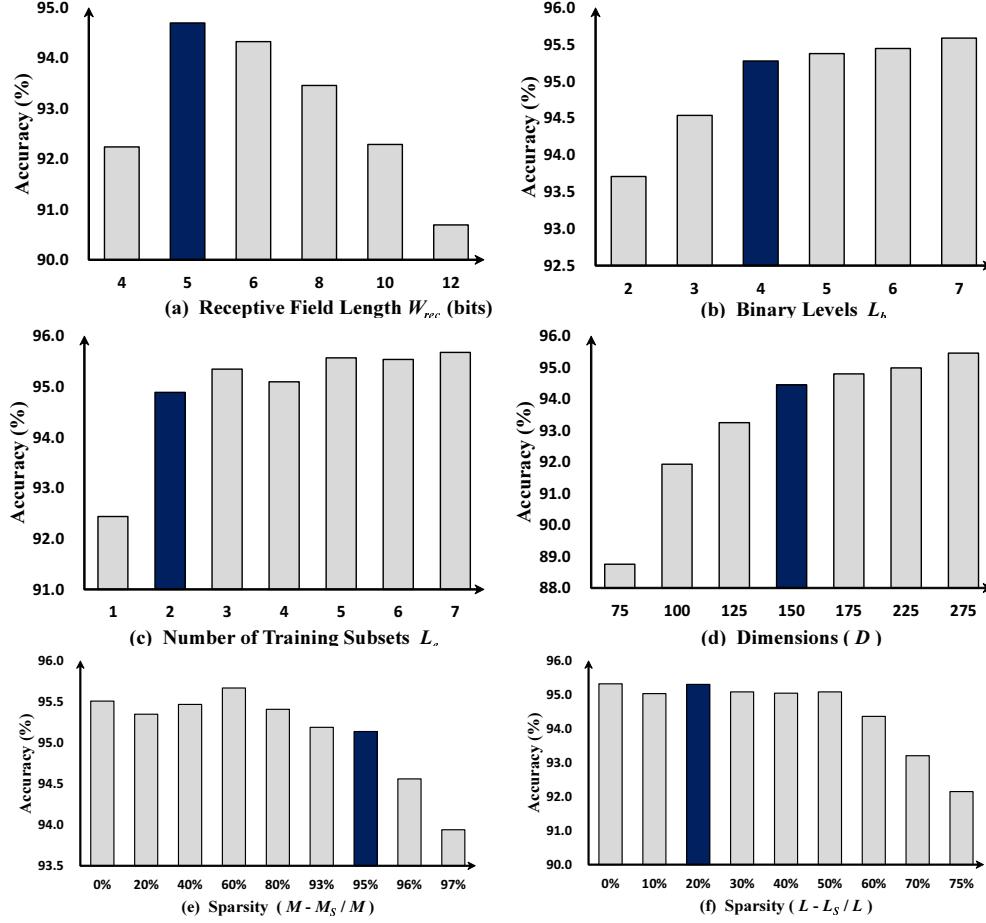

| 4.4.2    | Single-Pass Training Parameters Tuning . . . . .          | 59        |

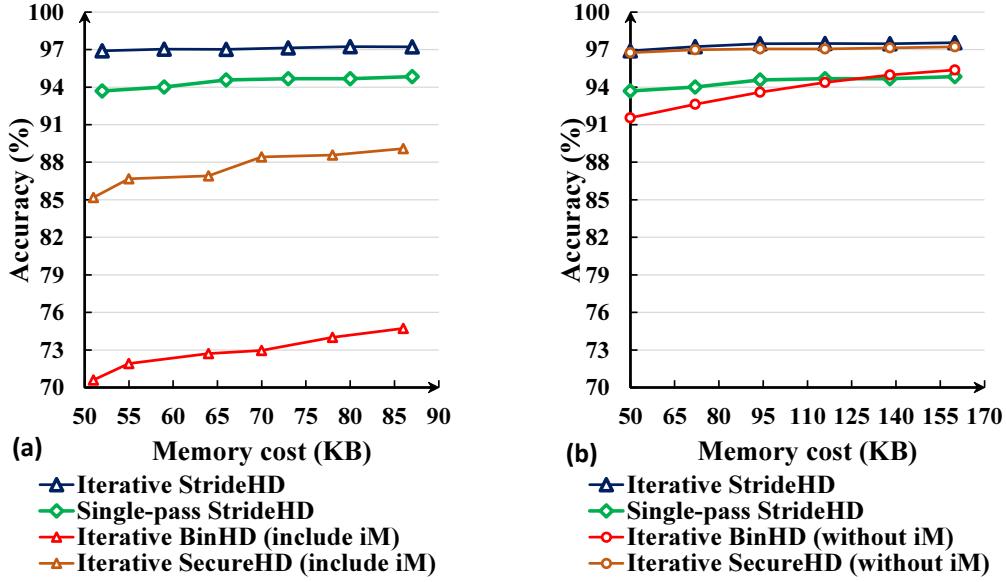

| 4.4.3    | Memory Efficiency . . . . .                               | 59        |

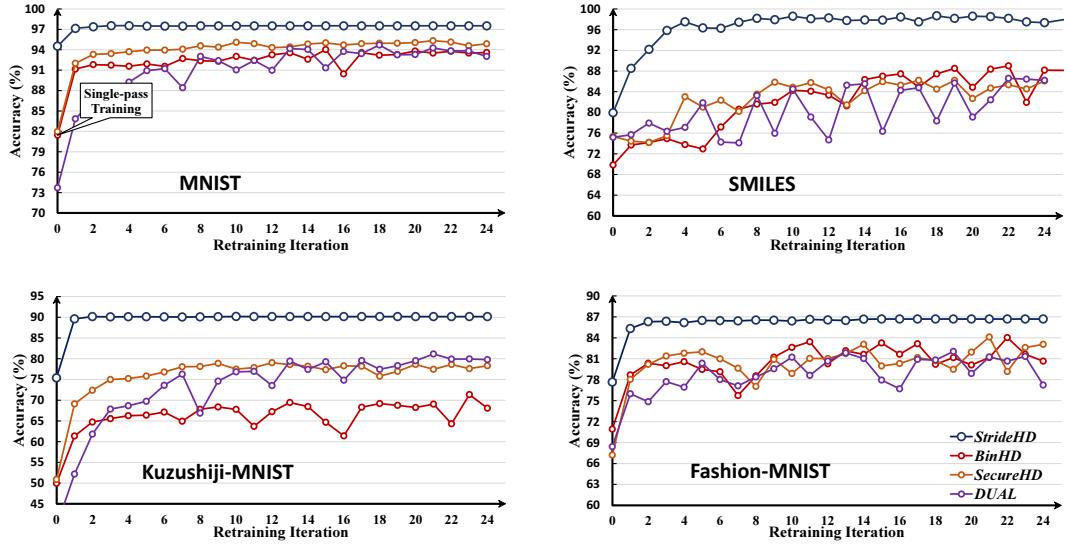

| 4.4.4    | Retraining Iterations & Classification Accuracy . . . . . | 61        |

| 4.4.5    | Hardware Implementation . . . . .                         | 63        |

| 4.5      | Conclusion . . . . .                                      | 64        |

| <b>5</b> | <b>Robust HDC System for Voltage-scaled Circuits</b>      | <b>67</b> |

| 5.1      | Introduction . . . . .                                    | 67        |

| 5.2      | Proposed Method . . . . .                                 | 69        |

| 5.2.1    | Margin Enhancement . . . . .                              | 70        |

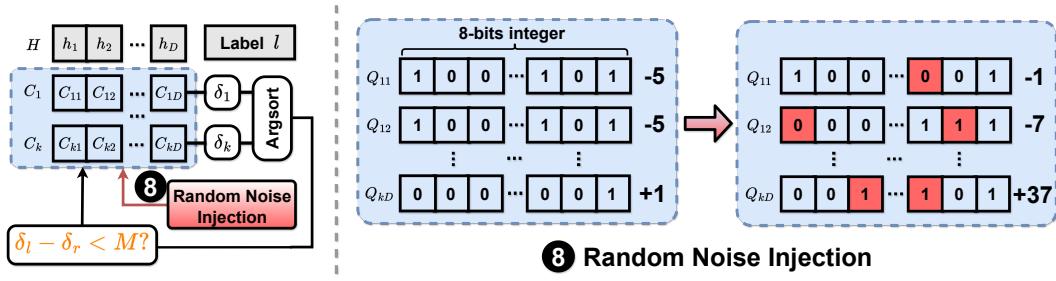

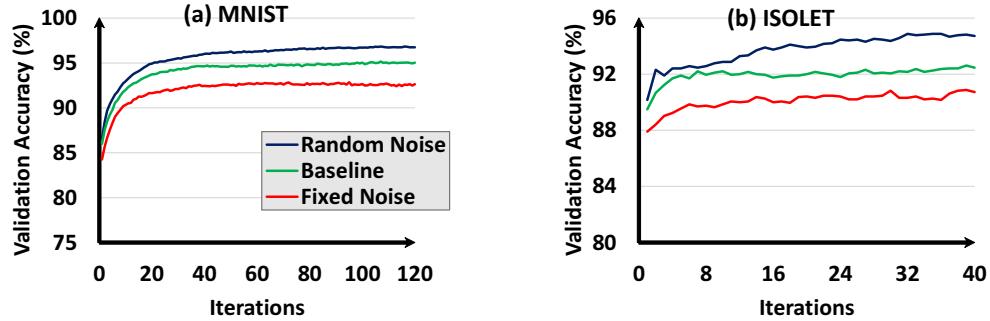

| 5.2.2    | Random Noise Injection . . . . .                          | 72        |

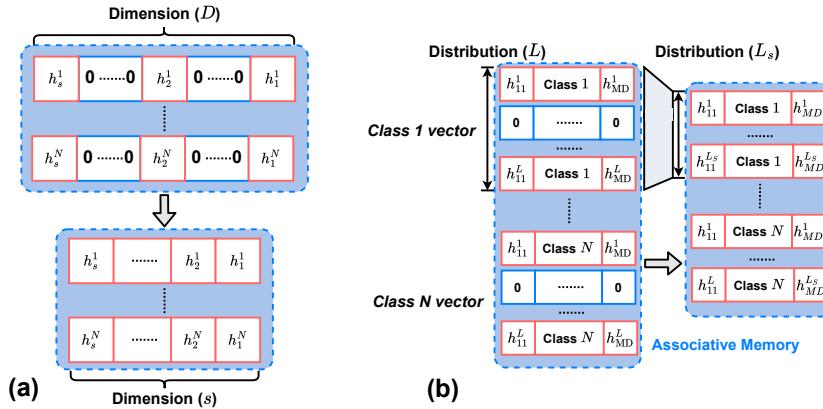

| 5.2.3    | Dimension-swapping . . . . .                              | 73        |

| 5.3      | Architecture of <i>DependableHDv2</i> . . . . .           | 74        |

| 5.3.1    | Memory Blocks . . . . .                                   | 75        |

| 5.3.2    | Encoding Modules . . . . .                                | 75        |

| 5.3.3    | Nearest Distance Searching . . . . .                      | 75        |

|                     |                                                                   |           |

|---------------------|-------------------------------------------------------------------|-----------|

| 5.3.4               | Dimension Sorting Modules . . . . .                               | 75        |

| 5.4                 | Experiment . . . . .                                              | 77        |

| 5.4.1               | Experimental Setup . . . . .                                      | 77        |

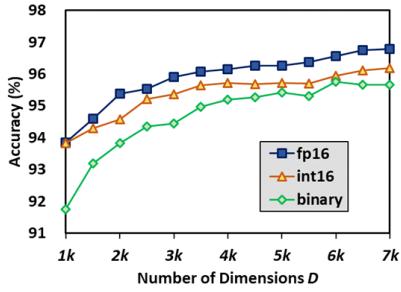

| 5.4.2               | Impact of Voltage Scaling, Dimensionality and Precision . . . . . | 77        |

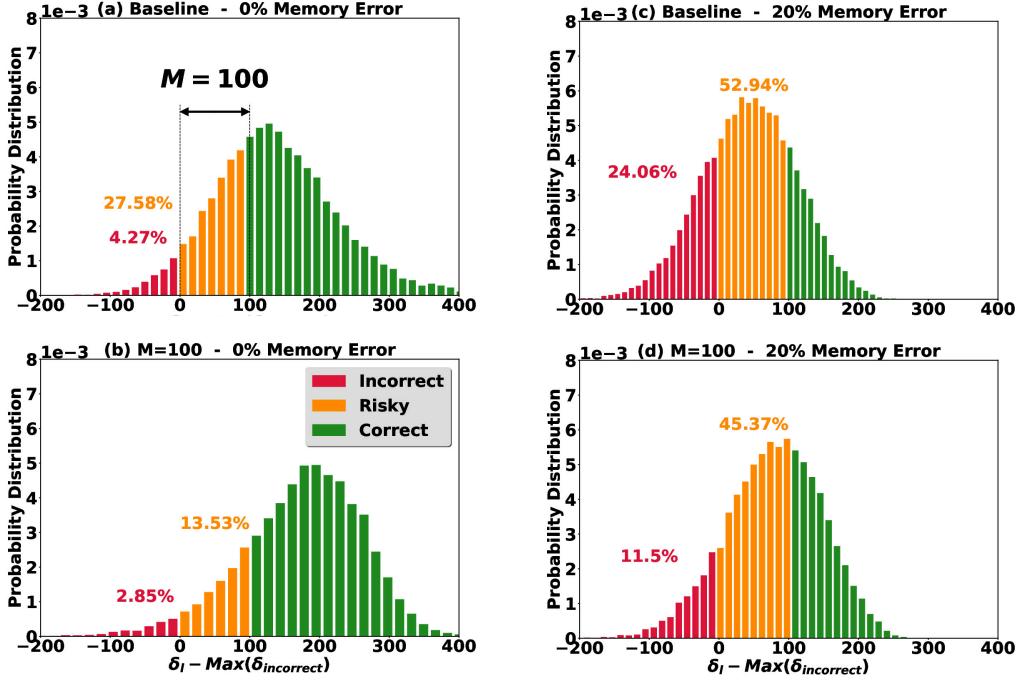

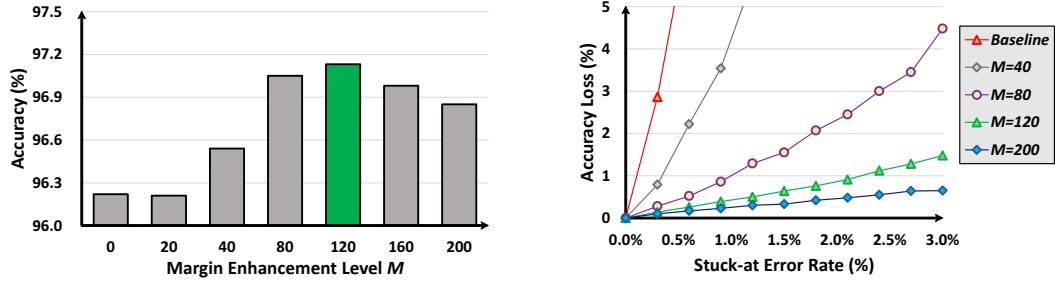

| 5.4.3               | Margin Enhancement Level . . . . .                                | 78        |

| 5.4.4               | Random Noise Injection Level . . . . .                            | 79        |

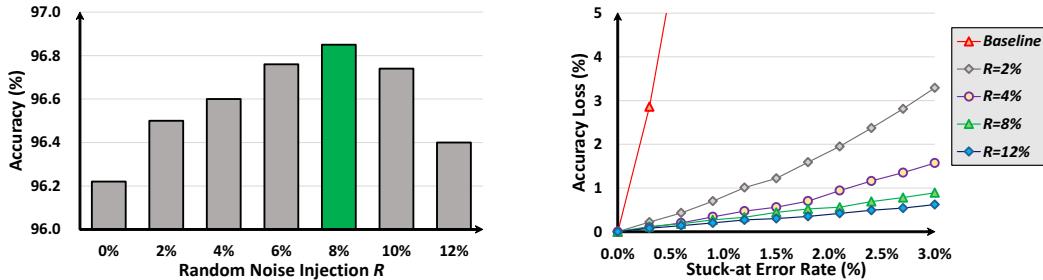

| 5.4.5               | Performance of Dimension-swapping . . . . .                       | 80        |

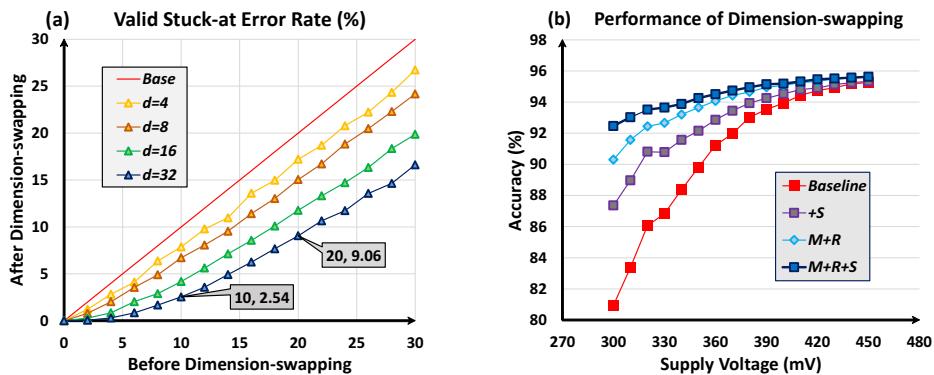

| 5.4.6               | <i>DependableHDv2</i> Robustness . . . . .                        | 81        |

| 5.4.7               | Energy Consumption Reduction . . . . .                            | 83        |

| 5.5                 | Conclusion . . . . .                                              | 84        |

| <b>6</b>            | <b>Summary</b>                                                    | <b>87</b> |

| 6.1                 | Summary of This Thesis . . . . .                                  | 87        |

| 6.2                 | Clarification of Proposed Methods . . . . .                       | 89        |

| 6.3                 | Future Works . . . . .                                            | 91        |

| <b>Bibliography</b> |                                                                   | <b>93</b> |

# List of Figures

|     |                                                                                                                                                                                |    |

|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

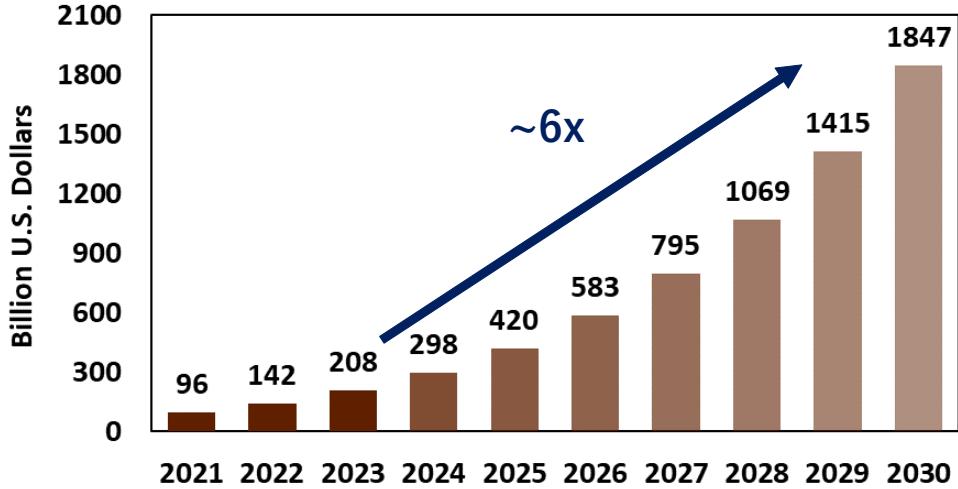

| 1.1 | The worldwide market size of Artificial Intelligence (AI) in 2021 with a forecast until 2030 (in billion U.S. dollars). . . . .                                                | 2  |

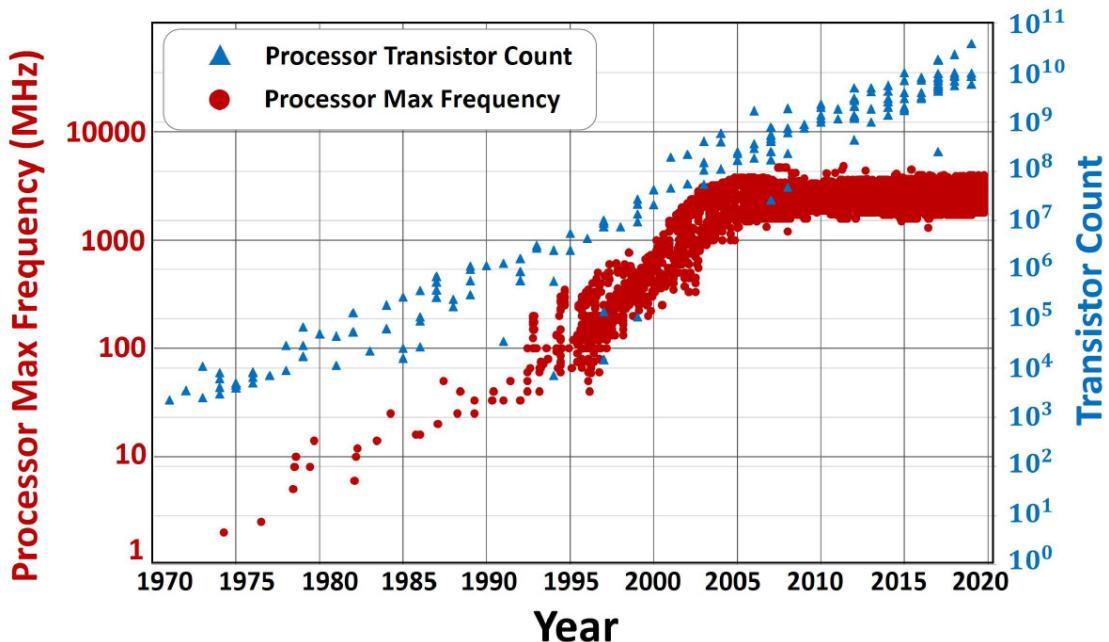

| 1.2 | Trend Data of the Transistors Numbers and Maximum Clock Frequency in Microprocessor. . . . .                                                                                   | 4  |

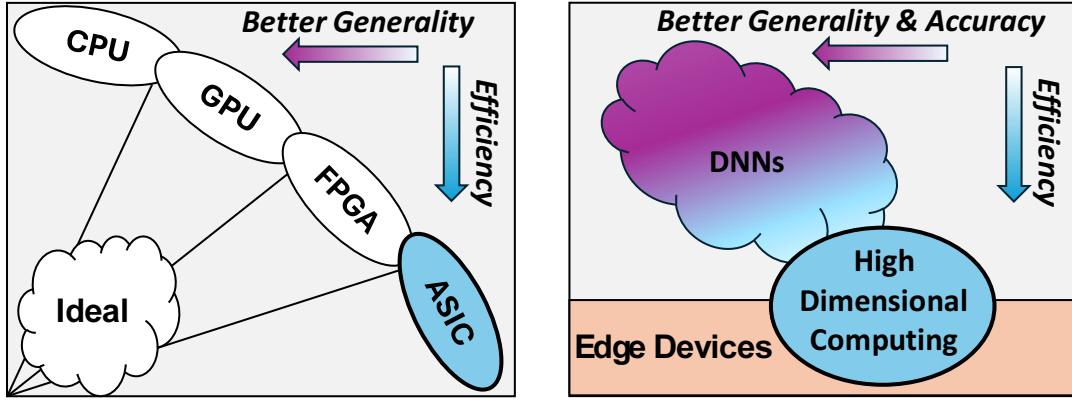

| 1.3 | (a) Generality and Energy Efficiency of Computing Architecture. (b) Generality/Accuracy and Efficiency of Computing Paradigm. . . . .                                          | 8  |

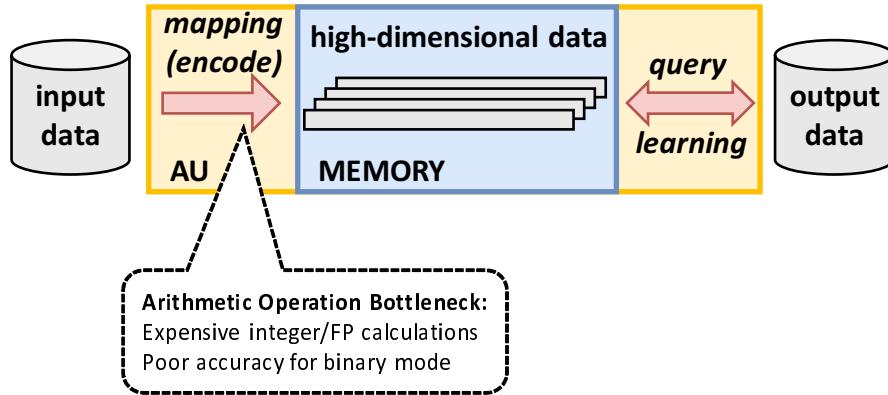

| 1.4 | Arithmetic Operations Challenges on High-Dimensional Computing. . .                                                                                                            | 9  |

| 1.5 | Memory Usage Challenges on High-Dimensional Computing. . . . .                                                                                                                 | 10 |

| 1.6 | Voltage Scaling Challenges on High-Dimensional Computing. . . . .                                                                                                              | 11 |

| 1.7 | Overview of the Challenges on High-Dimensional Computing. . . . .                                                                                                              | 12 |

| 1.8 | Solutions toward the Challenges on High-Dimensional Computing. . .                                                                                                             | 13 |

| 2.1 | Comparison of conventional DNN and Reservoir Computing (RC) system. .                                                                                                          | 18 |

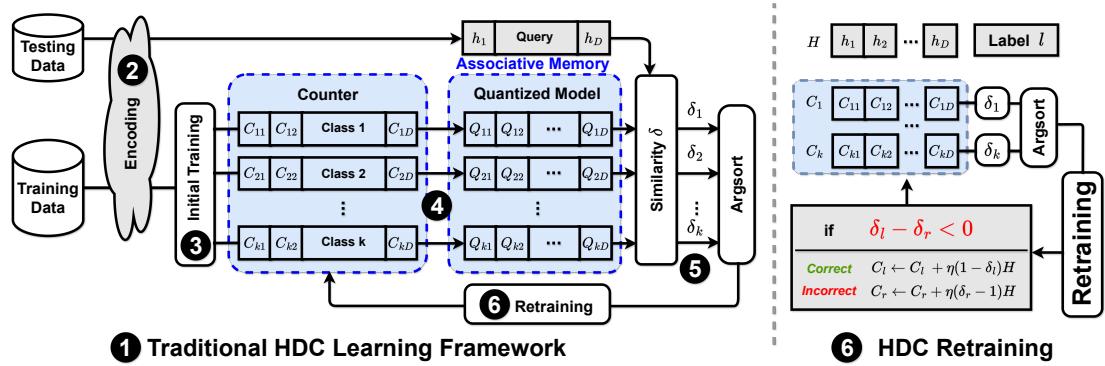

| 2.2 | (a) Overview of General HDC. (b) Retraining Process. . . . .                                                                                                                   | 21 |

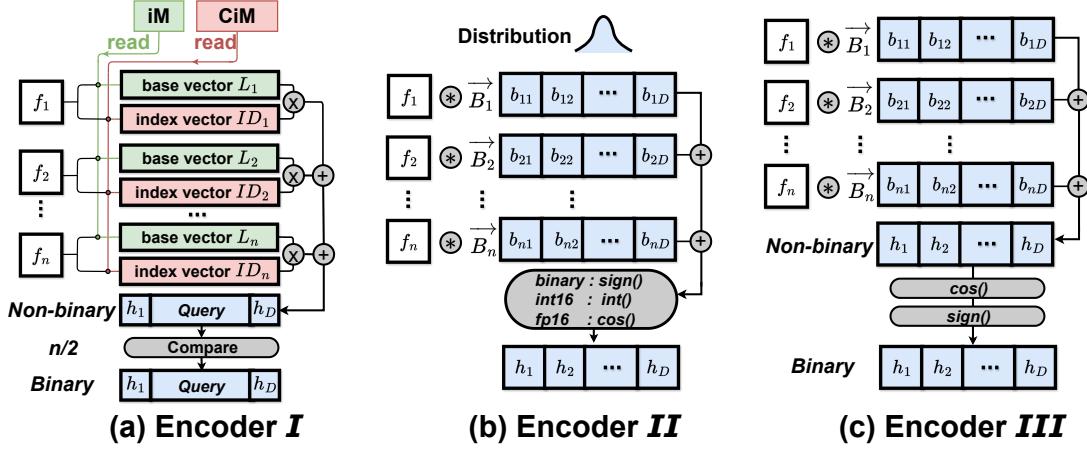

| 2.3 | Functionality of three popular encoders. . . . .                                                                                                                               | 22 |

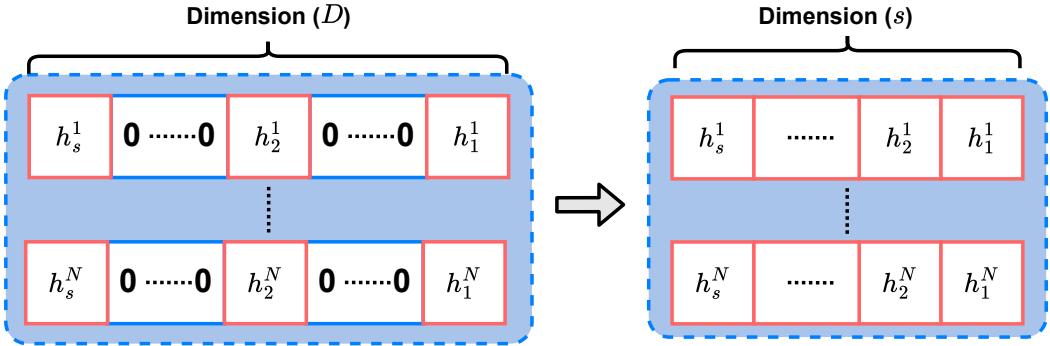

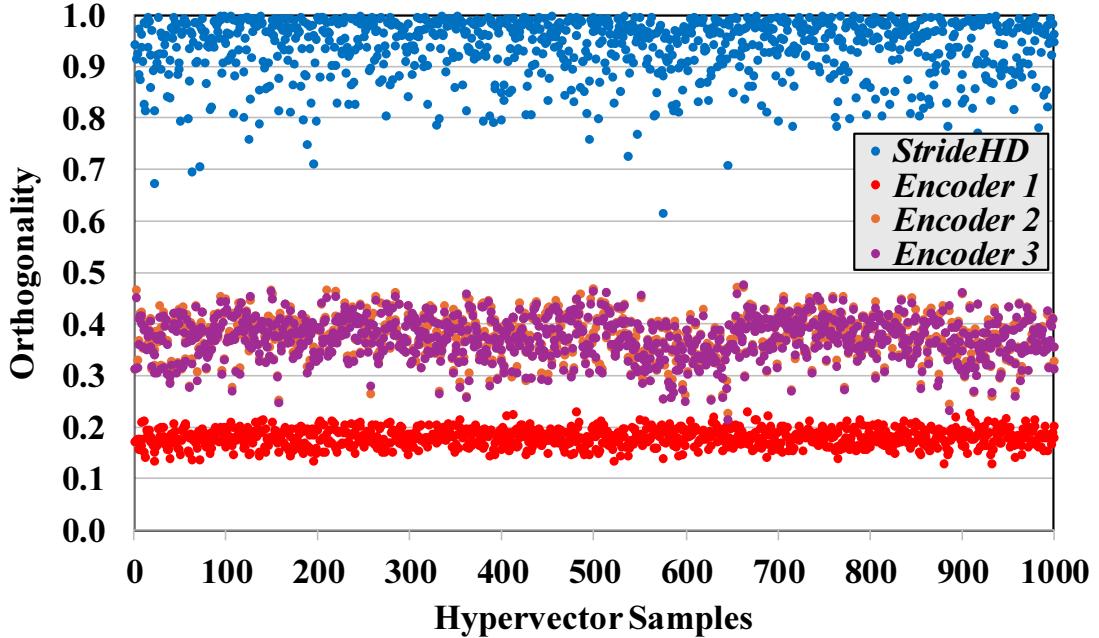

| 2.4 | Dimension-wise Model Sparsification in HDC System. . . . .                                                                                                                     | 25 |

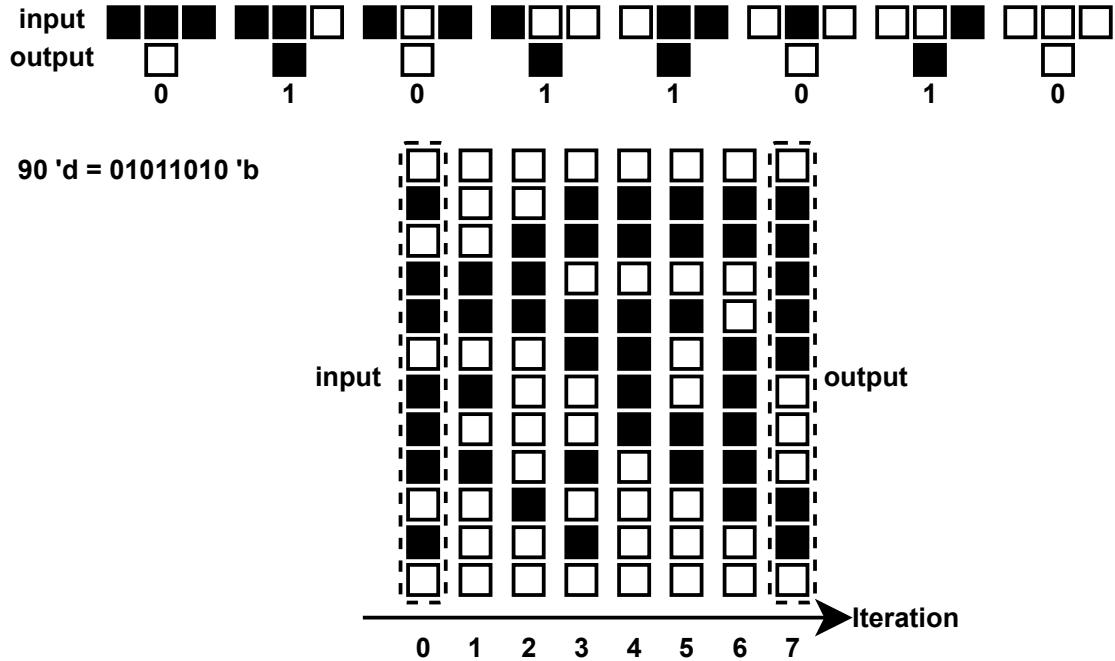

| 3.1 | Example of cellular automata evolution in Rule 90. . . . .                                                                                                                     | 35 |

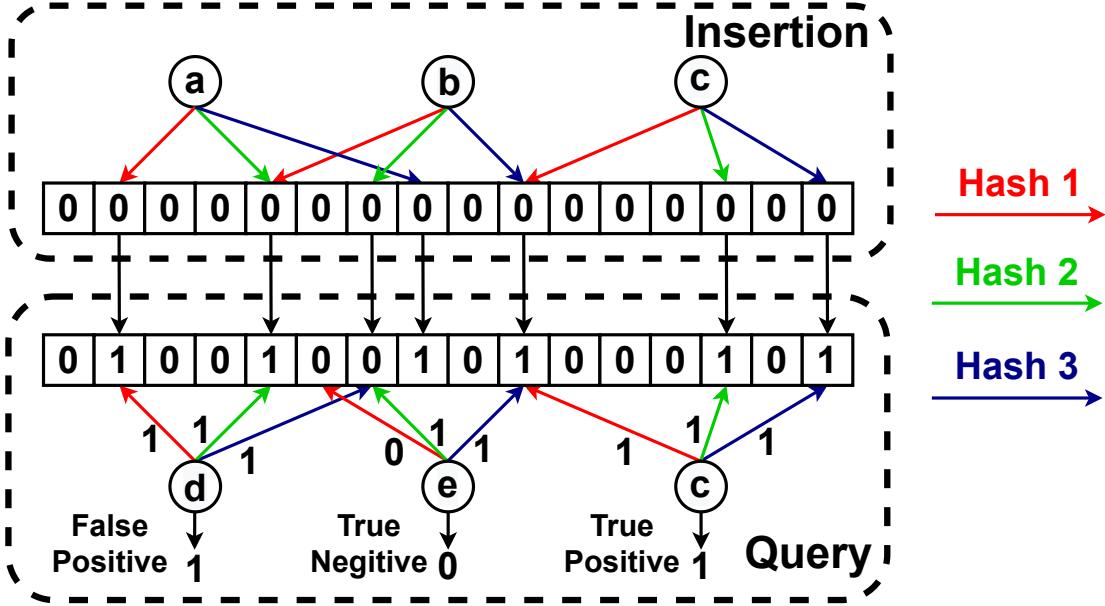

| 3.2 | Example of Bloom filter operations with a 16-bit array and three hash functions. . . . .                                                                                       | 38 |

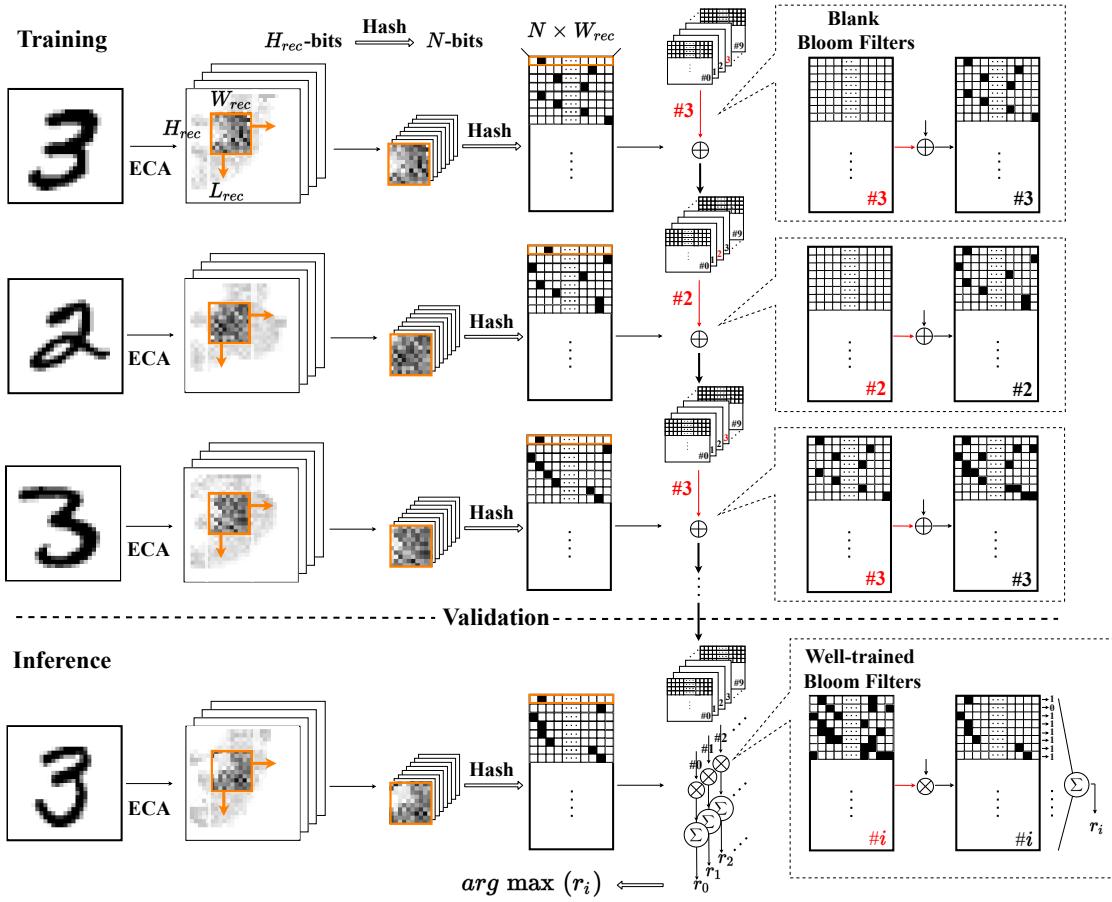

| 3.3 | Overview of the proposed <i>EnsembleBloomCA</i> . . . . .                                                                                                                      | 39 |

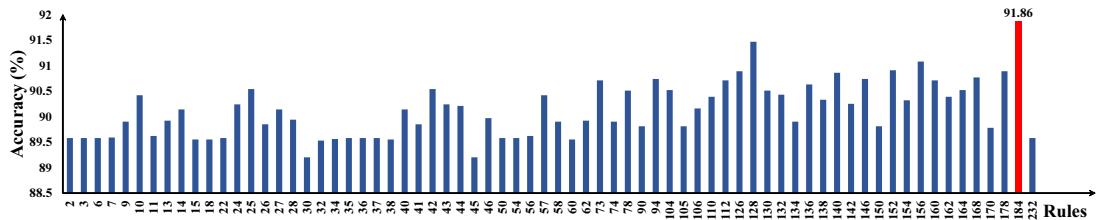

| 3.4 | Accuracy Performance applying different ECA rules. . . . .                                                                                                                     | 43 |

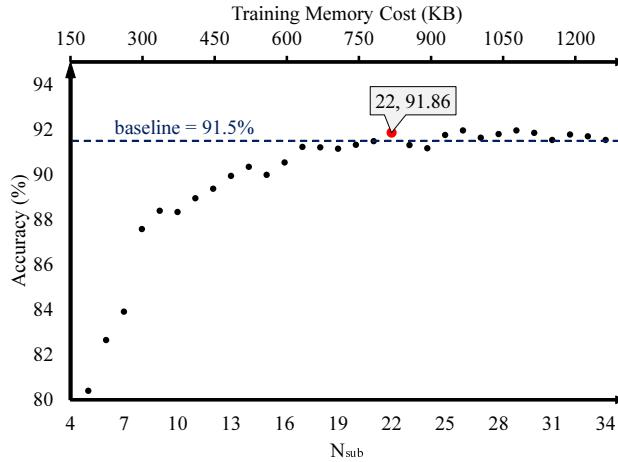

| 3.5 | Accuracy - $N_{sub}$ / Training Memory Cost. . . . .                                                                                                                           | 44 |

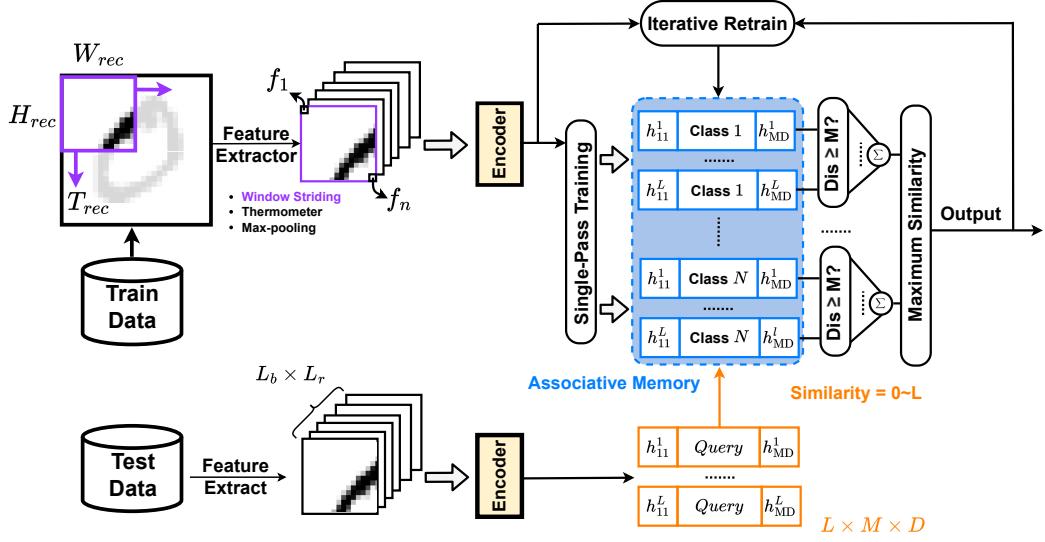

| 4.1 | Overview of the proposed <i>StrideHD</i> . . . . .                                                                                                                             | 51 |

| 4.2 | Overview of the proposed encoder in <i>StrideHD</i> . . . . .                                                                                                                  | 52 |

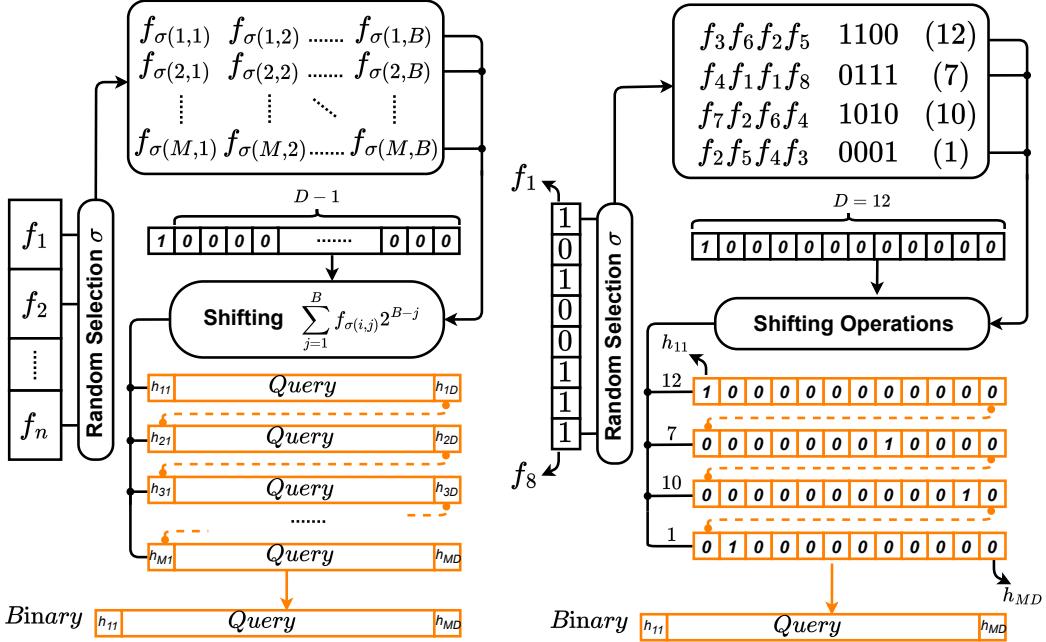

| 4.3 | Hypervector Orthogonality of different Encoders. . . . .                                                                                                                       | 53 |

| 4.4 | (a) Dimension-wise Sparsification. (b) Feature-wise Sparsification. . .                                                                                                        | 55 |

| 4.5 | The hardware implementation of <i>StrideHD</i> during inference includes Encoding, Associative Memory Blocks, AND Gates Array, and Nearest Distance Searching modules. . . . . | 57 |

|      |                                                                                                                                                                                                                       |    |

|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 4.6  | Impact of Different Parameters: (a) Length of Receptive Window. (b) Binary Levels $L_b$ . (c) Number of Training Subsets $L_e$ . (d) Dimensions $D$ . (e) Dimension-wise Sparsity. (f) Feature-wise Sparsity. . . . . | 60 |

| 4.7  | The comparison of accuracy and memory cost. . . . .                                                                                                                                                                   | 61 |

| 4.8  | Comparison of Iterative Retraining for <i>StrideHD</i> and Baseline HD models in different datasets. . . . .                                                                                                          | 63 |

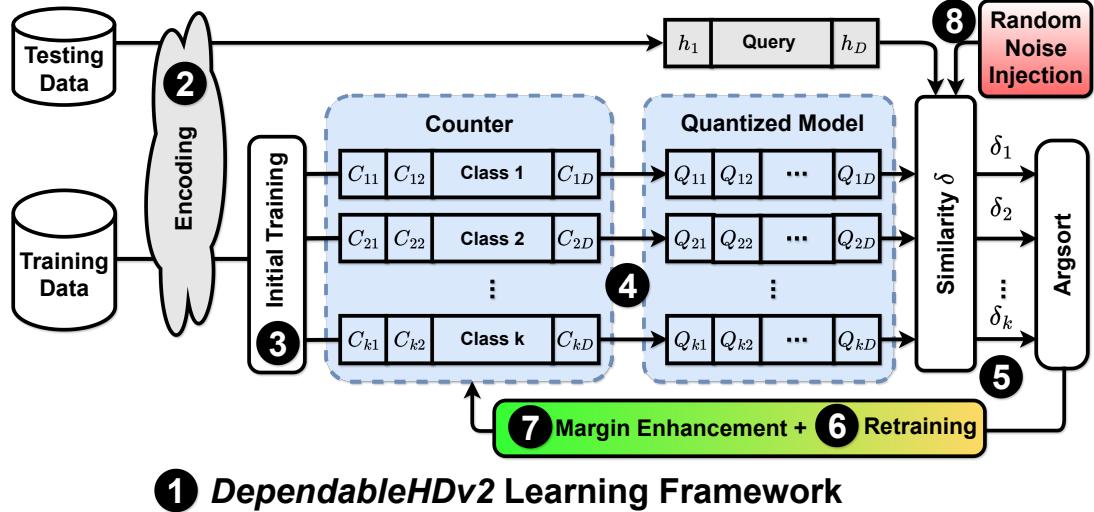

| 5.1  | Overview of DependableHD (v2) framework. . . . .                                                                                                                                                                      | 69 |

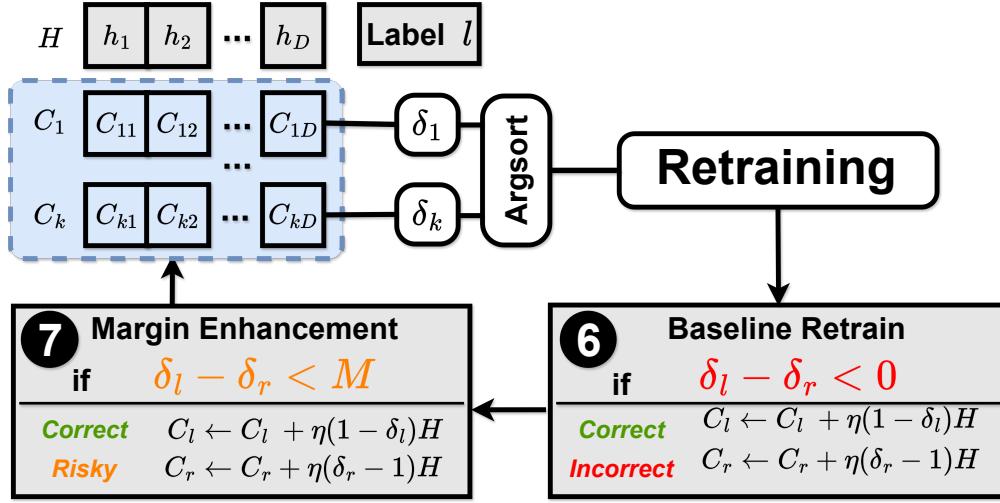

| 5.2  | Overview of Margin Enhancement technique during Retraining. . . . .                                                                                                                                                   | 70 |

| 5.3  | Impact of Margin Enhancement technique during Retraining. . . . .                                                                                                                                                     | 71 |

| 5.4  | Overview of Random Noise Injection technique during Retraining. . . . .                                                                                                                                               | 72 |

| 5.5  | Validation Accuracy during iterations. . . . .                                                                                                                                                                        | 72 |

| 5.6  | Overview of Dimension-swapping technique. . . . .                                                                                                                                                                     | 73 |

| 5.7  | Impact of $V_{DD}$ . . . . .                                                                                                                                                                                          | 78 |

| 5.8  | Impact of $D$ and precision. . . . .                                                                                                                                                                                  | 78 |

| 5.9  | Impact of Margin Enhancement Level $M$ . . . . .                                                                                                                                                                      | 79 |

| 5.10 | Impact of Random Noise Injection Level $R$ . . . . .                                                                                                                                                                  | 79 |

| 5.11 | Impact of Dimension-swapping technique. . . . .                                                                                                                                                                       | 80 |

| 5.12 | Accuracy of Binary <i>DependableHDv2</i> under different Supply Voltages. . . . .                                                                                                                                     | 83 |

## List of Tables

|     |                                                                                                                    |    |

|-----|--------------------------------------------------------------------------------------------------------------------|----|

| 2.1 | Arithmetic Comparison of HDC Encoders in the Previous Works. . . . .                                               | 24 |

| 2.2 | Inference Memory Occupations in popular HDC model BinHD. . . . .                                                   | 24 |

| 2.3 | Information about datasets covered by high-dimensional computing paradigms. . . . .                                | 27 |

| 3.1 | Performance Comparison. . . . .                                                                                    | 44 |

| 3.2 | Hardware Performance Comparison. . . . .                                                                           | 45 |

| 4.1 | Parameters Setting for <i>StrideHD</i> . . . . .                                                                   | 58 |

| 4.2 | Classification Accuracy Comparison between <i>StrideHD</i> and baseline HDC models for different datasets. . . . . | 62 |

| 4.3 | Hardware Performance Comparison. . . . .                                                                           | 64 |

| 5.1 | <i>DependableHDv2</i> Parameters Setup. . . . .                                                                    | 81 |

| 5.2 | Accuracy Loss Comparison. . . . .                                                                                  | 82 |

| 5.3 | Energy Consumption Comparison. . . . .                                                                             | 84 |

| 6.1 | Computational Characteristics and Accuracy Performance of Popular DNN Models. . . . .                              | 89 |

| 6.2 | Hardware Cost Comparison between DNN Accelerators and our Proposed Architectures. . . . .                          | 90 |

# Chapter 1

## Introduction

This dissertation aims to provide an energy-efficient architectural design of the high-dimensional computing paradigms for edge devices. This chapter provides the background of the research and the objectives of this dissertation. Section 1.1 introduces the background of AI applications for edge devices. Section 1.2 shows the motivation of high-dimensional computing paradigm. Section 1.3 describes the challenges for this research and points out issues preventing us from energy-efficient hardware implementation. Section 1.4 claims the goal of our research and the contribution of this thesis. Finally, the overall organization of this dissertation is presented in Section 1.5.

### 1.1 Background

Artificial intelligence (AI) has become a ubiquitous technology indispensable for personal daily life. Statistical data reveals that the investment in AI has incredibly grown in recent years, which could even burst in the coming decade [1]. Fig 1.1 shows that the AI market has grown to 208 billion USD by 2023, while the data forecast that the value would reach 1.85 trillion USD by 2030. Currently, the AI market covers a vast number of industries, such as IoT, supply chains, and product making, while more are fields that will in some aspect adopt artificial intelligence within their business structures. Chatbots, image/video generating AI, IoT, and mobile applications are all among the major trends improving AI in the near future.

Rather than serving as a replacement for human intelligence, AI should be considered a supporting tool for our society in the information era. The machine learning algorithms in AI applications can recognize objects and speech and have mastered games like chess, even surpassing human performance, e.g., DeepMind's AlphaGo Zero [2]. More and more AI-related companies are poised to play a crucial role in shaping the future economy and society. Taking the OpenAI as an example, it stands among the

Figure 1.1: The worldwide market size of Artificial Intelligence (AI) in 2021 with a forecast until 2030 (in billion U.S. dollars).

most well-funded machine learning related startups globally, having secured more than 12 billion USD in investments and recorded more than 100 million monthly active users as of 2023.

Deep neural network (DNN) has thrived and formed the foundation for many advanced machine learning algorithms in the AI applications due to its unmatchable performance. It contributes to unprecedented success in different AI tasks thanks to its outstanding accuracy and generality in several fields, e.g., image processing, computer vision, and natural language processing. In many of these domains, DNNs are now able to exceed human accuracy performance, which mainly comes from its ability to extract high-level features from raw sensory data after using statistical learning over a large amount of data to obtain an effective representation of an input space. This is different from earlier approaches that use hand-crafted features or rules designed by experts [3]. However, as DNNs grow in complexity, their associated energy consumption becomes a challenging problem when it comes to the implementation in edge devices like the Internet of Things (IoT).

Villalobos *et al.* study the tendency in model size of the popular and notable machine learning systems over time in Ref. [4]. A great increase shows in the size of machine learning models, measured in the number of free parameters that have to be fit to the data. Model size has become especially important as researchers have improved the understanding of scaling laws for language models, which govern how increases in model size and training data produce better performance. However, the rapid growth of model size and computing resource requirement also leads to the bottleneck of machine learning on edge devices. In general, DNNs have millions of parameters. For exam-

ple, a popular DNN model, AlexNet [5] has 60 million parameters and requires 249MB of inference memory and performs 1.5 billion high-precision operations to classify one image. More recently, it took seven months to train a DNN with 175 billion parameters, developed by OpenAI for natural language processing (NLP) [6]. The memory capacity of most edge devices is hard to store all data for large-size DNNs with hundreds of layers and millions of weights. Even applying the hardware-friendly implementation techniques to get the Binarized Neural Networks (BNNs) [7] or XNOR-Networks [8], still require considerably intensive computation costs due to the floating-point calculation and backpropagation algorithm during the training. The emergence of the IoT has led to a copious amount of small connected edge-oriented devices and systems [9], while most of these small edge-oriented systems do not have sufficient computing power to accomplish the sophisticated machine learning algorithms such as DNNs individually. The energy constraint of edge devices hinders them from the real-time training of neural network models [10].

In order to optimize the power dissipation of digital systems on edge devices, low-power methodology should be applied throughout the design process, which usually includes the system-level design, architecture-level design, and device-level design [11].

Regarding to the device-level design, one of the most practical ways of reducing the energy consumption for edge devices is to shrink the feature size of transistors, *i.e.*, the minimum length of the MOS transistor channel between the drain and the source. Moore’s law has been driving the semiconductor industry for over 50 years. With continuously scaling of technology node, the transistor count per die kept doubling in bi-annual pace [12–15]. Meanwhile, though clock frequency for single thread reached operation has reached a plateau around the year of 2006, it still keeps 15% to 20% increment per technology node generation [13, 16]. Following the ITRS2.0 (International Technology Roadmap for Semiconductors) and IRDS (International Roadmap for Devices and Systems) prediction [17, 18], to the 2030s, even for the low-power mobile devices, computing capability can increase 10 $\times$  within a decade. However, such a technology scaling trend pushes the future chip design to the power wall [14, 19, 20], because the increasing frequency and transistor count will eventually hit the physical limitations such as thermal dissipation limit and battery capacity limit [21]. Fig. 1.2 shows the trend data of the commercial microprocessor in terms of number of transistors and maximum working clock frequency, which are collected by M. Horowitz *et al.* in Ref. [12, 13]. Therefore, more and more researchers turn their attention to the exploration of system-level design and architectural design for driving the computer performance in the Post-Moore’s Era.

In terms of the architecture-level optimization, many designers needs to balance the trade-off between efficiency and generality base on the application scenario. Compared to the general-purpose Central Processing Units (CPUs), many AI applications

Figure 1.2: Trend Data of the Transistor Numbers and Maximum Clock Frequency in Microprocessor.

look to the Graphics Processing Units (GPUs) and Tensor Processing Unit (TPUs) as accelerator architectures. GPUs, initially designed for graphics rendering, have evolved into versatile processors capable of handling AI tasks due to their parallel processing strengths. For the TPUs developed by Google, they are specialized for AI computations, and offer optimized performance for many popular machine learning algorithms. When it comes to implementation on edge devices, the Application-Specific Integrated Circuits (ASICs) are customized for a particular use and leads to the extreme energy efficiency. Rather than intended for general-purpose use, ASICs are optimized to deliver the best performance for a specific application, making them incredibly efficient but inflexible compared to CPUs, GPUs, and TPUs. The co-design between system-level algorithms and architecture-level hardware implementation provides potential solution for the strict resource constraints on edge devices.

For the system-level design, the power reduction can be achieved through algorithm selection [11]. Cloud computing has emerged as one of the solutions to meet the hardware requirements of complex models. It has become increasingly common to deploy the ML algorithms like DNNs using cloud platforms, which are high-performance computing platforms with tremendous speed and memory. Training can be performed within a reasonable time on cloud machine learning platforms, where the servers provide large computational resources, large data storage, high-speed computation, low latency, and high availability. Cloud computing is also used to deploy DNNs for on-

line applications [22]. However, cloud computing also causes high latency and requires high transmission bandwidth and privacy security issues [23]. For example, in health care monitoring, we often require learning algorithms to have real-time control of the patient's daily behavior, speech, and bio-medical sensors. Sending all data points to the cloud, cannot guarantee scalability and real-time response, which is often undesirable due to privacy and security concerns [24]. On the other hand, edge computing aims at processing the information/data from edge devices with extreme limited resource constraints. For the specific scenario, the processing task with simple workload is requested on the edge devices, which makes it possible to run the light-weight model and finish the task on local devices. Hence, for running the machine learning algorithms on edge devices, we recognize the following technical challenges:

- **Sufficient performance for edge applications:** Although trade-offs may exist in machine learning algorithms between factors such as accuracy, speed, and resource consumption, maintaining high accuracy remains a primary objective when deploying AI solutions in real-life scenarios.

- **Limited hardware resources:** The embedded devices in IoT systems often do not have sufficient computing resources and memory capacity for the processing of sophisticated learning and big data applications. Running existing machine learning using traditional cores results in high energy consumption.

- **High robustness:** The technological and fabrication issues in highly scaled technology nodes add a significant amount of noise to the VLSI circuits. Most existing algorithms do not have the enough robustness to work with noisy devices while providing accurate results.

To address such challenges for edge devices, the demand for a more energy-efficient architectural design with the novel computing paradigms is crucially rising.

## 1.2 Motivation: High-Dimensional Computing

Classical computation can be interpreted as the computers embodied in the Turing/von Neumann paradigm. Nowadays it has been incredibly successful for information processing. However, the increased demand due to highly complex computational tasks has motivated the search for advanced unconventional computation. To achieve real-time performance with high energy efficiency, we need to rethink not only how we accelerate machine learning algorithms in hardware, but also we need to redesign the algorithms themselves using strategies that more closely model the ultimate efficient learning machine: *the human brain*. The nervous system in human brains carries out computation through elegant and sophisticated spatio-temporal dynamics [25]. The human brains are capable to process signals with excellent precision and power efficiency (the brain drains 20% of the body's energy [26, 27], which amounts to an overall power-consumption es-

timated at around 20 W). Such energy requirements are impressive compared to digital machines, which easily exceed 100 W during inference and several kilowatts during the training of traditional DNNs. Motivated by the observation that the human brain operates on high dimensional representations of data originated from the large size of brain circuits [28], computational neuroscientists begins the exploration of modeling memory of human brain. In the high-dimensional computing (e.g., reservoir computing, hyper-dimensional computing), human memory are modeled by mapping input data points to the representation in high-dimensional space, while the important functionalities of human brain are referred by the well-defined vector operations.

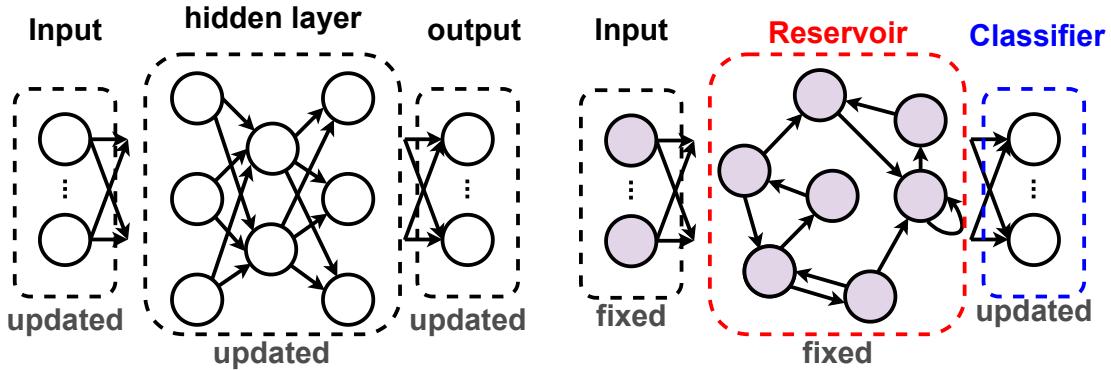

Reservoir computing (RC), first applied to temporal signal processing, is a recurrent neural network in which neurons are randomly connected. Once initialized, the connection strengths remain unchanged. These fixed and nonlinear hidden layers are generally referred to as the *reservoir* part, which can map the original input data into a higher-dimensional feature space. On the other hand, the output layer is considered as a *classifier*. The model's rich dynamics, linear separability, and memory capacity then enable a simple linear readout to generate adequate responses for various applications [29]. Compared with conventional DNNs, RC systems use fixed weights in the input and hidden layers and only modify the weights of the output layer in the training process [30]. Because most of the weights can be fixed during training and inference, they can be implemented using hardwired logic and thus do not require memory circuits. Hence, RC is considered to be a promising alternative to replace DNNs, the model size of which continues to increase exponentially [31].

Hyperdimensional computing (HDC) is a strategy developed by computational neuroscientists as a model the human short-term memory. HDC is motivated by the understanding that the human brain operates on high dimensional representations of data originated from the large size of brain circuits. It models the human memory using points of a high-dimensional space, called *hypervectors*. The hyperspace typically refers to tens of thousand dimensions. HD mimics several important functionalities of the human memory model with vector operations which are computationally tractable and mathematically rigorous. HDC models are computationally efficient with high parallelism and amenable to hardware level optimization. It offers a complete computational paradigm that can be applied to cognitive as well as learning problems. Meanwhile, it provides strong robustness to noise and naturally enable secure and lightweight learning, which makes it a promising solution for today's edge devices with limited storage, battery, and resources, as well as future computing systems in deep nano-scaled technology which devices will have high noise and variability.

On one hand, both of RC and HDC have been widely explored by many researchers. These two kind of systems are connected by several similar core principles in the current studies: (i) Random projections of input values onto a reservoir (which in essence

is a high-dimensional vector) matches random HDC representations stored in a superposition. (ii) The update of the reservoir by a random recurrent connection matrix is similar to HDC adding/shifting operations. (iii) The non-linearity of the reservoir can be approximated with the thresholded addition of integers in HDC. Therefore, both of RC and HDC can be considered as high-dimensional computing paradigms.

On the other hand, the focus of these two types of computing systems might be different for the current studies. For the RC system using reservoirs based on physical phenomena has recently attracted increasing interest in many research areas. Various physical systems, substrates, and devices have been proposed for realizing RC. A motivation for physical implementation of reservoirs is to realize fast information processing devices with low learning cost. Regarding the HDC system with massive parallelism and simple arithmetic, different kinds of training strategies and architectures have been proposed for the scope of energy-efficient and ultra-low-latency computing, especially with the rise of emerging hardware.

As frameworks for neural symbolic representation, computation, and analogical reasoning, there are two main advantages for the high-dimensional computing paradigms compared to the conventional DNN architectures: (i) Only some of the parameters are required to be trained, while the rest can be fixed. (ii) The complex data structures and analogical reasoning are implemented by simple arithmetical operations, e.g., binding, addition/bundling, and permutation, and a well defined similarity metric. Owing to these unique features, the RC systems and HDC systems can be implemented with limited hardware resources.

Besides the novel computing paradigm, the voltage-scaling is also one of the classic low power design methodologies for energy efficiency improvement in device-level. In typical circuits, the dominant source of energy consumption is a dynamic energy consumption which is consumed when Complementary MOS (CMOS) circuits charge or discharge load capacitors. Since the dynamic energy consumption is quadratically proportional to the supply voltage, the low voltage operation is a good choice to reduce the power and energy dissipation at the cost of degrading the computational power [32]. Although it also brings challenges to fully guaranteeing stable operation in the circuits, the natural robustness of HDC provides the room for the systems to tolerate the hardware error issues induced by voltage-scaling.

Therefore, in order to achieve practical machine learning on edge devices, we propose utilizing high-dimensional computing paradigm with energy-efficient architectural design, which includes three techniques from different design level: (i) reservoir computing for light-weight implementation, (ii) hyper-dimensional computing for energy reduction, and (iii) voltage-scaling for low power design. The literature review and preliminaries of these techniques are discussed in the Chapter 2.

Figure 1.3: (a) Generality and Energy Efficiency of Computing Architecture. (b) Generality/Accuracy and Efficiency of Computing Paradigm.

### 1.3 Challenges toward High-Dimensional Computing

Fig. 1.3 shows the research target area of this thesis. Fig. 1.3(a) shows the generality and energy efficiency of different computing architectures. CPUs are the most general computing architecture. However, their computing efficiency is not sufficient for some edge computing scenarios. Other popular architectures are GPUs and FPGAs at the cost of degrading the generality, while ASICs are the most efficient device for specific dedicated purposes. From the viewpoint of edge computing, ASICs are a suitable candidate for lightweight specific purposes in edge computing. Fig. 1.3(b) shows the generality/accuracy and energy efficiency of different computing paradigms. Here the generality intents to represent the ability of handling multi-task. Many other popular machine learning algorithms (e.g., multi-task learning) has been emerged as a powerful paradigm in deep learning to obtain language and visual representations from large-scale data [33]. By leveraging supervised data from related tasks, these approaches reduce the expensive cost of curating the massive per-task training data sets needed by deep learning methods and provide a shared representation which is also more efficient for learning over multiple tasks. When targeting the scenarios with multiple tasks, the current researches about high-dimensional computing paradigms are still lack of convincing performance in terms of generality. Most high-dimensional computing paradigms are focusing on the energy efficiency and robustness improvement. The ability of handling single task with wide coverage is sufficient for the scenarios on edge devices. The DNNs are very powerful but energy consuming, which may not be suitable for the edge computing scenario. Therefore, this thesis targets high-dimensional computing with ASICs as a potential solution for the edge computing scenario. This section describes challenges toward high-dimensional computing.

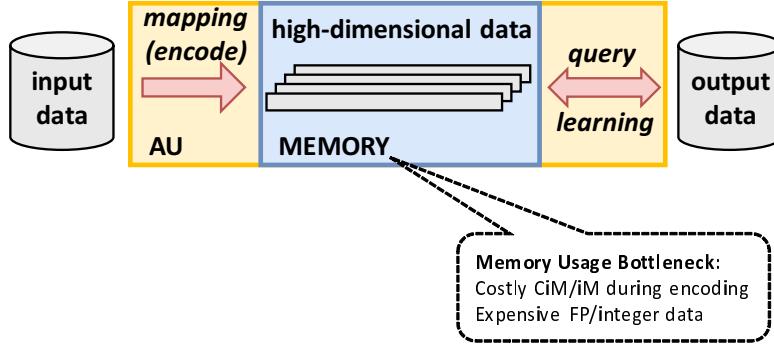

Figure 1.4: Arithmetic Operations Challenges on High-Dimensional Computing.

### 1.3.1 Elimination of Expensive Arithmetic Operations

Although the high-dimensional computing is a promising alternative for drastically reducing the computational burden compared to the traditional machine learning methods, the trade-off between accuracy performance and arithmetic precision still exists. From the circuit designer's point of view, it is important to reduce the hardware cost while maintaining accuracy performance. The arithmetic operations challenges on high-dimensional computing paradigms are diagrammed in Fig. 1.4. For high-dimensional computing, the hardware cost of arithmetic operations is affected by the precision of elements in the model. Although applying the precised FP calculation on high-dimensional computing can improve the accuracy performance, it also brings heavy computational burden to the edge devices.

For example, Ref. [34] select the most accurate cellular automata rules to represent the reservoir structure, which can easily be reproduced using a set of XOR gates and shift registers. They achieve a high-performance alternative for RC hardware implementation in terms of circuit area, power, and system accuracy, which can be considered as a low-cost method to implement fast pattern recognition digital circuits. However, this model exploits the softmax function as its classifier, which still requires expensive floating-point (FP) calculations; hence, it is not suitable for implementation on resource-constrained edge devices. For [35], authors utilize a random forest algorithm as the classifier, which avoids the costly FP calculation during the inference but also brings higher consumption for the training.

Similarly, in some HDC works, it is common to utilize hypervector with high-precision elements for accuracy improvement. In Ref. [36–41], authors need to encode data points to hypervectors with non-binary elements, *i.e.*, storing integer or FP value for each element. This leads to the high memory requirement and expensive computational cost. To reduce the inference cost, Rahimi *et al.* [42] and Imani *et al.* [24] propose bina-

Figure 1.5: Memory Usage Challenges on High-Dimensional Computing.

rizing the elements of class hypervectors after the training. Although these approaches can simplify the inference similarity matrix to Hamming distance and lead to a faster computation speed, it comes with the cost of significantly degraded HD classification accuracy on practical image recognition applications. For instance, Imani *et al.* [40] proposed a HDC model for face image classification task. If the model is binarized, the accuracy performance sharply decreases to 38.9%, which is far lower than the non-binarized mode. Since the frequent use of floating-point and integer calculations makes the hardware implementation challenging, the elimination of expensive arithmetic operations while maintaining accuracy performance becomes a must.

### 1.3.2 Memory Efficient High-Dimensional Computing

The high-dimensional computing paradigms need to ensure that the model has the separation capacity so that the no-linear mapping operations allow to differentiate different input signals. The performance of the computing paradigms usually related to how well the model separates the input signals, i.e. whether sufficiently different input signals become linearly separable in the high-dimensional space. The stronger a model's separation capacity, the larger the set of functions that it can approximate, which generally increases with the size of the no-linearity of networks, and also grows with larger memory capacity. The memory efficiency challenges on high-dimensional computing paradigms are diagrammed in Fig. 1.5. For high-dimensional computing, the input data points are mapped into the high-dimensional space in a fixed and no-linear way, which usually takes huge memory usage. Also, to storage the universal information in high-dimensional space, the hardware cost sharply increase when utilizing high-precision elements.

For example, Ref. [43, 44] adopts the bloom filters as the classifier in the RC system, which is a space-efficient probabilistic data structure aimed at approximate member queries. Such structure is capable of eliminating the costly FP calculations and characterized by its simple implementation in both software and hardware. However, the large

Figure 1.6: Voltage Scaling Challenges on High-Dimensional Computing.

amount of memory required remains as the bottleneck for its application, which makes it impractical when used for a portable device or hardware-resource-constrained system. Also, in many of the popular HDC models [36–42, 45], they need to represent the index and value of the input features via hypervectors, which requires a large size of memory blocks. Such a process takes huge occupation of the total inference memory cost, e.g., 96.15% for a letters recognition task. Therefore, the demand of memory efficiency improvement is crucially rising for the high-dimensional computing paradigms.

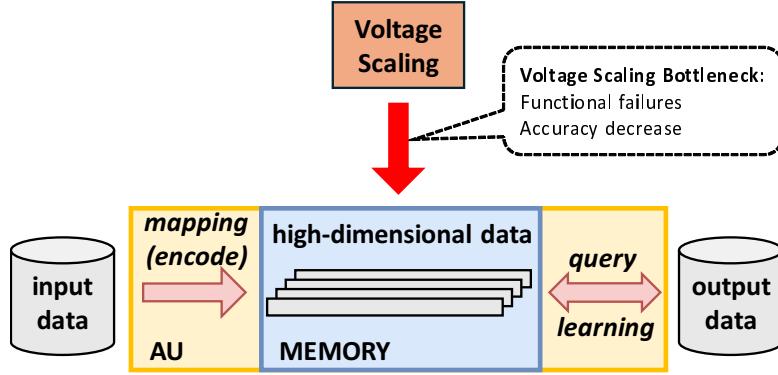

### 1.3.3 Model Robustness in the Low Voltage Operation

The voltage scaling challenges on high-dimensional computing paradigms are diagrammed in Fig. 1.6. The aggressively scaled voltage operation poses the further requirement of model robustness. Energy consumption in circuits largely results from the charging and discharging of internal node capacitances and can be reduced quadratically by lowering supply voltage ( $V_{DD}$ ). Ref. [46] achieved  $4.7\times$  energy consumption reduction by scaling down the voltage to the near-threshold voltage region compared with the nominal voltage operation. The near-threshold voltage region is a voltage region where the supply voltage is downscaled to near the threshold voltage of the transistor. If we further downscale the supply voltage, the minimum energy voltage can be found in the sub-threshold region [47], where the supply voltage is reduced below the threshold voltage of the transistor [48]. However, low-voltage designs may suffer from functional failures due to various causes, e.g., soft errors, aging, and processing variation. As a result, such functional failures might eventually result in the degradation of performance on edge devices.

A key attribute of high-dimensional computing is its robustness to the imperfections associated with the computational substrates on which it is implemented. It is therefore particularly amenable to emerging non-von Neumann approaches such as in-memory computing, where the physical attributes of nanoscale memristive devices are exploited

Figure 1.7: Overview of the Challenges on High-Dimensional Computing.

to perform computation [49]. Many works have indicated and explored the robustness of HDC learning framework. Ref. [42, 50] proposed a robust HDC that can tolerate approximately  $5 \times 10^{-7}$  probability of failure of memory cells while maintaining accuracy. Compared to the conventional DNNs architecture, the robustness of high-dimensional computing not only brings the advantage toward the future computing systems in deep nano-scaled technology which devices will have high noise and variability but also provides the potential for voltage-scaling on edge devices [51–54]. However, it is still far away from the prior solution to serious memory failure issues induced by scaling down the voltage to the sub-threshold region. For example, if the supply voltage of 65nm SRAM cells are scaled down from normal value (1.2V) to 500mV, the typical failure probability sharply increases from  $\sim 10^{-7}$  to 4% due to the process variations [55, 56]. Therefore, a further development of model robustness is necessary for applying aggressive voltage-scaling technique on edge devices.

## 1.4 Research Goal and Thesis Contribution

### 1.4.1 Research Target

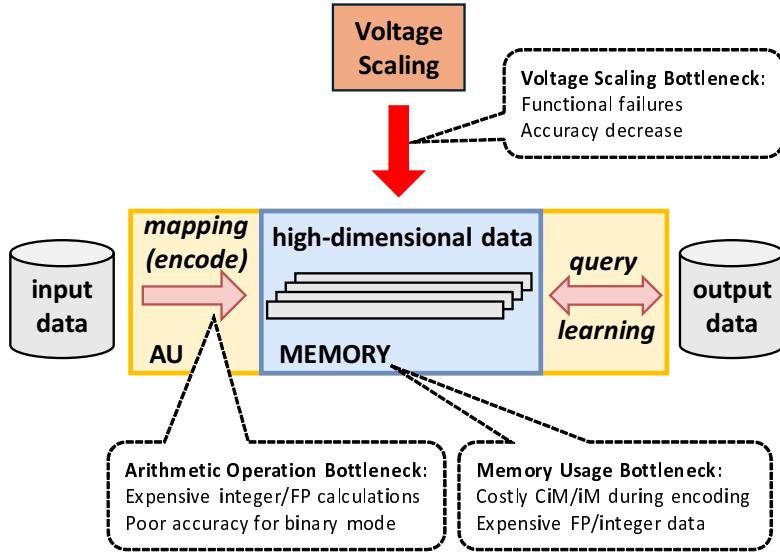

The goal of this thesis is to improve the energy efficiency for the architectural design of high-dimensional computing. Although the high-dimensional computing paradigm is a promising approach for the implementation on edge devices, its application still suffers from the expensive arithmetic operations, huge memory cost, and insufficient robustness against the aggressive voltage-scaling. The overall challenges on high-dimensional

Figure 1.8: Solutions toward the Challenges on High-Dimensional Computing.

computing paradigms are diagrammed in Fig. 1.7. The following requirements should be met for achieving energy-efficient high-dimensional computing architecture on edge devices:

1. Capability of hardware-friendly arithmetic operations,

2. Architecture with high memory efficiency, and

3. Model robustness in against to functional failures in voltage over-scaling.

From the circuit designer's point of view, the first two items are considered as universal and key indicators. The high-dimensional computing paradigm needs the capability to choose the appropriate arithmetic operations for different scenarios. Although the application of voltage-scaling has been widely studied, how to utilize model robustness to tolerate the functional failures induced by aggressive voltage-scaling is still the open problem.

### 1.4.2 Thesis Contribution

To pursue the research target, this thesis presents an RC system with extreme hardware efficiency, an HDC system with competitive accuracy performance and memory efficiency, as well as the strategies overcoming the functional failures when applying voltage over-scaling. The solutions toward the challenges on high-dimensional computing paradigms are diagrammed in Fig. 1.8. The contribution of this thesis is summarized below.

- ***EnsembleBloomCA: An RC System for Light-weight Implementation***

Reservoir computing (RC) is an attractive alternative to machine learning models owing to its computationally inexpensive training process and simplicity. In this thesis, we propose *EnsembleBloomCA*, which utilizes cellular automata (CA) and an ensemble Bloom filter to organize an RC system. In contrast to most existing RC systems, *EnsembleBloomCA* eliminates all floating-point calculation and integer multiplication. *EnsembleBloomCA* adopts CA as the reservoir in the RC system because it can be implemented using only binary operations and is thus energy efficient. The rich pattern dynamics created by CA can map the original input into a high-dimensional space and provide more features for the classifier. Utilizing an ensemble Bloom filter as the classifier, the features provided by the reservoir can be effectively memorized. Our experiment revealed that applying the ensemble mechanism to the Bloom filter resulted in a significant reduction in memory cost during the inference phase. In comparison with *Bloom WiSARD*, one of the state-of-the-art reference work, the *EnsembleBloomCA* model achieves a  $43\times$  reduction in memory cost while maintaining the same accuracy. Our hardware implementation also demonstrated that *EnsembleBloomCA* achieved over  $23\times$  and  $8.5\times$  reductions in area and power, respectively.

Such architecture is suitable for scenarios targeting medium-level tasks with extremely strict resource constraints. Because it can eliminate the costly arithmetic operations, supporting the hardware-friendly bit-wise operations for extreme energy efficiency. With around 18 KB memory usage, 91.9% classification accuracy is achieved for the handwritten number recognition task, which can be considered as a practical solution for edge devices with extremely limited hardware resources.

- ***StrideHD: A Memory Efficient HDC System***

Hyper-Dimensional (HD) computing is a brain-inspired learning approach for efficient and fast learning on today's embedded devices. Although HDC achieved reasonable performances in several practical tasks, it comes with huge memory requirements since the data point should be stored in a very long vector having thousands of bits. To alleviate this problem, we propose a novel HDC architecture, called *StrideHD*. By utilizing the window striding in image classification, *StrideHD* enables HDC system to be trained and tested using binary hypervectors and achieves high accuracy with fast training speed and significantly low hardware resources. *StrideHD* encodes data points to distributed binary hypervectors and eliminates the expensive Channel item Memory (CiM) and item Memory (iM) in the encoder, which significantly reduces the required hardware cost for inference. Our evaluation also shows that compared with two popular HD algorithms, the single-pass *StrideHD* model achieves a  $27.6\times$  and  $8.2\times$  reduction in inference memory cost without hurting the classification accuracy, while the iterative mode further provides  $8.7\times$  memory efficiency. Under the same inference memory cost,

our single-pass mode *StrideHD* averagely achieves 13.56% accuracy improvement in comparison with the single-pass baseline HD, which is a similar performance even in comparison with the costly iterative baseline HD models. As an extension, the iterative retraining mode of *StrideHD* averagely provides 11.33% accuracy improvement to its single-pass mode, which can be accomplished in fewer iterations in comparison with the baseline HD algorithms. The hardware implementation also demonstrates that *StrideHD* achieves over 9.9 $\times$  and 28.8 $\times$  reduction compared with baseline in area and power, respectively.

This architecture is suitable for scenarios with limited resources and facing complex datasets. It supports elements in fp16, int16, and binary format. The wide range of element precision provides sufficient room for the customers to select the appropriate strategy. The single pass mode training can achieve acceptable accuracy performance, while the iterative training mode can further provide 13% accuracy improvement. Even for the recognition tasks in complicated levels, a competitive accuracy is achieved while maintaining 8.7 $\times$  memory efficiency.

- ***DependableHDv2: A Robust HDC System for Voltage-scaled Circuits***

Voltage scaling is one of the most promising approaches for energy efficiency improvement but also brings challenges to fully guaranteeing stable operation in modern VLSI.

To tackle such issues, we firstly developed a *DependableHD* framework, which aims to improve the robustness of HDC in against to the functional failures induced by voltage-scaling. Targeting the stuck-at errors of SRAM cells in low voltage region, we extend the *DependableHD* to the second version *DependableHDv2* for further improvement in HDC robustness. *DependableHDv2* introduces the concept of margin enhancement for model retraining and utilizes noise injection to improve the robustness, which is capable of application in most state-of-the-art HDC algorithms. We additionally propose the dimension-swapping technique, which aims at handling the stuck-at errors induced by aggressive voltage scaling in the memory cells. Our experiment shows that under 8% memory stuck-at error, *DependableHDv2* exhibits a 2.42% accuracy loss on average, which achieves a 14.1 $\times$  robustness improvement compared to the baseline HDC solution. The hardware evaluation shows that *DependableHDv2* supports the systems to reduce the supply voltage from 430mV to 340mV for both item Memory and Associative Memory, which provides a 41.8% energy consumption reduction while maintaining competitive accuracy performance.

It is suitable for scenarios with an extremely unreliable and noisy situation. Such architecture and design strategy can tolerate more than a 10% memory error for the medium-level task. Exploiting this advantage, aggressive voltage downscaling can be applied to the systems. Note that both of margin enhancement and

random noise injection techniques in this model focus on the retraining phase, which means it can be easily applied to other HDC architectures simultaneously for robustness improvement.

## 1.5 Thesis Organization

This thesis is organized in the following way. In Chapter 2, we present the literature survey and preliminaries relating the energy-efficient computing paradigms and the low power design methodology, *i.e.*, reservoir computing (RC), hyper-dimensional computing, and voltage-scaling. In Chapter 3, this thesis presents an RC system with extreme hardware efficiency, which utilize cellular automata and ensemble Bloom Filter. Chapter 4 presents a binary HDC system utilizing window striding for image classification. Chapter 5 presents the strategies overcoming the functional failures when applying voltage over-scaling in HDC system. Chapter 6 concludes this thesis.

# Chapter 2

## Literature Review and Preliminaries on High-Dimensional Computing

This chapter provides the literature review and preliminaries for this dissertation. Section 2.1 and 2.2 introduces the reservoir computing (RC) system and hyper-dimensional computing system, while both of these two computing paradigms aim to map the input data into high-dimensional space and can be considered as the energy-efficient alternatives. Section 2.3 shows the basic of voltage-scaling, which is a classic and promising low power design methodology. Finally, a summary of these techniques is presented in Section 2.4.

### 2.1 Reservoir Computing

#### 2.1.1 Basics of Reservoir Computing

Reservoir Computing (RC) can be considered as a potential candidate of the energy-efficient computing paradigms for edge devices. Fig. 2.1 shows a structural comparison between conventional DNN models and RC systems. The most critical advantage of RC is that only some of the parameters are trained, while the rest can be fixed. Owing to this unique feature, RC can be implemented with limited hardware resources, that is, fixed weights can be realized using hardwired logic. RC circumvents the difficulty of learning a number of RNN parameters, which has been successfully applied in numerous fields such as robot control [57] and image/video processing [58]. More recently, echo state networks [59] and liquid state machines [60] have been proposed for the use in different research domains. These technologies are collectively referred to as RC because both have a component called a *reservoir* [61]. The fixed and nonlinear hidden layers are generally referred to as the *reservoir* part, which can map the original input data into a higher-dimensional feature space. Meanwhile, the output layer is considered as a

Figure 2.1: Comparison of conventional DNN and Reservoir Computing (RC) system.

classifier.

Compared with conventional neural networks, RC systems use fixed weights in the input and hidden layers and only modify the weights of the output layer in the training process [30]. Because most of the weights can be fixed during training and inference, they can be implemented using hardwired logic and thus do not require memory circuits. Hence, RC is considered to be a promising alternative to replace DNNs, the model size of which continues to increase exponentially [31]. The state of each node is updated over  $M$  steps according to a nonlinear mapping  $F$ , which aims to map the low-dimensional input signal into the high-dimensional feature space as follows:

$$x_i(k) = F[\mathbf{x}(k-1), \mathbf{u}(k-1)]. \quad (2.1)$$

Here,  $x_i(k)$  is the state of the  $i$ -th node at time step  $k$ , where  $i \in \{1, 2, \dots, N\}$  and  $k \in \{1, 2, \dots, M\}$ .  $\mathbf{x}(k) = \{x_1(k), x_2(k), \dots, x_N(k)\}$  is the  $N$ -dimensional node state vector. Further,  $\mathbf{u}(k) = \{u_1(k), u_2(k), \dots, u_N(k)\}$  is the  $N$ -dimensional input vector, where  $u_i(k)$  is the input to the  $i$ -th node at step  $k$ . As Eq. (2.1) shows, the state of node  $x_i(k)$  depends on the previous state  $x_i(k-1)$  and input  $u_i(k-1)$ .

Note that the weights in the reservoir, which represents the nonlinear mapping, can be fixed during training and inference. Hence, the reservoir can be implemented using hardwired logic, which contributes to a reduction in hardware resources. However, the nonlinear mapping still requires floating-point computations, which may lead to constraints when considering the implementation of RC in portable devices. To eliminate floating-point computations in the reservoir, several studies [34, 35, 62] have proposed exploiting cellular automata (CA) as an alternative components to traditional reservoirs, which are summarized in the following Subsection 2.1.2.

### 2.1.2 Suitable Components for Hardware Implementation

The key idea of RC is to map the input to a higher-dimensional space to facilitate the classification. As the basic components of the RC system, various methods have been proposed to perform the *reservoir* and *classifier*. The following techniques are commonly used because they are considered suitable for hardware implementation.

#### Cellular Automata

To reduce the massive usage of arithmetic units, the use of cellular automata (CA) has been proposed as a promising alternative to reservoirs [35]. A CA consists of multiple cells aligned in a one-dimensional array, where each cell takes two possible discrete states (“1” or “0”) and evolves in discrete time steps. This evolution process is guided by specific rules and interactions between the nearest neighbors. With rich pattern dynamics, which makes CA very well suited to the hardware implementation of reservoir structures. The CA is a discrete computational model consisting of a regular grid of cells, each in one of a finite number of states. The state of an individual cell evolves in time according to a fixed rule, depending on the current state and the states of its neighbors. CA governed by certain rules have been proven to be computationally universal, that is, capable of simulating a Turing machine [63].

Ref. [34, 62] perform exhaustive studies of the performance of different CA rules when applied to pattern recognition of time-independent input signals using an RC scheme. Nichele *et al.* [62] evaluates the model on a 5-bit task, which is insufficient for the complicated application field. Moran *et al.* [34] selects the most accurate CA rules to represent the reservoir structure, which can easily be reproduced using a set of XOR gates and shift registers. They achieve a high-performance alternative for RC hardware implementation in terms of circuit area, power, and system accuracy, which can be considered as a low-cost method to implement fast pattern recognition digital circuits. However, this model exploits the softmax function as its classifier, which still requires FP calculations; hence, it is not suitable for implementation on resource-constrained devices. Lopez *et al.* [35] utilizes a random forest algorithm as the classifier, which avoids the costly FP calculation during the inference but also brings higher consumption for the training.

#### Bloom Filter

Bloom filters (BFs) are probabilistic data structures that represent a set as a small bit array allowing the occurrences of false positives, i.e., in a Bloom filter, an element can be incorrectly classified as a member of a set when it is not. Such memory-oriented classifiers for pattern recognition are typically very simple and can be easily implemented in hardware and software.

In [44], *Bloom WiSARD* was presented as an optimized framework that utilizes the BFs in a memory-segment way. Compared with the standard BFs, this model significantly reduces the memory requirement to some extent at the cost of allowing false positives and shows practically useful performance in image recognition tasks. The elimination of FP calculation and fast single-pass training are important advantages of *Bloom WiSARD* in terms of hardware efficiency. However, a large amount of memory required remains a key bottleneck. Take the MNIST classification task [64] as an example, when the false positive rate is 10%, the memory requirement is over 800MB for the inference implementation. It makes the adoption of *Bloom WiSARD* impractical for use in portable devices or memory-constrained systems.

## 2.2 Hyper-Dimensional Computing

### 2.2.1 Basic of Hyper-Dimensional Computing

HDC is a computing paradigm involving long vectors with dimensionality in the thousands, which are called hypervectors. In high-dimensional space, there are several nearly orthogonal hypervectors. HDC exploits well-defined vector operations to combine these hypervectors, while also preserving most of the information of the hypervectors [65]. Hypervectors are holographic and (pseudo) random with independent and identically distributed components as well as full holistic representation, thus no component has more responsibility to store any piece of information than any other hypervector.

Fig. 2.2 shows the overview of the classification in high dimensional space. HDC system generally consists of an encoder and an Associative Memory (AM). For all sample data within a class, HDC maps data to high dimensional vectors, called *hypervectors*, then combines them together to create a single hypervector modeling each class. Thereafter, the encoded hypervectors belonging to the same prediction class (label) are accumulated to build up the class's hypervector. All trained class hypervectors are stored in the AM. During the inference process, the same encoding scheme maps test input data to high dimensional space. AM looks at the similarity of the generated query hypervector against all stored class hypervectors. The input then gets the label of that class with which it has the highest similarity.

#### General Encoding Approach

The goal of HDC is to represent the input data in high-dimensional space. In the current HDC algorithms, models need to encode the input data to a single hypervector  $\vec{H} = \langle h_1, \dots, h_D \rangle$  with  $D$  dimensions as well as the corresponding precision. Here

Figure 2.2: (a) Overview of General HDC. (b) Retraining Process.

the elements of hypervector  $\vec{H}$  are  $m$ -bits length, while the values of  $h_i$  are in the range of  $(-2^{m-1}, 2^{m-1})$ . Consider an input data represented by the feature vector  $\vec{F} = \langle f_1, f_2, \dots, f_n \rangle$ , where  $n \ll D$  is the number of features for each input data. In Ref. [66], Aygun *et al.* summarized many encoding styles for the prior HDC. The difference of encoders epitomizes from two perspectives: (i) The operation in the high-dimensional space. *E.g.*, the binding in Record-based encoder, the bundling in Random-projection encoder, and the permutation in N-gram based encoder [42]. (ii) The way to consider the impact of each feature value on the final hypervector. For the reference, we explain the functionality of three popular encoders in detail:

### Encoder I: Record-based encoder

Fig. 2.3 (a) shows the functionality of this encoding scheme, which was proposed and utilized in [24, 67]. Assume the original data point has  $n$  features  $\{f_1, \dots, f_n\}$ . The first step is to quantize the range of pixel values into  $m$  levels. Then it assigns a random binary hypervector with  $D$  dimensions to each quantized level  $\{\vec{L}_1, \dots, \vec{L}_m\}$ , where  $L_i$  is the  $i^{th}$  feature values level. The number of dimensions  $D$  in the hypervector is large enough compared to the number of features ( $D \gg n$ ) in the original data. The level hypervectors are generated such that the neighbor levels have higher similarity, as their absolute values have closer distance. To take the impact of each feature position under consideration, the encoding module assigns a random binary hypervector to each existing feature index  $\{ID_1, \dots, ID_n\}$ , where  $ID \in \{0, 1\}^D$ . These  $ID$ s are randomly generated such that all features will have orthogonal  $ID$ s. The encoding can happen by linearly combining the feature values over different indices, where a hypervector corresponding to a feature index preserves the position of each feature value in a combined set:

$$\vec{H} = ID_1 \oplus \vec{L}_1 + ID_2 \oplus \vec{L}_2 + \dots + ID_n \oplus \vec{L}_n. \quad (2.2)$$

Here the  $\vec{H}$  is the non-binary encoded hypervector,  $\oplus$  denotes the XOR operation, and  $\vec{L}_i$  is the binary hypervector corresponding to the  $i$ -th feature of vector  $\vec{F}$ . The binarization

Figure 2.3: Functionality of three popular encoders.