|              |                                                                                                   |

|--------------|---------------------------------------------------------------------------------------------------|

| Title        | Studies on Miniaturization of Power Converters Using Gallium Compound Semiconductor Power Devices |

| Author(s)    | 關, 翔太                                                                                             |

| Citation     | 大阪大学, 2024, 博士論文                                                                                  |

| Version Type | VoR                                                                                               |

| URL          | <a href="https://doi.org/10.18910/98761">https://doi.org/10.18910/98761</a>                       |

| rights       |                                                                                                   |

| Note         |                                                                                                   |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

Doctoral Dissertation

**Studies on Miniaturization of

Power Converters Using Gallium

Compound Semiconductor Power Devices**

**Shota Seki**

June, 2024

Division of Electrical, Electronic

and Infocommunications Engineering

Graduate School of Engineering

Osaka University

# Abstract

The development of wide bandgap power semiconductor devices has enabled the miniaturization of power conversion circuits. In particular, the implementation of GaN power semiconductor devices has made it possible to significantly increase the operating frequency of power conversion circuits. GaN HEMTs are switching devices that use two-dimensional electron gas to achieve high electron mobility and to enable fast switching. However, GaN SBDs with good characteristics are difficult to obtain.  $\text{Ga}_2\text{O}_3$  SBDs are expected as alternative to GaN as a fast switching diodes. By applying gallium compound power semiconductors, GaN and  $\text{Ga}_2\text{O}_3$ , it is possible to realize power conversion circuits that are smaller and higher efficiency than conventional ones.

The objective of this study is to develop miniaturization technology for power conversion circuits using gallium compound power semiconductors. Power conversion circuits using gallium compound power semiconductors can operate at frequencies above 10 MHz. This thesis discusses the factors required for power conversion circuits above 10 MHz with gallium compound power semiconductors. Since magnetic components have a significant impact on the operation of high-frequency power conversion circuits, this thesis develops a method to evaluate the characteristics of magnetic components. In addition, the thermal conductivity of gallium compound power semiconductors is lower than that of Si, and the parasitic capacitance of semiconductor devices differs from that of Si. This thesis evaluates the thermal characteristics and models the voltage dependency of parasitic capacitance in gallium compound power semiconductor devices. The equivalent circuit model of magnetic components and the voltage dependency of capacitance model are validated using actual circuits of class-E amplifiers.

This thesis consists of the following six chapters. Chapter 1 is the introduction. Chapter 1 introduces the background and objectives of this study. This chapter de-

## ABSTRACT

---

scribes the problems preventing the miniaturization of power conversion circuit using gallium compound power semiconductors.

Chapter 2 describes the physical properties of gallium compound power semiconductors, including the structure and properties of GaN HEMTs. Chapter 2 also describes the physical properties and SBD structures of  $\text{Ga}_2\text{O}_3$ .

Chapter 3 evaluates magnetic components applied to a class-E amplifiers using GaN HEMTs. A method for evaluating magnetic characteristics using a 2-port circuit model and a vector network analyzer is developed. An equivalent circuit model of an inductor is proposed based on the 2-port model. The model is verified through circuit simulations and experiments of class-E amplifiers.

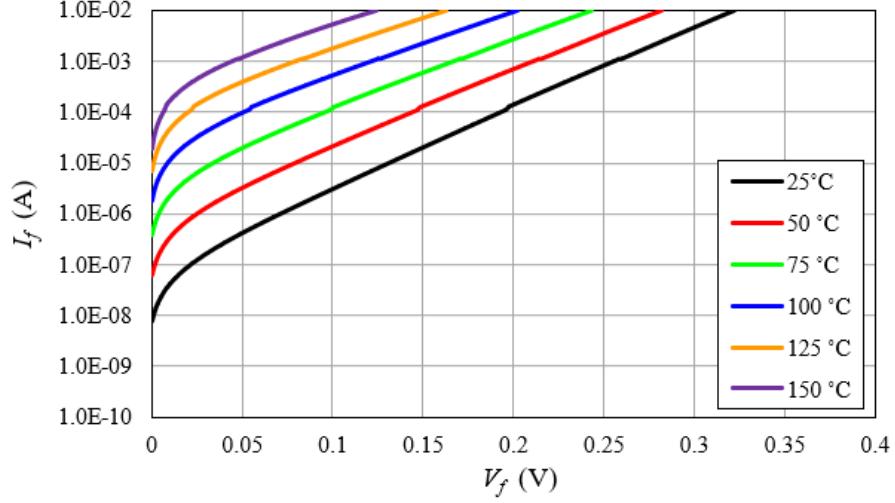

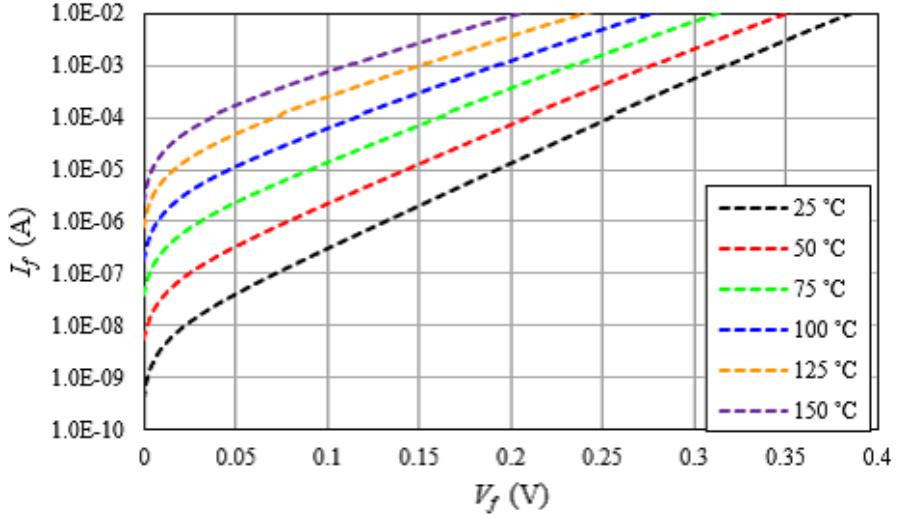

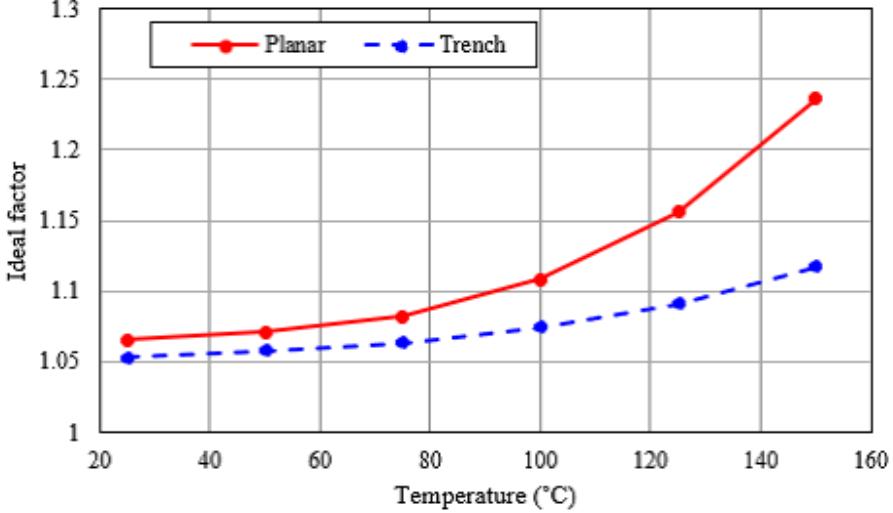

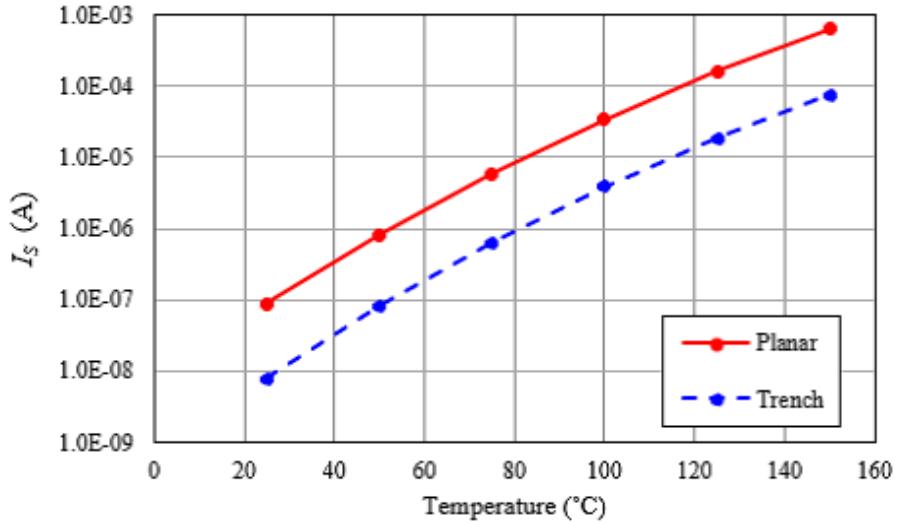

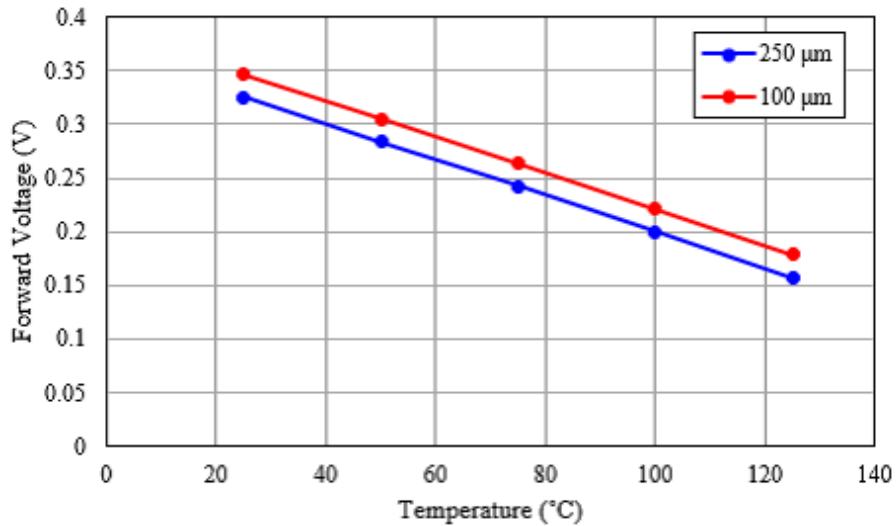

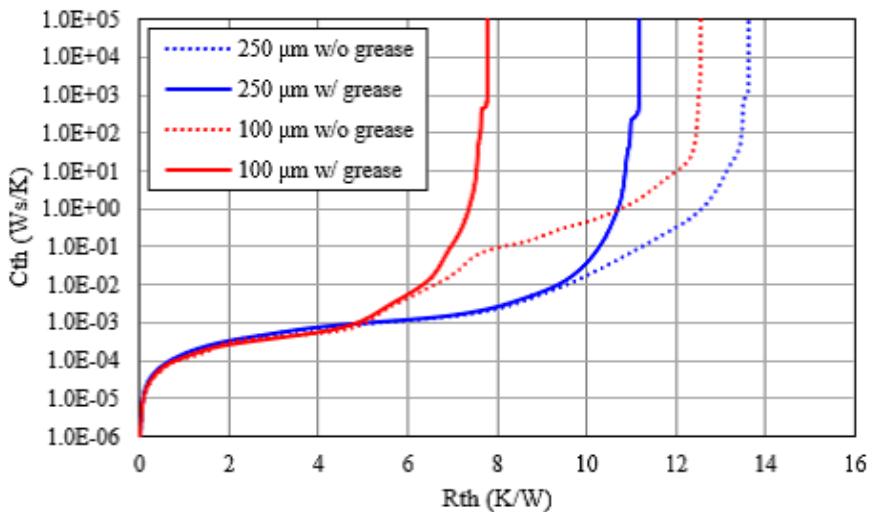

Chapter 4 evaluates transient thermal characteristics of  $\text{Ga}_2\text{O}_3$  SBDs. The forward current characteristics of diodes are used to evaluate the thermal characteristics of power semiconductor devices. However, the ideality of  $\text{Ga}_2\text{O}_3$  devices is not certified. In this thesis, the quality of  $\text{Ga}_2\text{O}_3$  Schottky junctions is evaluated based on measured static characteristics. Transient thermal characteristics of  $\text{Ga}_2\text{O}_3$  SBDs are also evaluated. In addition, a method to reduce transient thermal resistance by grinding the substrate layer of SBDs is discussed.

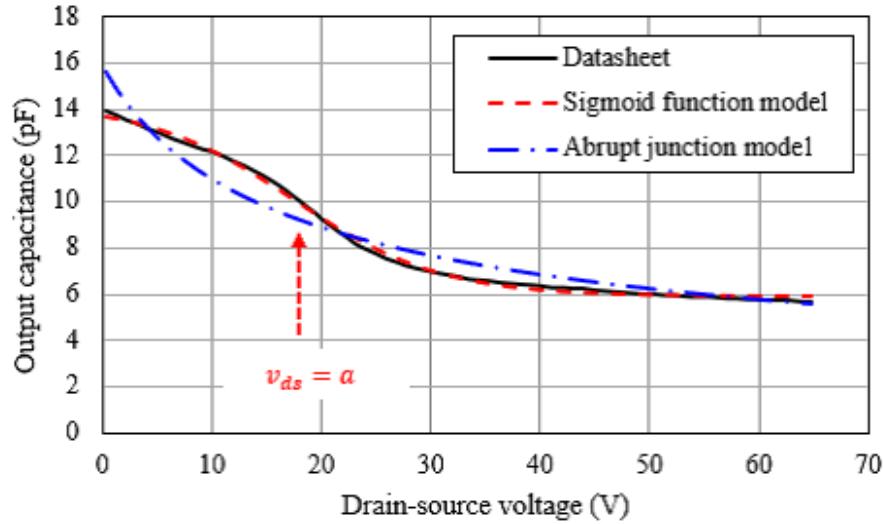

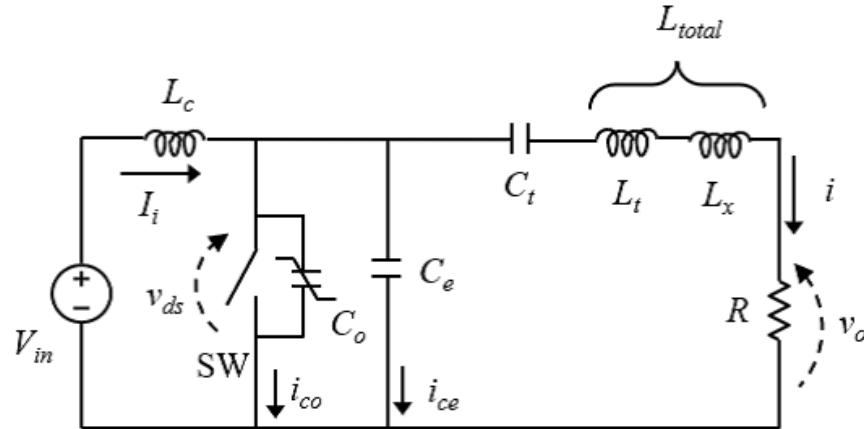

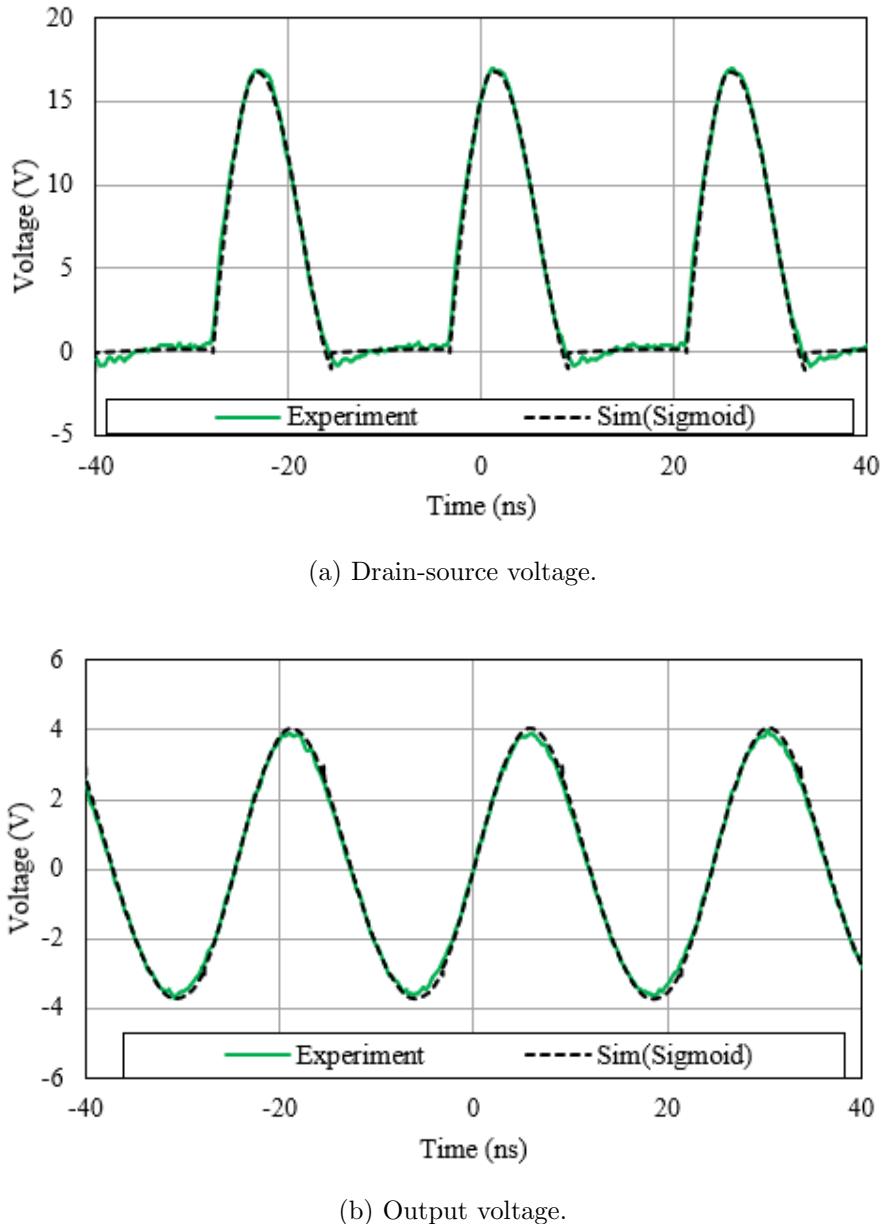

Chapter 5 models the voltage dependency of the parasitic capacitance for GaN HEMTs using a sigmoid function. Using the sigmoid function model, a circuit analysis of a class-E amplifier is performed to derive the soft-switching conditions. The derived soft-switching condition is verified by circuit simulation and experiment for actual circuits.

Chapter 6 concludes this thesis. This chapter also discusses the industrial impact and future prospects of this study.

# Acknowledgement

First of all I would like to express my most gratitude to Professor Tsuyoshi Funaki at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University. This work would not be accomplished without his constant support and prominent wisdom. He conferred invaluable and magnificent insight through discussions.

I would like to acknowledge Professor Tomoo Ushio and Professor Shigemasa Takai at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University for their careful review and attentive suggestions on this thesis. I also would like to appreciate Professor Masahide Hojo at Department of Electrical and Electronic Engineering, Graduate School of Technology, Industrial and Social Science, Tokushima University for his careful review and attentive suggestions.

I sincerely thank Professor Hideharu Sugihara at Program of Electrical and Electronic Engineering, School of Engineering, Kwansei Gakuin University, Lecturer Takaaki Ibuchi and Assistant Professor Shuhei Fukunaga at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University for a lot of their valuable advices and precise suggestions. I also thank Appointed Professor Takashi Nakamura and Guest Professor Shigekazu Sakabe at Division of Electrical, Electronic and Infocommunications Engineering, Graduate School of Engineering, Osaka University for their precious opinions.

I would like to thank Mr. Jun Arima, Mr. Minoru Fujita, Mr. Jun Hirabayashi, and Mr. Kazuyoshi Hanabusa at TDK Corporation for their enthusiastic and polite corporation in the joint research.

I would like to express great appreciation to all members of Funaki Laboratory for

## ACKNOWLEDGEMENT

---

their support and cooperation. I am deeply grateful to Mr. Hiroshi Kinemura for kind instruction and valuable discussion. I specially thank Ms. Fumie Imura secretary in Funaki Laboratory for her kind support to my daily work. I would like to thank my doctoral colleagues Mr. Yuki Nomura and Mr. Kazuki Nishatani for their cooperation.

I would like to express great appreciation to all colleagues of ROHM Corporation for their understanding and supports. I am deeply grateful to Mr. Satoru Nate, Mr. Satoshi Maejima, and Mr. Takumi Fujimaki for their thoughtful cooperations.

This work was partially supported by Waseda University Graduate Program for Power Energy Professionals (PEP). This work was partially supported by Osaka University Support for Pioneering Research Initiated by the Next Generation Project. This work has been partially implemented under a joint research project with TDK Corporation.

Finally, I deeply thank my parents, brothers and friends of mine for their understanding, careful supports, and constant encouragement.

*Shota SEKI*

Osaka, June 2024

# Contents

|                                                                                                                  |            |

|------------------------------------------------------------------------------------------------------------------|------------|

| <b>Abstract</b>                                                                                                  | <b>i</b>   |

| <b>Acknowledgement</b>                                                                                           | <b>iii</b> |

| <b>Contents</b>                                                                                                  | <b>v</b>   |

| <b>1 Introduction</b>                                                                                            | <b>1</b>   |

| 1.1 Background . . . . .                                                                                         | 1          |

| 1.2 Problems in miniaturization of power converters using gallium compound power semiconductor devices . . . . . | 4          |

| 1.2.1 Problems in magnetic components for high frequency power conversion . . . . .                              | 5          |

| 1.2.2 Problems in heat dissipation of gallium compound power semiconductor devices . . . . .                     | 6          |

| 1.2.3 Problems in consideration of output capacitance for soft-switching                                         | 6          |

| 1.3 Purpose and outline of this thesis . . . . .                                                                 | 7          |

| <b>2 Gallium compound semiconductor devices</b>                                                                  | <b>9</b>   |

| 2.1 Introduction . . . . .                                                                                       | 9          |

| 2.2 Physical properties of semiconductor devices . . . . .                                                       | 9          |

| 2.3 GaN power semiconductor devices . . . . .                                                                    | 14         |

| 2.4 Ga <sub>2</sub> O <sub>3</sub> power semiconductor devices . . . . .                                         | 19         |

| 2.5 Summary . . . . .                                                                                            | 23         |

| <b>3 Characterization and modeling of magnetic components for class-E amplifier using GaN HEMT</b>               | <b>25</b>  |

|          |                                                                                                                             |           |

|----------|-----------------------------------------------------------------------------------------------------------------------------|-----------|

| 3.1      | Introduction . . . . .                                                                                                      | 25        |

| 3.2      | Class-E amplifier . . . . .                                                                                                 | 27        |

| 3.2.1    | The operation of a class-E amplifier . . . . .                                                                              | 27        |

| 3.2.2    | Issues in the design of class-E amplifiers . . . . .                                                                        | 29        |

| 3.3      | Evaluation and modeling of magnetic properties for power inductors . . . . .                                                | 29        |

| 3.3.1    | Magnetic materials considered in this chapter . . . . .                                                                     | 30        |

| 3.3.2    | Evaluation of magnetic components using 2-port equivalent circuit model . . . . .                                           | 32        |

| 3.3.3    | Equivalent circuit model for inductors . . . . .                                                                            | 44        |

| 3.4      | Verification of inductor model with class-E amplifiers . . . . .                                                            | 46        |

| 3.5      | Summary . . . . .                                                                                                           | 51        |

| <b>4</b> | <b>Evaluation and reduction of transient thermal resistance for <math>\beta</math>-Ga<sub>2</sub>O<sub>3</sub> SBD</b>      | <b>52</b> |

| 4.1      | Introduction . . . . .                                                                                                      | 52        |

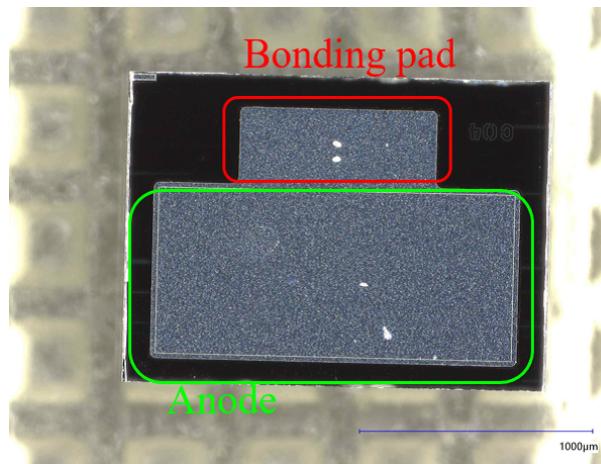

| 4.2      | $\beta$ -Ga <sub>2</sub> O <sub>3</sub> SBDs under evaluation . . . . .                                                     | 53        |

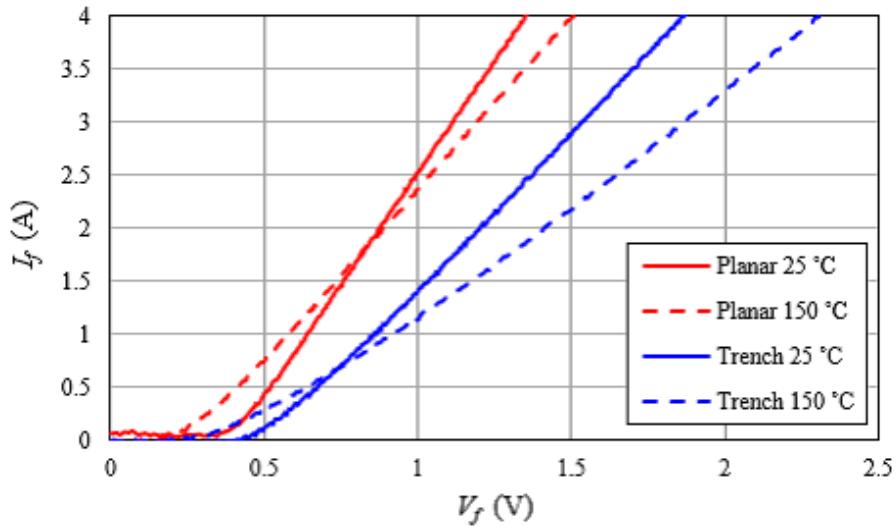

| 4.3      | Static characteristics of $\beta$ -Ga <sub>2</sub> O <sub>3</sub> SBDs . . . . .                                            | 54        |

| 4.4      | Extraction of transient thermal resistance for $\beta$ -Ga <sub>2</sub> O <sub>3</sub> SBDs . . . . .                       | 57        |

| 4.5      | Transient thermal resistance reduction by thinning substrate of a $\beta$ -Ga <sub>2</sub> O <sub>3</sub> SBD . . . . .     | 62        |

| 4.6      | Summary . . . . .                                                                                                           | 64        |

| <b>5</b> | <b>Analysis and Design of class-E amplifier with nonlinear output capacitance model using sigmoid function for GaN HEMT</b> | <b>66</b> |

| 5.1      | Introduction . . . . .                                                                                                      | 66        |

| 5.2      | Output capacitance model with sigmoid function . . . . .                                                                    | 68        |

| 5.3      | Circuit analysis of a class-E amplifier using sigmoid function model . . . . .                                              | 70        |

| 5.3.1    | ZVS condition . . . . .                                                                                                     | 73        |

| 5.3.2    | ZVDS condition . . . . .                                                                                                    | 73        |

| 5.3.3    | Derivation of passive component parameters . . . . .                                                                        | 73        |

| 5.4      | Class-E amplifier designs to verify the analysis using sigmoid function model . . . . .                                     | 75        |

## CONTENTS

---

|                     |                                                                 |            |

|---------------------|-----------------------------------------------------------------|------------|

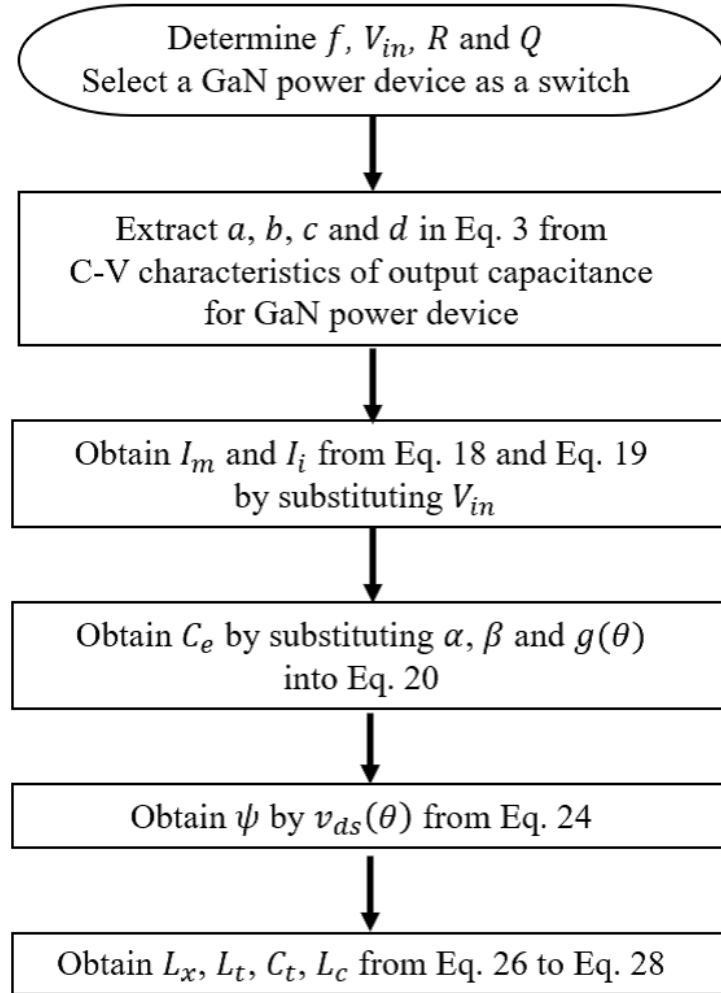

| 5.4.1               | Class-E amplifier design procedure using sigmoid function model | 75         |

| 5.4.2               | The designed class-E amplifiers with proposed method . . . . .  | 76         |

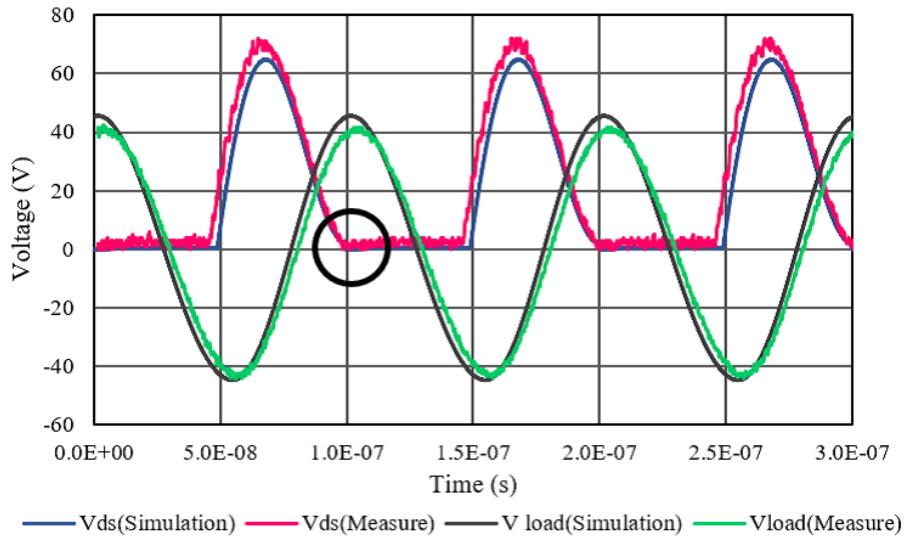

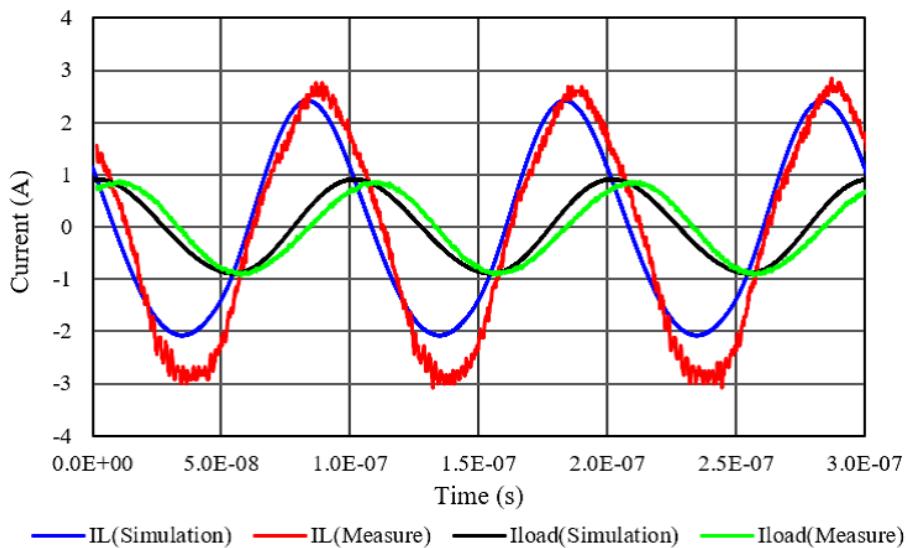

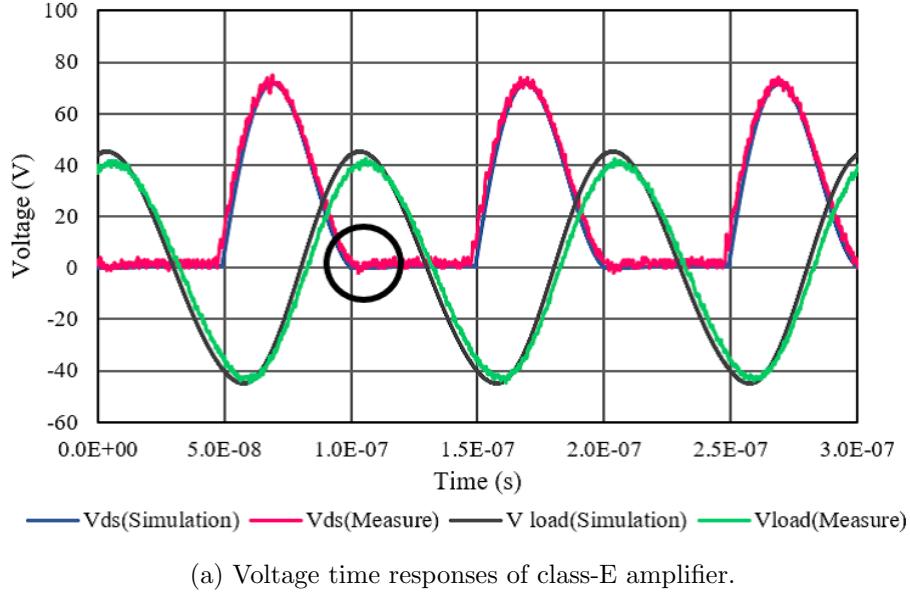

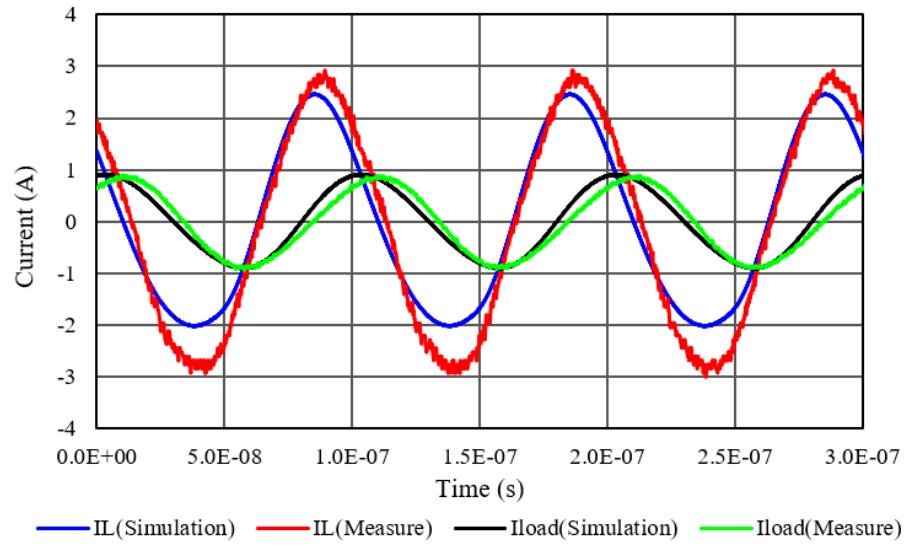

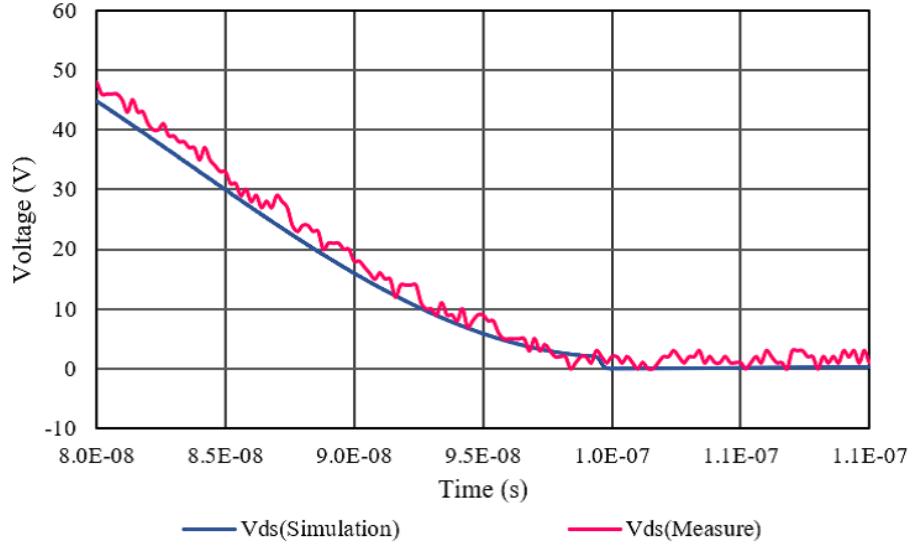

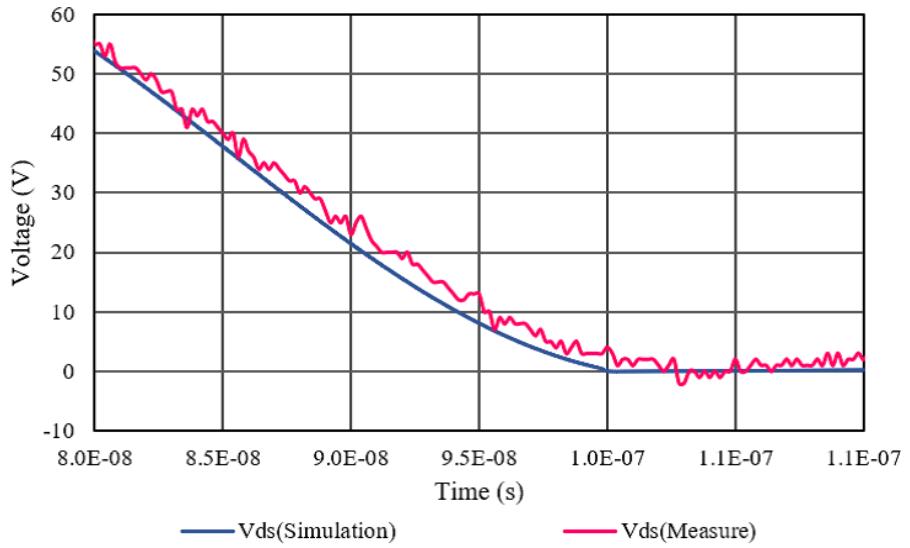

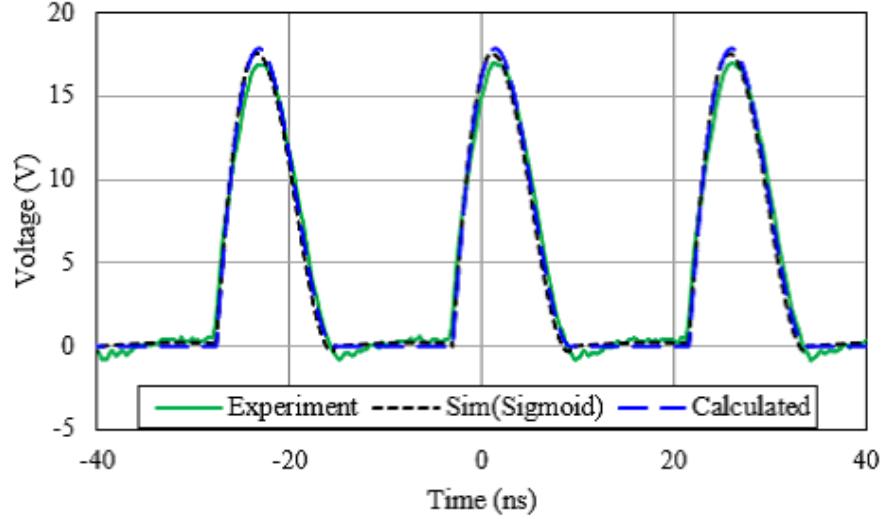

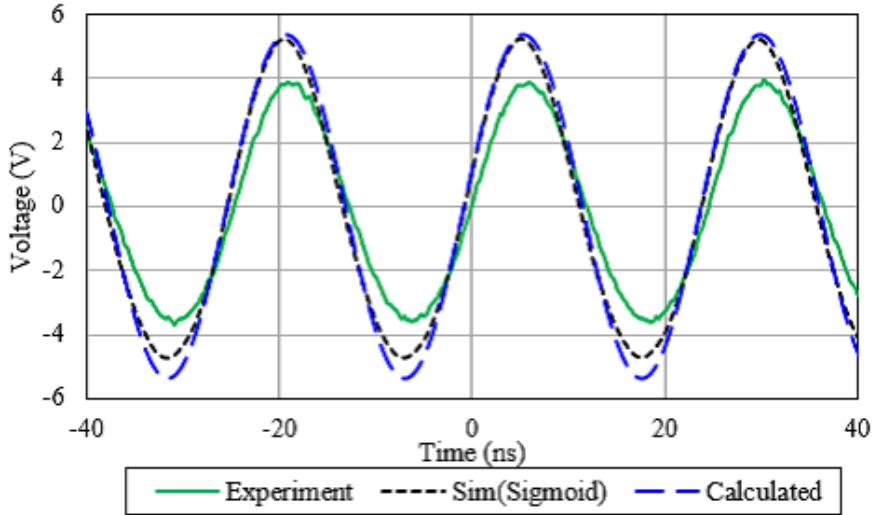

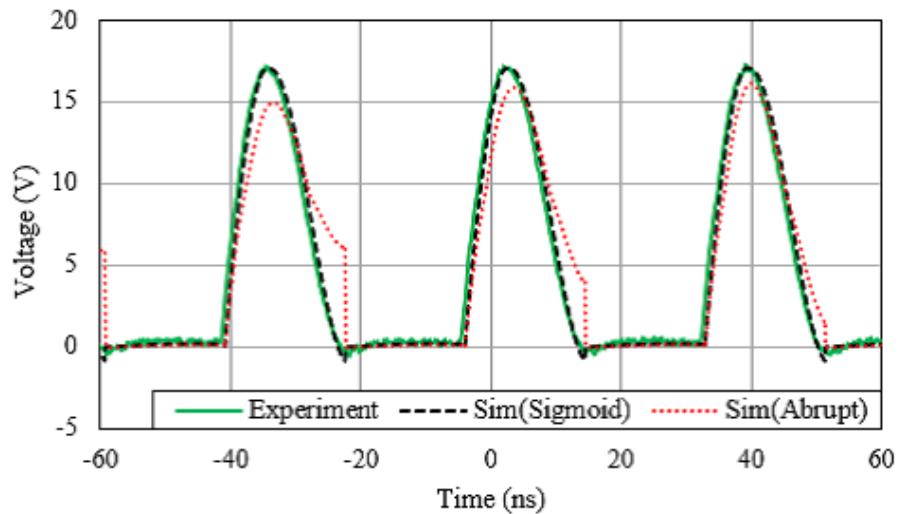

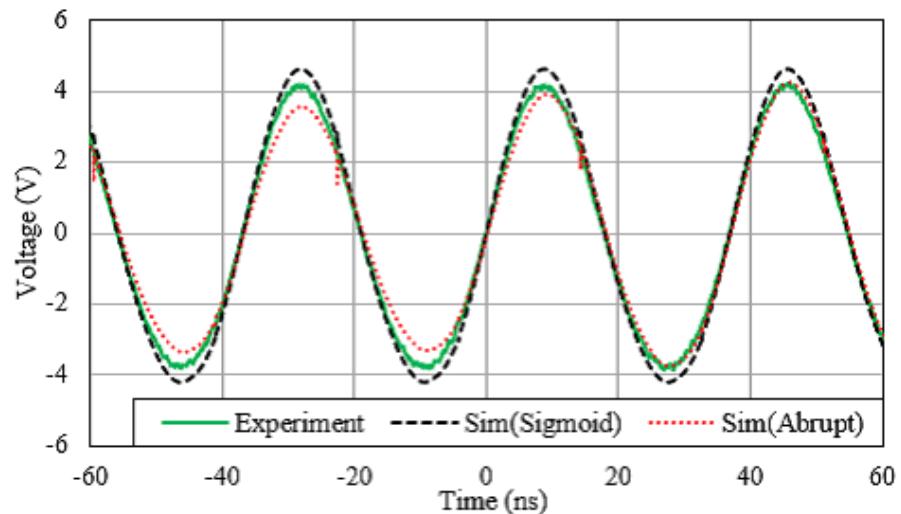

| 5.5                 | Simulation and experimental results . . . . .                   | 78         |

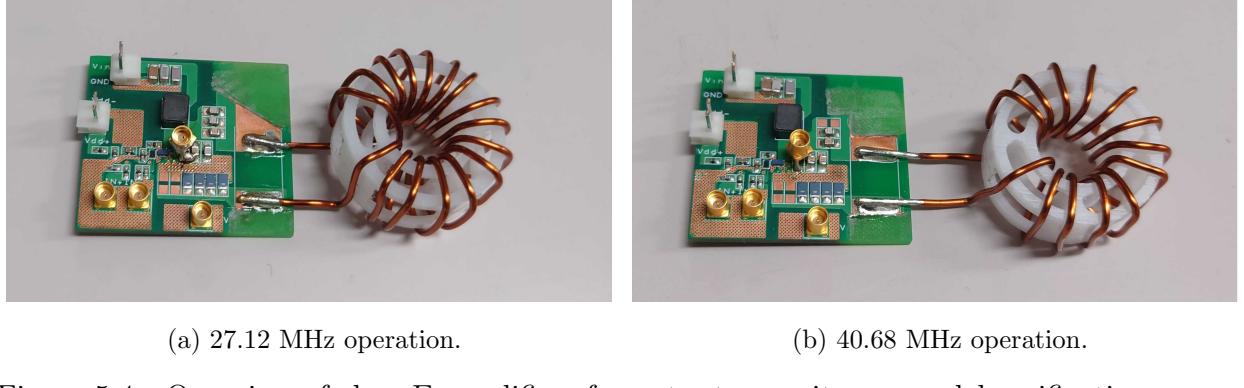

| 5.5.1               | Fabrication of actual circuits . . . . .                        | 78         |

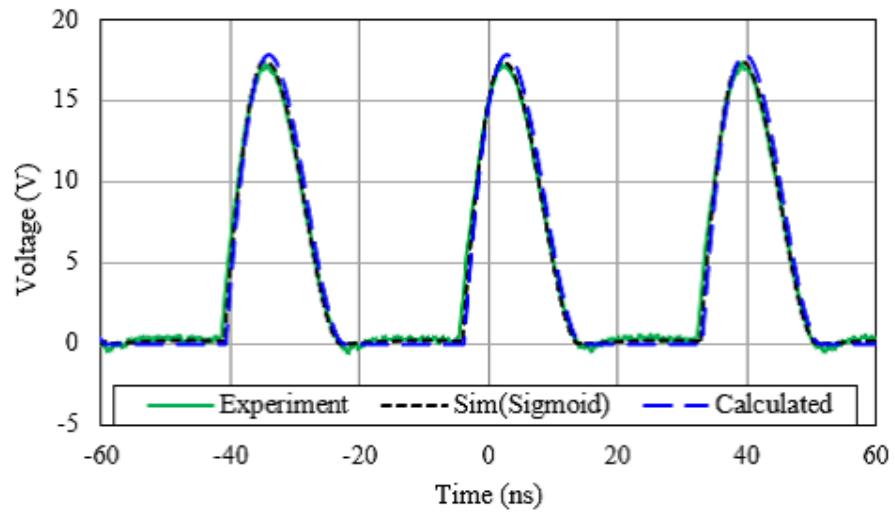

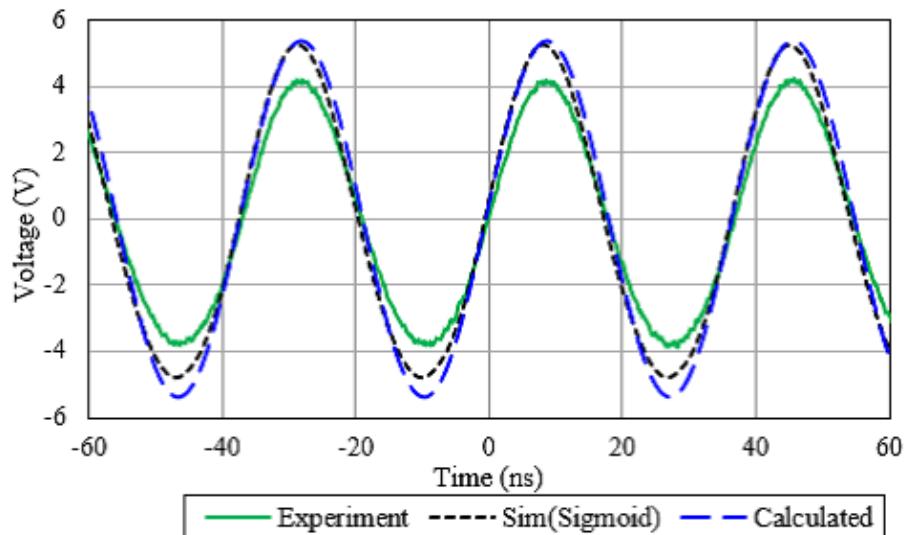

| 5.5.2               | Simulation and experimental results . . . . .                   | 79         |

| 5.6                 | Summary . . . . .                                               | 86         |

| <b>6</b>            | <b>Conclusions</b>                                              | <b>88</b>  |

| 6.1                 | Conclusions . . . . .                                           | 88         |

| 6.2                 | Industrial impacts . . . . .                                    | 90         |

| 6.3                 | Future prospects . . . . .                                      | 91         |

| <b>References</b>   |                                                                 | <b>93</b>  |

| <b>Publications</b> |                                                                 | <b>107</b> |

# Chapter 1

## Introduction

### 1.1 Background

Power electronics is the key to solve social problems[1]. There is vigorous controversy on improving the sustainability of human society. Reducing consumption of fossil fuels is one of the urgent problems[2][3]. Fossil fuels lead to global warming and economic disparity between oil-producing and non-oil-producing countries. To reduce fossil fuel consumption, electrification of internal combustion engines and the use of renewable energy sources are necessary[4].

The development of power electronics is essential for these electrification and utilization of renewable energy. Semiconductor power conversion technology has been used in power converters and motor drive circuits, which results in significant improvements in efficiency and controllability. These semiconductor power conversion circuits have mainly used silicon (Si) semiconductors. Low-voltage circuits adopt Si metal oxide semiconductor field effect transistors (MOSFETs) as switches and Si Schottky barrier diodes (SBDs) as rectifiers. High-voltage circuits adopt Si insulated gate bipolar transistors (IGBTs) and Si gate turn-off thyristors (GTOs) as switches. PN diodes and PiN diodes are used as rectifiers[5][6].

Semiconductor power conversion circuits are required to achieve both high power density and high efficiency. Power density is the ratio between volume of the converter to converted power. The small converters which handles large amount of power is required. Increase in operating frequency is effective to reduce the size of power con-

## 1.1 Background

---

version circuits. By increasing the operating frequency, the inductance and capacitance required for circuit operation can be reduced[7]. This is because the higher operating frequency reduces the amount of energy handled by passive components per cycle.

However, There are some drawback to the higher operating frequency. Power dissipations in power devices can be divided into conduction loss and switching loss. Conduction loss is the product of the current flowing through the power device and the voltage applied during the conduction state. Conduction loss is determined by the characteristics of the power device and amount of flowing current.

Semiconductor power devices require time for the transition between the on-state and off-state. The transient time causes the power device's simultaneous current and voltage application. The losses in the transient time of power devices are called switching loss. Since the switching transition time is a parameter independent of the switching frequency, the switching loss increases proportionally as the operating frequency increases. From the above, the higher power and higher operating frequency increases the losses consumed in the switches.

In order to reduce losses in switches as well as to achieve both miniaturization and high efficiency, faster switching and low on-resistance of power semiconductor devices are needed. Unipolar devices have an advantage for fast switching because they use only majority carrier for conduction. However, unipolar devices have a trade-off between breakdown voltage and on-resistance. Si power semiconductor devices are reaching their performance limit for improving this trade-off[1][8].

Studies on wide bandgap semiconductors such as SiC and GaN are undergoing as semiconductor materials that exceed the performance limits of Si power semiconductor devices. SiC and GaN have wider bandgap than Si, which enables semiconductor device operation at high temperature. Also, the critical electric field strength of wide bandgap semiconductors is higher than that of Si, which can achieve both higher breakdown voltage and lower on-resistance [9][10].

Table 1.1 shows the physical properties of semiconductor materials. Wide bandgap semiconductors have wider bandgap and higher critical electric field strength compared to Si. This feature enables unipolar devices to have high Baliga's Figure-Of-Merits (BFOM), which indicates the trade-off performance between breakdown voltage and

## 1.1 Background

---

Table 1.1 Physical properties of semiconductor materials[11]-[26]

|                         |                                | Si   | 4H-SiC | GaN  | $\alpha\text{-Ga}_2\text{O}_3$ | $\beta\text{-Ga}_2\text{O}_3$ |

|-------------------------|--------------------------------|------|--------|------|--------------------------------|-------------------------------|

| Bandgap                 | $E_g$ (eV)                     | 1.1  | 3.3    | 3.4  | 5.3                            | 4.5-4.9                       |

| Critical electric field | $E_{crt}$ (MV/cm)              | 0.23 | 2.2    | 3.3  | 9.5                            | 8.0                           |

| Electron mobility       | $\mu_e$ (cm <sup>2</sup> /V·s) | 1450 | 1000   | 900  | 200(est.)                      | 150                           |

| Relative permittivity   | $\epsilon$                     | 11.9 | 12.8   | 10.4 | 10(est.)                       | 10.2                          |

| Thermal conductivity    | $\lambda$ (W/cm·K)             | 1.5  | 2.8    | 1.5  | 0.09[010]<br>0.12 [100]        | 0.13 [010]<br>0.21 [100]      |

| BFOM                    | $\epsilon\mu_e E_g^3$          | 1    | 500    | 900  | 3844                           | 3444                          |

on-resistance[27].

SiC power semiconductor devices enable high-speed switching by replacing Si IGBTs with SiC MOSFETs and Si PiN diodes with SiC SBDs in high-voltage, high-current applications. The SiC manufacturing technologies have already reached the commercial level. SiC applications have been implemented in society, for example, in the motor drive system of the Shinkansen high-speed train[28][29].

GaN semiconductor has bandgap almost same as that of SiC. However, GaN is difficult to fabricate as a single crystal. GaN crystals are grown on other materials such as Si, SiC, and sapphire. Currently used commercially available GaN devices are lateral structure power semiconductor devices. Compared to vertical structure devices, lateral devices have lower current capability. On the other hand, the piezoelectric polarization and the spontaneous polarization caused by the boundary of an Al-GaN layer and a GaN layer generates two-dimensional electron gas (2DEG) in lateral structure GaN devices. Two-dimensional electron gas has high mobility and enables power semiconductor device to switch at fast. This feature makes GaN power devices suitable for low-power and compact power conversion circuits[10][11][12][30] and RF power converters[31]-[33].

There are many preceding research on power conversion circuits using GaN power devices. For example, 1 MHz driven power converters have achieved efficiencies of up to 98% or more at around 1kW output power[34][35]. In the MHz band, there are many reports of converters of 100 W or less, with efficiencies of around 90% at best[36][37]. In

addition, converters from tens to 100 MHz have been reported[38][39][40]. These have output powers from a few Watt to several tens-of-Watt. Some use soft-switching and have efficiencies in excess of 90%[41][42]. However, the driving frequency of commercial converters, such as VIPerGaN (STmicro) and EPC9171 (EPC), is 1 MHz or less. This is due to limitations imposed by the magnetic components and thermal characteristics.

Gallium oxide ( $\text{Ga}_2\text{O}_3$ ) semiconductors have wider bandgap than SiC and GaN[43]-[46].  $\text{Ga}_2\text{O}_3$  also has multiple polymorphs. Among them,  $\alpha$  and  $\beta$   $\text{Ga}_2\text{O}_3$  is expected as materials for power semiconductor devices[13]-[18]. Especially,  $\beta$ - $\text{Ga}_2\text{O}_3$  can be grown from its melt under atmospheric pressure, which is suitable for mass-production[47]-[49]. For this reason,  $\beta$ - $\text{Ga}_2\text{O}_3$  is expected to be used as inexpensive, high-voltage, low on-resistance power devices. Because fabrication of GaN SBD is difficult, the combination of GaN semiconductor switching device and SiC or  $\text{Ga}_2\text{O}_3$  SBDs is expected to realize power conversion circuits that can operate at fast and high frequency[50].

$\beta$ - $\text{Ga}_2\text{O}_3$  power devices are currently in the research and development stage.  $\beta$ - $\text{Ga}_2\text{O}_3$  power devices with various structures have been proposed. Generally, it is difficult to dope *p*-type impurities into  $\text{Ga}_2\text{O}_3$ [51]. Then, *n*-type SBDs are mainly developed[15][18]. As switching devices, lateral FETs have been developed first[26]. In recent years, vertical FETs, which are suitable for high current, have also been reported[44][52].

## 1.2 Problems in miniaturization of power converters using gallium compound power semiconductor devices

Although gallium compound power semiconductor devices such as GaN and  $\text{Ga}_2\text{O}_3$  power semiconductor devices are actively developed, there are many challenges in miniaturization of power conversion circuits using gallium compound power semiconductor devices. This section discusses the problems in miniaturization of power converters using gallium compound power semiconductor devices.

### 1.2.1 Problems in magnetic components for high frequency power conversion

GaN power semiconductor devices are capable of high-speed switching and high-frequency operation. Despite of high performance of GaN power devices, magnetic components such as inductors are the bottleneck of miniaturization of whole circuits. Magnetic components with air cores do not cause magnetic saturation and do not generate iron loss[53][54]. They can be used in high-frequency converters. On the contrary, air-core inductors tend to be large in volume. In addition, EMI effects are serious due to high leakage magnetic flux[55]. Magnetic components with magnetic cores are desirable for power conversion circuits[37][56][57].

Losses in magnetic components are divided into iron loss and copper loss, which increase as the operating frequency increases. And, iron loss is divided into hysteresis loss and eddy current loss. To reduce these losses, it is effective to reduce area of the magnetic domain and the loop of eddy currents. Magnetic components for high-frequency power conversion are realized by miniaturized magnetic domains and eddy current paths with solidified finely processed magnetic materials[58]-[61].

Those low-loss magnetic components have low permeability due to microscopic gaps in the magnetic path. While such magnetic components can reduce losses, low permeability increases the size of magnetic components to realize enough inductance for circuit operation. Design of magnetic components is important to achieve both low loss at high switching frequency and miniaturization. Evaluation of magnetic material properties is essential for the design of high-frequency magnetic components[62].

However, it is difficult to evaluate the characteristics of low-permeability magnetic components because of inability in accurate measurement of current and phase difference between voltage and current. There is a need to evaluate the characteristics of inductors used in high-frequency power conversion circuits.

### **1.2.2 Problems in heat dissipation of gallium compound power semiconductor devices**

In addition to magnetic components, power semiconductor devices also have problems for miniaturization of power conversion circuits. High-frequency operation of power conversion circuits increases switching losses. However, it is difficult to dissipate heat sufficiently in circuits with a small volume. In addition, the thermal conductivity of GaN is almost the same as that of Si[12]. The thermal conductivity of  $\text{Ga}_2\text{O}_3$  is much lower than that of Si[19]-[21].

Improving heat dissipation performance is particularly important for the practical application of  $\text{Ga}_2\text{O}_3$  power semiconductor devices. However, there are few studies in evaluation of thermal characteristics of  $\text{Ga}_2\text{O}_3$  power semiconductor devices. It is necessary to develop device structures for reducing the thermal resistance of  $\text{Ga}_2\text{O}_3$  power semiconductor devices[63].

### **1.2.3 Problems in consideration of output capacitance for soft-switching**

Soft-switching technique is used to reduce switching losses. Soft-switching uses resonance to prevent switching losses at switching transition. In soft-switching circuits, capacitors are connected in parallel with the switching devices to form a resonant circuit[64]-[72].

FETs have parasitic capacitance between drain and source, which is called output capacitance. Output capacitance in FETs has voltage dependency. Voltage dependency of output capacitance makes the resonant circuit nonlinear and time-variant. Circuit design must consider the voltage dependency of output capacitance to achieve soft-switching[73]-[79].

GaN high electron mobility transistors (HEMTs) used as switching devices are lateral structure. The parasitic capacitance characteristics of the lateral structure devices differ from those of vertical structure devices. For this reason, the parasitic capacitance of GaN HEMTs cannot be represented by the vertical type Si MOSFET model[80]-[83]. The dedicated model of voltage dependency in GaN output capacitance

is needed for soft-switching analysis.

### 1.3 Purpose and outline of this thesis

This thesis investigates the technologies to miniaturize power conversion circuits using gallium compound power semiconductor devices. This thesis focuses on magnetic components and semiconductor devices in power conversion circuits operating at frequencies above MHz. In addition, this thesis fabricates power conversion circuit that operates at operating frequencies 10 MHz or higher and verifies the validity of the proposed consideration.

Chapter 2 describes device structures of gallium compound semiconductor devices, GaN and  $\text{Ga}_2\text{O}_3$ . Based on the characteristics of GaN and  $\text{Ga}_2\text{O}_3$  semiconductor devices, issues for miniaturization of power conversion circuits are also discussed.

Chapter 3 models magnetic components made of iron-based metal composite materials and carbonyl iron materials. Those materials are developed as magnetic components for high-frequency power conversion circuits. This chapter evaluates the losses of the two materials and proposes an equivalent circuit model that can be used for circuit analysis and simulation. The identification of parameters in the proposed equivalent circuit model is described. The identified parameters are validated by circuit simulations and experiments on class-E amplifiers.

Chapter 4 describes a method for evaluating device electrical and transient thermal characteristics of  $\beta\text{-Ga}_2\text{O}_3$  power Schottky barrier diodes. The temperature dependency of the diode's forward current characteristics is used to estimate transient thermal resistance.  $\beta\text{-Ga}_2\text{O}_3$  is still in the development stage and its crystal has many defects. In this chapter, the possibility of measuring transient thermal resistance is discussed based on the evaluation of the ideal factor of diodes and other properties of  $\beta\text{-Ga}_2\text{O}_3$  SBDs. In addition, a method of thinning the substrate layer in the diode is discussed to reduce the thermal resistance of  $\beta\text{-Ga}_2\text{O}_3$  SBDs to conquer low thermal conductivity.

Chapter 5 proposes to model the voltage dependency of the output capacitance in GaN power devices using sigmoid function for the circuit analysis of a class-E amplifier.

### 1.3 Purpose and outline of this thesis

---

This chapter derives the conditions for class-E switching with sigmoid function modeled output capacitance of GaN power devices. The results obtained by circuit analysis are verified by simulations and circuit experiments operated above 10 MHz operating frequencies.

Chapter 6 summarizes this thesis and discusses the industrial impact and future prospects of this work.

# Chapter 2

## Gallium compound semiconductor devices

### 2.1 Introduction

Wide bandgap power semiconductors are being studied as an alternative to Si semiconductors. This thesis focuses on gallium compound power semiconductor devices. Gallium compound power semiconductor devices have wider bandgap and higher critical electric field strength than Si. However, Gallium compound semiconductors have some problems such as difficulty in fabricating single crystals. To overcome the physical problems and take advantage of the excellent physical properties for semiconductor materials, various device structures are being investigated.

In this chapter, the physical properties of gallium compound semiconductor devices are explained based on semiconductor physics. Then, device structures specified to gallium compound power semiconductors are described. In this thesis, GaN and  $\beta$ - $\text{Ga}_2\text{O}_3$  are treated as gallium compound power semiconductor devices. This chapter explains the structures of GaN HEMTs and  $\beta$ - $\text{Ga}_2\text{O}_3$  SBDs in detail.

### 2.2 Physical properties of semiconductor devices

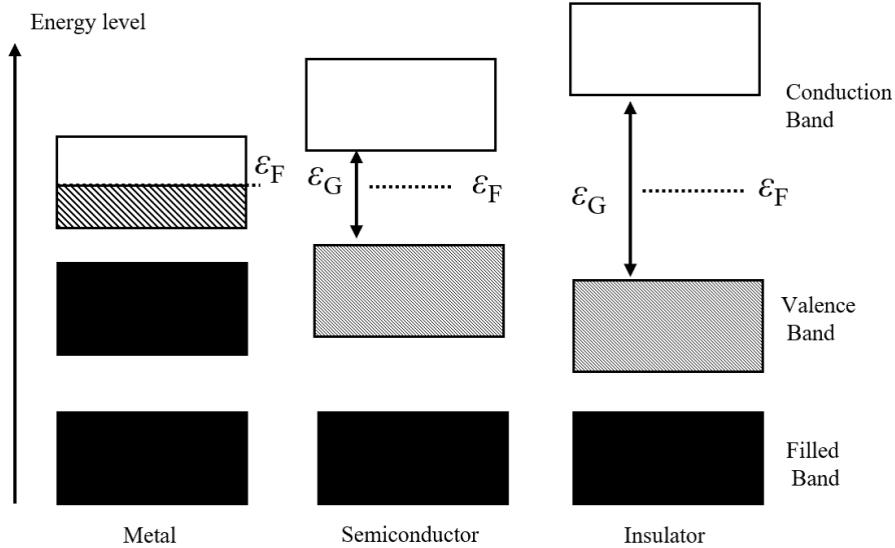

Semiconductors are materials with properties intermediate between those of conductors and insulators. The energy band structures of conductor, semiconductor, and insulator

crystals are shown in Fig. 2.1.  $\varepsilon_G$  is bandgap and  $\varepsilon_F$  is Fermi level[11][27][84][85].

Figure 2.1 Energy bands of conductor, semiconductor, and insulator.

In crystals, the energy of electrons is discrete value. This value is called the energy level. In the case of crystals, there are many electrons with discrete energy levels. The energy level differences among electrons becomes very small, so that each level forms a continuous band. This continuous level is called an energy band. The energy level is divided into an allowed band, in which electrons are allowed to exist, and a forbidden band, in which they are not allowed to exist. In a crystal, electrons are trapped in order from the lowest energy level to the highest. The allowed band in which electrons are completely occupied is called the filled band. The highest energy level in the filled band is called the valence band.

When an electric field is applied to a crystal, electrons receive energy from the electric field and transit to higher energy level. However, all the levels in the filled band are occupied by electrons. Then, the electrons in the filled band cannot transit to another level due to the energy from the electric field. Therefore, electrons in the filled band cannot contribute to electrical conduction.

An empty or partially occupied allowed band is called conduction band. The conduction band is an allowed band just above the valence band. Because the conduction band is vacant, electrons in the conduction band can receive energy from the electric field and transit to another level. The transited electrons contribute to electrical con-

duction. Such electrons are called free electrons. In the case of metals, electrons are occupied up to the middle of the conduction band. The free electrons in the conductor contribute to electrical conduction, which results in very high conductivity. In the case of insulators, electrons are occupied up to the valence band. There are almost no electrons in the conduction band, thus the conductivity is very low.

In semiconductors, electrons occupy the valence band. However, because the forbidden bandgap  $\varepsilon_G$ , which is the energy difference between the valence band and the conduction band, is relatively low. The transition of electrons from the valence band to the conduction band is possible. Thus, there are a few free electrons in conduction band of semiconductors. In the valence band of semiconductors, an empty level is left after the transition of electrons. This level can be regarded as a positive charge. Electrons can easily transit to this empty level. The left energy level becomes an empty level again. As this process continues, the empty level can be regarded as conductor. This empty level is called hole. In semiconductors, both free electrons and holes contribute to electrical conduction. Electrons and holes are called carriers.

The electron energy  $\varepsilon_e$  is expressed as Eq. 2.1, where  $m_e$ ,  $\varepsilon_c$ ,  $\hbar$ , and  $k$  are effective mass of electron, bottom energy of conduction band, Planck constant, and wavenumber of wave function, respectively.

$$\varepsilon_e = \varepsilon_c + \frac{\hbar^2 k^2}{2m_e} \quad (2.1)$$

The electron energy  $\varepsilon_h$  is expressed as Eq. 2.2, where  $m_h$  and  $\varepsilon_v$  are effective mass of hole and bottom energy of valence band, respectively.

$$\varepsilon_h = \varepsilon_v - \frac{\hbar^2 k^2}{2m_h} \quad (2.2)$$

Bandgap  $\varepsilon_G$  is expressed as Eq. 2.3 using  $\varepsilon_c$  and  $\varepsilon_v$ .

$$\varepsilon_G = \varepsilon_c - \varepsilon_v \quad (2.3)$$

The bandgap depends on the semiconductor materials. The electrical properties of semiconductors depend on the value of the bandgap.

Electron density of states  $g_n(\varepsilon)d\varepsilon$  between valence band and conduction band is a function of  $\varepsilon_e$  as shown in Eq. 2.4. Hole density of states  $\varepsilon_e$  between valence band and conduction band is a function of  $\varepsilon_h$  as shown in Eq. 2.5.

$$g_n(\varepsilon_e)d\varepsilon_e = \frac{(2m_e)^{3/2}}{2\pi^2\hbar^3} \sqrt{\varepsilon_e - \varepsilon_c} d\varepsilon_e \quad (2.4)$$

$$g_p(\varepsilon_h)d\varepsilon_h = \frac{(2m_h)^{3/2}}{2\pi^2\hbar^3} \sqrt{\varepsilon_v - \varepsilon_h} d\varepsilon_h \quad (2.5)$$

From Fermi-Dirac statistics, probability of electron occupation  $f_n(\varepsilon_e)$  and probability of hole occupation  $f_p(\varepsilon_h)$  are expressed as Eq. 2.6 and Eq. 2.7, respectively, where  $k_B$  is Boltzmann constant and  $T$  is absolute temperature.

$$f_n(\varepsilon_e) = \frac{1}{e^{(\varepsilon_e - \varepsilon_F)k_B T} + 1} \quad (2.6)$$

$$f_p(\varepsilon_h) = 1 - f_n(\varepsilon_e) \quad (2.7)$$

Density of electron  $n$  and density of hole  $p$  is expressed as Eq. 2.8 and Eq. 2.9 using Eq. 2.6 and Eq. 2.7.

$$n = \int_{\varepsilon_c}^{\infty} g_n(\varepsilon_e) f_n(\varepsilon_e) d\varepsilon_e = \frac{(2m_e)^{3/2}}{2\pi^2\hbar^3} \int_{\varepsilon_c}^{\infty} \frac{(\varepsilon_e - \varepsilon_c)^{1/2}}{1 + e^{(\varepsilon_e - \varepsilon_F)/k_B T}} \quad (2.8)$$

$$p = \int_{-\infty}^{\varepsilon_v} g_p(\varepsilon_h) f_p(\varepsilon_h) d\varepsilon_h = \frac{(2m_h)^{3/2}}{2\pi^2\hbar^3} \int_{-\infty}^{\varepsilon_v} \frac{(\varepsilon_v - \varepsilon_h)^{1/2}}{1 + e^{(\varepsilon_F - \varepsilon_h)/k_B T}} \quad (2.9)$$

In intrinsic semiconductors, the Fermi level  $\varepsilon_F$  is in the middle of forbidden band, and  $f_n(\varepsilon_e) \ll 1$ ,  $f_p(\varepsilon_h) \ll 1$ . Thus, Eq. 2.8 and Eq. 2.9 can be approximated by the Boltzmann distribution. Using Boltzmann distribution, Eq. 2.8 and Eq. 2.9 are expressed as Eq. 2.10 and Eq. 2.11.

$$n = N_c \exp\left(-\frac{\varepsilon_c - \varepsilon_F}{k_B T}\right) \approx N_c f_n(\varepsilon_c) \quad (2.10)$$

$$p = N_v \exp\left(-\frac{\varepsilon_F - \varepsilon_v}{k_B T}\right) \approx N_v f_p(\varepsilon_v) \quad (2.11)$$

$N_c$  in Eq. 2.10 is called conduction band effective density of states and expressed as Eq. 2.12.  $N_v$  in Eq. 2.11 is called valence band effective density of states and expressed as Eq. 2.13.

$$N_c = 2 \left( \frac{2\pi m_e k_B T}{h^2} \right)^{3/2} \quad (2.12)$$

$$N_v = 2 \left( \frac{2\pi m_h k_B T}{h^2} \right)^{3/2} \quad (2.13)$$

The product of Eq. 2.10 and Eq. 2.11 is Eq. 2.14.

$$np = N_c N_v \exp\left(-\frac{\varepsilon_c - \varepsilon_v}{k_B T}\right) = N_c N_v \exp\left(-\frac{\varepsilon_G}{k_B T}\right) \quad (2.14)$$

In intrinsic semiconductor, the number of free electrons and that of holes are equal. Then, the electroneutrality condition  $n = p = n_i$  is satisfied. Electron density  $n_i$  is expressed as Eq. 2.15.

$$n_i = \sqrt{N_c N_v} \exp\left(-\frac{\varepsilon_G}{2k_B T}\right) = 2 \left(\frac{2\pi k_B T}{h^2}\right)^{3/2} (m_e m_h)^{3/4} \exp\left(-\frac{\varepsilon_G}{2k_B T}\right) \quad (2.15)$$

Fermi level  $\varepsilon_F$  is expressed as Eq. 2.16.

$$\varepsilon_F = \frac{\varepsilon_c + \varepsilon_v}{2} + \frac{k_B T}{2} \log\left(\frac{N_v}{N_c}\right) = \frac{\varepsilon_c + \varepsilon_v}{2} + \frac{3k_B T}{4} \log\left(\frac{m_h}{m_e}\right) \quad (2.16)$$

In Eq. 2.16, the first term in the right hand side is sufficiently large compared to the second term. Hence, the Fermi level in a intrinsic semiconductor is approximately at the center of the forbidden band.

From Eq. 2.14, the product of electron density and hole density is a function of temperature  $T$ , providing that  $m_e$ ,  $m_h$  and  $\varepsilon_G$  are given. As temperature increases, the product of electron density and hole density increases exponentially, which indicates that the electrical conductivity increases. This makes it difficult for power semiconductor devices to operate as designed in high temperature. Therefore, the upper limit of the operating temperature for power semiconductor devices depends on the bandgap.

Notably, unipolar devices use the impurity doped layer called the drift layer to ensure breakdown voltage  $V_B$ . The on-resistance of ideal drift region  $R_{on}$  is expressed as Eq. 2.17, where  $e$  is electron elementary charge and  $\mu_e$  is electron mobility.  $W_D$  and  $N_D$  are depletion width and doping concentration, respectively.

$$R_{on} = \frac{W_D}{e\mu_e N_D} \quad (2.17)$$

$W_D$  in Eq. 2.17 is expressed as Eq. 2.18 using  $V_B$  and critical electric field strength  $E_c$ .

$$W_D = \frac{2V_B}{E_c} \quad (2.18)$$

The doping concentration  $N_D$  is expressed as Eq. 2.19, where  $\epsilon_s$  is permittivity.

$$N_D = \frac{\epsilon_s E_c^2}{2eV_B} \quad (2.19)$$

Combing Eq. 2.17 to Eq. 2.19,  $R_{on}$  is expressed as Eq. 2.20, where  $\epsilon_s$ ,  $\mu_e$ , and  $E_c$  are material specific values.

$$R_{on} = \frac{4V_B^2}{\epsilon_s \mu_e E_c^3} \quad (2.20)$$

However, there are little differences in  $\epsilon_s$  between materials as shown in Table 1.1.  $E_c$  has a greater impact than  $\mu_e$  because cubic of  $E_c$  is in denominator of Eq. 2.20. The wider  $E_c$  gives the better trade-off between on-resistance and breakdown voltage.  $E_c$  correlates with bandgap width.

As described above, wide bandgap allows for high temperature operation and improves the trade-off between on-resistance and blocking voltage in unipolar device. Gallium compound power semiconductor devices have wide bandgap and high critical electric field strength, which is expected to improve performance.

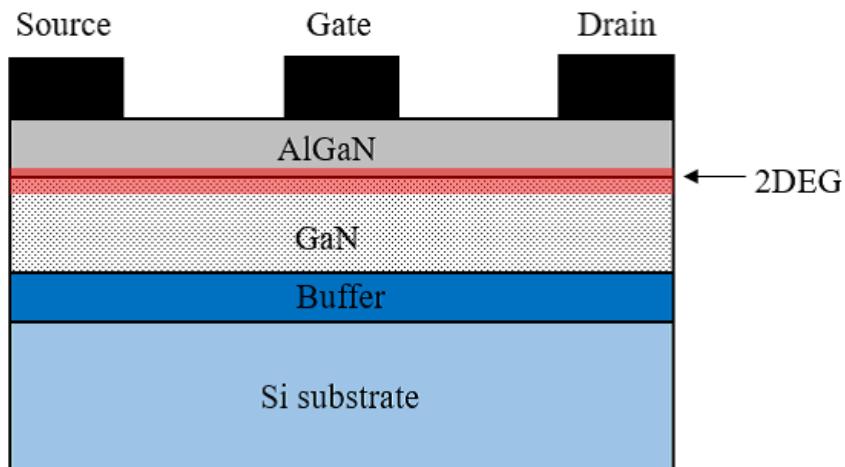

## 2.3 GaN power semiconductor devices

GaN has superior properties due to its wide bandgap and high critical electric field strength as shown in Table 1.1. The majority of GaN power devices currently being investigated are high electron mobility transistor (HEMT) structures using two-dimensional electron gas (2DEG). Figure 2.2 shows the structure of typical normally-on GaN HEMT.

Figure 2.2 Structure of normally-on GaN HEMT.

GaN HEMTs have heterojunctions of GaN and AlGaN in their internal structure. Spontaneous polarization occurs at the interface due to the different lattice constant of GaN and AlGaN. Besides, AlGaN has strain in the layer, which causes piezoelectric

polarization. The sum of those polarization generates 2DEG at the heterojunction boundary, which has very high saturation mobility, resulting in fast switching, and low on-resistance. Heterojunction polarization occurs even when the gate voltage is zero. Therefore, the GaN HEMT in the figure has normally-on characteristics[86].

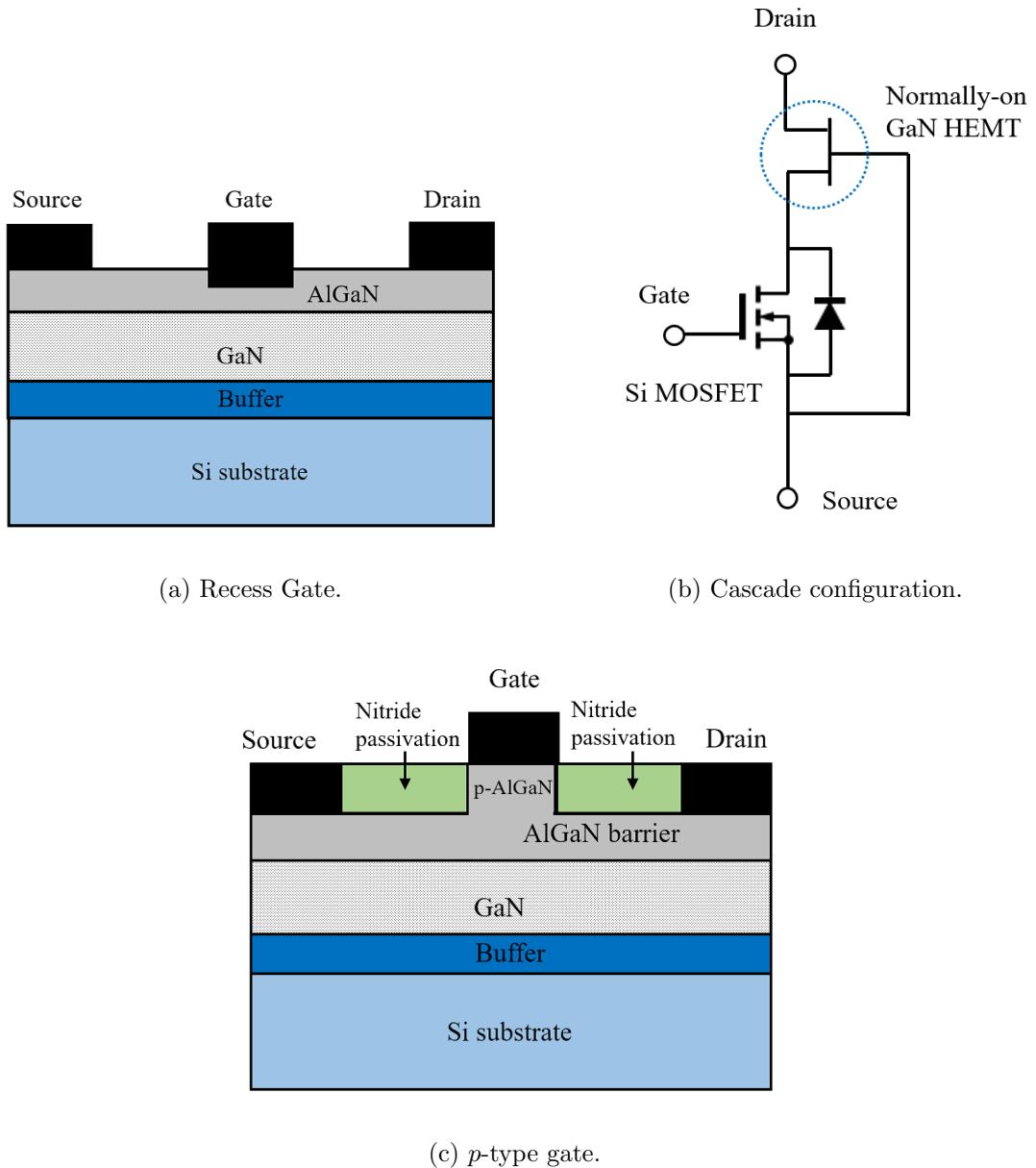

Figure 2.3 Structure and configuration of normally-off GaN HEMT.

In the normally-on characteristic, a failure of the peripheral circuit causes short circuit between the drain and source of the power device, which results in high current

flow. Several structures have been proposed to make GaN power semiconductor devices with normally-off characteristics. Figure 2.3 shows several examples of GaN structures with normally-off characteristics[87][88].

Figure 2.3(a) is called recess gate structure. Recess gates can achieve normally-off without increasing on-resistance. On the other hand, the fabrication process requires the plasma-etching. It is difficult to control the depth of gate recess with plasma etching. The ion bombardment of etching plasma causes damage of power device.

Figure 2.3(b) is called cascade connection. Figure 2.3(b) is series connection of normally-on GaN HEMT shown in Fig. 2.2 and low voltage normally-off Si MOSFET. The gate of GaN HEMT is connected to source of Si MOSFET. In this structure, the Si MOSFET provide normally-off and isolated gate, and the GaN HEMT provide high breakdown voltage. However, in the cascade connection, the on-resistance is the sum of that in Si MOSFET and that in GaN HEMT. Therefore, it is difficult to achieve low on-resistance compared to other structures.

Figure 2.3(c) is called *p*-gate structure. The 2DEG is depleted by processing a *p*-type layer below the gate metal. *p*-type doping and nitride passivation are required for the fabrication. The GaN HEMTs treated in this thesis are basically *p*-type gate structure. The actual cross-sectional structure of GaN HEMTs depends on structure designs determined by the parameters as blocking voltage and forward current.

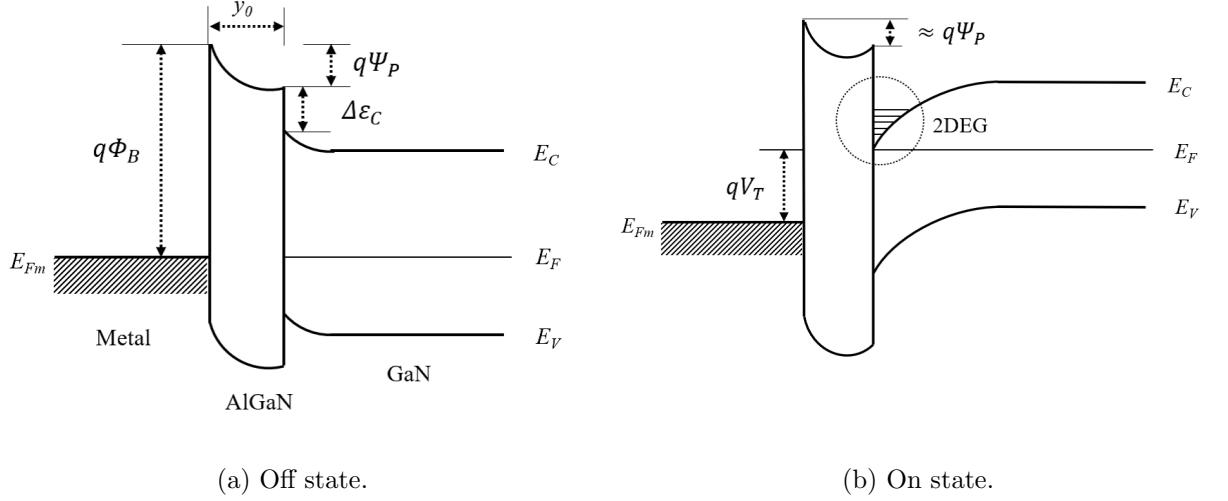

Figure 2.4 shows the band diagram of normally-off GaN HEMT. In normally-off GaN HEMTs, the equilibrium state is the off state and there is no 2DEG under the gate metal. When the gate voltage exceeds the threshold voltage, 2DEG is generated and current can flow between drain and source.  $\Phi_B$  is work function of metal.  $\Delta\varepsilon_c$  is difference of conduction band edge  $\varepsilon_c$ .

Figure 2.4 Band diagram of normally-off GaN HEMT.

The potential variation within the depleted region  $\Psi_p$  is expressed in Eq. 2.21, where  $\epsilon_s$  is permittivity of GaN and  $y_0$  is the thickness of AlGaN layer.

$$\Psi_p = \frac{e N_D y_0^2}{2 \epsilon_s} \quad (2.21)$$

By using  $\Psi_p$ , threshold voltage  $V_{th}$  is expressed as Eq. 2.22.

$$V_{th} \approx \Phi_B - \Psi_p + \frac{\Delta E_c}{e} \quad (2.22)$$

With the condition that gate voltage is higher than the threshold voltage, the charge in the channel  $Q_n$  is expressed as Eq. 2.23.

$$Q_n = C_o (V_G - V_{th}) \quad (2.23)$$

In Eq. 2.23,  $C_o$  is expressed as Eq. 2.24, where  $\Delta y$  is the channel thickness of the 2DEG.

$$C_o = \frac{\epsilon_s}{y_0 + \Delta y} \quad (2.24)$$

Assuming constant carrier mobility, the drain current  $I_D$  is expressed as Eq. 2.25, where  $Z$ ,  $L$ , and  $V_D$  is channel width, channel length, and drain-source voltage.

$$I_D = \frac{Z \mu_e C_o}{L} \left[ (V_G - V_{th}) V_D - \frac{V_D^2}{2} \right] \quad (2.25)$$

In the linear region, where  $V_D \ll (V_G - V_{th})$ , Eq. 2.25 is expressed as Eq. 2.26, where  $I_{Dlin}$  is drain current in linear region.

$$I_{Dlin} = \frac{Z\mu_e C_o (V_G - V_{th}) V_D}{L} \quad (2.26)$$

At high  $V_D$ , pinch-off occurs in the channel. The saturated drain voltage  $V_{Dsat}$  is expressed as Eq. 2.27.

$$V_{Dsat} = V_G - V_{th} \quad (2.27)$$

The saturation drain current  $I_{Dsat}$  is expressed as Eq. 2.28.

$$I_{Dsat} = \frac{Z\mu_e C_o}{2L} (V_G - V_{th})^2 \quad (2.28)$$

From Eq. 2.28, transconductance  $g_m$  is expressed as Eq. 2.29.

$$g_m \equiv \frac{dI_{Dsat}}{dV_G} = \frac{Z\mu_e C_o (V_G - V_{th})}{L} \quad (2.29)$$

The on-resistance of GaN HEMT is expressed as Eq. 2.20. Generally, lateral devices have smaller channel cross-sectional area than vertical devices and are not suitable for high current flow. On the contrary, GaN HEMTs can provide lower on-resistance and higher breakdown voltage than Si MOSFETs due to GaN properties.

GaN HEMTs have not only superior characteristics but also drawbacks. Vertical type power MOSFETs have parasitic *pn* junctions that allow reverse conduction between drain and source, which is called body diode. In order to achieve reverse conduction in GaN HEMTs, the drain and source are made asymmetrically with respect to the gate electrode. This causes charge accumulation on the gate when reverse voltage is applied between the source and drain. This charge forms the channel of the 2DEG, achieving reverse conduction. At this time, the voltage drop of  $V_{th}$  in the gate and that drop due to the channel resistance are generated between the source and drain. The sum of these voltage drops is generally higher than the forward voltage of the body diode of Si power MOSFETs. Therefore, the power loss due to reverse current is higher than that of Si power MOSFETs.

Low loss reverse conduction can be achieved by such methods as connecting SBDs in parallel. However, commercially available GaN power semiconductor devices currently utilize GaN on Si substrates, which make the vertical GaN devices difficult. There

are few commercially available GaN SBDs. Additionally, lateral structure is difficult to use 2DEG in SBDs. Thus, it is difficult to achieve low resistance, high breakdown voltage, and fast switching as vertical structure. Diodes are essential as components of power conversion circuits. Therefore, wide bandgap semiconductors such as  $\beta\text{-Ga}_2\text{O}_3$ , for which single crystals can be fabricated, are expected to be used for diodes.

The parasitic capacitance in the lateral GaN power semiconductor device differs from that of vertical power MOSFETs. The gate-drain and drain-source capacitances of GaN HEMTs are lower than those of vertical devices. Therefore, the amount of charge during switching operation is small, which enables high-speed switching. Soft-switching technology is often used in high-frequency power conversion circuits to reduce switching losses. Soft-switching is based on resonance circuits, where the parasitic capacitance of power semiconductor devices can be used as a component of resonance. In circuits using Si power MOSFETs, parasitic capacitance of power semiconductor devices has been modeled to analyze the conditions of soft-switching[73]-[79]. Nevertheless, the model of power MOSFETs is not applicable for lateral GaN HEMTs. Therefore, it is necessary to consider a parasitic capacitance model suitable for GaN HEMTs.

## 2.4 $\text{Ga}_2\text{O}_3$ power semiconductor devices

$\text{Ga}_2\text{O}_3$  has multiple polymorphs types.  $\alpha$  type and  $\beta$  type are the most expected to be used for power semiconductor devices.  $\alpha$  type has wider bandgap than  $\beta$  type. However,  $\alpha$  type single crystal is grown using heteroepitaxy on sapphire substrates. This makes it difficult to fabricate devices with vertical structures. In addition, the cost of wafers is high due to the sapphire substrates.

$\beta\text{-Ga}_2\text{O}_3$  is capable of growing single crystals from solution under atmospheric pressure. Therefore, it is expected that wafers can be manufactured at low cost. There are already many reports on SBD of  $\beta\text{-Ga}_2\text{O}_3$ [15][16][18]. In addition, lateral and vertical structure transistors using  $\beta\text{-Ga}_2\text{O}_3$  have already been reported[51]-[52]. Nonetheless,  $\text{Ga}_2\text{O}_3$  transistors are still in the research and development stage. This thesis uses  $\beta\text{-Ga}_2\text{O}_3$  SBDs as  $\text{Ga}_2\text{O}_3$  power semiconductor devices.

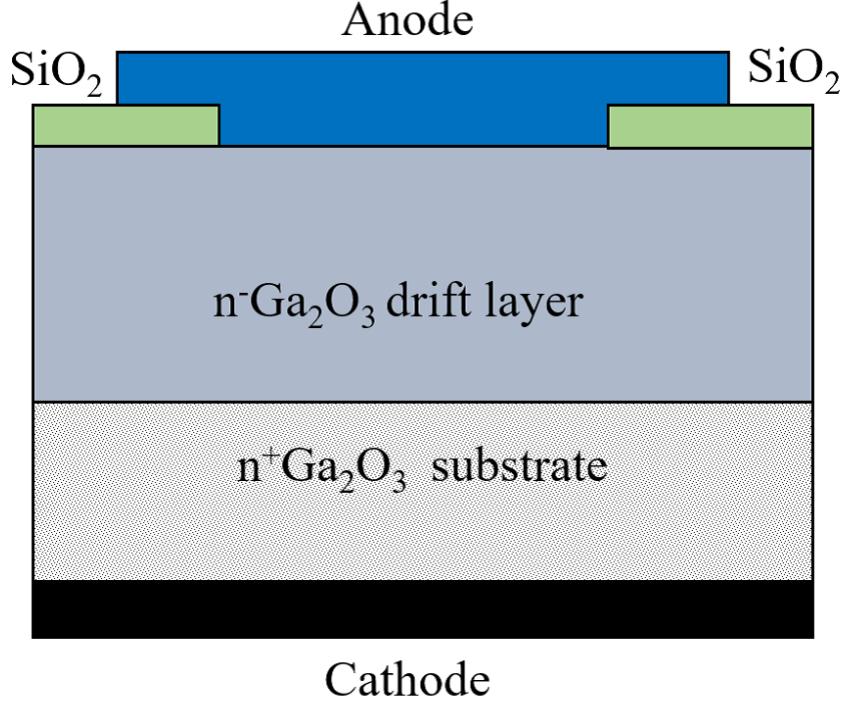

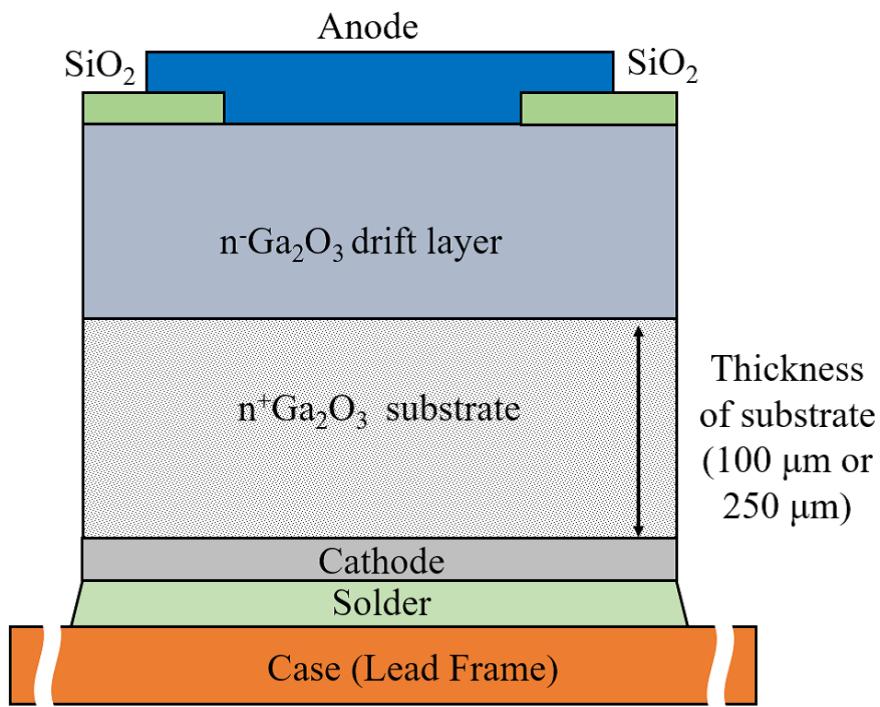

Figure 2.5 shows structure of typical  $\beta\text{-Ga}_2\text{O}_3$  SBD. The SBD in Fig. 2.5 consists

of  $n$  type  $\beta\text{-Ga}_2\text{O}_3$  and a Schottky metal[89][90].

Figure 2.5 Structure of  $\beta\text{-Ga}_2\text{O}_3$  SBD.

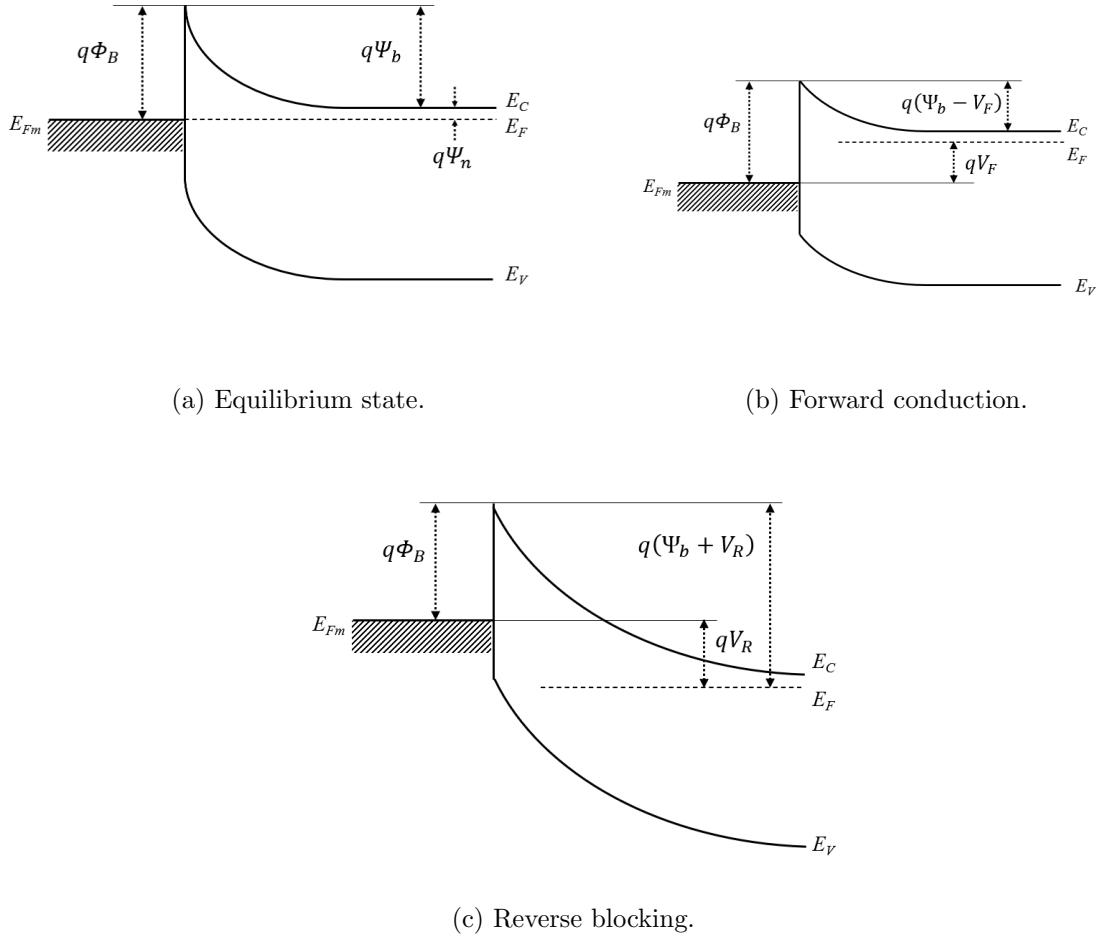

Figure 2.6 shows the band diagram of  $\beta\text{-Ga}_2\text{O}_3$  SBD. The barrier height  $\Phi_B$  is expressed as Eq. 2.30, where  $\Phi_m$  is work function of metal and  $\chi$  is electron affinity of  $\beta\text{-Ga}_2\text{O}_3$ , respectively[91].

$$e\Phi_B = e(\Phi_m - \chi) \quad (2.30)$$

From Eq. 2.30, The Schottky barrier height is determined by the physical properties of the Schottky metal and semiconductor.

When forward voltage is applied to the anode-cathode as shown in Fig. 2.6(b), the forward current density  $J$  is expressed as Eq. 2.31.

$$\begin{aligned} J &= \left( \frac{4\pi em^*k^2}{h^3} \right) T^2 \exp\left(-\frac{e\Phi_B}{kT}\right) \left[ \exp\left(\frac{eV}{kT}\right) - 1 \right] \\ &= A^* T^2 \exp\left(-\frac{e\Phi_B}{kT}\right) \left[ \exp\left(\frac{eV}{kT}\right) - 1 \right] \end{aligned} \quad (2.31)$$

$A^*$  is called effective Richardson constant.  $A^*$  is expressed as Eq. 2.32.

$$A^* = \frac{4\pi em^*k^2}{h^3} \quad (2.32)$$

Figure 2.6 Band diagram of  $\beta\text{-Ga}_2\text{O}_3$  SBD.

Assuming the cross-sectional area of the Schottky junction is  $S$ , the relationship between forward current and voltage is expressed as Eq. 2.33 from Eq. 2.31.

$$\begin{aligned} I_f &= A^* S T^2 \exp\left(-\frac{e\Phi_B}{kT}\right) \left[ \exp\left(\frac{eV}{nkT}\right) - 1 \right] \\ &= I_s \left[ \exp\left(\frac{eV}{nkT}\right) - 1 \right] \end{aligned} \quad (2.33)$$

In Eq. 2.33,  $I_s$  is called saturation current and expressed as Eq. 2.34.

$$I_s = A^* S T^2 \exp\left(-\frac{e\Phi_B}{kT}\right) \quad (2.34)$$

$n$  in Eq. 2.33 is called ideal factor. In ideal SBD,  $n = 1$  and Eq. 2.31 coincide to Eq. 2.33. If the characteristics of the SBD are not ideal,  $n$  deviates from 1. The ideal factor is an indicator of the ideality of the SBD[92]-[95].

When reverse voltage is applied to the anode-cathode as shown in Fig. 2.6(c), the depletion width  $W_D$  is expressed as Eq. 2.35.

$$W_D = \sqrt{\frac{2\epsilon_s}{eN_D} \left( \Psi_b - V_R - \frac{kT}{e} \right)} \quad (2.35)$$

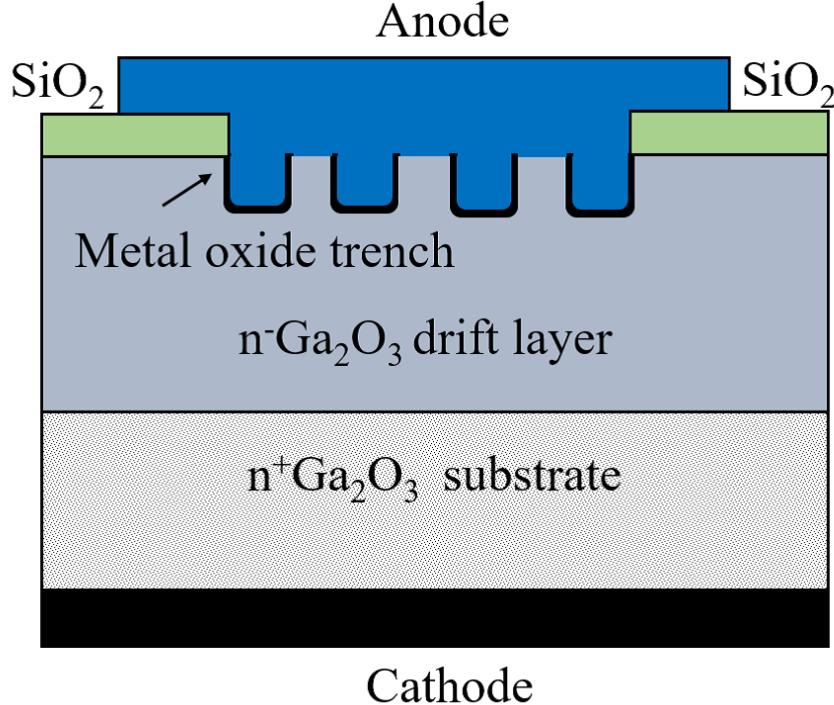

As the reverse voltage is increased, avalanche breakdown occurs when the critical electric field strength is exceeded. This avalanche voltage is the limit breakdown voltage of the SBD. However, in actual SBDs, leakage current flows at the Schottky junction when reverse voltage is applied. Since the critical electric field strength of  $\text{Ga}_2\text{O}_3$  is higher than that of other semiconductors, the blocking voltage is often limited by the leakage current. To reduce leakage current when reverse voltage is applied, trench type structure as shown in Fig. 2.7 has been proposed[96]-[98].

Figure 2.7 Structure of trench type  $\beta\text{-Ga}_2\text{O}_3$  SBD.

Trench type SBD has metal oxide grooves into the Schottky junction. This metal oxide groove is located on the cathode side of the Schottky junction. Therefore, strong

electric field is applied to the Schottky metal and the drift layer across the metal oxide. Since the critical electric field strength of  $\text{Ga}_2\text{O}_3$  is high, the formation of the trench does not cause breakdown voltage reduction. The presence of the trench mitigates the electric field in the Schottky junction when reverse voltage is applied. Therefore, leakage current can be reduced to low level.

$\text{Ga}_2\text{O}_3$  is currently difficult to achieve *p*-type doping. Consequently, trench SBD is an effective method to achieve high blocking voltage. This thesis also evaluates both conventional (planar type) and trench type SBDs.

$\text{Ga}_2\text{O}_3$  is expected to be a useful semiconductor material owing to its trench type structure and other innovations. However, it has a serious drawback.  $\text{Ga}_2\text{O}_3$  has lower thermal conductivity than other semiconductor materials. In vertical SBDs, heat is dissipated from the active area through the die-bonding of the cathode. The heat dissipation performance from this active area to die-bonding is determined by the thermal conducting characteristics of the semiconductor device. Flip mounting has been attempted as a method to reduce the thermal resistance of  $\text{Ga}_2\text{O}_3$  power semiconductor devices[63]. However, while flip mounting is effective for diodes, it cannot be applied to vertical structure transistors due to wiring problems. Therefore, it is important to develop methods for thermal resistance reduction, such as increasing the area of the dies and making it thinner.

## 2.5 Summary

In this chapter, the physical properties and structure of gallium compound power semiconductor devices were described. The wide bandgap semiconductor properties improve the characteristics of power semiconductor devices. GaN HEMTs and  $\text{Ga}_2\text{O}_3$  SBDs considered in this paper were described. GaN HEMTs are capable of high-speed operation with 2DEG. However, they have drawbacks attributable to lateral device structure.

$\beta\text{-Ga}_2\text{O}_3$  is expected as future material for power devices due to its wide bandgap, high critical electric field strength, and ease of single crystal fabrication. Trench structure has been proposed for SBD to reduce leakage current. However, it is essential to

## 2.5 Summary

---

investigate methodologies to reduce thermal resistance for practical use.

# Chapter 3

## Characterization and modeling of magnetic components for class-E amplifier using GaN HEMT

### 3.1 Introduction

Compact, lightweight, and highly efficient power conversion circuits are indispensable for the recent trend. Passive components such as inductors and transformers occupy a large volume in power conversion circuits. Higher operating frequency is effective to reduce their size. The application of switching devices using wide bandgap semiconductors such as GaN and  $\text{Ga}_2\text{O}_3$  is expected to realize high-frequency switching power conversion circuits.

On the other hand, high-frequency operation by hard-switching of power converters leads to increment in switching losses. In order to suppress switching losses, soft-switching is effective. Soft-switching is the technique that the current or voltage becomes zero at the transition of switching.

However, especially in circuit operation above 10 MHz, the loss of magnetic components cannot be ignored. Air-core inductors that do not use magnetic materials are used for high frequency power converters. While air-core inductors do not have iron loss or magnetic saturation caused by magnetic materials, they require a large volume to achieve the inductance necessary for operation. That makes it difficult for

power converters to realize compact and high-density. In addition, the suppression of electromagnetic noise radiated into the space is also an issue. Therefore, there are growing demands for the development of magnetic materials applicable to high-frequency switching power supply circuits.

This section focuses on class-E amplifiers, which can operate with low loss at high frequency by soft-switching. Class-E amplifiers are expected to be a power conversion circuit applicable to wireless power transmission in IoT devices. It is analytically possible to calculate the operation of a class-E amplifier composed of ideal elements. However, actual components do not exhibit ideal characteristics. In particular, magnetic components deviate from ideal electrical characteristics due to the magnetic properties of magnetic cores and parasitic components that depend on the structure of the windings. Magnetic materials with low permeability and low loss that can be used in power supply circuits operating at high frequencies above 10 MHz show particularly large deviations from ideal electrical characteristics. Therefore, in order to design an actual circuits that achieves soft-switching operation, it is necessary to analyze by circuit simulation[99]. Simulation requires the components models that take into account the non-ideal characteristics of magnetic components.

Circuit simulation for the design of 10 MHz band class-E amplifiers requires a circuit element model that can simulate the harmonic characteristics above 10 MHz band. In this section, magnetic characteristics are evaluated by 2-port measurement using a network analyzer for the purpose of evaluation up to high frequency range. Equivalent circuit modeling is performed based on the measurement results. The model parameters are extracted by using the equivalent transformation of the 2-port circuit. In a previous study, an attempt has been made to extract the magnetic properties of magnetic materials such as magnetic thin films from the S-parameters obtained using a network analyzer[22]. There are no examples of magnetic component models used in high-frequency switching power conversion circuits.

In this section, modeling is performed based on S-parameters obtained from 2-port measurements of toroidal cores for inductors used in class-E amplifiers. 2-winding method is a commonly used measurement method for magnetic characteristics such as B-H analyzers. There are no general-purpose measurement equipments for frequency

bands above 10 MHz. For this reason, this section utilizes a 2-port measurement using a network analyzer that measures the reflectance of power, which is different from voltage and current measurements, as a measurement equivalent to the 2-wire method. This method evaluates the magnetic characteristics of inductors and transformers in the frequency band above 10 MHz. This method aims to separately extract equivalent circuit model parameters such as coupling capacitance of windings and leakage inductance, which are problems in the high frequency band. In this section, the validity of the proposed 2-port measurement is verified by comparing with a 1-port measurement. Furthermore, the validity of the circuit simulation using the obtained equivalent circuit model is verified based on the circuit experiment of class-E amplifiers.

## 3.2 Class-E amplifier

This chapter describes the operation of the class-E amplifier under study and issues related to magnetic components used in class-E amplifiers.

### 3.2.1 The operation of a class-E amplifier

Class-E amplifiers can significantly reduce switching losses by soft-switching. Soft-switching used in class-E amplifier is zero voltage switching (ZVS). In ZVS, the voltage applied to the switching device is zero during turn-on and turn-off. In addition, class-E switching utilize zero derivative voltage switching (ZDVS) which sets the rate of voltage change at turn-on and turn-off zero.

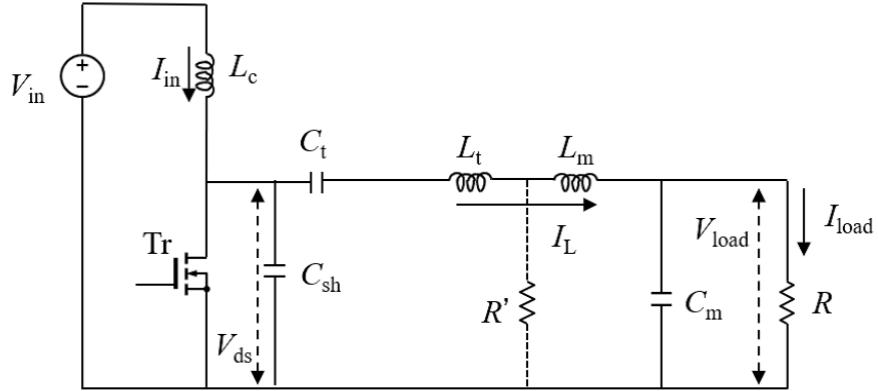

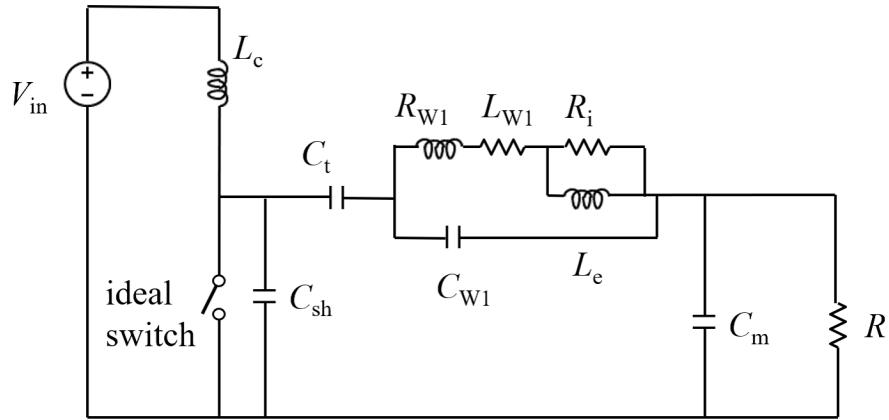

Figure 3.1 shows the circuit diagram of the class-E amplifier discussed in this section. It consists of a class-E amplifier with output impedance  $R'$  and an L-type matching circuit consisting of  $L_m$  and  $C_m$  to match the load impedance  $R$ .

In order to achieve the class-E soft-switching conditions of ZVS and ZDVS, the switching device  $Tr$  is driven with a constant operating frequency  $f$  and a constant duty ratio of 50%. Soft-switching utilizes the resonance phenomenon of  $C_{sh}$ ,  $C_t$ , and  $L_t$ .  $L_c$  is a choke inductor. When the  $L_c$  is high enough, ripple in power supply current  $I_{in}$  is small enough and  $I_{in}$  can be regarded as direct current. The circuit parameters that realizes class-E soft-switching with  $V_{ds} = 0$  and  $dV_{ds}/dt = 0$  at turn-

Figure 3.1 Circuit diagram of class-E amplifier with L type matching circuit.

on of switching device Tr, are given by Eq. 3.1 to Eq. 3.4. This section assumes  $R' < R$  and  $Q_L = (2\pi f L_t)/R' > 1.7879$ , where the  $Q_L$  is quality factor of  $L_t$  and  $R'$ .  $\omega$  is expressed as  $\omega = 2\pi f$ .

$$C_{sh} = \frac{1}{\omega R' \left( \frac{\pi^2}{4} + 1 \right) \frac{\pi}{2}} \left( 0.9987 + \frac{0.9142}{Q_L} - \frac{1.0318}{Q_L^2} \right) + \frac{0.6}{\omega^2 L_c} \quad (3.1)$$

$$C_t = \frac{1}{\omega R'} \left( \frac{1}{Q_L - 0.1048} \right) + \left( 1.0012 + \frac{1.0147}{Q_L - 1.7879} \right) - \frac{0.2}{\omega^2 L_c} \quad (3.2)$$

$$L_m = \frac{R'}{\omega} \sqrt{\frac{R}{R'} - 1} \quad (3.3)$$

$$C_m = \frac{1}{R\omega} \sqrt{\frac{R}{R'} - 1} \quad (3.4)$$

The drain-source voltage applied to switching device Tr is expressed in Eq. 3.5.

$$V_{ds} = \begin{cases} 0 & 0 < \omega \leq \pi \\ V_{in}\pi \left( \omega t - \frac{3\pi}{2} - \frac{\pi}{2} \cos \omega t - \sin \omega t \right) & \pi < \omega \leq 2\pi \end{cases} \quad (3.5)$$

The drain current conducting in switching device is expressed in Eq. 3.6, where  $\phi = 2.575$  rad.

$$I_d = \begin{cases} I_{in} \left( 1 - \frac{\sqrt{\pi^2 + 4}}{2} \sin (\omega t + \phi) \right) & 0 < \omega \leq \pi \\ 0 & \pi < \omega \leq 2\pi \end{cases} \quad (3.6)$$

Equation 3.5 indicates that the maximum value of  $V_{ds}$  is 3.562 times  $V_{in}$ . Equation 3.6 indicates that the maximum value of  $I_d$  is 2.575 times  $I_{in}$ . Circuit topologies such as class-E/F and class- $\Phi_2$  have been proposed to suppress the maximum value.

### 3.2.2 Issues in the design of class-E amplifiers

Equations 3.1 to 3.3 give the soft-switching conditions for a class-E amplifier. They are for ideal elements and not for actual elements and circuits with parasitic components. In the design of a class-E amplifier, it is necessary not only to design circuit components but also to analyze the behavior in actual circuits with parasitic components. For this purpose, circuit simulation is used, which requires a detailed model to simulate the characteristics of components.

In the circuit of Fig. 3.1, the output impedance  $R'$  of the class-E amplifier is not directly implemented in the circuit, but it is connected to the load  $R$  via a matching circuit. Therefore, the characteristics of the inductor affect not only the soft-switching operation, but also the impedance matching between the output and the load.

In the high-frequency switching operation at 10 MHz in this study, the inductor deviates significantly from ideal characteristics due to losses and parasitic components in the cores and windings. It cannot be considered as an ideal components like other passive devices.

Losses in magnetic components are mainly caused by iron and copper losses. The model used in circuit simulation must be able to account for these losses in detail. Section 3.3 describes how to evaluate the magnetic properties of an inductor used in a class-E soft-switching circuit and how to extract the model parameters for the electrical characteristics.

## 3.3 Evaluation and modeling of magnetic properties for power inductors

This section discusses a method for evaluating the magnetic characteristics of inductors used in class-E amplifiers for switching operation at 10 MHz and a model for circuit

simulation.

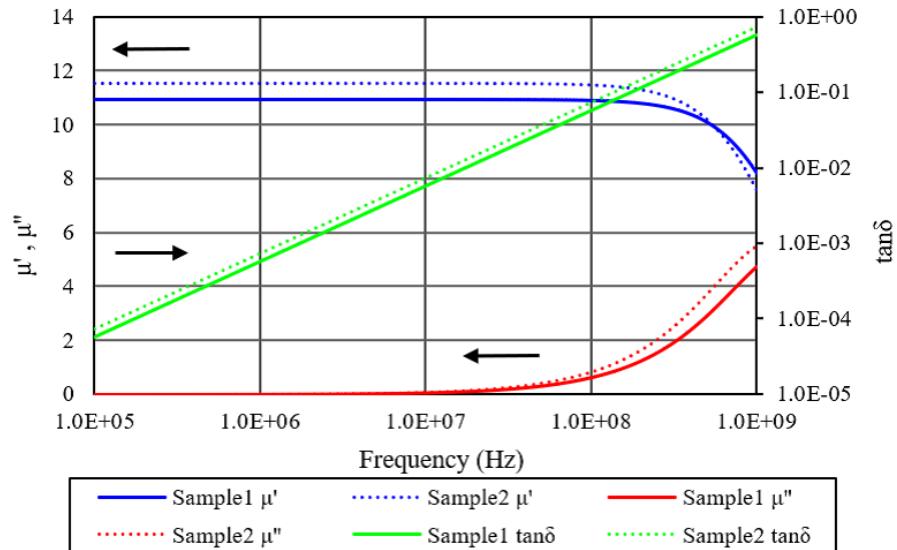

### 3.3.1 Magnetic materials considered in this chapter

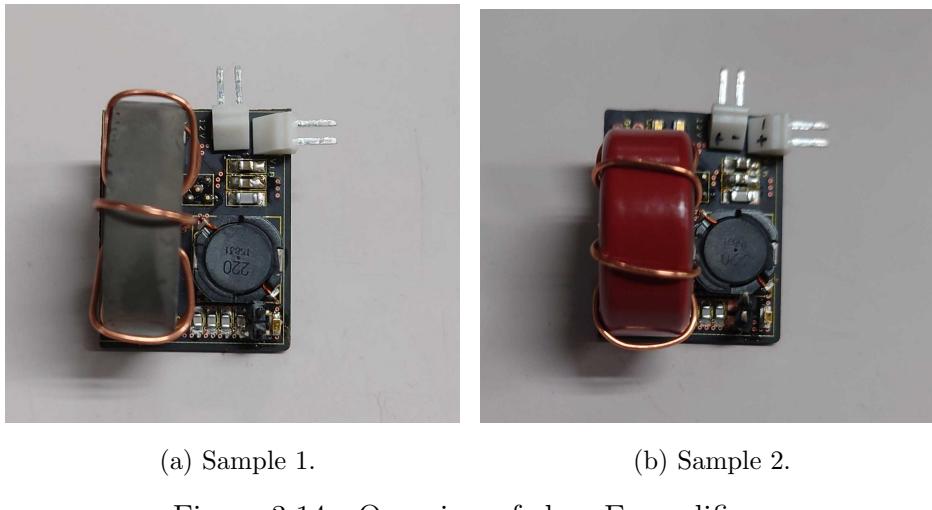

This chapter considers iron-based metal composite material and carbonyl iron composite material as low-loss magnetic materials for use in class-E amplifiers with switching operation at 10 MHz. The iron-based metal composite material is a composite of iron-based amorphous alloy with an average grain size of  $2.56 \mu\text{m}$ , which is solidified with epoxy resin. The ratio of magnetic material is 91.5 wt.%. The core is molded into a toroidal shape and annealed at  $300^\circ\text{C}$  for 3 hours. The iron-based metal composite material is Sample 1. The carbonyl iron powder material is toroidal core T106-2 (Micrometals), which is Sample 2. The magnetic path of a toroidal core is isotropic with respect to the windings. This makes it a suitable for the evaluation of magnetic properties. However, toroidal cores have the problem of increasing volume compared to other types of cores.

Table 3.1 shows the core specifications. Relative permeability (Typ) is the datasheet value of the specific magnetic permeability of each core. Both sample 1 and sample 2 have saturation flux densities of 1.2 T or higher[100].

Table 3.1 Specifications of magnetic cores.

|                                          | Sample 1 | Sample 2 |

|------------------------------------------|----------|----------|

| Outer diameter (mm)                      | 30.0     | 26.9     |

| Inner diameter (mm)                      | 10.0     | 14.5     |

| Height (mm)                              | 8.87     | 11.1     |

| Mass (g)                                 | 27.1     | 21.0     |

| Magnetic pass length (mm)                | 62.8     | 64.9     |

| Magnetic cross section ( $\text{mm}^2$ ) | 88.7     | 65.9     |

| Volume ( $\text{mm}^3$ )                 | 5570     | 4280     |

| Relative Permeability (Typ.)             | 9.6      | 10       |

| Saturation magnetization (T)             | 1.26     | 1.48     |

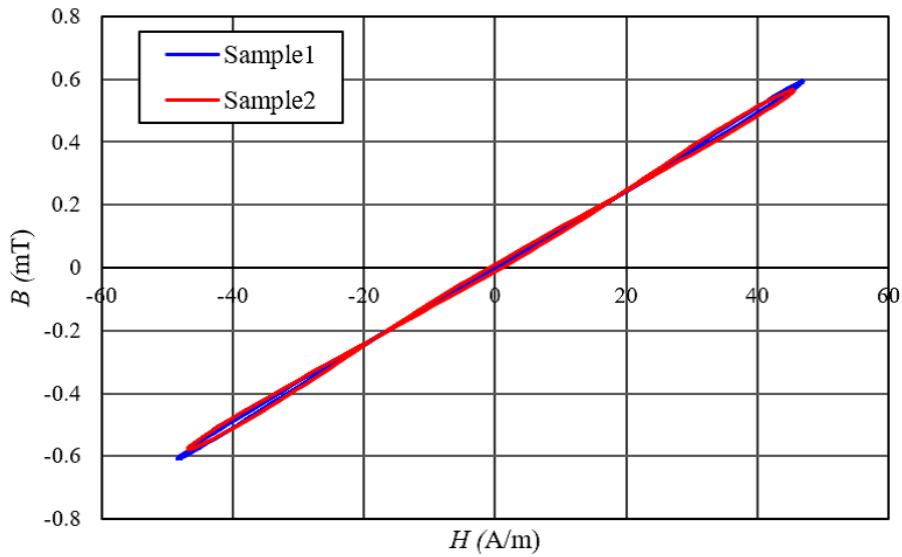

Figure 3.2 shows the magnetic properties at 10 MHz measured with a B-H analyzer (SY-8218, Iwatsu). Both the excitation and detection windings are 6 turns of 0.8 mm

diameter single copper enameled wire. They are the same as the inductors for class-E amplifier designed in Sect. 3.4. A power amplifier (HSA 4101-IW, NF Corporation) is used for excitation. Magnetic saturation is not observed at the maximum possible magnetic flux density of 0.6 mT. Hysteresis loss is very low and difficult to measure.

Figure 3.2 Magnetization characteristics measured with B-H analyzer.

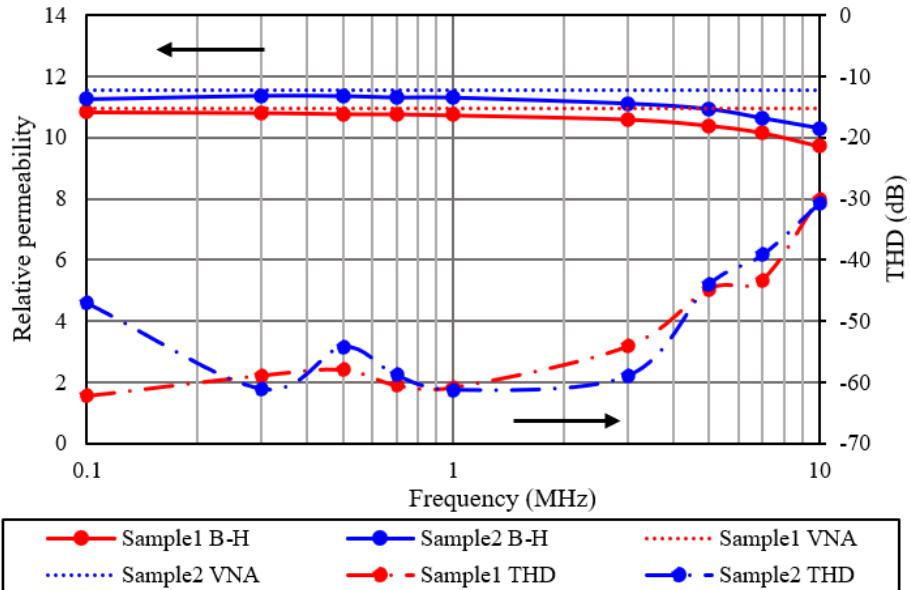

Figure 3.3 shows the permeability measured by the B-H analyzer (solid line). Dash-dot lines are the THD of the current at the time of measurement. The permeabilities measured by the network analyzer are shown in Fig. 3.3, which are described in Sect. 3.3.2. The excitation current is set to 600 mA during the measurement.

Figure 3.3 Permeability measured with B-H analyzer and vector network analyzer.

In the measurement with the B-H analyzer, the total harmonic distortion (THD) is  $-30$  dB or higher at  $5$  MHz and above. The accuracy of the measurement is degraded, and magnetic characteristics can not be measured precisely. Therefore, this section attempts to measure the magnetic characteristics using other methods.

### 3.3.2 Evaluation of magnetic components using 2-port equivalent circuit model

This study considers a configuration equivalent to the 2-winding method of the B-H analyzer. In B-H analyzer measurements, excitation and detection are performed in individual windings. This thesis attempts to evaluate magnetic characteristics by 2-port S-parameter measurement using a network analyzer. Although the measurement signal from the network analyzer is small, the saturation flux density of the target magnetic material is  $1.2$  T or higher. The flux density applied to the magnetic components in the circuit considered in this thesis is  $5$  mT or lower. Under the conditions in this thesis, it is considered possible to evaluate magnetic properties even with measurements using a network analyzer.

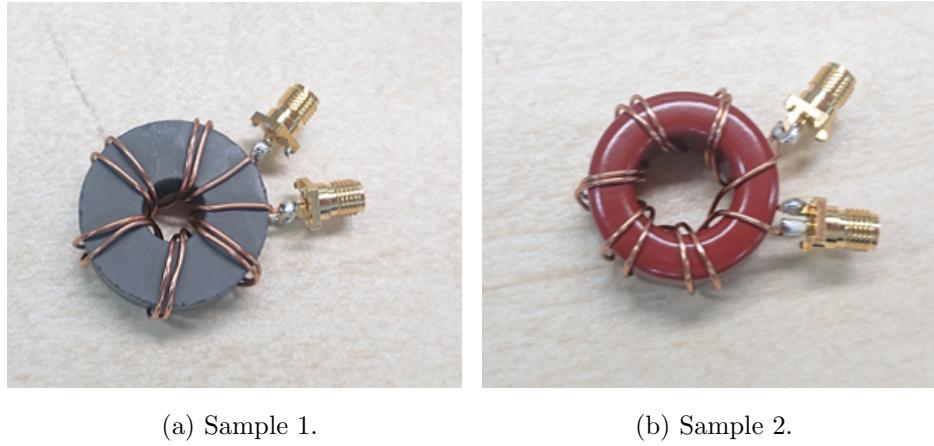

Figure 3.4 shows the winding and connector of the toroidal core used for the 2-port

measurement of the network analyzer. The windings are 6:6 turns bifilar windings of 0.8 mm diameter single copper enameled wire. The terminals are SMA connectors, which are the reference plane connected to a network analyzer.

Figure 3.4 Overview of magnetic components under evaluation.

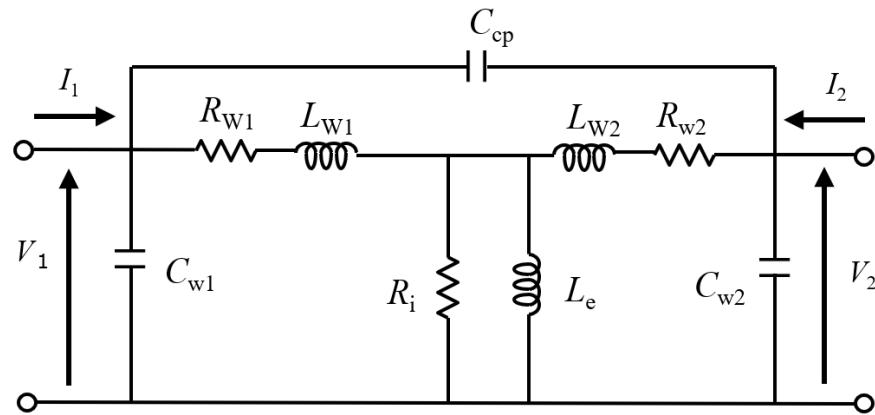

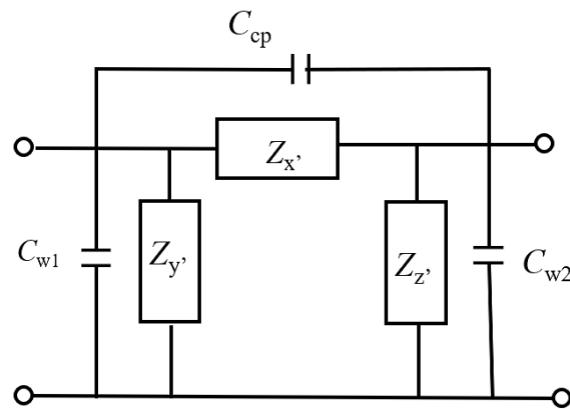

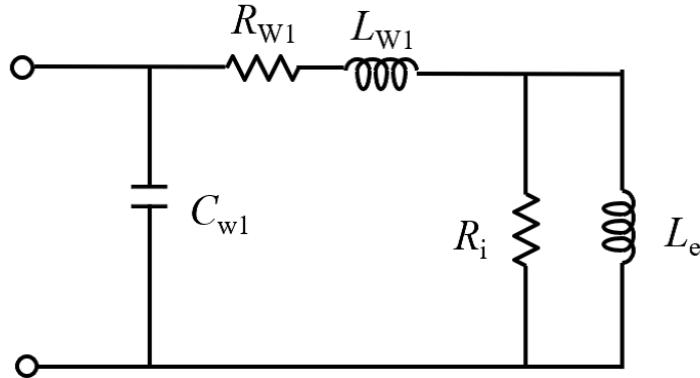

In this thesis, the magnetic properties are evaluated based on the 2-port S-parameter measurement using a network analyzer (E5061B, Agilent Technologies). The magnetic components are modeled with 2-port equivalent circuit. Figure 3.5 shows the 2-port equivalent circuit model considered in this thesis.

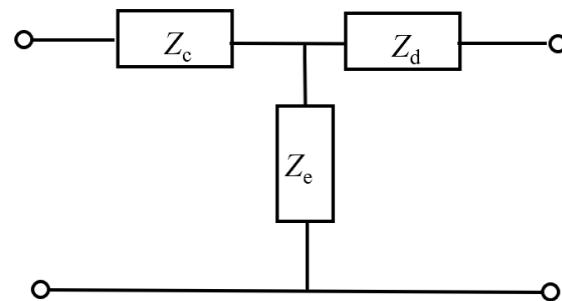

Figure 3.5 2-port equivalent circuit model of magnetic component.

In Fig. 3.5,  $C_{W1}$  and  $C_{W2}$  are the parasitic capacitances of each winding.  $R_{W1}$  and  $R_{W2}$  are the resistances of each winding.  $L_{W1}$  and  $L_{W2}$  are the leakage inductances.

$R_i$  is the iron loss resistance.  $L_e$  is the excitation inductance.  $C_{cp}$  is the coupling capacitance. The equivalent circuit model of a transformer in the low-frequency range consists only of inductance and resistance[101]. However, in the high-frequency range, the capacitance of the windings cannot be ignored[102]. Therefore, this thesis uses a model including capacitance as Fig. 3.5. The relationship between the impedance and S-parameters of a 2-port circuit is expressed by Eq. 3.7, where  $Z_0$  is the reference impedance connected to each port.

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} \frac{(1+S_{11})(1-S_{22})+S_{12}S_{21}}{(1-S_{11})(1-S_{22})-S_{12}S_{21}} Z_0 & \frac{2S_{12}}{(1-S_{11})(1-S_{22})-S_{12}S_{21}} Z_0 \\ \frac{2S_{21}}{(1-S_{11})(1-S_{22})-S_{12}S_{21}} Z_0 & \frac{(1-S_{11})(1+S_{22})+S_{12}S_{21}}{(1-S_{11})(1-S_{22})-S_{12}S_{21}} Z_0 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

$$= \begin{bmatrix} Z_{11} & Z_{12} \\ Z_{21} & Z_{22} \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix} \quad (3.7)$$

The relationships between the component parameters in Fig. 3.5 and the Z parameters are expressed by the following equations.

$$Z_{11} = \frac{Z_\beta(Z_\alpha + Z_\gamma)}{Z_\alpha + Z_\beta + Z_\gamma} \quad (3.8)$$

$$Z_{12} = \left( \frac{Z_\beta}{Z_\beta + Z_\alpha} \right) \left( \frac{Z_\gamma(Z_\alpha + Z_\beta)}{Z_\alpha + Z_\beta + Z_\gamma} \right) \quad (3.9)$$

$$Z_{21} = \left( \frac{Z_\gamma}{Z_\gamma + Z_\alpha} \right) \left( \frac{Z_\beta(Z_\alpha + Z_\gamma)}{Z_\alpha + Z_\beta + Z_\gamma} \right) \quad (3.10)$$

$$Z_{22} = \frac{Z_\gamma(Z_\alpha + Z_\beta)}{Z_\alpha + Z_\beta + Z_\gamma} \quad (3.11)$$

$Z_\alpha$ ,  $Z_\beta$ , and  $Z_\gamma$  are expressed by the following equations.

$$Z_\alpha = \frac{Z_f(Z_cZ_d + Z_eZ_c + Z_dZ_e)}{Z_eZ_f + Z_cZ_d + Z_eZ_c + Z_dZ_e} \quad (3.12)$$

$$Z_\beta = \frac{Z_a(Z_cZ_d + Z_eZ_c + Z_dZ_e)}{Z_dZ_a + Z_cZ_d + Z_eZ_c + Z_dZ_e} \quad (3.13)$$

$$Z_\gamma = \frac{Z_b(Z_cZ_d + Z_eZ_c + Z_dZ_e)}{Z_cZ_b + Z_cZ_d + Z_eZ_c + Z_dZ_e} \quad (3.14)$$

$Z_a$ ,  $Z_b$ ,  $Z_c$ ,  $Z_d$ ,  $Z_e$ , and  $Z_f$  in Eq. 3.12 to Eq. 3.14 are expressed by the following

equations.

$$Z_a = -j \frac{1}{\omega C_{W1}} \quad (3.15)$$

$$Z_b = -j \frac{1}{\omega C_{W2}} \quad (3.16)$$

$$Z_c = R_{W1} + j\omega L_{W1} \quad (3.17)$$

$$Z_d = R_{W2} + j\omega L_{W2} \quad (3.18)$$

$$Z_e = \frac{j\omega R_i L_e}{R_i + j\omega L_e} \quad (3.19)$$

$$Z_f = -j \frac{1}{\omega C_{cp}} \quad (3.20)$$

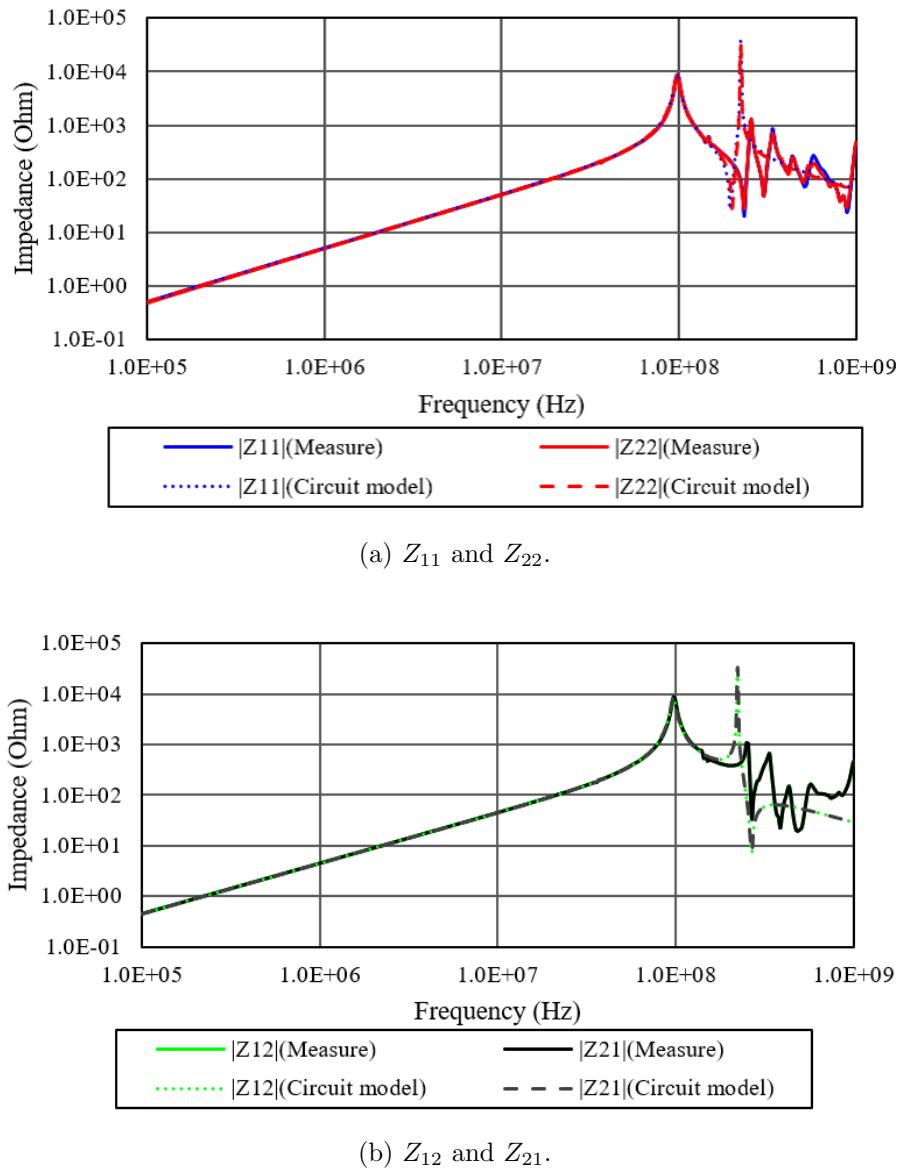

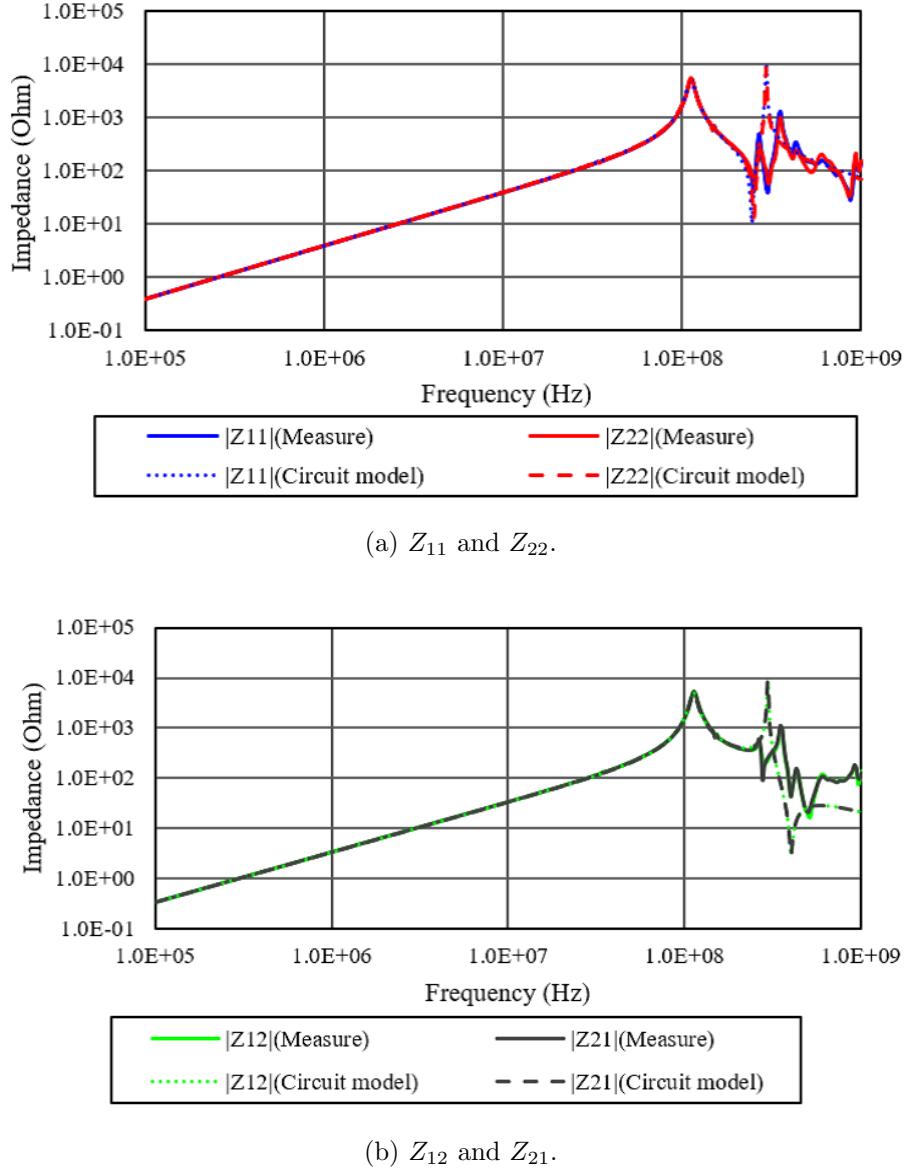

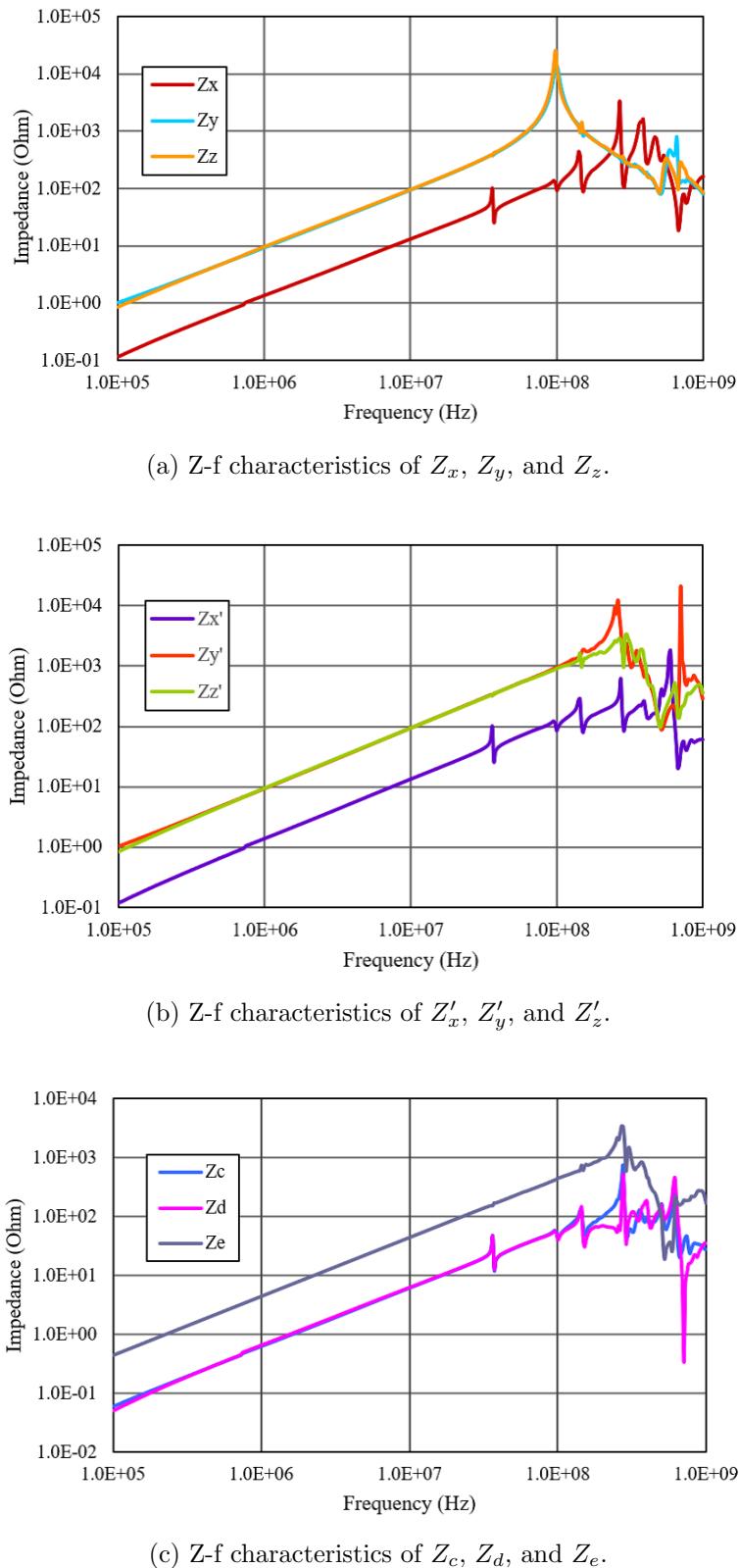

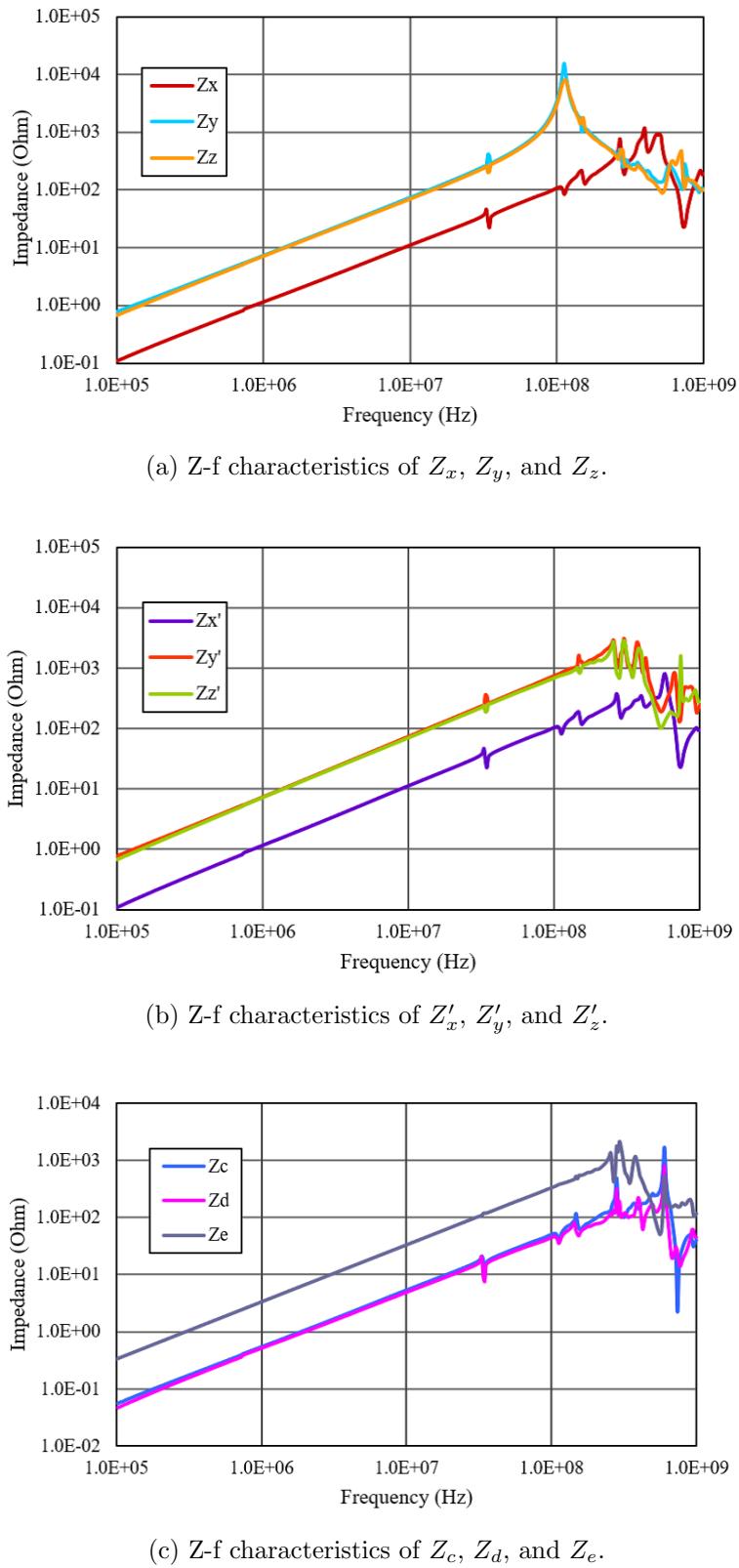

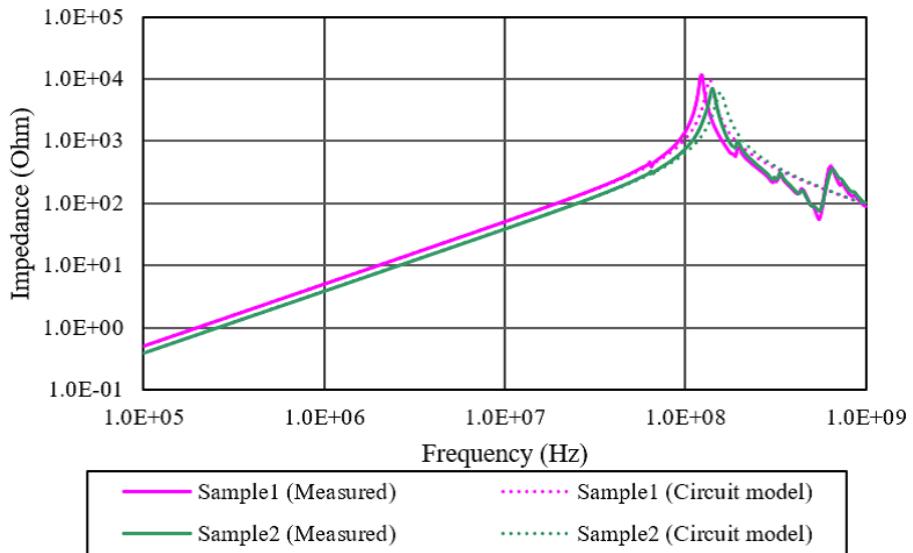

The (Measure) in Fig. 3.6 and Fig. 3.7 show the frequency responses of the impedance in the 2-port circuit calculated from the measurement results. The frequency responses of  $Z_{12}$  and  $Z_{21}$  are almost identical for both Sample 1 and Sample 2. This indicates that duality is established, and the 2-port circuit can be treated as a linear time-invariant circuit.

Figure 3.6 Measured and circuit modeled time response of Z-parameter for Sample 1.

Figure 3.7 Measured and circuit modeled time response of Z-parameter for Sample 2.

The (Circuit model) in Fig. 3.6 and Fig. 3.7 show the frequency characteristics of the Z-parameters obtained using the equivalent circuit model shown in Fig. 3.5. The circuit parameters are obtained by the extraction method described below.

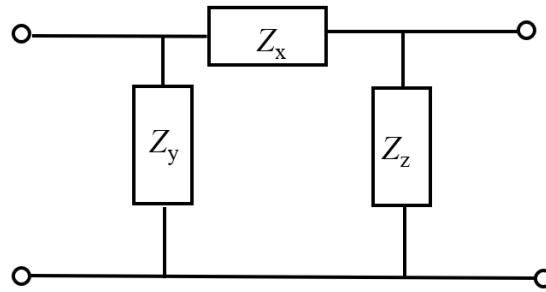

The 2-port circuit is represented by the  $\pi$ -type circuit in Fig. 3.8(a). Each element is expressed using the Z parameter as Eq. 3.21 to Eq. 3.23.

(a)  $\pi$ -type circuit of 2-port model.

(b)  $\pi$ -type circuit with capacitance and residual impedance.

(c) T-type circuit without capacitance.

Figure 3.8 Equivalent circuits of 2-port circuit model.

$$Z_x = \frac{Z_{11}Z_{22} - Z_{12}^2}{Z_{12}} \quad (3.21)$$

$$Z_y = \frac{Z_{11}Z_{22} - Z_{12}^2}{Z_{22} - Z_{12}} \quad (3.22)$$

$$Z_z = \frac{Z_{11}Z_{22} - Z_{12}^2}{Z_{11} - Z_{12}} \quad (3.23)$$

Figure 3.9(a) and Figure 3.10(a) show the frequency response of  $Z_x$ ,  $Z_y$ , and  $Z_z$  for Sample 1 and 2. The inductance and resistance that constitute the T-type circuit in Fig. 3.5 are converted to the  $\pi$ -type circuit. As shown in Fig. 3.8(b),  $Z_x$  is a parallel circuit of  $Z'_x$  and  $C_{cp}$ .  $Z_y$  is a parallel circuit of  $Z'_y$  and  $C_{W1}$ .  $Z_z$  is a parallel circuit of  $Z'_z$  and  $C_{W2}$ .

As shown in Fig. 3.9(a) and Fig. 3.10(a), the frequency characteristics of  $Z_x$ ,  $Z_y$ , and  $Z_z$  vary by 20 dB/dec in the low frequency range respectively. The frequency characteristics of  $Z_x$ ,  $Z_y$ , and  $Z_z$  vary by  $-20$  dB/dec in the region above the self-resonant frequency. Therefore, it can be regarded as an LC parallel circuit. The capacitive elements are low and the impedance can be considered inductive below 10 MHz. The inductive elements of  $Z'_x$ ,  $Z'_y$ , and,  $Z'_z$  are obtained by the least-squares approximation of the double logarithmic function for the frequency characteristics of each Z-f characteristics.

In the Z-f characteristics shown in Fig. 3.9(a) and Fig. 3.10(a), the capacitances  $C_{cp}$ ,  $C_{W1}$ , and  $C_{W2}$  are obtained from the self-resonance frequency  $f = 1/2\pi\sqrt{LC}$  at which the value of  $|Z|$  is maximum. The self-resonant frequencies of Sample 1 and 2 are shown in Table 3.2.

Table 3.2 Self-resonant frequencies of  $Z_x$ ,  $Z_y$ , and  $Z_z$ .

|          |       |          |

|----------|-------|----------|

| Sample 1 | $Z_x$ | 269 MHz  |

|          | $Z_y$ | 97.7 MHz |

|          | $Z_z$ | 97.7 MHz |

| Sample 2 | $Z_x$ | 398 MHz  |

|          | $Z_y$ | 112 MHz  |

|          | $Z_z$ | 112 MHz  |

Figure 3.9 Z-f characteristics of 2-port circuit model elements for Sample 1.

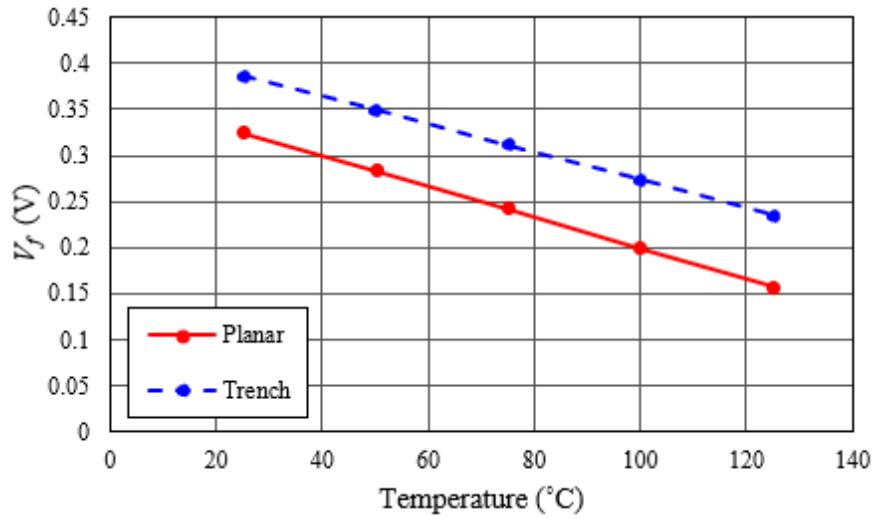

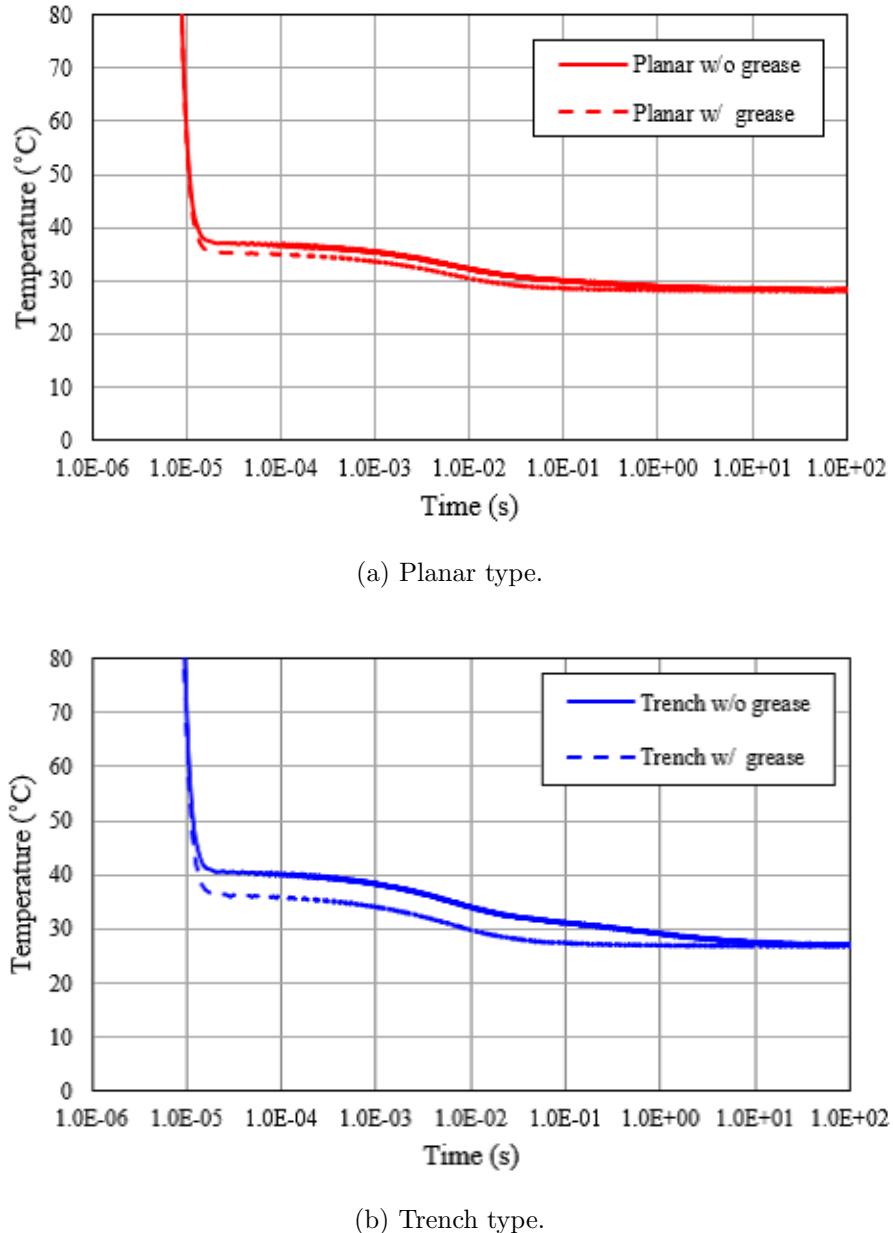

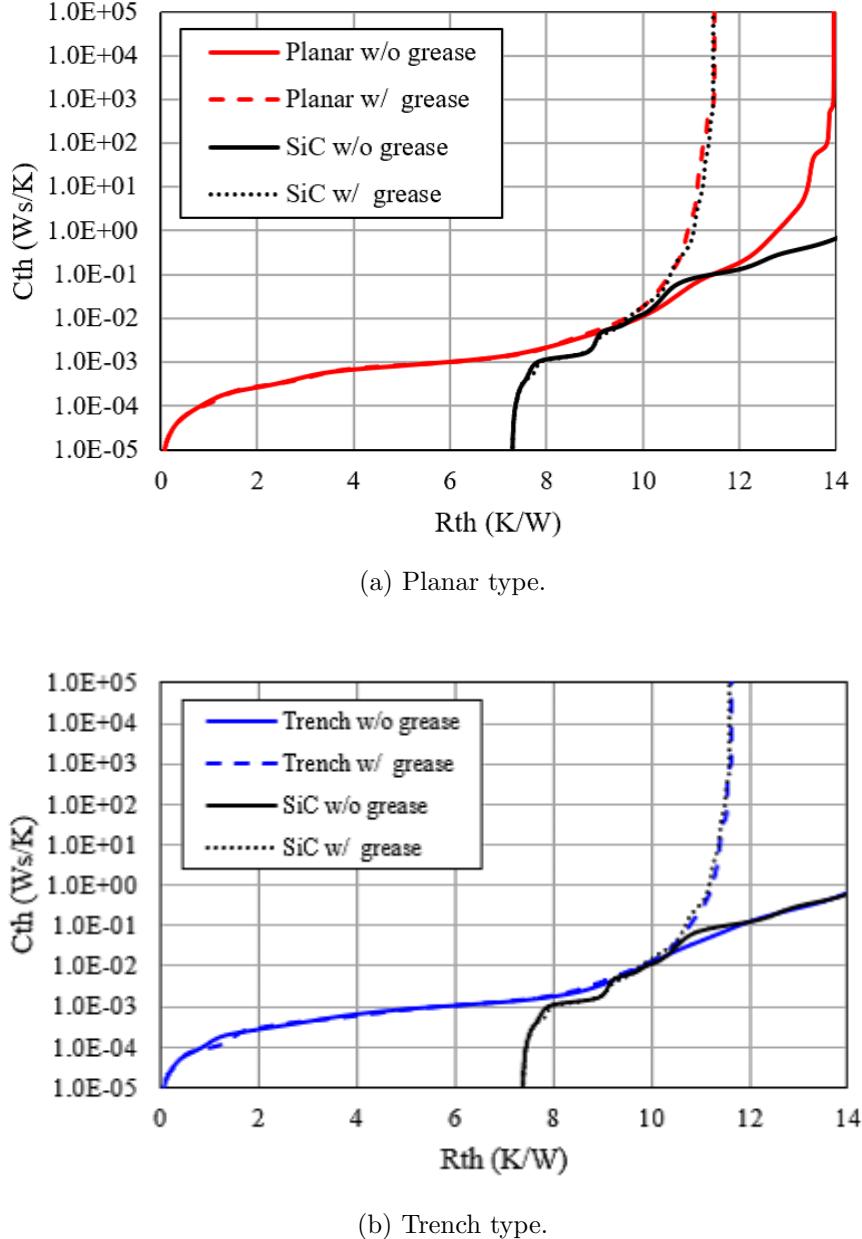

Figure 3.10 Z-f characteristics of 2-port circuit model elements for Sample 2.