|              |                                                                                                                                                                                                                                                                                                                       |

|--------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Title        | Gate stress-induced mobility degradation in NO-nitrided SiC(0001) MOSFETs                                                                                                                                                                                                                                             |

| Author(s)    | Kobayashi, Takuma; Koyanagi, Kaho; Hirai, Hirohisa et al.                                                                                                                                                                                                                                                             |

| Citation     | Applied Physics Letters. 2024, 125(25), p. 252101                                                                                                                                                                                                                                                                     |

| Version Type | AM                                                                                                                                                                                                                                                                                                                    |

| URL          | <a href="https://hdl.handle.net/11094/98804">https://hdl.handle.net/11094/98804</a>                                                                                                                                                                                                                                   |

| rights       | This article may be downloaded for personal use only. Any other use requires prior permission of the author and AIP Publishing. This article appeared in Appl. Phys. Lett. 16 December 2024; 125 (25): 252101 and may be found at <a href="https://doi.org/10.1063/5.0245907">https://doi.org/10.1063/5.0245907</a> . |

| Note         |                                                                                                                                                                                                                                                                                                                       |

*The University of Osaka Institutional Knowledge Archive : OUKA*

<https://ir.library.osaka-u.ac.jp/>

The University of Osaka

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

## Gate stress-induced mobility degradation in NO-nitrided SiC(0001) MOSFETs

Takuma Kobayashi<sup>1,\*</sup>, Kaho Koyanagi<sup>1</sup>, Hirohisa Hirai<sup>2</sup>, Mitsuru Sometani<sup>1,2</sup>, Mitsuo Okamoto<sup>2</sup>, and Heiji Watanabe<sup>1</sup>

<sup>1)</sup>*Graduate School of Engineering, Osaka University, Suita Osaka 565-0871, Japan*

<sup>2)</sup>*National Institute of Advanced Industrial Science and Technology, Tsukuba, Ibaraki*

*305-8569, Japan*

E-mail: kobayashi@prec.eng.osaka-u.ac.jp

The impacts of gate voltage stress on the on-state characteristics of NO-nitrided SiC(0001) MOSFETs were examined. A strong negative voltage stress at 300°C induced a decrease in the channel mobility of the MOSFETs. This mobility decrease occurred along with an increase in the interface state density. Through MOS Hall effect measurements, we proposed a model in which the stress-induced interface states are located on the SiC side of the interface, close to where free electrons in the MOS channel are confined, thereby acting as a strong source of Coulomb scattering.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

1     Silicon carbide (SiC) is a material characterized by a wide bandgap, high critical electric

2     field, and high thermal conductivity<sup>1)</sup>. These properties make SiC metal-oxide-

3     semiconductor field-effect transistors (MOSFETs) promising as power switching devices.

4     However, the performance of practical SiC MOSFETs is limited by their high channel

5     resistance ( $R_{ch}$ )<sup>2)</sup>.  $R_{ch}$  is governed by two factors: the free carrier density ( $n_{free}$ ) and the

6     mobility of free electrons<sup>3)</sup>. The  $n_{free}$  is determined by the interface state density ( $D_{it}$ ) of the

7     MOS structure; increased electron trapping results in fewer free electrons in the MOS

8     channel.  $D_{it}$  values are known to be very high in SiC MOS structures, exceeding  $10^{14} \text{ cm}^{-2}\text{eV}^{-1}$  near the conduction band edge ( $E_c$ ) of SiC<sup>3)-5)</sup>. Although the origin of the interface

9     states is uncertain, carbon-related defects generated during the thermal oxidation of SiC are

10    a primary candidate, as suggested both experimentally<sup>6)-8)</sup> and theoretically<sup>9)-12)</sup>. Interface

11    nitridation in a nitric oxide (NO) ambient is the standard method for defect passivation at

12    the SiC MOS interface<sup>13),14)</sup>. While there are reliability concerns with nitridation<sup>15)-17)</sup>, it is

13    evident that  $D_{it}$  passivation leads to an increase in  $n_{free}$ . The mobility of free electrons is

14    typically represented by the Hall mobility ( $\mu_{Hall}$ ) obtained from MOS Hall effect

15    measurements. However, clarifying the limiting factors of  $\mu_{Hall}$  is not straightforward.

16    Previous studies have reported that nitridation unexpectedly results in a decrease in  $\mu_{Hall}$ <sup>3),18)</sup>.

17    The difficulty lies in the fact that while nitridation passivates interface states, it can also lead

18    to the generation of fast interface states<sup>19),20)</sup>, fixed charges<sup>21)</sup>, and interface dipoles<sup>16),22)</sup>.

19    Although both experimental<sup>23)-26)</sup> and theoretical studies<sup>27),28)</sup> have investigated the limiting

20    factors of  $\mu_{Hall}$ , the complicated situation makes it difficult to resolve the factors that

21    determine mobility. Thus, a means to change the density of interface states and fixed charges

22    in a controlled manner is needed to help clarify the mobility-limiting factors.

23

24    In the present study, we focused on how gate voltage stress affects the on-state

25    characteristics of MOSFETs. In terms of reliability, the effect of gate stress has been

26    extensively studied<sup>16),29)-32)</sup>, highlighting the impacts of post-deposition annealing<sup>30)</sup>, crystal

27    faces<sup>16)</sup>, measurement methods<sup>31)</sup>, and practical device processing<sup>32)</sup>. While it is well known

28    that gate voltage stress induces carrier trapping in the oxide, it can also cause additional

29    interface states depending on the stress conditions<sup>33),34)</sup>. We aim to control the density of

30    interface states and fixed charges by adjusting the stress conditions, thereby gaining insight

31    into the mobility-limiting factors of SiC MOSFETs.

32

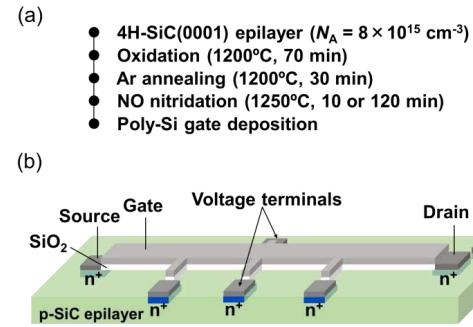

33    Figure 1(a) describes the gate stack formation process of MOSFETs and MOS Hall bars

34    in this study. We used *p*-type SiC(0001) epilayers (acceptor density:  $8 \times 10^{15} \text{ cm}^{-3}$ ). After wet

cleaning, the oxide was formed by dry oxidation and Ar annealing at 1200°C, followed by

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

1 NO annealing at 1250°C for either 10 or 120 min. Poly-Si was used as the gate electrode

2 material. The channel length and width of the MOSFETs (MOS Hall bars) were 5 (300) and

3 200 (40)  $\mu\text{m}$ , respectively. We focused on the impact of negative gate voltage stress in this

4 study. A gate voltage stress corresponding to an oxide field of  $-8 \text{ MVcm}^{-1}$  was applied for

5 up to 5000 s at either room temperature (RT) or 300°C, and gate characteristics (Hall effect

6 characteristics) were repeatedly measured for the MOSFETs (MOS Hall bars). The source

7 and drain contacts were floating, and the body contact was grounded when the stress voltage

8 was applied. The voltage sweep direction was negative to positive (positive to negative) with

9 a sweep rate of approximately  $1.0 \text{ Vs}^{-1}$  ( $0.14 \text{ Vs}^{-1}$ ) when measuring the gate characteristics

10 (Hall effect characteristics). As shown in the schematic illustration of MOS Hall bars in Fig.

11 1(b), Hall voltage was measured using external voltage terminals. A magnetic field of 0.2 T

12 was applied perpendicularly to the  $\text{SiO}_2/\text{SiC}$  interface during the Hall effect measurements.

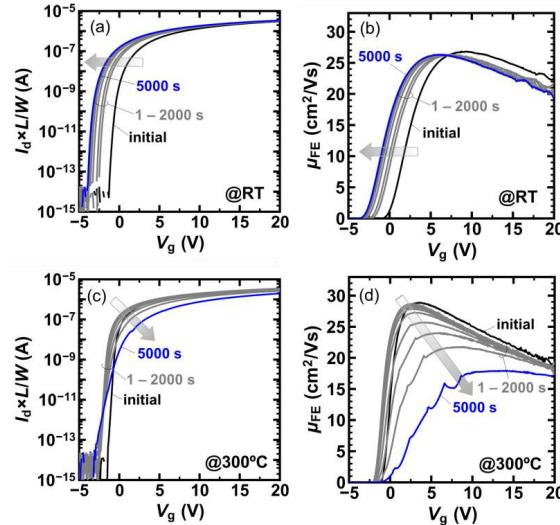

13 Figure 2 shows the variation of drain current ( $I_d$ ) and field-effect mobility ( $\mu_{\text{FE}}$ ) as a

14 function of gate voltage ( $V_g$ ) for the 120-min nitrided SiC MOSFET during the stress test

15 measurements. Both bias stress and measurements were performed at (a)(b) RT and (c)(d)

16 300°C.  $I_d$  was normalized by the channel length ( $L$ ) and channel width ( $W$ ), and the drain

17 voltage was set to 0.1 V. For RT stress, the  $I_d$ - $V_g$  characteristic drifted with the application of

18 stress (Fig. 2(a)). During the negative voltage stress, holes in the MOS channel are captured

19 into the near-interface oxide traps, resulting in a negative threshold voltage ( $V_{\text{th}}$ ) drift.

20 Although generation of interface hole traps is also a possible explanation of the negative  $V_{\text{th}}$

21 drift, the holes captured into interface traps would immediately recombine with electrons as

22 soon as electrons are induced in the MOS channel. As a hump due to electron-hole

23 recombination is not evident in the characteristic, it is likely that the holes are rather injected

24 into oxide traps where the recombination does not easily occur. The mobility characteristic

25 also experienced the drift, but its maximum value remained almost constant before and after

26 the stress (Fig. 2(b)). This indicates that the oxide traps have a limited impact on  $\mu_{\text{FE}}$ . As a

27 result of high-temperature stress at 300°C, degradation in the subthreshold characteristic was

28 observed in addition to the drift (Fig. 3(c)). This indicates an increase in the  $D_{\text{it}}$  values. In

29 addition, a strong decrease in the  $\mu_{\text{FE}}$  was observed (Fig. 2(d)). Thus, in contrast to oxide

30 traps, the stress-induced interface states seem to have a strong impact on the  $\mu_{\text{FE}}$ . Figure 3

31 summarizes the threshold voltage drift ( $\Delta V_{\text{th}}$ ), subthreshold swing (SS), and maximum  $\mu_{\text{FE}}$

32 ( $\mu_{\text{FE},\text{max}}$ ) of a 120-min nitrided SiC MOSFET as a function of stress time: (a) the relationship

33 between  $\Delta V_{\text{th}}$  and SS, and (b) that between  $\mu_{\text{FE},\text{max}}$  and SS. Here,  $V_{\text{th}}$  was determined as the

34 gate voltage where  $I_d \times L/W$  equals  $10^{-9} \text{ A}$ , and SS was evaluated within the drain current range

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

1 of  $10^{-11} \text{ A} < I_d \times L/W < 10^{-10} \text{ A}$ . Although  $V_{th}$  drifted negatively with applied RT stress, the SS

2 value hardly changed (Fig. 3(a)). Thus, the capture of holes into the oxide traps is irrelevant

3 to the generation of interface states. At 300°C stress,  $V_{th}$  slightly drifted negatively until 100

4 s, but then drifted positively. The positive drift of  $V_{th}$  is accompanied by an increase in SS

5 and thus caused by an increase in  $D_{it}$ . Although the mechanism of  $D_{it}$  increase remains

6 uncertain, high electric field and high temperature conditions likely lead to bond-breaking

7 reactions, thereby generating additional defects. The  $\mu_{FE,max}$  and SS were both unchanged by

8 RT stress (Fig. 3(b)). However, as a result of 300°C stress, the decrease in the  $\mu_{FE,max}$  occurred

9 in accordance with the increase in the SS. Thus, it is clear that the stress-induced interface

10 states strongly reduce the  $\mu_{FE}$ .

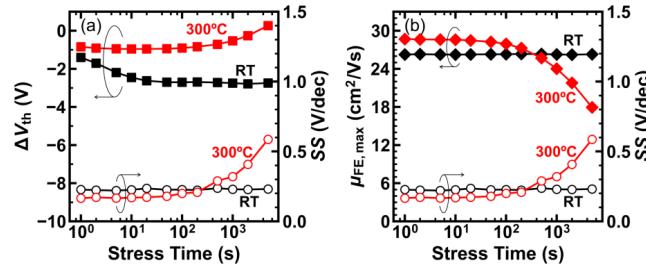

11 Figure 4 shows the energy distribution of  $D_{it}$  values of 10-min nitrided (NO10) and 120-

12 min nitrided (NO120) SiC MOS structures obtained from the SS values within the drain

13 current range of  $10^{-11} \text{ A} < I_d \times L/W < 10^{-7} \text{ A}$ . The detailed method of  $D_{it}$  evaluation is described

14 in Ref.<sup>35</sup>. The change in the  $D_{it}$  values when applying stress at 300°C is also shown for

15 sample NO120. The trap energy level (horizontal axis) was determined as the average Fermi

16 level that corresponds to the minimum and maximum drain current where the SS values were

17 evaluated. For example, when the SS value was obtained within the drain current range of

18  $10^{-11} \text{ A} < I_d \times L/W < 10^{-10} \text{ A}$ , the trap energy level equals the mean value of Fermi levels,

19 which gives  $I_d \times L/W$  of  $10^{-11} \text{ A}$  and  $10^{-10} \text{ A}$ . To calculate the Fermi level corresponding to a

20 given drain current, free electron mobility should be assumed. We assumed the free electron

21 mobilities of NO10 and NO120 to be  $70 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , and those of NO120 after 10, 1000, 2000,

22 3000, and 4000 s of stress to be 70, 60, 40, 20, and  $20 \text{ cm}^2 \text{V}^{-1} \text{s}^{-1}$ , respectively, referring to

23 the  $\mu_{Hall}$  at a low free electron density ( $n_{free} = 1 \times 10^{11} \text{ cm}^{-2}$ ). The gate voltage dependence of

24 free electron mobility was neglected for the sake of simplicity. As a result,  $D_{it}$  in the energy

25 range of approximately  $0.15 \text{ eV} < E_C - E_T < 0.30 \text{ eV}$  increased as the stress was applied to

26 sample NO120 (Fig. 4). Nevertheless, the  $D_{it}$  values were still lower compared with the

27 sample with insufficient nitridation (NO10).

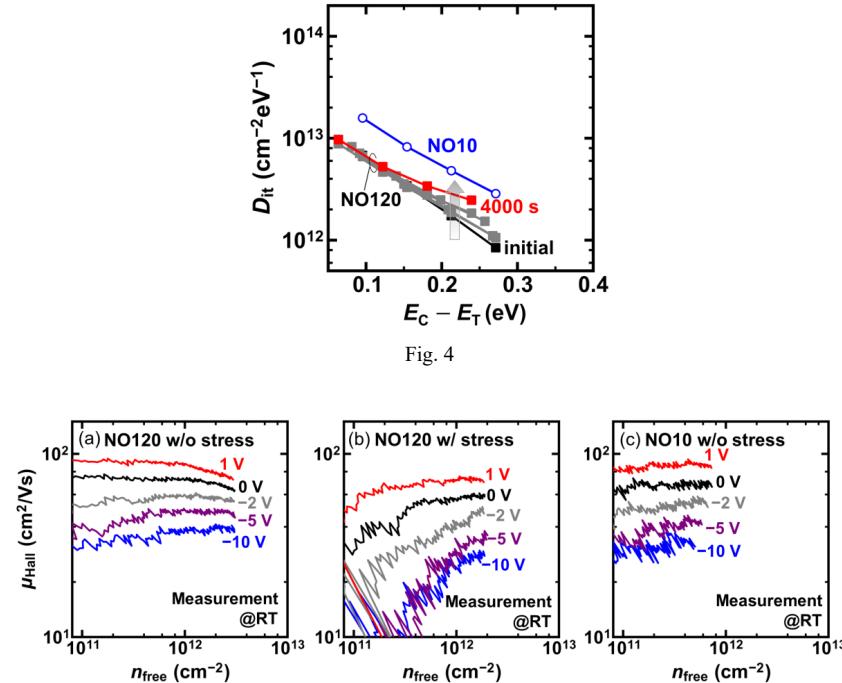

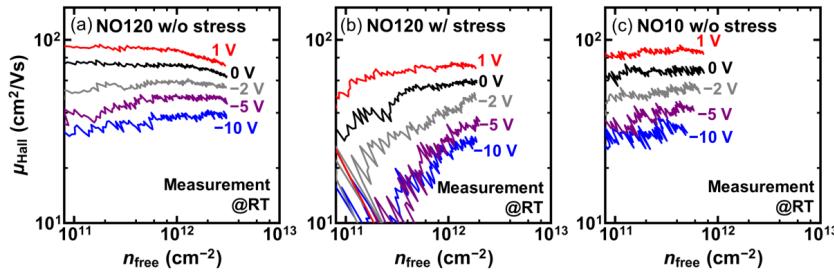

28 We then examined the  $\mu_{Hall}$  of the samples as shown in Fig. 5: (a) NO120 before applying

29 stress (NO120 w/o stress), (b) NO120 after applying 4000-s stress at 300°C (NO120 w/

30 stress), and (c) NO10 without stress. Unlike the  $\mu_{FE}$  which is affected by both the density and

31 mobility of free electrons by its definition,  $\mu_{Hall}$  represents the actual free electron mobility

32 and thus is useful for discussing the carrier scattering mechanisms. A body bias was applied

33 to control the surface electric field ( $E_s$ ) of SiC, and the measurements were performed at RT.

34 When comparing the results without the application of the body bias (0 V), the samples

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

1 NO120 w/o stress (Fig. 5(a)) and NO10 w/o stress (Fig. 5(c)) showed similar  $\mu_{\text{Hall}}$ , while the

2 sample NO120 w/ stress showed significantly lower  $\mu_{\text{Hall}}$  especially at lower  $n_{\text{free}}$ . With the

3 application of the body bias, this difference is even more pronounced. The sample NO120

4 w/ stress exhibited a strong decrease in the  $\mu_{\text{Hall}}$  when applying a negative body bias. Since

5 a negative body bias increases the surface electric field of SiC, free electrons become more

6 strongly confined to the MOS channel, leading to enhanced carrier scattering, in particular

7 for the sample NO120 w/ stress. Focusing on the  $n_{\text{free}}$  dependence of  $\mu_{\text{Hall}}$ ,  $\mu_{\text{Hall}}$  increases with

8 the  $n_{\text{free}}$  in the sample NO120 w/ stress. This is a clear signature of Coulomb scattering, where

9 electron shielding results in increased mobility as the  $n_{\text{free}}$  increases<sup>36)</sup>. However, the  $D_{\text{it}}$

10 values are still lower in the sample NO120 w/ stress than in the sample NO10 (Fig. 4). Thus,

11 the high  $D_{\text{it}}$  does not necessarily lead to a decrease in the  $\mu_{\text{Hall}}$ .

12 To discuss the cause of the  $\mu_{\text{Hall}}$  decrease observed in the sample NO120 w/ stress, we

13 further analyzed the Hall mobility data, considering the spatial distribution of free electrons

14 in the MOS channel. The free electron wave function in the first subband of the inversion

15 layer,  $\zeta_0(z)$  under the triangular potential approximation is given by<sup>37)</sup>

$$16 \quad \zeta_0(z) = \text{Ai} \left[ \left( \frac{2m_z q E_s}{\hbar^2} \right)^{\frac{1}{3}} \left( z - \frac{E_0}{q E_s} \right) \right], \quad (1)$$

17 where Ai represents the Airy function.  $z$ ,  $m_z$ ,  $\hbar$ , and  $E_0$  are the depth in SiC measured from

18 the SiO<sub>2</sub>/SiC interface, the electron effective mass in SiC perpendicular to the interface,

19 Dirac's constant, and the energy level of first subband, respectively. Then, the averaged

20 distance of electrons from the interface,  $z_{\text{AV}}$  can be estimated by<sup>37)</sup>

$$21 \quad z_{\text{AV}} = \frac{\int z \zeta_0^2 dz}{\int \zeta_0^2 dz}. \quad (2)$$

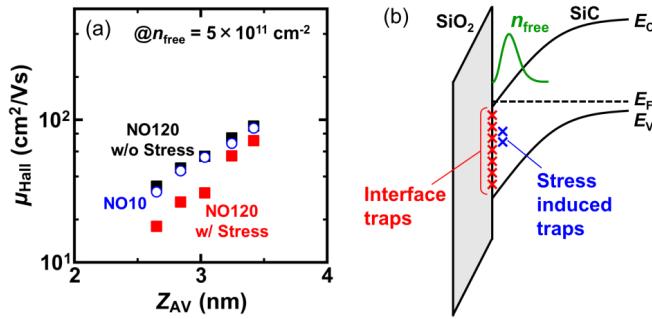

22 Figure 6(a) plots the  $\mu_{\text{Hall}}$  at a low free electron density ( $n_{\text{free}} = 5 \times 10^{11} \text{ cm}^{-2}$ ) as a function of

23  $z_{\text{AV}}$ .  $z_{\text{AV}}$  was changed by applying body bias for each sample. As a result, while  $\mu_{\text{Hall}}$  took

24 similar values for the samples NO120 w/o stress and NO10 at a given  $z_{\text{AV}}$ , the sample NO

25 120 w/ stress showed lower  $\mu_{\text{Hall}}$ . When shifting the data points of NO120 w/o stress and

26 NO10 towards larger  $z_{\text{AV}}$  by a few angstroms, it seems that they match well with those of

27 NO120 w/ stress. This suggests that the stress-induced  $D_{\text{it}}$  is located slightly deep inside the

28 SiC and thus behaves as a strong Coulomb scattering source, as shown in Fig. 6(b). In the

29 present case, the origin of  $D_{\text{it}}$  at the SiC side is presumably nitrogen-related defects that are

30 activated by the gate voltage stress. As a result, we pointed out that, while of relatively low

31 trap density,  $D_{\text{it}}$  located on the SiC side of the interface can behave as a strong source of

32 Coulomb scattering.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

1      In conclusion, we investigated the impact of gate stress on the on-state characteristics of

2      nitrided SiC MOSFETs. We found that, while hole trapping into the oxide has a limited

3      impact on field-effect mobility, the stress-induced  $D_{it}$  severely degrades the mobility.

4      Through MOS Hall effect measurements, it is highly likely that the mobility of MOSFETs

5      subjected to high-temperature stress is limited by Coulomb scattering. We proposed that  $D_{it}$

6      on the SiC side of the interface, although of comparably low density, can behave as a strong

7      source of Coulomb scattering.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

### Acknowledgments

This work was partly supported by MEXT-Program for Creation of Innovative Core Technology for Power Electronics (Grant No. JPJ009777) and JSPS KAKENHI (Grant No. 24H00046).

### AUTHOR DECLARATIONS

#### Conflict of Interest

The authors have no conflicts to disclose.

### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

## References

- 1) T. Kimoto and J. A. Cooper, *Fundamentals of Silicon Carbide Technology* (Wiley, Singapore, 2014).

- 2) T. Kimoto and H. Watanabe, *Appl. Phys. Express* **13**, 120101 (2020).

- 3) T. Hatakeyama, Y. Kiuchi, M. Sometani, S. Harada, D. Okamoto, H. Yano, Y. Yonezawa and H. Okumura, *Appl. Phys. Express* **10**, 046601 (2017).

- 4) H. Yoshioka, J. Senzaki, A. Shimozato, Y. Tanaka and H. Okumura, *AIP Adv.* **5**, 017109 (2015).

- 5) T. Kobayashi, S. Nakazawa, T. Okuda, J. Suda and T. Kimoto, *Appl. Phys. Lett.* **108**, 152108 (2016).

- 6) V. V. Afanas'ev, F. Ciobanu, S. Dimitrijev, G. Pensl and A. Stesmans, *J. Phys. Condens. Matter* **16**, S1839 (2004).

- 7) T. Umeda, G. W. Kim, T. Okuda, M. Sometani, T. Kimoto and S. Harada, *Appl. Phys. Lett.* **113**, 061605 (2018).

- 8) T. Kobayashi and T. Kimoto, *Appl. Phys. Lett.* **111**, 062101 (2017).

- 9) J. M. Knaup, P. Deák, T. Frauenheim, A. Gali, Z. Hajnal and W. J. Choyke, *Phys. Rev. B - Condens. Matter Mater. Phys.* **72**, 115323 (2005).

- 10) P. Deák, J. M. Knaup, T. Hornos, C. Thill, A. Gali and T. Frauenheim, *J. Phys. D. Appl. Phys.* **40**, 6242 (2007).

- 11) F. Devynck, A. Alkauskas, P. Broqvist and A. Pasquarello, *Phys. Rev. B - Condens. Matter Mater. Phys.* **84**, 235320 (2011).

- 12) T. Kobayashi and Y. I. Matsushita, *J. Appl. Phys.* **126**, 145302 (2019).

- 13) H. F. Li, S. Dimitrijev, H. B. Harrison and D. Sweatman, *Appl. Phys. Lett.* **70**, 2028 (1997).

- 14) G. Y. Chung, C. C. Tin, J. R. Williams, K. McDonald, R. K. Chanana, R. A. Weller, S. T. Pantelides, L. C. Feldman, O. W. Holland, M. K. Das and J. W. Palmour, *IEEE Electron Device Lett.* **22**, 176 (2001).

- 15) K. Moges, M. Sometani, T. Hosoi, T. Shimura, S. Harada and H. Watanabe, *Appl. Phys. Express* **11**, 101303 (2018).

- 16) T. Nakanuma, T. Kobayashi, T. Hosoi, M. Sometani, M. Okamoto, A. Yoshigoe, T. Shimura and H. Watanabe, *Appl. Phys. Express* **15**, 041002 (2022).

- 17) T. Nakanuma, A. Suzuki, Y. Iwakata, T. Kobayashi, M. Sometani, M. Okamoto, T. Hosoi, T. Shimura and H. Watanabe, 2022 IEEE Int. Reliab. Phys. Symp. 3B.2 (2022).

- 18) M. Sometani, T. Hosoi, H. Hirai, T. Hatakeyama, S. Harada, H. Yano, T. Shimura, H.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

Watanabe, Y. Yonezawa and H. Okumura, *Appl. Phys. Lett.* **115**, 132102 (2019).

- 19) H. Yoshioka, T. Nakamura and T. Kimoto, *J. Appl. Phys.* **112**, 024520 (2012).

- 20) S. Nakazawa, T. Okuda, J. Suda, T. Nakamura and T. Kimoto, *IEEE Trans. Electron Devices* **62**, 309 (2015).

- 21) A. Chanthaphan, T. Hosoi, T. Shimura and H. Watanabe, *AIP Adv.* **5**, 097134 (2015).

- 22) T. Kobayashi, A. Suzuki, T. Nakanuma and M. Sometani, *Mater. Sci. Semicond. Process.* **175**, 108251 (2024).

- 23) V. Tilak, K. Matocha, G. Dunne, F. Allerstam and E. Ö. Sveinbjornsson, *IEEE Trans. Electron Devices* **56**, 162 (2009).

- 24) S. Dhar, S. Haney, L. Cheng, S. R. Ryu, A. K. Agarwal, L. C. Yu and K. P. Cheung, *J. Appl. Phys.* **108**, 054509 (2010).

- 25) M. Noguchi, T. Iwamatsu, H. Amishiro, H. Watanabe, K. Kita and N. Miura, *Jpn. J. Appl. Phys.* **59**, 051006 (2020).

- 26) K. Ito, H. Tanaka, M. Horita, J. Suda and T. Kimoto, *Appl. Phys. Express* **17**, 081003 (2024).

- 27) H. Tanaka and N. Mori, *Jpn. J. Appl. Phys.* **59**, 031006 (2020).

- 28) T. Hatakeyama, H. Hirai, M. Sometani, D. Okamoto, M. Okamoto and S. Harada, *J. Appl. Phys.* **131**, 145701 (2022).

- 29) K. Puschkarsky, T. Grasser, T. Aichinger, W. Gustin and H. Reisinger, *IEEE Trans. Electron Devices* **66**, 4604 (2019).

- 30) H. Yano, N. Kanafuji, A. Osawa, T. Hatayama and T. Fuyuki, *IEEE Trans. Electron Devices* **62**, 324 (2015).

- 31) M. Sometani, M. Okamoto, T. Hatakeyama, Y. Iwahashi, M. Hayashi, D. Okamoto, H. Yano, S. Harada, Y. Yonezawa and H. Okumura, *Jpn. J. Appl. Phys.* **57**, 04FA07 (2018).

- 32) L. C. Yu, G. T. Dunne, K. S. Matocha, K. P. Cheung, J. S. Suehle and K. Sheng, *IEEE Trans. Device Mater. Reliab.* **10**, 418 (2010).

- 33) C. H. and R. W. B. Mong-Song Liang, Chi Chang, Yew Tong Yeow, *IEEE Trans. Electron Devices* **31**, 1238 (1984).

- 34) S. Shabde, A. Bhattacharyya, R. S. Kao and R. S. Muller, *Solid State Electron.* **31**, 1603 (1988).

- 35) H. Yoshioka, J. Senzaki, A. Shimozato, Y. Tanaka and H. Okumura, *Appl. Phys. Lett.* **104**, 083516 (2014).

- 36) S. Takagi, A. Toriumi, M. Iwase and H. Tango, *IEEE Trans. Electron Devices* **41**,

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: [10.1063/5.0245907](https://doi.org/10.1063/5.0245907)

2357 (1994).

37) F. Stern, Phys. Rev. B **5**, 4891 (1972).

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

## Figures

Fig. 1. (a) Process flow of gate stack formation in this study. (b) Schematic of MOS Hall bar structures.

Fig. 2. Drain current and field-effect mobility as a function of gate voltage for the 120-min nitrided SiC MOSFET during stress test measurements: negative bias stress and measurement were performed at (a)(b) RT and (c)(d) 300°C.

Fig. 3. Threshold voltage drift, subthreshold swing, and maximum field-effect mobility of the 120-min nitrided SiC MOSFET as a function of stress time: (a) the relationship between threshold voltage drift and subthreshold swing, and (b) that between maximum field-effect mobility and subthreshold swing.

Fig. 4. Energy distribution of interface state density for the 10-min nitrided (NO10) and 120-min nitrided (NO120) SiC MOS structures obtained from the subthreshold swing.

Fig. 5. Hall mobility of SiC MOS devices: (a) NO120 before applying stress, (b) NO120 after 4000-s stress at 300°C, and (c) NO10 without stress.

Fig. 6. (a) Hall mobility of SiC MOS devices at a low free electron density ( $n_{\text{free}} = 5 \times 10^{11} \text{ cm}^{-2}$ ) as a function of the average distance of free electrons from the  $\text{SiO}_2/\text{SiC}$  interface. (b) Schematic describing a model where stress-induced interface states are located on the SiC side of the interface, behaving as a strong source of Coulomb scattering.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

Fig. 1

Fig. 2

Fig. 3

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245907

Fig. 4

Fig. 5

Fig. 6