| Title        | Formation of high-quality $SiO_2/\beta$ -Ga <sub>2</sub> O <sub>3</sub> (001) MOS structures: The role of post-deposition annealing                                                                                                                                              |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Author(s)    | Kobayashi, Takuma; Maeda, Kensei; Hara, Masahiro<br>et al.                                                                                                                                                                                                                       |

| Citation     | Applied Physics Letters. 2025, 126(1), p. 012108                                                                                                                                                                                                                                 |

| Version Type | АМ                                                                                                                                                                                                                                                                               |

| URL          | https://hdl.handle.net/11094/99315                                                                                                                                                                                                                                               |

| rights       | This article may be downloaded for personal use<br>only. Any other use requires prior permission of<br>the author and AIP Publishing. This article<br>appeared in Appl. Phys. Lett. 6 January 2025;<br>126 (1): 012108 and may be found at<br>https://doi.org/10.1063/5.0245289. |

| Note         |                                                                                                                                                                                                                                                                                  |

The University of Osaka Institutional Knowledge Archive : OUKA

https://ir.library.osaka-u.ac.jp/

The University of Osaka

## Formation of high-quality SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>(001) MOS structures: the role of post-deposition annealing

Takuma Kobayashi\*, Kensei Maeda, Masahiro Hara, Mikito Nozaki, and Heiji Watanabe Graduate School of Engineering, Osaka University, Suita Osaka 565-0871, Japan E-mail: kobayashi@prec.eng.osaka-u.ac.jp

We investigated the effect of post-deposition annealing on the electrical characteristics of SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>(001) MOS structures. While oxygen annealing effectively improves the interface properties, it induces acceptor defects in Ga<sub>2</sub>O<sub>3</sub>, leading to a decrease in net donor density. With the combination of oxygen and nitrogen annealing, carrier compensation was suppressed, and a low interface state density of about  $1 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> was obtained near the conduction band edge of Ga<sub>2</sub>O<sub>3</sub>. High immunity against positive gate bias stress was also confirmed.

1

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

1

$\frac{2}{3}$

4

$\mathbf{5}$

6

7

8

9

10 11

12

13

14

15

16 17

18

19

20

21

22 23

24

25

26

27

Gallium oxide (Ga<sub>2</sub>O<sub>3</sub>) is an ultra-wide bandgap semiconductor that shows promise for next-generation power electronics and solar-blind deep ultraviolet photodetectors<sup>1)-5)</sup>. Among the confirmed polytypes ( $\alpha$ ,  $\beta$ ,  $\gamma$ ,  $\delta$ ,  $\epsilon$ ), the monoclinic  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> is the most stable, with a large bandgap energy of 4.9 eV. The major advantage of Ga<sub>2</sub>O<sub>3</sub> over other wide bandgap semiconductors is the availability of the melt growth process, which can produce large, uniform substrates at a lower cost compared with vapor growth techniques. Ga2O3 metal-oxide-semiconductor field-effect transistors (MOSFETs) are attractive for power switching applications. Typically, n-channel power MOSFETs (e.g., DMOSFETs<sup>6</sup>) have a *p*-type body layer, whose surface is inverted to *n*-type by the application of a gate voltage in the on-state of the devices. In the off-state, the depletion layer vertically extends from the p*n* junction to a thick *n*-type drift layer to withstand high voltage. However, obtaining *p*-type conductivity in Ga<sub>2</sub>O<sub>3</sub> is challenging due to the presence of self-trapping holes (hole polarons)<sup>7)-9)</sup>, the high effective mass of holes<sup>10),11)</sup>, and a high abundance of Ga interstitials under p-type conditions<sup>12)-14)</sup>. Despite the lack of p-type doping, various power devices, including depletion-mode<sup>15),16)</sup> and enhancement-mode MOSFETs<sup>17),18)</sup>, MOS junction FETs<sup>19</sup>, and superjunction-equivalent MOSFETs<sup>20</sup>, have been demonstrated for Ga<sub>2</sub>O<sub>3</sub>. The choice of dielectrics is particularly important for achieving high performance, stability, and reliability of MOS devices. Aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) is the best-studied dielectric for Ga<sub>2</sub>O<sub>3</sub><sup>21)-26</sup>, but it suffers from small band offsets (1.5–1.6 eV for the conduction band and 0.7 eV for the valence band<sup>27)</sup>) and Ga diffusion into the dielectric during thermal annealing<sup>22)</sup>. Given the wide bandgap of Ga<sub>2</sub>O<sub>3</sub>, silicon dioxide (SiO<sub>2</sub>) would be a better dielectric to ensure sufficiently large band offsets<sup>28</sup>. SiO<sub>2</sub> also has advantages in terms of its high thermal stability. In addition to the deposition process of dielectrics, a key factor in optimizing MOS structures is post-deposition annealing (PDA). Although there are few reports on the improvement of SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub> MOS structures by PDA<sup>29),30)</sup>, the practical role of PDA has not been well studied. To establish a method for obtaining a high-quality interface between SiO2 and Ga2O3, the role of PDA should be further investigated. In the present study, we extensively studied the effect of oxygen (O<sub>2</sub>) and nitrogen (N<sub>2</sub>)

In the present study, we extensively studied the effect of oxygen (O<sub>2</sub>) and nitrogen (N<sub>2</sub>) PDA on the electrical characteristics of SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>(001) MOS structures. We investigated the dependence on annealing temperature and examined the effectiveness of a two-step annealing treatment (i.e., O<sub>2</sub> annealing followed by N<sub>2</sub> annealing) on the device characteristics. In particular, we focused on the impact of PDA on the interface properties, bulk carrier density, and reliability of the MOS structures. We aim to develop a strategy for forming a high-quality SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub> MOS structure.

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

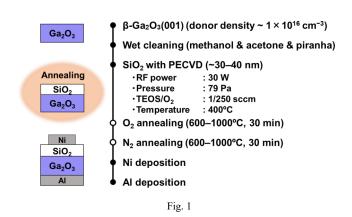

1 Figure 1 illustrates the fabrication process flow of  $Ga_2O_3MOS$  capacitors.  $\beta$ - $Ga_2O_3(001)$ epilayers with a donor density of approximately 1×10<sup>16</sup> cm<sup>-3</sup> were used in this study. After 2 3 wet cleaning the samples with methanol, acetone, and piranha solution, SiO<sub>2</sub> films were 4 deposited using plasma-enhanced chemical vapor deposition (PECVD). Under a  $\mathbf{5}$ radiofrequency (RF) power of 30 W and pressure of 79 Pa, a gas mixture of tetraethyl 6 orthosilicate (TEOS) and O2 was introduced into the PECVD chamber, and SiO2 was 7 deposited at a substrate temperature of 400°C. The samples were then subjected to  $O_2$  or  $N_2$ 8 annealing at 600-1000°C for 30 min, or a combination of these annealing conditions. Finally, nickel (Ni) gate electrodes and aluminum (Al) back contacts were formed by vacuum 9 10 evaporation to fabricate the MOS structures. Table I summarizes the names and capacitance 11 equivalent SiO<sub>2</sub> thickness of Ga<sub>2</sub>O<sub>3</sub> MOS structures prepared in this study. In addition, a reference Schottky barrier diode without a SiO2 film was also prepared to investigate the 12bulk properties of Ga<sub>2</sub>O<sub>3</sub>. All electrical measurements were conducted at room temperature. 13

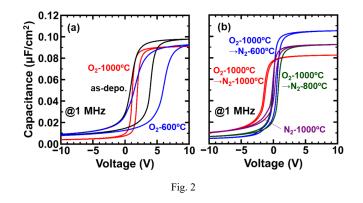

Figure 2 shows the bidirectional capacitance-voltage (C-V) characteristics of Ga<sub>2</sub>O<sub>3</sub> MOS 14capacitors measured at a probe frequency of 1 MHz: (a) samples with and without  $O_2$ 15annealing and (b) those with N2 annealing or combined O2 and N2 annealing. As shown in 16Fig. 2(a), the as-deposited sample exhibited a large C-V hysteresis due to a high number of 1718 interface traps. While O<sub>2</sub> annealing at 600°C resulted in an even degraded characteristic 19indicating trap formation at the interface, the situation was improved after annealing at 201000°C. Although high-temperature O2 annealing was effective in reducing the traps, a 21relatively large hysteresis remained even after annealing at 1000°C. With additional N<sub>2</sub> 22annealing, the situation improved significantly (Fig. 2(b)). In particular, after O2 and N2 23annealing at 1000°C, a steep C-V characteristic with minimal hysteresis was obtained. On 24the contrary, the sample with N2 annealing at 1000°C alone resulted in a limited 25improvement. These results suggest that the combination of O<sub>2</sub> and N<sub>2</sub> annealing is effective in reducing interface traps in SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub> MOS structures. A slight negative shift in the C-V 2627characteristic was confirmed, which is likely due to the presence of positive fixed charges at the interface. Since the maximum capacitance varies among the samples without a clear 2829trend with respect to the PDA conditions, the variation is mainly attributed to the differences 30 in the deposited SiO<sub>2</sub> thickness (Table I). In addition to the maximum capacitance, we found 31 that the minimum capacitance also depends on the sample conditions (Figs. 2(a) and (b)). 32 This indicates that PDA affects the donor concentration in bulk Ga<sub>2</sub>O<sub>3</sub>.

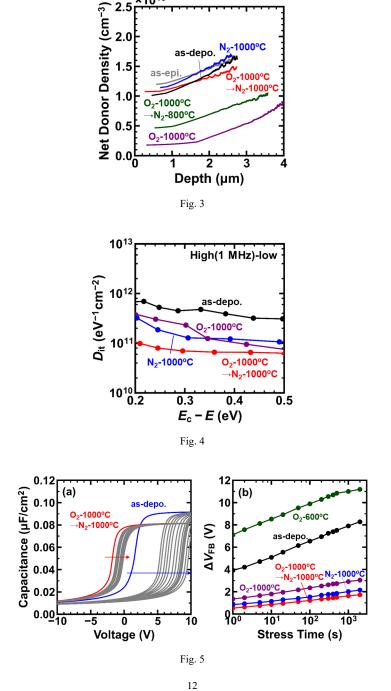

We then evaluated the net donor density from the  $1/C^2$ -V characteristics of Ga<sub>2</sub>O<sub>3</sub> MOS capacitors in the deep-depletion range. The donor density as a function of depth from the

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

21

1 SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub> interface is shown in Fig. 3. Initially, the as-deposited sample showed a doping 2 profile identical to that of a Schottky diode formed directly on the epilayer surface (as-epi.). 3 This indicates that SiO<sub>2</sub> formation by PECVD has a limited impact on donor density. This is 4 likely due to the low-temperature deposition, which should be favorable in suppressing  $\mathbf{5}$ unwanted defect formation in bulk Ga<sub>2</sub>O<sub>3</sub> due to the thermal budget. The slight increase in 6 density observed in deeper Ga2O3 is likely due to imperfect doping control during the epitaxy 7 process. After O2 annealing at 1000°C, an order-of-magnitude decrease in donor density was observed. Since oxygen interstitials act as deep acceptors in Ga<sub>2</sub>O<sub>3</sub><sup>12)-14)</sup>, this suggests that 8 oxygen diffuses into the Ga2O3 during O2 annealing, leading to a reduction in donor density 9 10 via the carrier compensation effect. The formation of oxygen interstitials is preferred in Ga<sub>2</sub>O<sub>3</sub> because they have quite low formation energies especially under oxygen-rich and *n*-11 type conditions<sup>12)-14)</sup>. However, the diffusion barrier of oxygen atoms in the [100] direction 12in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub> has been experimentally determined to be as high as (3.2 ± 0.4) eV<sup>31</sup>. Thus, a 13crystal orientation dependent or a defect mediated diffusion process is responsible for 14explaining the oxygen diffusion on the um scale. Another possibility is the formation of 15gallium vacancies during  $O_2$  annealing, which also act as deep acceptors in  $Ga_2O_3^{12)-14}$ . The 16formation of gallium vacancies is favored under an oxygen-rich condition because it 17corresponds to a gallium-poor condition<sup>12)-14)</sup>. In fact, their formation during O<sub>2</sub> annealing 18 is experimentally discussed as the cause of the resistivity increase observed in  $\beta$ -Ga<sub>2</sub>O<sub>3</sub><sup>32)</sup>. 1920Although further studies are needed to clarify the origin of the deep acceptors, a clear recovery of donor density towards its initial values was observed with additional N2 22annealing (Fig. 3). With N2 annealing at 1000°C after O2 annealing, the doping profile of the as-deposited sample was reproduced. Note that the differences in the profiles of as-epi., as-2324depo., N<sub>2</sub>-1000°C, and O<sub>2</sub>-1000°C $\rightarrow$ N<sub>2</sub>-1000°C samples are small and well within the experimental variation. In bulk Ga<sub>2</sub>O<sub>3</sub>, it has also been reported that O<sub>2</sub> annealing reduces 25donor density, while N<sub>2</sub> annealing is effective in suppressing carrier compensation<sup>33)</sup>. Thus, 2627additional N2 annealing appears to reduce the deep acceptors in Ga2O3. Overall, the combination of O2 and N2 annealing not only improves interface properties (Fig. 2(b)) but 2829also suppresses unwanted carrier compensation caused by acceptor-type defects (Fig. 3). To further assess the interface properties, we evaluated the interface state density  $(D_{it})$

30 31 using the high (1 MHz)-low method. Note that the Dit distribution is evaluated by taking into 32 account the SiO<sub>2</sub> thickness of each sample and the results are not affected by the variation in 33 the thickness. Figure 4 shows the energy distribution of Dit for Ga<sub>2</sub>O<sub>3</sub> MOS capacitors. To 34determine the trap energy level  $(E_c - E)$ , the donor density value is needed. Since the donor

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

21

24

1 density varies with depth for the samples in this study (Fig. 3), we assumed the donor density 2 at depth of approximately 0.5 µm from the interface for each sample. As shown in Fig. 4, the 3 as-deposited sample exhibited a relatively high  $D_{\rm it}$  of about  $7 \times 10^{11}$  cm<sup>-2</sup>eV<sup>-1</sup> at  $E_{\rm c} - E = 0.2$ eV. However, Dit was reduced to about (3-4)×10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup> after either O<sub>2</sub> or N<sub>2</sub> annealing  $\mathbf{4}$ at 1000°C. The combination of O2 and N2 annealing resulted in further improvement of Dit  $\mathbf{5}$  $(\sim 1 \times 10^{11} \text{ cm}^{-2} \text{eV}^{-1})$ . This result aligns well with the C-V measurements (Fig. 2), indicating 6 7 the effectiveness of combined O2 and N2 annealing in improving interface properties.

8 Finally, we investigated the reliability of the MOS structures in response to charge 9 injection into the SiO2 film. Specifically, a constant gate voltage stress corresponding to an 10 oxide field of  $+ 4 \text{ MV cm}^{-1}$  was applied to the MOS structures for up to 2000 s, and C-V 11 characteristics were repeatedly measured to monitor any changes. Here, the stress field was determined for each sample from the over drive voltage, i.e.,  $(V_G - V_{FB})/t_{OX}$ , where  $V_G$ ,  $V_{FB}$ , 12and tox are the gate voltage, the flatband voltage, and the SiO2 thickness, respectively. Figure 135(a) shows the measurement results for typical samples. While the as-deposited sample 14exhibited significant drift in the characteristics under stress, the sample with combined  $O_2$ 15and N<sub>2</sub> annealing showed substantially less drift. The flatband voltage drift ( $\Delta V_{\text{FB}}$ ) as a 1617function of stress time was quantified for the fabricated samples, as summarized in Fig. 5(b). 18 The as-deposited sample exhibited a large  $\Delta V_{\rm FB}$  of about 8 V after 2000 s of stress. O<sub>2</sub> 19annealing at 600°C resulted in an even larger drift (~11 V), indicating that low-temperature 20oxidation induces near-interface traps. When the annealing temperature was increased to 1000°C, a much smaller drift (~3 V) was observed, likely due to trap passivation. The sample 22with combined O2 and N2 annealing exhibited a drift of less than 2 V. Thus, the combination 23of O2 and N2 annealing effectively improves reliability. Since the reliability is also improved by N2 annealing alone, thermal effects are likely responsible for the improved reliability.

25In conclusion, we investigated the impact of PDA on the electrical characteristics of SiO<sub>2</sub>/β-Ga<sub>2</sub>O<sub>3</sub>(001) MOS structures. While O<sub>2</sub> annealing was effective in improving the C-2627V characteristics to some extent, we found that it leads to a decrease in net donor density in Ga<sub>2</sub>O<sub>3</sub>, indicating the formation of deep acceptor defects, likely due to oxygen interstitials 2829or gallium vacancies. However, by performing N2 annealing in addition to O2 annealing, the 30 donor density recovered to its initial values observed after the epitaxial growth of Ga<sub>2</sub>O<sub>3</sub>. 31 The combination of O<sub>2</sub> and N<sub>2</sub> annealing resulted in a very low D<sub>it</sub> of approximately 1×10<sup>11</sup> 32 cm<sup>-2</sup>eV<sup>-1</sup> near the conduction band edge ( $E_c - E = 0.2 \text{ eV}$ ) of Ga<sub>2</sub>O<sub>3</sub>, while a slight negative 33 shift in the C-V characteristics due to positive fixed charges was observed after the 34 improvement. On the contrary, O2 or N2 annealing alone resulted in limited improvement in

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

- 1 the  $D_{it}$  (about (3-4)×10<sup>11</sup> cm<sup>-2</sup>eV<sup>-1</sup>). Gate bias stress measurements also confirmed high

- 2 immunity against positive gate bias for the sample with combined O2 and N2 annealing.

- $3\quad$  Since high immunity was also achieved by  $N_2$  annealing alone, the improved reliability is

- 4 mostly due to thermal effects. After all, the two-step annealing treatment is effective in

- 5 reducing the  $D_{it}$  values and improving the reliability of SiO<sub>2</sub>/ $\beta$ -Ga<sub>2</sub>O<sub>3</sub>(001) MOS structures.

6

### Acknowledgments

$\beta$ -Ga<sub>2</sub>O<sub>3</sub> epilayers used in this study were provided by Novel Crystal Technology, Inc.

### AUTHOR DECLARATIONS

Conflict of Interest

The authors have no conflicts to disclose.

### DATA AVAILABILITY

The data that support the findings of this study are available from the corresponding author upon reasonable request.

7

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

### References

- 1) M. Higashiwaki, K. Sasaki, A. Kuramata, T. Masui and S. Yamakoshi, Phys. Status Solidi A 211, 21 (2014).

- 2) M. Baldini, Z. Galazka and G. Wagner, Mater. Sci. Semicond. Process. 78, 132 (2018).

- 3) E. Ahmadi and Y. Oshima, J. Appl. Phys. 126, 160901 (2019).

- S. J. Pearton, J. Yang, P. H. Cary, F. Ren, J. Kim, M. J. Tadjer and M. A. Mastro, 4) Appl. Phys. Rev. 5, 011301 (2018).

- J. Zhang, J. Shi, D. C. Qi, L. Chen and K. H. L. Zhang, APL Mater. 8, 020906 (2020). 5)

- B. J. Baliga, IEEE Trans. Electron Devices 38, 1568 (1991). 6)

- 7) T. Gake, Y. Kumagai and F. Oba, Phys. Rev. Mater. 3, 044603 (2019).

- 8) S. Marcinkevičius and J. S. Speck, Appl. Phys. Lett. 116, 132101 (2020).

- 9) B. E. Kananen, N. C. Giles, L. E. Halliburton, G. K. Foundos, K. B. Chang and K. T. Stevens, J. Appl. Phys. 122, 215703 (2017).

- M. Mohamed, C. Janowitz, I. Unger, R. Manzke, Z. Galazka, R. Uecker, R. Fornari, 10)J. R. Weber, J. B. Varley and C. G. Van De Walle, Appl. Phys. Lett. 97, 211903 (2010).

- A. Mock, R. Korlacki, C. Briley, V. Darakchieva, B. Monemar, Y. Kumagai, K. Goto, 11) M. Higashiwaki and M. Schubert, Phys. Rev. B 96, 245205 (2017).

- T. Kobayashi, T. Gake, Y. Kumagai, F. Oba and Y.-I. Matsushita, Appl. Phys. 12) Express 12, 091001 (2019).

- 13) T. Zacherle, P. C. Schmidt and M. Martin, Phys. Rev. B - Condens. Matter Mater. Phys. 87, 235206 (2013).

- 14) H. Peelaers, J. L. Lyons, J. B. Varley and C. G. Van De Walle, APL Mater. 7, 022519 (2019).

- M. Higashiwaki, K. Sasaki, T. Kamimura, M. Hoi Wong, D. Krishnamurthy, A. 15) Kuramata, T. Masui and S. Yamakoshi, Appl. Phys. Lett. 103, 123511 (2013).

- 16) K. Sasaki, Q. T. Thieu, D. Wakimoto, Y. Koishikawa, A. Kuramata and S. Yamakoshi, Appl. Phys. Express 10, 124201 (2017).

- 17) K. D. Chabak, J. P. McCandless, N. A. Moser, A. J. Green, K. Mahalingam, A. Crespo, N. Hendricks, B. M. Howe, S. E. Tetlak, K. Leedy, R. C. Fitch, D. Wakimoto, K. Sasaki, A. Kuramata and G. H. Jessen, IEEE Electron Device Lett. 39, 67 (2018).

- 18) M. H. Wong, Y. Nakata, A. Kuramata, S. Yamakoshi and M. Higashiwaki, Appl. Phys. Express 10, 041101 (2017).

- C. Wang, Q. Yan, C. Su, S. Alghamdi, E. Ghandourah, Z. Liu, X. Feng, W. Zhang, 19)

8

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

ACCEPTED MANUSCRIPT

K. Dang, Y. Wang, J. Wang, J. Zhang, H. Zhou and Y. Hao, IEEE Electron Device Lett. 44, 380 (2023).

- Y. Wang, H. Gong, X. Jia, J. Ye, Y. Liu, H. Hu, X. Ou, X. Ma, R. Zhang, Y. Hao and G. Han, IEEE Trans. Electron Devices 69, 2203 (2022).

- 21) H. Zhou, S. Alghamdi, M. Si, G. Qiu and P. D. Ye, IEEE Electron Device Lett. 37, 1411 (2016).

- M. Hirose, T. Nabatame, K. Yuge, E. Maeda, A. Ohi, N. Ikeda, Y. Irokawa, H. Iwai, H. Yasufuku, S. Kawada, M. Takahashi, K. Ito, Y. Koide and H. Kiyono, Microelectron. Eng. 216, 111040 (2019).

- 23) M. Hirose, T. Nabatame, Y. Irokawa, E. Maeda, A. Ohi, N. Ikeda, L. Sang, Y. Koide and H. Kiyono, J. Vac. Sci. Technol. A Vacuum, Surfaces, Film. 39, 012401 (2021).

- 24) P. Fang, Z. Liao, D. Su, J. Liang, X. Wang and Y. Pei, Semicond. Sci. Technol. 39, 085003 (2024).

- 25) C. J. Klingshirn, A. Jayawardena, S. Dhar, R. P. Ramamurthy, D. Morisette, Z. Warecki, J. Cumings, T. Zheleva, A. Lelis and L. G. Salamanca-Riba, Micron 140, 102954 (2021).

- 26) B. Feng, T. He, G. He, X. Zhang, Y. Wu, X. Chen, Z. Li, X. Zhang, Z. Jia, G. Niu, Q. Guo, Z. Zeng and S. Ding, Appl. Phys. Lett. **118**, 181602 (2021).

- T. Kamimura, K. Sasaki, M. Hoi Wong, D. Krishnamurthy, A. Kuramata, T. Masui,

S. Yamakoshi and M. Higashiwaki, Appl. Phys. Lett. 104, 192104 (2014).

- A. Jayawardena, R. P. Ramamurthy, A. C. Ahyi, D. Morisette and S. Dhar, Appl. Phys. Lett. 112, 192108 (2018).

- 29) K. Kita, E. Suzuki and Q. Mao, ECS Meet. Abstr. 92, 59 (2019).

- Q. Zhang, D. Zhai, M. He and J. Lu, Mater. Sci. Semicond. Process. 184, 108777 (2024).

- 31) J. Uhlendorf, Z. Galazka and H. Schmidt, Appl. Phys. Lett. 119, 242106 (2021).

- 32) J. Jesenovec, M. H. Weber, C. Pansegrau, M. D. McCluskey, K. G. Lynn and J. S. McCloy, J. Appl. Phys. 129, 245701 (2021).

- A. Kuramata, K. Koshi, S. Watanabe, Y. Yamaoka, T. Masui and S. Yamakoshi, Jpn. J. Appl. Phys. 55, 1202A2 (2016).

9

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

ACCEPTED MANUSCRIPT **Applied Physics Letters**

Publishing

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

## PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

**Figures**

Table I. Names and SiO2 thickness of Ga2O3 MOS structures prepared in this study. The SiO2

Fig. 2. Bidirectional C-V characteristics of Ga<sub>2</sub>O<sub>3</sub> MOS capacitors measured at a frequency of 1 MHz: (a) samples with and without O<sub>2</sub> annealing, and (b) those with N<sub>2</sub> annealing or

Fig. 3. Net donor density in Ga<sub>2</sub>O<sub>3</sub> evaluated from the 1/C<sup>2</sup>-V characteristics of Ga<sub>2</sub>O<sub>3</sub> MOS

capacitors in the deep-depletion range as a function of depth from the  $SiO_2/Ga_2O_3$  interface. The result for the  $Ga_2O_3$  Schottky diode formed on the epilayer is also shown (as-epi).

Fig. 4. Energy distribution of Dit for SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub> MOS capacitors evaluated using the high

Fig. 5. (a) Change in the *C*-*V* characteristics of  $SiO_2/Ga_2O_3$  MOS capacitors under positive gate bias stress (Eox = +4 MVcm<sup>-1</sup>). The stress was applied for up to 2000 s. (b) Flatband

voltage drift ( $\Delta V_{FB}$ ) as a function of stress time for SiO<sub>2</sub>/Ga<sub>2</sub>O<sub>3</sub> MOS capacitors.

thickness was evaluated from the maximum capacitance of MOS capacitors.

Fig. 1. Fabrication process flow of Ga<sub>2</sub>O<sub>3</sub> MOS capacitors.

combined O2 and N2 annealing.

(1 MHz)-low method.

| Table I                                                                   |                                 |  |  |

|---------------------------------------------------------------------------|---------------------------------|--|--|

| Sample Name                                                               | SiO <sub>2</sub> Thickness [nm] |  |  |

| as-depo.                                                                  | 35.0                            |  |  |

| O <sub>2</sub> -600°C                                                     | 37.1                            |  |  |

| O <sub>2</sub> -1000°C                                                    | 37.6                            |  |  |

| $O_2\text{-}1000^\circ\text{C}{\rightarrow}N_2\text{-}600^\circ\text{C}$  | 32.5                            |  |  |

| O <sub>2</sub> -1000°C→N <sub>2</sub> -800°C                              | 37.1                            |  |  |

| $O_2\text{-}1000^\circ\text{C}{\rightarrow}N_2\text{-}1000^\circ\text{C}$ | 41.5                            |  |  |

| N <sub>2</sub> -1000°C                                                    | 37.0                            |  |  |

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset.

**Applied Physics Letters**

AIP Publishing

ACCEPTED MANUSCRIPT

PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

# **Applied Physics Letters**

ACCEPTED MANUSCRIPT

This is the author's peer reviewed, accepted manuscript. However, the online version of record will be different from this version once it has been copyedited and typeset. PLEASE CITE THIS ARTICLE AS DOI: 10.1063/5.0245289

×10<sup>16</sup>

as-epi

N<sub>2</sub>-1000°C

as-depo.